**NASA SP-8070**

NASA SPACE VEHICLE DESIGN CRITERIA (GUIDANCE AND CONTROL)

# SPACEBORNE DIGITAL COMPUTER SYSTEMS

**MARCH 1971**

#### GUIDE TO THE USE OF THIS MONOGRAPH

The purpose of this monograph is to organize and present, for effective use in spacecraft development, the significant experience and knowledge accumulated in development and operational programs to date. It reviews and assesses current design practices, and from them establishes firm guidance for achieving greater consistency in design, increased reliability in the end product, and greater efficiency in the design effort. The monograph is organized into three major sections that are preceded by a brief *Introduction* and complemented by a set of *References*.

The State of the Art, section 2, reviews and discusses the total design problem, and identifies which design elements are involved in successful designs. It describes succinctly the current technology pertaining to these elements. When detailed information is required, the best available references are cited. This section serves as a survey of the subject that provides background material and prepares a proper technological base for the Design Criteria and Recommended Practices.

The *Design Criteria*, shown in section 3, state clearly and briefly what rule, guide, limitation, or standard must be imposed on each essential design element to insure successful design. The *Design Criteria* can serve effectively as a checklist for the project manager to use in guiding a design or in assessing its adequacy.

The Recommended Practices, as shown in section 4, state how to satisfy each of the criteria. Whenever possible, the best procedure is described; when this cannot be done concisely, appropriate references are provided. The Recommended Practices, in conjunction with the Design Criteria, provide positive guidance to the practicing designer on how to achieve successful design.

Both sections have been organized into decimally numbered subsections so that the subjects within similarly numbered subsections correspond from section to section. The format for the Contents displays this continuity of subject in such a way that a particular aspect of design can be followed through both sections as a discrete subject.

The design criteria monograph is not intended to be a design handbook, a set of specifications, or a design manual. It is a summary and a systematic ordering of the large and loosely organized body of existing successful design techniques and practices. Its value and its merit should be judged on how effectively it makes that material available to and useful to the user.

### **FOREWORD**

NASA experience has indicated a need for uniform criteria for the design of space vehicles. Accordingly, criteria are being developed in the following areas of technology:

Environment Structures Guidance and Control Chemical Propulsion

Individual components of this work will be issued as separate monographs as soon as they are completed. This document, *Spaceborne Digital Computer Systems*, is one such monograph.

A list of all previously issued monographs can be found at the back of this publication.

These monographs serve as guides to NASA design and mission planning. They are used to develop requirements for specific projects and also are cited as the applicable references in mission studies and in contracts for design and development of space vehicle systems.

This monograph was prepared for NASA under the cognizance of the Jet Propulsion Laboratory, California Institute of Technology. Principal contributors were Mr. William C. Hoffman of Aerospace Systems, Inc., Professor Albert L. Hopkins, Jr. of the Massachusetts Institute of Technology, and Mr. John P. Green, Jr. of Intermetrics, Inc. The program manager was Mr. John Zvara of Aerospace Systems, Inc.

The effort was guided by an advisory panel which was chaired by Professor Hopkins. The following individuals participated in the advisory panel and monograph review activities:

| A. A. Avizienis   | University of California, Los Angeles             |

|-------------------|---------------------------------------------------|

| D. O. Baechler    | Bellcomm, Inc.                                    |

| T. C. Bartee      | Harvard University                                |

| J. M. Black       | NASA Flight Research Center                       |

| J. V. Christensen | NASA Ames Research Center                         |

| B. M. Dobrotin    | Jet Propulsion Laboratory                         |

| B. L. Dove        | NASA Langley Research Center                      |

| B. J. Jansen      | UNIVAC, Defense Systems Division                  |

| L. R. Manoni      | United Aircraft, Hamilton Standard Systems Center |

| W. J. Patzer      | IBM, Federal Systems Division                     |

| D. H. Schaeffer   | NASA Goddard Space Flight Center                  |

| G. P. Talcott     | Raytheon Co., Equipment Division                  |

| W. E. VanderVelde | Massachusetts Institute of Technology             |

|                   |                                                   |

Contributions in the form of design and development practices were also provided by many other engineers of NASA and the aerospace community.

Comments concerning the technical content of this monograph will be welcomed by the National Aeronautics and Space Administration, Office of Advanced Research and Technology (Code RE), Washington, D.C. 20546.

March 1971

# **CONTENTS**

| 1. | INTRODUCTION                        | •      | •    | ٠    | •   | ٠ | •   | •   | •    | •    | •     | •  | •  | •  | ٠ | • | • | • | I  |

|----|-------------------------------------|--------|------|------|-----|---|-----|-----|------|------|-------|----|----|----|---|---|---|---|----|

| 2. | STATE OF THE ART                    |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 2  |

|    | 2.1 Spaceborne Computer Functions   | s .    |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 2  |

|    | 2.2 System Design                   |        |      |      |     |   |     |     |      | •    |       |    | -  |    |   |   |   |   | 13 |

|    | 2.3 Physical Characteristics        |        |      |      |     |   |     |     |      |      |       |    | •  |    |   |   |   |   | 29 |

|    | 2.4 Environmental Design Factors    |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 33 |

|    | 2.5 Reliability and Fault Tolerance |        |      |      |     |   | •   |     |      |      |       |    |    |    |   |   |   |   | 35 |

|    | 2.6 Testing and Checkout            |        |      | •    |     |   |     |     | ٠    |      | •     | ٠  |    |    |   |   |   |   | 4] |

| 3. | DESIGN CRITERIA                     |        |      |      |     |   |     |     | •    |      |       |    |    | •  |   |   | ٠ |   | 43 |

|    | 3.1 Design Tradeoffs                |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 43 |

|    | 3.2 System Design                   |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 44 |

|    | 3.3 Simulation                      |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 45 |

|    | 3.4 Testing and Checkout            |        |      |      | ٠   |   |     | •   |      |      |       |    |    |    |   | • |   |   | 45 |

|    | 3.5 Reliability and Fault Tolerance |        |      |      | •   | • | •   |     | •    |      |       |    |    | •  |   | • | • |   | 46 |

| 4. | RECOMMENDED PRACTICES .             | ٠      |      |      | •   |   | ٠   |     |      |      |       |    | •  |    | • |   |   |   | 46 |

|    | 4.1 Design Tradeoffs                |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 4  |

|    | 4.2 System Design                   |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 49 |

|    | 4.3 Simulation                      |        |      |      |     |   |     |     |      |      |       |    |    |    |   |   |   |   | 5  |

|    | 4.4 Testing and Checkout            |        |      |      | •   |   |     |     |      |      |       |    |    |    |   |   |   |   | 53 |

|    | 4.5 Reliability and Fault Tolerance |        | ٠    |      |     |   |     |     |      |      |       | •  | •  |    |   |   |   | • | 56 |

| R  | EFERENCES                           |        |      |      |     |   |     |     |      |      | •     |    | •  |    | • |   |   |   | 59 |

| G  | LOSSARY                             |        |      | •    |     |   |     | •   |      | ٠    | •     |    |    |    |   |   |   | • | 6  |

| N  | ACA CDACE VEUICI E DECICNICE        | ידיז ( | ED I | A N. | (ON |   | DAI | рцс | e te | CIII | י רוק | тО | DA | тъ |   |   |   |   | 71 |

# SPACEBORNE DIGITAL COMPUTER SYSTEMS

#### 1. INTRODUCTION

As space vehicle missions have become more complex, the use of onboard digital computers has become more prevalent. The functions which these computers are assigned to perform are also expanding in number and magnitude. As a result, the problem of specifying and designing digital computers for space vehicles has increased in complexity.

Although most spaceborne digital computers are of the type often referred to as "general purpose," they have been in fact special-purpose machines in that a particular choice of design must reflect the requirements of the particular mission application. Thus, the program manager must be aware of the capabilities and limitations of spaceborne computer systems and the design tradeoffs which might affect his application.

The flight performance of spaceborne digital computer systems has generally been successful. However, a number of recurring problems have been experienced during the design, development, and testing of these machines. Previous systems have been very costly, have required major redesigns, and have caused significant schedule delays. Most difficulties have resulted from 1) lack of adequate capacity and flexibility to accommodate expanded requirements, 2) poorly defined subsystem and interface specifications, 3) the impact on software of changing mission requirements, and 4) reliability demands.

Important factors which influence the design and performance of spaceborne digital computer systems include:

- System architecture

- Computational capability (precision, speed, throughput, memory capacity, input/output capability, instruction repertoire, etc.)

- Adaptability (expandability, flexibility, compatibility, etc.)

- Provisions for interface with other components of the system

- Software (support and applications programs, ease of programming, etc.)

- Cost (money, weight, power, volume, time)

- Reliability related items (fault tolerance, failure rate, redundancy, ease of checkout, etc.)

- Environment (temperature, shock and vibration, electromagnetic and nuclear radiation, noise, power fluctuations, etc.)

- Packaging and cabling design

The preferred design should consider the expanding nature of the requirements, potential advances in the technological state of the art, and the entire spectrum of environmental requirements. It should strike a balance between hardware complexity and software simplicity, and facilitate simulation, testing, and checkout.

This monograph discusses considerations which form a basis for the specification, design and evaluation of digital computer systems for spaceborne applications. Detailed discussion of the following items are outside the scope of this monograph: software development, mechanical and electrical design, hardware technology, I/O equipment, displays, and test equipments or specifications.

Related documents are SP-8053, "Nuclear and Space Radiation Effects on Materials," June 1970 and SP-8054, "Space Radiation Protection," June 1970.

## 2. STATE OF THE ART

The state of the art of spaceborne digital computer systems has undergone a rapid development over the past decade and will continue to do so in the future. An onboard digital computer has now become essential for most new space vehicles. This section provides a brief description and appraisal of some of the design and flight experience of these systems, and the technology which presently exists.

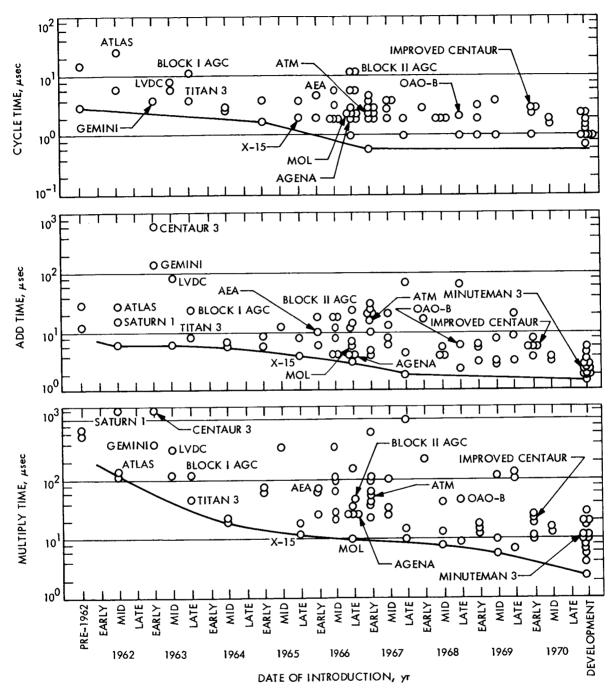

To appraise the various design approaches to spaceborne computers, it is convenient to consider their common features. Table 1 summarizes the more important characteristics of selected digital computers which have been designed or are under development for space vehicle application. Although the data in table 1 was compiled from numerous sources, much of the information was drawn from references 1 and 2. Due primarily to the differences in requirements between launch vehicles and spacecraft, separate computer systems are usually designed for both the launch vehicle and spacecraft. The launch vehicle requires a large amount of complex high-speed computation, while the spacecraft has fewer computations over a long period of time.

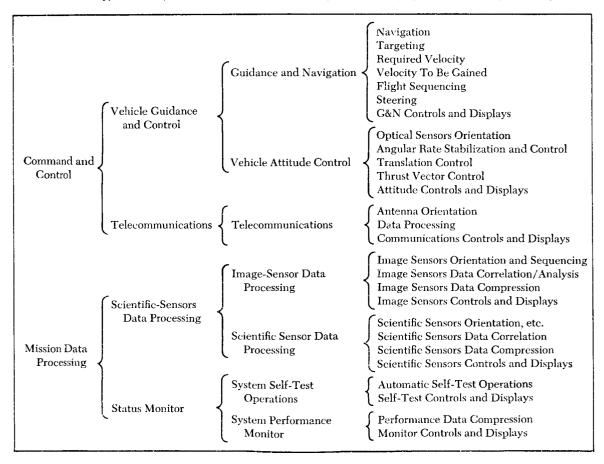

# 2.1 Spaceborne Computer Functions

The functions or tasks of spaceborne computers have ranged from simple mission sequencing to complex multipurpose uses in manned spacecraft. With the expanding complexity of space missions, the number of tasks which are assigned to onboard digital computers is growing rapidly. In many cases, digital computers are taking over functions which were formerly performed by analog equipment. As time goes by, increasing experience is gained in sharing a computer or system of computers among numerous tasks. In spaceborne applications, most of the tasks involve real-time, sampled-data control problems, which place specific demands on, and yield certain advantages for, the computer system. Sections 2.1.1 through 2.1.6 summarize some of the most common onboard computer tasks.

TABLE 1.-Selected Spaceborne Computer Characteristics

| Space Vehicle                                   |                    | Physical Characte | eristics    |                     |

|-------------------------------------------------|--------------------|-------------------|-------------|---------------------|

| (Computer Designation)                          | Weight,<br>kg (lb) | Size,<br>m³(ft³)  | Power,<br>W | Componentsc         |

| ATLAS<br>(ARMA MICRO)                           | 9.1(20)            | 0.011(0.4)        | 50          | Discrete            |

| SATURN 1<br>(IBM ASC-15)                        | 34.0(75)           | 0.06(2.12)        | 150         | Discrete            |

| TITAN 2/3-C<br>(IBM ASC-15B)                    |                    |                   |             | Discrete            |

| CENTAUR<br>(LIBRASCOPE-3)                       | 30.4(67)           | 0.052(1.83)       | 135         | Discrete            |

| GEMINI<br>(IBM GDC)                             | 26.7(59)           | 0.047(1.65)       | 85          | Discrete            |

| SABRE 2<br>(UNIVAC 1824-D)                      | 38.5(85)           | 0.033(1.15)       | 260         | DTL IC/<br>Discrete |

| SATURN 1B/5<br>(IBM LVDC)                       | 36.2(80)           | 0.06(2.1)         | 138         | DTL Hybrid          |

| TITAN 8-C<br>(UNIVAC 1824-MGC)                  | 45.3(100)          | 0.057(2.0)        | 168         | DTL IC/<br>Discrete |

| APOLLO CSM/LM<br>(MIT/RAYTHEON AGC BLOCK I)     | 39.4(87)           | 0.028(1)          | 125         | DCTL IC             |

| MINUTEMAN 2<br>(AUTONETICS D-37C)               |                    |                   |             |                     |

| X-15<br>(HONEYWELL HDC-801)                     | 31.7(70)           | 0.04(1.4)         | 150         | HLTTL IC            |

| AGENA<br>(HONEYWELL HDC-501)                    | 11.3(25)           | 0.014(0.49)       | 92          | DTL IC              |

| APOLLO LM-AEA<br>(TRW MARCO 4418)               | 14.7(32.5)         | 0.016(0.58)       | 91          | DTL IC              |

| APOLLO CSM/LM<br>(MIT-RAYTHEON AGC BLOCK II)    | 26.3(58)           | 0.028(1)          | 100         | DCTL IC             |

| MOL<br>(IBM SYSTEM/4Pi-EP)                      | 75.6(167)          | 0.113(4.0)        | 763         | TTL IC              |

| GEMINI EXPERIMENT<br>(CDC 449-1)                | 3.9(8.5)           | 0.002(0.08)       | 5           | IC                  |

| APOLLO TELESCOPE MOUNT<br>(IBM SYSTEM/4Pi-TC 1) | 45.3(100)          | 0.07(2.5)         | 165         | TTL IC              |

| OAO-B<br>(NASA/GSFC-WESTINGHOUSE OBP)           | 17.7(39)           | 0.015(0.52)       | 36          | LPDTL IC            |

| IMPROVED CENTAUR<br>(TELEDYNE TDY-300)          | 26.8(59)           | 0.035(1.25)       | 185         | Hybrid LSI          |

| ADVANCED IMP<br>(NASA/GSFC SDP-3)               | 1.8(4)             | 0.04(1.4)         | 2           | LPDTL IC            |

| MINUTEMAN 8<br>(HONEYWELL HDC-701)              | 22.6(50)           | 0.034(1.2)        | 270         | IC                  |

| MARINER '71                                     | 10.2(22.5)         | 0.01(0.37)        | 22.5        | IC/Discrete         |

TABLE 1.-(continued)

|                                                   |                  | Memory F              | eatures            |                               |

|---------------------------------------------------|------------------|-----------------------|--------------------|-------------------------------|

| Space Vehicle <sup>a</sup> (Computer Designation) | Typed            | Word<br>Size,<br>bits | Capacity,<br>words | Access/Cycle<br>Time,<br>μsec |

| ATLAS<br>(ARMA MICRO)                             | NDRO Core        | 22                    | 2K-8K              | /27                           |

| SATURN 1<br>(IBM ASC-15)                          | Drum             | 27                    | 6886               |                               |

| TITAN 2/3-C<br>(IBM ASC-15B)                      | Drum             | 27                    | 1160               |                               |

| CENTAUR<br>(LIBRASCOPE-3)                         | Drum             | 25                    | 3K                 |                               |

| GEMINI                                            | NDRO Core        | 39                    | 4K                 | 4/4                           |

| (IBM GDC)                                         | Tape             | 13                    | 85K                |                               |

| SABRE 2                                           | NDRO Film        | 48                    | 4K                 | /4                            |

| (UNIVAC 1824-D)                                   | DRO Film         | 24                    | 512                | 0.7/4                         |

| SATURN 1B/5<br>(IBM LVDC)                         | DRO Core         | 28                    | 4K-32K             | 4/8                           |

| TITAN 3-C                                         | DRO Film         | 24                    | 512                | 0.7/3.9                       |

| (UNIVAC 1824-MGC)                                 | NDRO Film        | 48                    | 4K                 | 0.7/3.9                       |

| APOLLO CSM/LM                                     | DRO Core         | 16                    | 1K                 | /11.7                         |

| (MIT/RAYTHEON AGC BLOCK I)                        | NDRO Core Rope   | 16                    | 24K                | /11.7                         |

| MINUTEMAN 2<br>(AUTONETICS D-37C)                 | Disc             | 27                    | 6966               | /78                           |

| X-15                                              | NDRO Core        | 24                    | 4K-32K             | 1.0/2.0                       |

| (HONEYWELL HDC-801)                               | NDRO Plated Wire | 24                    | 4K-32K             | 1.0/2.0                       |

| AGENA<br>(HONEYWELL HDC-501)                      | DRO Core         | 20                    | 4K-8K              | 0.65/2                        |

| APOLLO LM-AEA<br>(TRW MARCO 4418)                 | DRO Core         | 18                    | 4K-8K              | /5                            |

| APOLLO CSM/LM                                     | DRO Core         | 16                    | 2K                 | /11.7                         |

| (MIT-RAYTHEON AGC BLOCK II)                       | NDRO Core Rope   | 16                    | 36K                | /11.7                         |

| MOL<br>(IBM SYSTEM/4Pi-EP)                        | DRO Core         | 32                    | 16K-128K           | 0.9/2.5                       |

| GEMINI EXPERIMENT                                 | DRO Thin Film    | 24                    | 256                | 4.0/                          |

| (CDC 449-1)                                       | NDRO Core        | 12                    | 7680               | 4.0/                          |

| APOLLO TELESCOPE MOUNT<br>(IBM SYSTEM/4Pi-TC 1)   | DRO Core         | 8                     | 8K-64K             | 0.9/2.5                       |

| OAO-B<br>(NASA/GSFC-WESTINGHOUSE OBP)             | DRO Core         | 18                    | 4K-64K             | 0.85/2.5                      |

| IMPROVED CENTAUR<br>(TELEDYNE TDY-300)            | DRO Core         | 24                    | 8K-16K             | 1.5/3.0                       |

| ADVANCED IMP<br>(NASA/GSFC SDP-3)                 | DRO              | 16                    | 4K-64K             | 5/10                          |

| MINUTEMAN 3<br>(HONEYWELL HDC-701)                | NDRO Plated Wire | 32                    | 4K-16K             | 0.6/                          |

| MARINER '71                                       | DRO Core         | 22                    | 512                | 4/7                           |

TABLE 1.-(continued)

|                                                      |                           |              | Arithmetic                   | Features                               |                    |

|------------------------------------------------------|---------------------------|--------------|------------------------------|----------------------------------------|--------------------|

| Space Vehicle <sup>a</sup><br>(Computer Designation) | Data<br>Flow <sup>e</sup> | Data<br>Type | Number<br>of<br>Instructions | Add/Multiply/<br>Divide Times,<br>μsec | Index<br>Registers |

| ATLAS (ARMA MICRO)                                   | s                         | Fixed        | 19                           | 27/135/324                             |                    |

| SATURN 1<br>(IBM ASC-15)                             | S                         | Fixed        | 39                           | 156/1872/23K                           | 0                  |

| TITAN 2/3-C<br>(IBM ASC-15B)                         | S                         | Fixed        | 39                           | 156/1872/23K                           | 0                  |

| CENTAUR<br>(LIBRASCOPE-3)                            | S                         | Fixed        | 12                           | 625/4218/4218                          | 0                  |

| GEMINI<br>(IBM GDC)                                  | S                         | Fixed        | 16                           | 140/420/840                            | 0                  |

| SABRE 2<br>(UNIVAC 1824-D)                           | P                         | Fixed        | 45                           | 8/44-92/128                            | 3                  |

| SATURN 1B/5<br>(IBM LVDC)                            | S                         | Fixed        | 18                           | 82/328/656                             | 0                  |

| TITAN 3-C<br>(UNIVAC 1824-MCC)                       | P                         | Fixed        | 45                           | 8/44-92/128                            | 3                  |

| APOLLO CSM/LM<br>(MIT/RAYTHEON AGC BLOCK I)          | P                         | Fixed        | 11                           | 23.4/117/210                           | 0                  |

| MINUTEMAN 2<br>(AUTONETICS D-37C)                    | S                         | Fixed        | 57                           | ~350/~1400/                            | 0                  |

| X-15<br>(HONEYWELL HDC-801)                          | P                         | Fixed        | 89                           | 4/12/30                                | 6                  |

| AGENA<br>(HONEYWELL HDC-501)                         | P                         | Fixed        | 59                           | 4/24/24                                | 4                  |

| APOLLO LM-AEA<br>(TRW MARCO 4418)                    | P                         | Fixed        | 27                           | 10/70/73                               | 1                  |

| APOLLO CSM/LM<br>(MIT-RAYTHEON AGC BLOCK II)         | P                         | Fixed        | 34                           | 23.4/46.8/81.9                         | 0                  |

| MOL<br>(IBM SYSTEM/4Pi-EP)                           | P                         | Fixed        | 72                           | 5.8/9.5/18.3                           | 16                 |

| GEMINI EXPERIMENT<br>(CDC 449-1)                     | P                         | Fixed        | 38                           | 28/604/                                | 2                  |

| APOLLO TELESCOPE MOUNT<br>(IBM SYSTEM/4Pi-TC 1)      | P                         | Fixed        | 54                           | 15/51/54                               | 3                  |

| OAO-B<br>(NASA/GSFC-WESTINGHOUSE OBP)                | P                         | Fixed        | 50                           | 6.25/42.5/90                           | 1                  |

| IMPROVED CENTAUR<br>(TELEDYNE TDY-300)               | P                         | Fixed        | 33                           | 6/22.5/40.5                            | 3                  |

| ADVANCED IMP<br>(NASA/GSFC SDP-3)                    | S                         | Fixed        | 54                           | 78/ /                                  | 1                  |

| MINUTEMAN 3<br>(HONEYWELL HDC-701)                   | P                         | Fixed        | 56                           | 2.4/10.8/21.4                          | 3                  |

| MARINER '71                                          | S                         | Fixed        | 16                           |                                        | 1                  |

TABLE 1.—(continued)

| Cross Webines                               | Input/Output | utput           |                                                                                                                         |

|---------------------------------------------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| (Computer Designation)                      | Channels     | Inter-<br>rupts | Comments                                                                                                                |

| ATLAS<br>(ARMA MICRO)                       | 2            |                 | Registers are delay lines. Two aperture core memory.                                                                    |

| SATURN 1<br>(IBM ASC-15)                    | 10           |                 |                                                                                                                         |

| TITAN 2/3-C<br>(IBM ASC-15B)                |              |                 | 25-bit data word; 9-bit instruction word.                                                                               |

| CENTAUR<br>(LIBRASCOPE-3)                   | 32           | 0               | Two-address instruction-operand & location of next instruction. Multiply & divide by series of additions.               |

| GEMINI<br>(IBM GDC)                         | 14           | 0               | 13-bit instruction word; 26-bit data word. 13-bits of memory word are "read-only."                                      |

| SABRE 2<br>(UNIVAC 1824-D)                  | 8            | 63              | 24-bit data word; 16-bit instruction word.                                                                              |

| SATURN 1B/5<br>(IBM LVDC)                   | 25           | 7               | 26-bit data word; 13-bit instruction word. Memory expandable in 4K modules. Weight & size for $16K$ . TMR logic.        |

| TITAN 3-C<br>(UNIVAC 1824-MGC)              | 23           | 4               | 16-bit instruction word; 24-bit data word. Double precision add & subtract.                                             |

| APOLLO CSM/LM<br>(MIT/RAYTHEON AGC BLOCK I) | 6            | 8               | LM fixed memory capacity was 12K. Index instruction.                                                                    |

| MINUTEMAN 2<br>(AUTONETICS D-37C)           | 14           | 1               | 3 parity bits per word; split data word available. Phase register may serve as limited index register. Tailored $1/0$ . |

| X-15<br>(HONEYWELL HDC-801)                 | 28           | 32              | 32K maximum total memory capacity. 4-character alpha-numeric data word.                                                 |

| AGENA<br>(HONEYWELL HDC-501)                | 52           | 16              | 10- or 20-bit instruction word. Also designated ALERT.                                                                  |

| APOLLO LM-AEA<br>(TRW MARCO 4418)           | 1            | 1               | Memory can be partially hardwired.                                                                                      |

$TABLE_{i}I.-(continued)$

|                                                                                                                                                                                                                                                                                                            | India/Outnit                                 | Jutonit                                    |                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Space Vehicle <sup>a</sup><br>(Computer Designation)                                                                                                                                                                                                                                                       | Channels                                     | Inter-<br>rupts                            | Comments                                                                                                                                                         |

| APOLLO CSM/LM (MIT-RAYTHEON AGC BLOCK II)                                                                                                                                                                                                                                                                  | 15                                           | 10                                         | Index instruction. Double precision add.                                                                                                                         |

| MOL<br>(IBM SYSTEM/4Pi-EP)                                                                                                                                                                                                                                                                                 | 8                                            | 7                                          | 1-parity bit per 8-bit byte. Data word—2, 4, 8 bytes; instruction word—2, 4, 6 bytes. Floating point optional. Microprogram. Size, power, weight for 16K memory. |

| GEMINI EXPERIMENT<br>(CDC 449-1)                                                                                                                                                                                                                                                                           | 1                                            | 1                                          | Internal battery, keyboard, and dial readout. 12-bit parallel, 2-byte serial.                                                                                    |

| APOLLO TELESCOPE MOUNT (IBM SYSTEM/4Pi-TC 1)                                                                                                                                                                                                                                                               |                                              |                                            | 2-byte serial; 8-bit parallel. Data word 2 bytes; instruction word 1, 2, 3 bytes. Size, weight $\&$ power for 16K memory.                                        |

| OAO-B<br>(NASA/GSFC-WESTINGHOUSE OBP)                                                                                                                                                                                                                                                                      | 6                                            | 16                                         | Size, weight & power given for 4K memory. Scale register to locate binary point. Dual busses accommodate spare I/O, CPU, & memory units.                         |

| IMPROVED CENTAUR<br>(TELEDYNE TDY-300)                                                                                                                                                                                                                                                                     | 36                                           | 70                                         | Size, weight & power for 16K memory version and PCM telemetry master control capability.                                                                         |

| ADVANCED IMP<br>(NASA/GSFC SDP-3)                                                                                                                                                                                                                                                                          | 61                                           | 16                                         | Size, weight & power estimates do not include memory. Double precision add & subtract.                                                                           |

| MINUTEMAN 3<br>(HONEYWELL HDC-701)                                                                                                                                                                                                                                                                         |                                              | æ                                          | 16- or 32-bit instruction word. Microprogrammable.                                                                                                               |

| MARINER '71                                                                                                                                                                                                                                                                                                | 42                                           | 13                                         | Parallel redundancy for maneuver. Weight contains sequencer. Interrupts include flight commands, telemetry system, and TV subsystems.                            |

| Notes: *Arranged in approximate chronological order by date of computer introduction.  **eIC = Integrated circuit; DTL = diode-transistor logic; DCTL = direct-coupled transistor logic; TTl = transistor logic; HL = high level, as in HLTTL; LP = low power, as in LPDTL; LSI = large scale integration. | al order by de-transist ogic; TTI scale inte | date of or logic; = tran- ? = low gration. | <sup>d</sup> DRO = destructive readout; NDRO = nondestructive readout.  eS = serial; P = parallel.                                                               |

# 2.1.1 Guidance and Navigation

Digital computers were first placed on launch vehicles such as Atlas, Centaur, Minuteman and Titan to perform guidance and navigation (G&N) calculations. To accomplish this G&N task, the computer first processes data from various sources (e.g., inertial measurement units, star trackers, and horizon sensors) to estimate the present attitude, position, and velocity of the space vehicle. Using stored or computed trajectory data, it then determines any velocity corrections which are necessary and generates the appropriate steering commands, including thrust commencement and/or termination signals. Normally, the computation requirements for guidance and navigation do not by themselves dictate an excessively large or fast machine by present day standards. However, extreme accuracy and reliability demands can place stringent requirements on the spaceborne computer.

Guidance and navigation of a spacecraft in orbit involve calculations for such functions as 1) orbit parameters for use with experiment data, 2) steering commands for orbit maintenance, generation of ground tracks and display of latitude, longitude, and altitude, and 3) rendezvous guidance commands. Some missions require the capability of orbit changes in addition to orbit maintenance. In the Apollo guidance computer (AGC), the performance of all those G&N tasks requires some 24,000 words of memory and 26,000 operations per second (peak), out of the totals available for all calculations of 38,000 words and about 40,000 operations per second.

The Apollo spacecraft uses a stable platform for the primary inertial navigation system, whereas future vehicles may use strapdown systems which require additional calculations to update the inertial reference (e.g., see refs. 3 to 6). The memory requirement remains about the same as for a stable platform system, but the speed requirement depends heavily on the resolution desired and the rate at which the vehicle attitude is changing. For example, it is estimated that a system comprising three single-degree-of-freedom strapdown gyros and accelerometers in a vehicle rotating at 0.35 rad (20 deg)/sec would require approximately 120,000 operations per second to establish a resolution of 0.15 mrad ( $\pm$ 30 sec of arc) (ref. 7).

## 2.1.2 Stabilization and Control

The purpose of a stabilization and control (S&C) system is to orient and maintain the space vehicle with a specified attitude and/or attitude rate. Conventionally, analog circuitry has been employed to provide the required control signals to the appropriate effectors (e.g., engine gimbal actuator, reaction jets, and control moment gyros). During the development of the Apollo spacecraft, however, it was decided to switch from an analog to a digital mechanization of the autopilot in the onboard computer (refs. 8 and 9). Digital S&C systems have since been designed and flown on a number of space vehicles, including both the Apollo command and lunar modules, Titan 3-C (ref. 10) and the improved Centaur (ref. 11).

Since the dominant natural frequencies of an S&C system are much higher than those of the G&N system, a digital S&C system has a significant effect on the speed requirements of the onboard computer. An example of the computer requirements for a reaction jet S&C system during

coasting flight is obtained from experience with the Apollo program; about 2,000 memory words and 15,000 operations per second are necessary to support the control system itself, and another 2,500 words provide associated functions such as star tracker calculations (ref. 7). The requirements for S&C during powered flight are even more demanding. For example, the Apollo lunar module digital autopilot uses about 3,500 memory words and on the order of 25,000 operations per second (ref. 12).

# 2.1.3 Man/Machine Interface

For manned space vehicles, online communication between the computer and the crew is required. Thus, the computer must possess the capability to request action or information, display real-time status and other data, and accept and execute manual commands. Because man is accustomed to alphabetic and decimal characters whereas computers operate with binary numbers, all information to be communicated must be converted to the proper form before it is intelligible. Several implications of the man/machine interface on the computer design are discussed in reference 13. The major effect on the computer design has been to increase both the memory and input/output requirements. Although the programs required to implement the man/machine interface are long, their duty cycle is low so they do not consume much of the computer's time (ref. 14).

The Apollo guidance computer uses a peak rate of about 3,600 operations per second to interpret an input or handle an output in less than 0.1 sec, which appears as virtually an instantaneous response to the operator (ref. 7). The interface between the crew and the AGC consists of a display and keyboard assembly (DSKY) which has function keys for verb, noun, clear, standby, keyboard release, enter, and reset; numeric keys for zero through nine; and plus and minus signs. Three two-digit electroluminescent (EL) displays are used to indicate the verb, noun and program number that the computer is currently using, and three five-digit-plus-sign EL displays are used to show input and output data. Discrete outputs turn on status lamps to indicate a variety of events including uplink activity, gimbal lock, and operator error.

The data entry and display assembly used for communication with the abort electronics assembly (AEA) computer in the Apollo lunar module is similar to the DSKY but less elaborate. It also comprises a keyboard and EL address and data displays (ref. 15). A push-button keyboard was used for manual data insertion to the Gemini computer, but EL devices were not considered because the circuitry required was too complex, and the display intensity would have been insufficient in bright sunlight. Instead, electromechanical decimal wheel devices were used (ref. 16).

No alphabetic input or output has been used with the Gemini or Apollo computers, although the use of symbolic coding would have reduced training burdens as well as simplifying control and interpretation problems. The main drawback in the use of alphabetic or symbolic coding at the time of the Apollo design was the lack of reliable, solid-state display translators. However, the convenience of alphabetic information will undoubtedly lead to the use of symbolic codes in future spaceborne computers. The application of symbolic coding for spacecraft computer control and display has been investigated at the NASA Ames Research Center (ARC) in a simulation environment with considerable success (ref. 17).

## 2.1.4 Data Processing

A large amount of data can be generated in flight by scientific experiments as well as by other spacecraft subsystems, such as guidance and navigation instrumentation. Depending upon the type of data and the extent of processing desired, the onboard computer speed and size requirements may be significantly altered. The engineering and scientific data generally have a high bandwidth and are available in real time only, corrupted by noise and not in a convenient form. To reduce this data to a manageable and comprehensible form, without losing the information content, it may be processed through an onboard computer. Such processing can include filtering, smoothing, estimating, averaging, compression, and formating for display or transmission.

Even for small scientific spacecraft, an onboard computer can be used as the master control for collecting data and formating it for telemetry. Since the power consumption of the computer is generally much lower than that of the telemetry transmitter, it is easy to justify substantial computation to achieve a moderate amount of data compression. For example, the use of a small central computer in place of the individual processors on the three IMP-F satellite experiments on Explorer 34 would have reduced the average power consumption by about 70%, without increasing the size or weight requirements (ref. 18). A general-purpose stored-program computer, the SDP-3, has been designed at the NASA Goddard Space Flight Center (GSFC) for use as the core of the data system of small scientific spacecraft and will be flown as an

TABLE 2.-Summary of Computer Requirements for Typical Experiments (ref. 24)

| Functions                                 | Memor  | Speed<br>Requirements |        |                  |

|-------------------------------------------|--------|-----------------------|--------|------------------|

| r unctions                                | Data   | Program               | Total  | (Operations/sec) |

| Checkout                                  | 200    | 10                    | 210    | 17               |

| Experiment Control                        |        |                       |        |                  |

| Sequencing                                | 2      | 12                    | 14     | 10               |

| Mode control                              | 2      | 12                    | 14     | 10               |

| Rock spectra analysis                     | 17 000 | 3 000                 | 20 000 | 200              |

| Pointing control                          | 1 000  | 2 000                 | 3 000  | 12               |

| Solar flare sensing                       | 9 000  | 1 000                 | 10 000 | 70 000           |

| Data Compression                          |        |                       |        |                  |

| Simple predictor                          |        | 20                    | 20     | 500              |

| Sophisticated interpolator (ESSI system)  | 1 000  | 150                   | 1 150  | 1 400            |

| Data Reduction                            |        |                       |        |                  |

| Land SSE analysis (continuous)            | 900    | 100                   | 1 000  | 50 000           |

| Land SSE analysis (intermittent)          | 1 100  | 100                   | 1 200  | 25 000           |

| Magnetic field autocorrelation experiment | 100    | 50                    | 150    | 340              |

| Plasma experiment                         | 25     | 115                   | 140    | 140              |

engineering experiment on IMP-I (ref. 19). As an example of onboard data processing requirements, the reduction of 238 pieces of raw data from the IMP-F magnetic field autocorrelation experiment to one average value and nine other statistical values is estimated to require 150 memory words and 340 operations per second. Calculating a sum, a sum of squares, and their ratio for the plasma statistics experiment on that spacecraft (ref. 20) would require about 140 memory words and 140 operations per second (ref. 7).

The computer can also serve as the hub for data transfer through the spacecraft, such as the IBM primary processor and data storage system (ref. 21) on the Orbiting Astronomical Observatory (OAO). A more sophisticated, general-purpose central computer, the NASA/GSFC-Westinghouse onboard processor (OBP), was scheduled to be flown on the OAO-B (refs. 22 and 23). Had the launch been successful, the OBP would have taken a central role in the spacecraft's operation and control as well as data handling.

Reference 24 discusses some of the many ways onboard computers may be used to enhance experimentation in space and indicates the wide range of computer requirements which might be encountered. Estimates of the computer memory and speed requirements for several individual experiments are summarized in table 2 (from ref. 24).

# 2.1.5 Systems Checkout

Systems checkout includes the monitoring, testing and diagnosis of spacecraft systems to detect, and if possible to predict, failures or unsafe conditions. For most spacecraft systems, this consists of comparing current values of system parameters to their nominal ranges. When a value falls outside its acceptable range, a message or signal is sent to the crew or to the ground. However, for some systems, passive monitoring is inadequate and periodic active tests are required. An example of systems checkout is the orbital checkout mode of the Saturn 5 launch vehicle digital computer (LVDC). When the vehicle has achieved orbit, the computer checks out the propulsion system, the mid-course guidance and control system, and other related systems and sends the test results to the ground for analysis. If all tests are satisfactory, the next mission phase may be initiated from the ground (ref. 25).

The checkout of experiments is particularly important on long duration missions since some experiments may not be turned on until a substantial time has elapsed, and others may be operated throughout the mission (ref. 24). The computer requirements for checkout of experiments or other spacecraft systems depend on the number of test points, the type of testing being performed, and the frequency of the checkout. Typical requirements for a sophisticated experiment with fifty scientific data points are shown in table 2 (ref. 24). The memory requirements are dominated by the storage needed to indicate the acceptable range for each checkout point.

Checkout is not restricted to inflight needs but may be performed during certain phases prior to launch. For example, the AGC is used during prelaunch to check out the entire Apollo G&N system. Among other tasks, the AGC determines all drifts and biases in the inertial reference subsystem that can be measured in a 1-g field. In addition, the AGC is used in a simulated flight mode to check out various other vehicle and spacecraft systems. The Saturn 5 LVDC also operates in a prelaunch checkout mode to insure that all guidance system interfaces operate properly prior

to flight. The checkout program includes a computer self-test, complete mission simulation, and a system test, among others (ref. 25). With the development of more flexible and powerful space-borne computers in future programs, the use of an onboard computer for prelaunch checkout of spacecraft systems is expected to grow, and thus reduce the dependence on extensive ground-based facilities. In the advanced Centaur computer, for instance, prelaunch checkout was a major design requirement (ref. 11).

# 2.1.6 Computer Self-Test

A special case of systems checkout is the checkout of the computer itself, which generally requires the running of a self-test program. When an error is detected, its cause may be diagnosed and the error corrected or the computer reconfigured to minimize its effects. This task generally has a minor impact on the computer speed requirements since the self-test program is typically executed every one to two seconds, and is assigned a relatively low priority. However, additional hardware requirements for diagnosis and reconfiguration may be substantial and memory must be provided to store the checking routines.

Typically, a self-test program for checkout or restarting is a boot-strapping procedure which begins with the verification of the most elementary set of instructions, i.e., those which rely on only a fraction of the computer hardware in order to operate. These instructions are then used to construct a decision-making subroutine which verifies some primitive condition on a YES-NO basis. Once verified, this subroutine (or several similarly constructed) is used to check all other instructions and variations in sequence, beginning with the next least complex instruction and working up to the most complex instruction. After all instructions are verified, input/output (I/O) and memory self-test programs check the remaining hardware.

Self-test routines are also important for detecting malfunctions during operation. In the Gemini project, for example, diagnostic subroutines were interleaved in the operational computer program. When they detected a fault, a discrete command was issued to light a malfunction indicator lamp on the control panel. The circuit had a manual reset capability to test whether it was set by a transient malfunction. Three self checks were performed during flight (ref. 15):

- A timing check, based on the noncoincidence of certain signals within the computer under proper timing conditions.

- A thorough diagnostic test which exercised all of the computer's arithmetic operations during each computer cycle in all modes.

- A looping-check, to verify that the computer was following a normal program loop. A counter in the output processor was designed to overflow every 2.75 sec. Each program was written to reset this counter every 2.7 sec; thus, any change in the program flow would cause an overflow and indicate a malfunction.

In addition, a prelaunch mode check was included to verify the contents of memory syllable 2 by summing them. Since this syllable was "read-only" (after loading the memory by ground equipment), the sums could be checked against their known values to insure correct data.

The Apollo guidance computer is equipped with a restart feature comprising alarms to detect malfunction and a standard initiation sequence which leads back into the programs in progress. The AGC has six malfunction detection devices that cause a restart (ref. 26), as follows:

- A parity test of each word read from memory. An odd-parity bit is added to each fixed-memory word at manufacture time and to each erasable word at write time.

- A looping check much like the one on Gemini. A specified register must be periodically tested by any correctly operating program. This register is "wired" and if it is not tested often enough will cause restart.

- A transfer control trap, which detects endless loops containing only control transfer instructions, such as a location L which contains the instruction "transfer control to location L."

- An oscillator fail check caused by stopping of the timing oscillator.

- Voltage fail circuits to monitor the 28-, 14-, and 4-V power levels which drive the computer.

- An interrupt check, which detects excessive time spent in the interrupt mode, or too much time spent between interrupts.

# 2.2 System Design

This section provides a short discussion of the system design of spaceborne digital computers. It includes such considerations as organization, storage capacity, logic design, input/output, and anticipated future trends.

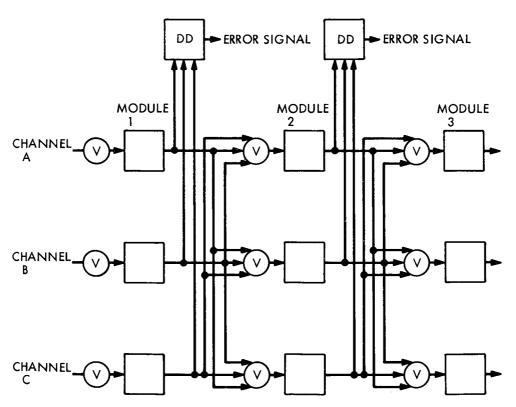

# 2.2.1 System Organization

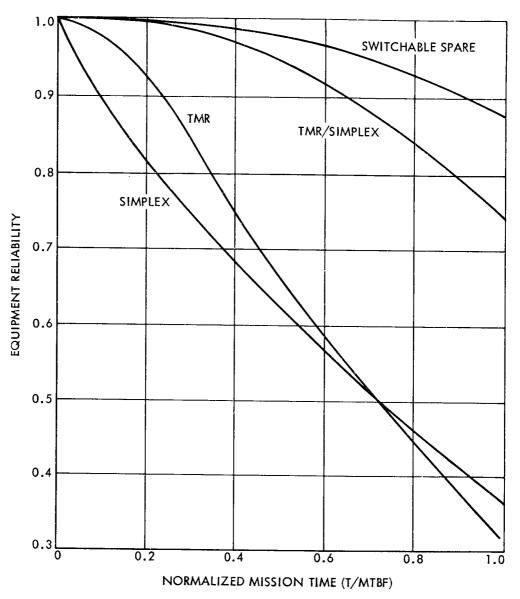

## (1) Central vs Dedicated Systems

There are two extreme approaches to the design of spaceborne computer systems. One approach favors the use of highly reliable, large central data processors to control and process several subsystems on the entire spacecraft. The opposing approach favors the development of small yet flexible, low power, dedicated processors where the ratio of processors to computational functions in any given spacecraft is equal to or greater than one. Large-scale integration (LSI) and complementary metal oxide semiconductor (MOS) technology are making the development of such small programmable processors possible (ref. 27).

There are two major advantages in using one or more small processors per function. One advantage is the ability to integrate subsystems with their computers at an early test stage, and to avoid interferences with other subsystems as might happen in a shared computer. Having its own processor permits the experiment freedom to be flown on different missions without the difficulty

of interfacing with each unique spacecraft processor, since only one experiment to processor interface need be designed. Although interfacing with telemetry cannot be avoided, this is much simpler than interfacing with a central processor. Reliability is another advantage since, with a collection of small decentralized processors, a failure may not jeopardize the entire mission of the spacecraft. The major disadvantages of the decentralized approach are that problems of information exchange and coordination are left unsolved, and error control is difficult to achieve.

The alternate concept of a wholly centralized computer solves many of the information exchange and coordination problems, but creates another in the number and diversity of its interfaces with all the sensors and effectors; and it poses a large challenge to fault-tolerant computer and system design (ref. 28).

A comparison of the two approaches, which was made for an example of an orbital mission to Mars in the early 1970s, is discussed in reference 29. The conclusions indicated that the anticipated functional requirements only lightly load the capacity of a general-purpose computer, and that the effect of economies in power, weight, and size for a centralized approach does not fully offset the inherent reliability of the decentralized concept. However, another study (ref. 18) found that a scientific spacecraft telemetry system utilizing a centralized computer is desirable over the decentralized processing approach, even for small satellites with only a few telemetry experiments.

A compromise between the two extremes which seems to combine their advantages is a distributed system, where information processing is done at various levels (ref. 28). The level at which a particular process takes place is almost entirely a function of the sophistication, reaction time, and bandwidth requirements associated with the process. A central computer is best suited to processes whose data-rate requirements are not severe, but whose sophistication is high in terms of program complexity and/or multiplicity of information sources and destinations. A dedicated computer is correspondingly appropriate for high bandwidth processes with limited complexity.

## (2) Computer Configuration

Although there are innumerable ways of configuring a computer system, all will contain one or more of each of the following units, plus the communication and data paths required to interconnect them (ref. 30):

- Memory

- Processor (arithmetic and control)

- Input/output

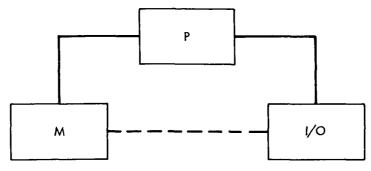

A variety of system configurations have been designed, developed, and flown. Figure 1 shows the conventional single processor or uniprocessor system; the processor (P) is connected to the memory (M) and to the I/O controller (I/O), which may also be connected directly to the memory. The connections of the I/O controller to I/O devices, and the I/O devices themselves, are not shown in the figure.

Nearly all spaceborne computers which have been flown to date have been uniprocessor systems, either with or without the direct access channel between I/O and memory. These include the

Figure 1.-Uniprocessor configuration.

computers on the Gemini spacecraft, the Apollo command and lunar modules, and the Atlas, Minuteman, Titan, Agena, Centaur, and Saturn launch vehicles.

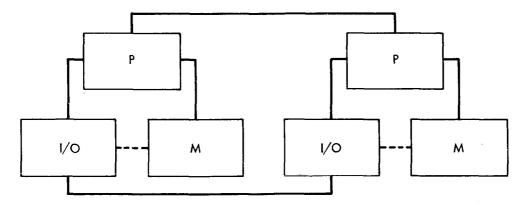

A multicomputer system is shown in figure 2. The processors and memories are not necessarily identical since they are generally assigned different tasks to perform. This configuration is distinguished from a multiprocessor system in that the processors do not share memory. They may communicate directly or via a channel-to-channel adapter which makes each computer look like an I/O device to the other. The two systems may also share I/O devices, such as disk storage. The multicomputer configuration has been used in numerous ground based applications, such as the IBM direct-coupled 7094/7044, and in airborne systems, such as the F-111 Mark II Avionics System (ref. 31). During the latter phase of the X-15 program, a multicomputer system was flown on the No. 3 vehicle. A second computer was added to perform energy management calculations; it communicated with the Alert computer through a special I/O adapter. In the AGC design, provision was originally made for direct communication between the command module and lunar module guidance computers; however, this was never implemented. The Hamilton Standard Modular Flight Computer (ref. 32) is a breadboard multicomputer configuration which was originally designed for the Advanced Kickstage booster.

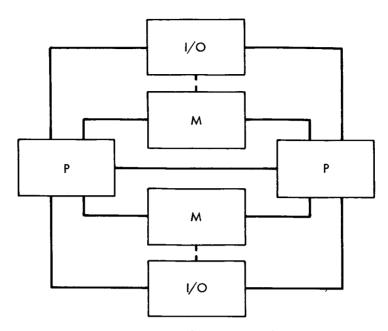

The general architecture for a symmetrical multiprocessor configuration is shown in figure 3. The distinguishing characteristic of the multiprocessor organization is the equal sharing of memory

Figure 2.-Multicomputer configuration.

Figure 3.-Symmetrical processor configuration.

and I/O by each processor. Although the processors in this organization are often alike, they need not be. When they are, the operating system software usually treats them interchangeably, and tasks may be assigned to any available processor when they become ready for execution.

Multiprocessors have not as yet been flown in space vehicles although they have been used in ground-based and airborne installations (e.g., Control Data 6600 and 7600, UNIVAC 1108 and AN/UYK-7, IBM System 360/Model 65 Multiprocessor, and System/4 Pi VS/ANEW Multiprocessor). However, several multiprocessor configurations are in the design or development stages for spaceborne applications. These include the NASA Manned Spacecraft Center (MSC) Experimental Aerospace Multiprocessor—EXAM (refs. 33 to 35), the Massachusetts Institute of Technology (MIT) Instrumentation Laboratory Advanced Control, Guidance and Navigation Computer (refs. 28, 36 to 39), the NASA Marshall Space Flight Center (MSFC) Space Ultrareliable Modular Computer—SUMC (ref. 40), and the NASA/GSFC Parallel Ultra-Low-Power Processor—PULPP (ref. 27).

A survey of actual and proposed multiprocessor computer systems, multiprocessor theory, and problems related to the proposed space station and space base data management systems is contained in reference 30. Reference 41 describes an earlier study of the use of multiprocessing techniques for deep-space missions. Additional references to multiprocessors can be found in reference 42.

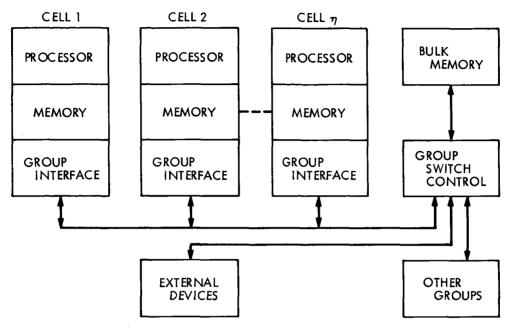

Figure 4 shows a closely related type of computer organization, the distributed processor, in which the logic elements are decentralized on an array basis. Each element has some memory associated with it, and its complexity can vary from the execution of a single instruction to a small computer. The execution of a program in the array can be centrally controlled. References 41, 43, and 44 discuss distributed processor designs which have been proposed for spaceborne applications.

Figure 4.-Distributed processor configuration.

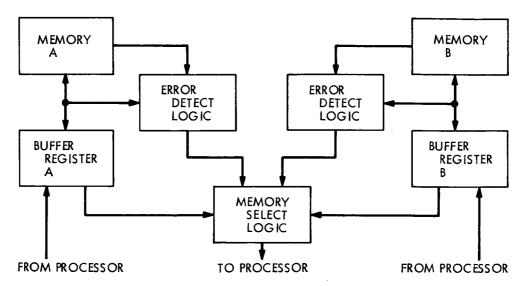

# 2.2.2 Memory

## (1) Organization and Type

Spaceborne computer memories are functionally divided into program memory and variable memory sections. Sometimes the memories are physically separate and may even be constructed of different types of devices. In other cases, program and variable storage is incorporated in the same memory, as is generally the case with ground-based computers. The program memory is often either a fixed or a nondestructive read-out (NDRO) memory which contains the program instructions and constants. The variable memory is almost invariably a random-access read-write memory for temporary (erasable) storage of computational results. The size of the program memory is typically five to twenty times that of the variable memory, although the ratio will generally not exceed about ten.

Fixed or read-only memories usually have their contents manufactured into them; thus, changing the contents of a read-only memory requires physical modification of the device. The possible advantages of fixed memories lie in volume efficiency; retention of program following electrical malfunctions, power loss, or program error (sometimes shared by protected core memories); simplicity of construction and operation; and increased reliability (NDRO memories share some of these characteristics). Moreover, a fixed memory offers assurance that the computer program is identical through all phases of testing and in flight. On the other hand, a "read-only" memory requires that program and data be determined well in advance of use; consequently, it places a limitation on the computer's ability to accommodate changes in mission plan such as may be required periodically in most applications.

An example of a fixed memory is the core-rope program memory used in the Apollo guidance computer (ref. 14). This design achieved high density and reliability at a cost of having to procure new memory modules with about a four-week production cycle for program changes. Despite the fact that verification cycles were at least as long as production cycles, and that no launch post-ponements have yet been caused by this production cycle, the fixed memory has been a controversial issue owing to its potential for causing problems.

Read-write memories are classified as volatile or nonvolatile depending upon whether or not their contents remain intact when power is removed. Read-write memories may also be either destructive readout (DRO) or nondestructive readout. In general, NDRO memories enjoy two advantages over DRO memories. They are less vulnerable to power fluctuations or other interruptions of the read process, since at no time during the reading operation is the information cleared from the memory. Secondly, they can operate at higher speeds since it is not necessary to restore the contents following each read cycle.

As a compromise between reliability and flexibility, some read-write memories are designed so that their contents are electrically alterable only by special equipment; thus, in normal operation they behave as "read-only" devices. The Gemini guidance computer memory was an example. Each 39-bit memory word was divided into three 13-bit syllables; syllables 0 and 1 were multiaperture NDRO core read-write storage, while syllable 2 was "read-only" after being loaded by ground-support equipment.

In addition to their main memories, many newer computers have "scratchpad" memories, which are small, high-speed memories associated with the calculating circuitry. These memories give additional operating speed to a computer and seem particularly desirable for spaceborne computers since only small segments of the variable memory are likely to be used during any one program subroutine. The size of these memories may be determined by the mission requirements for operating speed since there is some penalty in power, weight, and complexity for scratchpad memory words vs the regular, random-access memory of the computer. These memories are especially popular in larger systems because of their increased operating speed and reduced number of instructions (since two-address systems are generally used). However, the saving in program storage is partially offset since the two-address instructions require a greater word length.

## (2) Capacity

One of the most difficult parameters to specify, and one which has been a constant problem in space vehicle applications, is the memory size or capacity. Basically, memory capacity problems have arisen because the number of tasks assigned to the computer increased substantially as the spacecraft program progressed. Also, the complexity of certain tasks has sometimes been underestimated.

One of the earliest computers to experience memory capacity problems was the original Centaur machine (ref. 45). As the major storage medium, this computer used a magnetic drum, which included a timing track, instruction register, accumulator, multiplier/quotient register, as well as a main memory. In the original design (1959/1960), the main memory consisted of 37 tracks of permanent storage and 3 tracks of temporary storage, at 64 words per track. However, this was found to be inadequate, and in the redesign in 1961/1962, seven permanent tracks and one

temporary track were added to the drum. With clever programming, this 3072-word capacity has been adequate to implement G&N tasks, and the Centaur has successfully launched several Surveyor spacecraft to the moon, two Mariner spacecraft to Mars, and an OAO into earth orbit. However, to expand the Centaur's capability for future missions, a new computer was required and is presently in development (ref. 11). The improved Centaur computer will provide not only guidance and navigation, but also flight attitude control, vehicle sequencing, propellant utilization, and telemetry format control.

The Gemini program experience is another example of the problems associated with growing computer memory requirements (ref. 15). These were increased significantly when the ascent guidance mode was added to the computer in May 1962 to provide backup guidance capability for the Titan 2 launch vehicle. Another early addition was the requirement for an orbit navigation mode. These additions, plus numerous small features and improvements to existing programs which required additional memory capacity, occupied all the memory space by January 1963. The programming of the second operational "math" flow in June 1963 revealed that the memory capacity was exceeded by over 700 words, even after significant savings had been achieved by reprogramming. Three solutions were considered for this problem:

- Reduce programming requirements at the expense of accuracy and/or versatility. This approach could have been accomplished by across-the-board reductions in all modes, or by dropping one of the computer modes (rendezvous and orbit navigation were not required for the early spacecraft).

- Provide additional usable memory locations by hard wiring some elementary functions presently programmed. Such an approach would have gained 825 instruction locations.

- Provide an auxiliary tape memory external to the computer under the control of the astronauts. This unit would contain sufficient storage to handle present requirements, as well as any contemplated future requirements.

A combination of the first and third alternatives was eventually adopted. On Spacecraft 2 through 7, the orbit navigation mode was not included. On Spacecraft 8 through 12, an auxiliary tape memory was added to the spacecraft.

The development of the tape memory, begun in mid-1964, was a costly and time-consuming process which could have been avoided if the original design had provided for easy memory expansion. However, when completed, it provided an additional capacity for storage of 85,000 13-bit words and permitted a high degree of computer flexibility, as evidenced by the inclusion of nine operational computer modes in the last four spacecraft. In addition to alleviating the memory capacity problem, the auxiliary tape memory provided a memory reload capability for use in the event of an inflight memory alteration, such as occurred during the flight of Spacecraft 4.

A similar experience was encountered during the design of the Apollo guidance computer. Table 3 presents a chronological summary of the AGC memory growth from 1961 to 1965. Throughout much of this history, at least prior to 1964, the memory growth was due more to demonstration of the feasibility of a larger memory than to well-defined system requirements.

TABLE 3.-History of Apollo Guidance Computer Memory Growth

| Date | Variable   | Program | Remarks                                                                                                                                                              |

|------|------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1961 | 512        | 4K      | Paper design based on inertial navigation requirements. Only executive and similar tasks programmed.                                                                 |

| 1962 | 1K         | 12K     | Original mechanical design.                                                                                                                                          |

| 1963 | 1K         | 24K     | Block I design. Guidance system programming started.                                                                                                                 |

| 1964 | 2K         | 36K     | Block II design. Redefinition of functional requirements; change to digital autopilot, improved crew displays and controls, and others. Greater speed also required. |

| 1965 | 2 <b>K</b> | 36K     | Mission programming started.                                                                                                                                         |

The Block I Apollo G&N system was conceived about 1962 to furnish position, velocity, and attitude control of the command module using inertial and optical sensor inputs. Outputs were transmitted to an analog S&C system responsible for the direct excitation of control actuators. To meet these requirements, plus a variety of less challenging ones such as telemetry, the Block I AGC design provided a 1K coincident-current core variable memory, a 12K core-rope fixed program memory, eleven instructions, and a 12-µsec memory cycle.

The Block I computer was used in support of three suborbital unmanned missions and was programmed, but not used, for a manned orbital mission. As these programs were being prepared, it was concluded that more memory and speed resources would be required for the lunar missions.

In 1964, the Apollo G&N system was revised to conform with the lunar module and revised command module designs. Design decisions made at that time are of some interest because of the knowledge gained during the Block I design and checkout. The Block II computer requirements were larger than those of Block I for several reasons. One reason was the decision to incorporate the autopilot function, which was formerly in the analog stabilization and control system, into the AGC. Another was the evolution of the computer's display into a major mission sequencing device. In addition, several new interfaces were defined whereby the computer could deliver data to spacecraft displays and receive data from spacecraft manual controls.

A 50% increase in the fixed memory capacity and a doubling of the variable memory capacity were made without any major impact on the associated circuit techniques. At this stage it was felt that all functions could be performed within these new memory capacities. Not surprisingly, the increased memory resources were committed before the programming was complete, and a large effort was expended to maximize the utilization of the available memory.

A final example of memory capacity growth is the Abort Electronics Assembly computer which provides backup guidance for the Apollo lunar module (ref. 16). In the original design, based on request for proposal (RFP) requirements, 500 18-bit words of memory were determined to be adequate for the required computations. At that time, there were no requirements for variable mission changes since the Abort Guidance System was essentially an attitude reference system. However, due to major increases in system functional requirements, the memory grew to 2,000 words, including 500 words of erasable storage. Additional studies soon revealed that the original

guidance scheme was not adequate, and that explicit guidance was required to provide rendez-vous via parking orbit or direct ascent. To implement the revised guidance system functions, it became necessary to provide an I/O unit for use by the crew in communicating with the computer, and to increase the size of the memory to a total of 4,096 words, with 2,048 words of hardwired "read-only" memory and 2,048 words of read-write data memory. A significant by-product of these memory and I/O changes was the required redesign of the AEA power supply.

# 2.2.3 Logic Design

#### (1.) Word Length

Word lengths of aerospace computers have varied from 9 to 52 bits with most being around 24 bits. The major considerations have to do with precision of calculations (with due attention to roundoff and truncation errors), addressing formats, input/output precision, economy of size, and programming convenience. The size, speed, and power consumption of the memory all increase with longer memory words. Shorter word lengths impose limitations on the operand addressing and precision of data representation.