MSFC No. 111-5-510-9 IBM No. 66-966-0001

## TECHNICAL MANUAL

. . . \*

# SATURN IB/V INSTRUMENT UNIT SWITCH SELECTOR, MODEL II

Prepared under Contract

NAS 8-14000

by

International Business Machines Corporation

Federal Systems Division

Huntsville, Alabama

1 February 1966

Technical Library, Bellcomm, Inc.

## LIST OF EFFECTIVE PAGES

#### INSERT LATEST CHANGED PAGES, DESTROY SUPERSEDED PAGES

\* \* , ,

5

NOTE: The portion of the text affected by the changes is indicated by a vertical line in the outer margins of the page.

·....

| Page                  |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Issue    |

|-----------------------|---|---|---|---|---|----|---|---|---|---|----|---|---|----------|----------|

| Title · · ·           |   | • | • | • | • |    | • | • | • | • |    |   | • | •        | Original |

| Α                     | • | • | • | ٠ | • |    | • | • | ٠ | • |    | • | • | ٠        | Original |

| i thru iii .          | • |   |   | ٠ |   |    | ٠ | ٠ | • | • | •  | • | • | •        | Original |

| iv Blank .            |   |   |   |   |   |    |   | • |   |   |    |   |   |          | Original |

| 1 thru 9 .            |   |   |   |   |   |    |   |   |   |   | ÷  |   |   |          | Original |

| 10 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 11 thru 13            |   |   |   | 2 |   |    |   |   | 2 | 2 |    |   |   |          | Original |

| 14 Blank .            |   |   |   |   |   |    |   |   |   | 2 |    |   |   |          | Original |

| 15 thru 31            |   |   |   |   | ļ | ì  |   |   |   |   |    |   |   |          | Original |

| 32 Blank .            |   | ÷ |   |   |   | ŝ  |   | Ĵ |   |   | ĵ, | ĉ | Ĵ | <u> </u> | Original |

| 33                    | ÷ | ÷ |   |   | ÷ | Ĵ  |   | Ċ |   |   | Ĵ  | 2 | Ĵ | č        | Original |

| 34 Blank .            |   |   |   |   |   |    |   |   |   |   | Ĵ  | 1 |   |          | Original |

|                       |   | · | • |   |   |    | • |   | • |   |    |   | • | •        |          |

| 35 thru 39            | • | • | • | • | • | •  | • | • | • | • | •  | • |   | •        | Original |

| 40 Blank .            | • | • | • | • | • |    |   |   | ٠ | • | •  | • | • | •        | Original |

| 41                    |   | ٠ | • | • | • | ·  | • | ٠ | • | • |    | • | • |          | Original |

| 42 Blank .            | • | • | • | • | • | •  |   | • | • |   | •  |   | • | •        | Original |

| 43                    | • |   |   | ٠ |   |    | • | ٠ |   |   |    |   | • |          | Original |

| 44 Blank .            |   |   | • |   |   |    |   | • | • |   |    | • |   | •        | Original |

| 45                    |   | • |   |   |   |    |   |   | • |   |    |   |   | •        | Original |

| 46 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   | •        | Original |

| 47                    |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 48 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 49                    |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 50 Blank .            |   |   |   |   | 2 |    |   |   |   | 2 |    |   |   |          | Original |

| 51                    |   |   |   | 2 |   |    |   |   |   |   | 2  | 2 |   |          | Original |

| 52 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 53                    | ÷ |   | Ĵ | ÷ | Ĵ | ÷  |   |   |   | Ĵ | Ĵ  | Ĵ |   |          | Original |

| 54 Blank .            |   |   |   |   |   |    |   |   | : |   |    |   |   | •        | Original |

| 55                    |   |   |   |   |   |    |   |   |   |   | ÷  |   | ÷ |          | Original |

| 56 Blank .            |   |   |   |   | ÷ | ÷  |   |   |   |   | Ĵ  | ÷ | ÷ |          | Original |

|                       |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 57<br>58 Blank .      |   | • |   |   |   | •  |   |   |   |   |    |   | • |          | Original |

| and an entropy of the | • |   | • |   | • | •  |   | • |   |   | ÷  |   | • |          | 0        |

| 59                    |   | ٠ |   |   | • |    |   | • |   |   |    |   |   | •        | Original |

| 60 Blank .            | • | • | • | • | • | •  | • | • | • | • | •  | • | • | •        | Original |

| 61                    | • | ٠ |   | • | • | ·  | • | • | • | • | ٠  | • | • | •        | Original |

| 62 Blank .            |   | • |   |   | • |    |   | • |   |   | •  |   |   |          | Original |

| 63                    | • | • |   | × |   | •  |   |   |   |   |    |   |   | ×        | Original |

| 64 Blank .            |   |   |   |   |   |    |   |   |   |   | •  | × |   |          | Original |

| 65                    |   |   | • |   |   |    |   | • | • |   |    | • |   | •        | Original |

| 66 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 67                    |   |   |   |   |   |    |   |   |   |   |    |   |   | •        | Original |

| 68 Blank .            |   |   | • |   |   | ÷  |   |   | • |   |    |   | • | •        | Original |

| 69                    |   | • |   |   |   |    |   | • |   |   |    |   |   |          | Original |

| 70 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 71                    |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 72 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 73                    |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 74 Blank .            |   |   |   |   |   |    |   |   |   |   |    |   |   |          | Original |

| 75                    |   |   |   |   |   | 2  |   |   |   | ì |    | 2 |   |          | Original |

| 76 Blank .            |   |   |   |   | 2 | ÷  |   |   |   |   | ŝ. | ŝ |   |          | Original |

| 77                    |   | 0 |   |   | ŝ |    |   | Ĵ |   |   |    |   | Ĵ | 0        | Original |

| 78 Blank .            |   |   | ÷ | 1 | ċ | ÷. | ŝ | ÷ |   |   |    | Ċ |   | Ċ        | Original |

| 79                    | ÷ | ÷ |   | ċ | į |    | ÷ |   | • | ÷ | Ĵ  | • |   | •        | Original |

| 80 Blank .            |   | • | • |   | ċ |    |   |   |   |   | Ĵ  | • |   | •        | Original |

|                       |   | • | • | • |   | •  | • | • |   |   | •  | • | • |          |          |

| 81 82 Blank .         |   | ٠ | ٠ |   | • | ·  |   | • | • |   | •  | • |   | •        | Original |

|                       | • |   | • | , |   | •  |   |   | • | • | •  | • | • | ×        | Original |

| 83 thru 85            |   | • | • | • |   | •  | • | ٠ | • | • |    | • | • | ٠        | Original |

| 86 Blank .            | • | • | • | • | • | •  | ٠ | • | ٠ | • | ÷  | • | • | •        | Original |

| 87                    | • | • | • | • | ٠ | •  | ٠ | • | ٠ | • |    | • | • | •        | Original |

|                       |   |   |   |   |   |    |   |   |   |   |    |   |   |          |          |

\* The asterisk indicates pages changed, added, or deleted by the current change.

### COMMENT SHEET

Your comments will help improve this publication. The following comment sheets are provided for your comments on the usefulness and readability of this publication. Also, suggest additions and deletions, and indicate any specific errors or omissions. Please forward the completed comment sheet to the following address:

> Manager Department 966 IBM Corporation Huntsville Facility Space Systems Center Huntsville, Alabama

| Manual Title  |             |

|---------------|-------------|

| Manual Number | Change Date |

| Comments      |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

| Name          | -           |

| Address       | -           |

|               | -           |

|               | -           |

| Manual Title  |             |

|---------------|-------------|

| Manual Number | Change Date |

| Comments      |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

|               |             |

| Name          | -           |

| Address       | -           |

|               | -           |

|               | -           |

## LIST OF RELATED DOCUMENTS

The manuals listed below have been published under NASA contracts as source and reference information on IU systems and/or components.

| Title                                                                | Num                   | ber         | Published        | Changed         |  |  |  |

|----------------------------------------------------------------------|-----------------------|-------------|------------------|-----------------|--|--|--|

| Title                                                                | IBM                   | MSFC        | Date             | Changed<br>Date |  |  |  |

| Saturn IB/V Instrument Unit<br>Structure Repair Manual               | 65-966-0011H          | III-5-510-1 | 1 September 1965 |                 |  |  |  |

| Auxiliary Power Distributors                                         | 65-966- <b>0013</b> H | III-5-510-2 | 1 October 1965   |                 |  |  |  |

| Power Distributor                                                    | 65-966-0014H          | III-5-510-3 | 1 October 1965   |                 |  |  |  |

| Emergency Detection System<br>Distributor                            | 65-966-0015H          | III-5-510-4 | 1 October 1965   |                 |  |  |  |

| Control Distributor                                                  | 65-966-0016H          | III-5-510-5 | 1 October 1965   |                 |  |  |  |

| Measuring Distributors                                               | 65-966-0017H          | III-5-510-6 | 1 October 1965   |                 |  |  |  |

| 56 Volt Power Supply                                                 | 65-966-0018H          | III-5-510-7 | 1 October 1965   | 1 January 1966  |  |  |  |

| 5 Volt Measuring Voltage Supply                                      | 65-966-0019H          | III-5-510-8 | 1 October 1965   |                 |  |  |  |

| Saturn IB/V Instrument Unit<br>Instrumentation System<br>Description | 65-966-0021H          | III-5-509-1 | 1 November 1965  | 1 January 1966  |  |  |  |

| Switch Selector, Model II                                            | 66-966-0001           | III-5-510-9 | 1 February 1966  |                 |  |  |  |

#### LIST OF SPECIFICATIONS AND PROCEDURES FOR SWITCH SELECTOR, MODEL II

| Title                         | Number             |

|-------------------------------|--------------------|

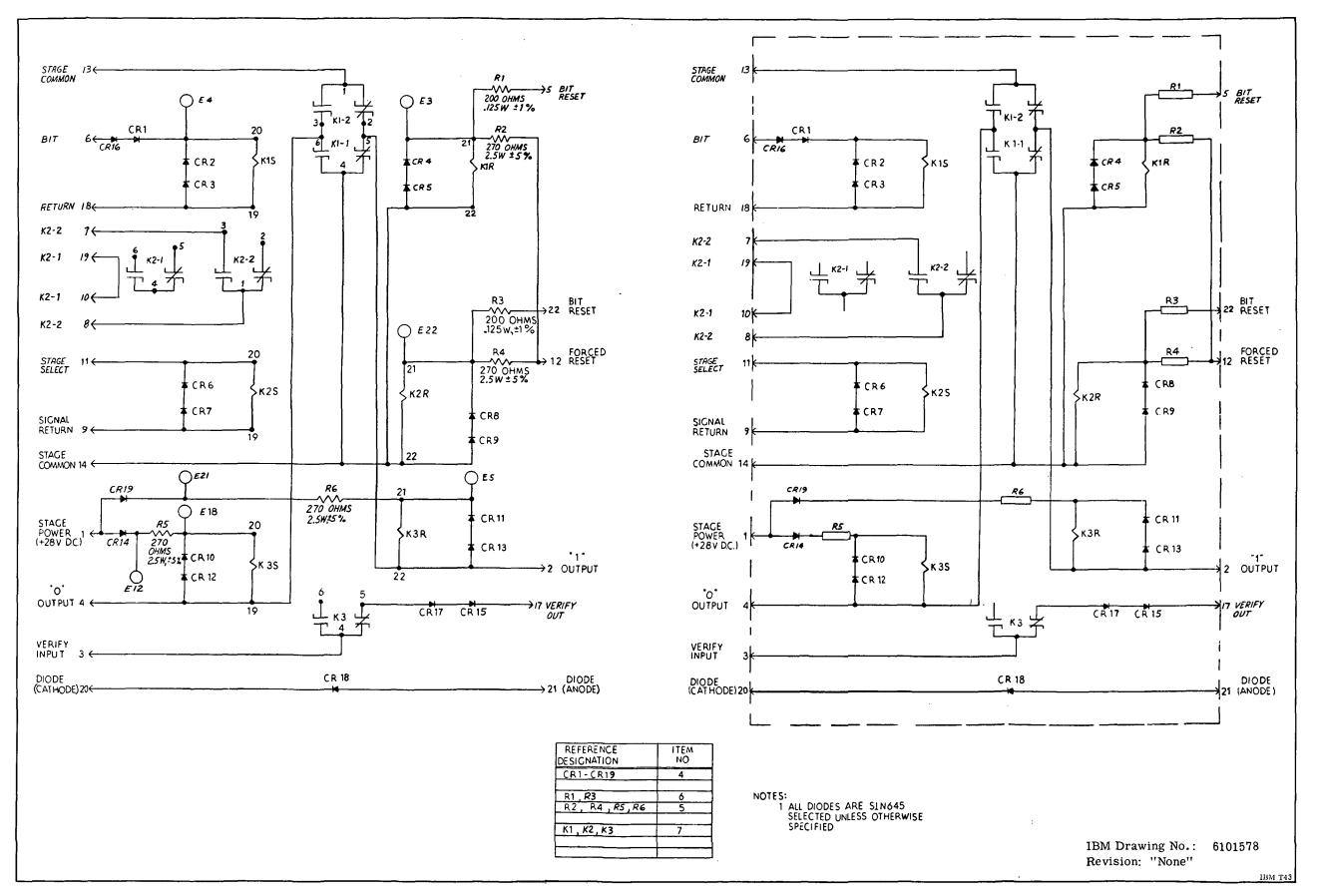

| Schematic                     | 6101534            |

| Switch Selector (Top Drawing) | 6101400 (50M67864) |

| Design Specification          | 6009026            |

| Acceptance Test Plan          | 373-66644-05       |

| Qualification Test Plan       | 373-66644-06       |

| Unit Outline                  | 6101487            |

## CONTENTS

| Section                                                                                                                                                                                                                  | Page Section |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| ILLUSTRATIONS                                                                                                                                                                                                            | ii           |

| TABLES                                                                                                                                                                                                                   | iii          |

| I INTRODUCTION AND DES                                                                                                                                                                                                   | CRIPTION 1   |

| <ul> <li>1-1 Introduction</li> <li>1-2 Description</li> <li>1-3 Mechanical Design</li> <li>1-4 Electrical Character</li> <li>1-5 Dimensions and Weig</li> <li>II PRINCIPLES OF OPERAT</li> </ul>                         |              |

| <ul> <li>2-1 General Operation</li> <li>2-2 System Description</li> <li>2-3 Component Descripti</li> <li>2-4 Detailed Operation</li> <li>2-5 Stage Select</li> <li>2-6 Input Relays</li> <li>2-7 Verification</li> </ul> |              |

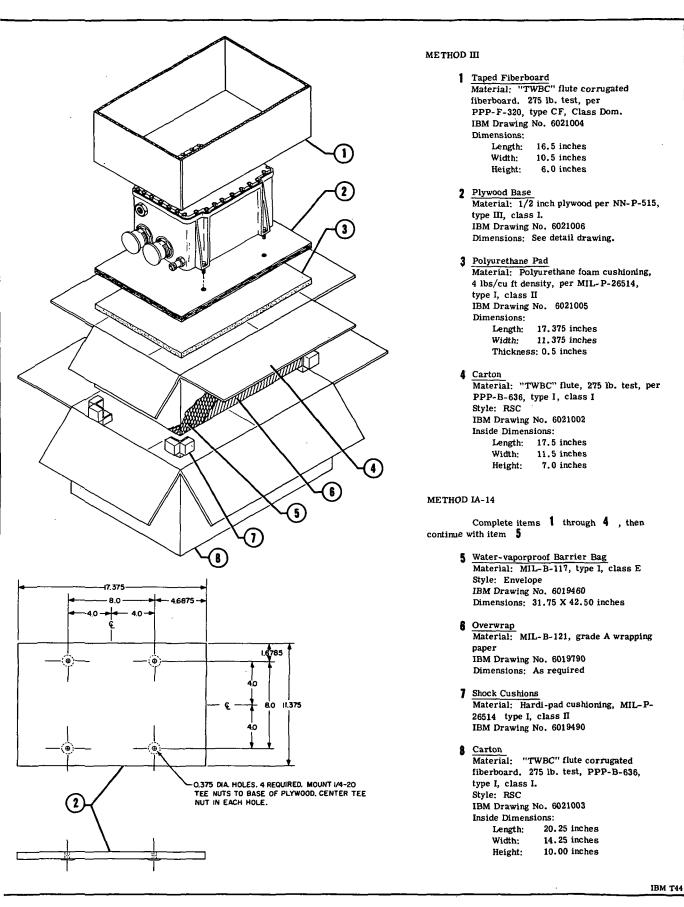

2-12 Output Matrix and Telemetry . . . 27 2-14 Circuit Description . . . . . . . 29 PREPARATION FOR USE AND SHIPMENT 83 3-1 Preparation for Use . . . . . . . . . 83 3-2 Preparation for Shipment . . . . 83 Packaging . . . . . . . . . . . . . . . . . 83 3-3 PREVENTIVE MAINTENANCE AND REPAIR 87 4-1 Preventive Maintenance . . . . . 87

Page

### ILLUSTRATIONS

Page

| 1-1   | Switch Selector, Model II          |   |   |   |    |  |

|-------|------------------------------------|---|---|---|----|--|

|       | (Three-Quarter View)               | • | • | • | 1  |  |

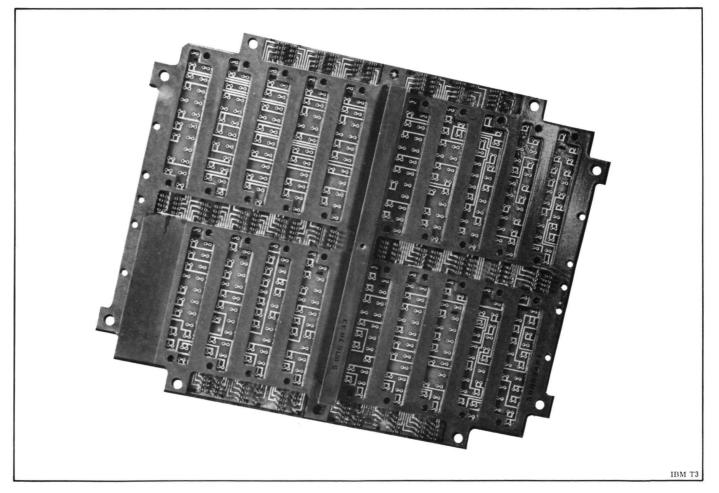

| 1-2   | Switch Selector Circuit Module     | • | • |   | 2  |  |

| 1-3   | Switch Selector Panel Assembly .   | • | • |   | 3  |  |

| 1-4   | Switch Selector Electrical         |   |   |   |    |  |

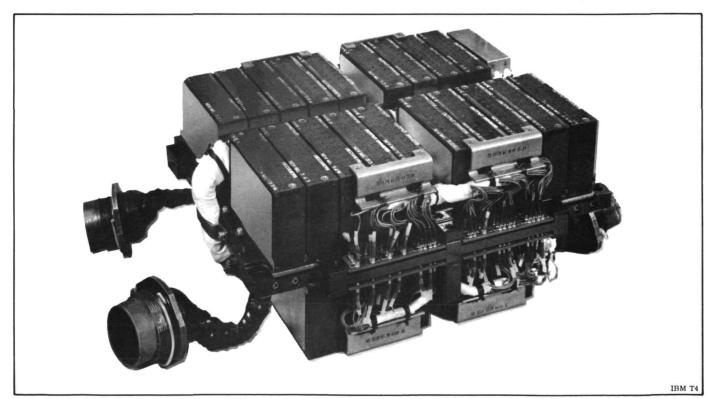

|       | Assembly                           | • | • | • | 4  |  |

| 1-5   | Switch Selector, Model II          |   |   |   |    |  |

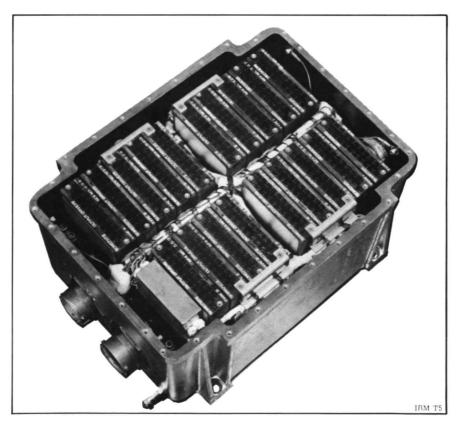

|       | (Internal View)                    | • | • |   | 5  |  |

| 2-1   | Saturn V Switch Selector           |   |   |   |    |  |

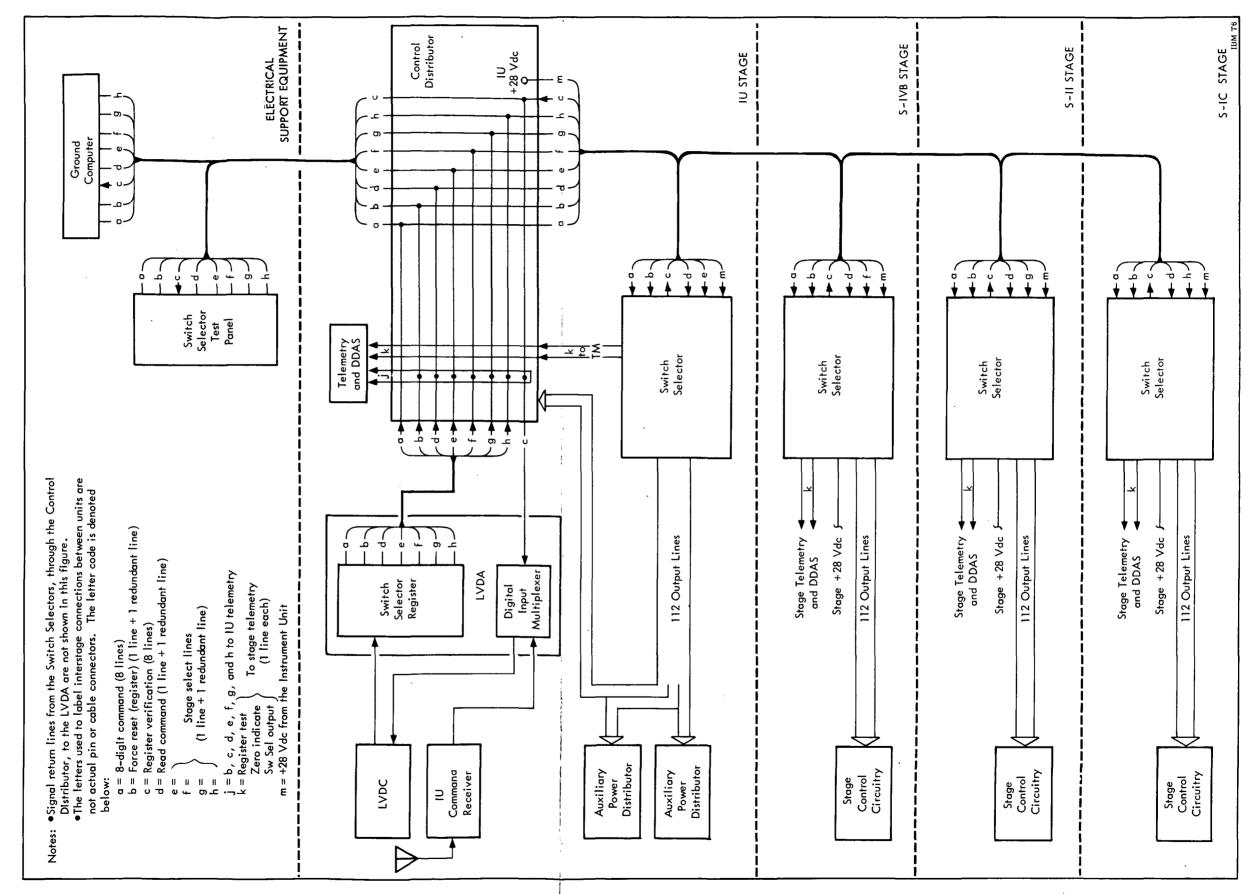

|       | Configurations                     | • | • | • | 9  |  |

| 2-2   | LVDC - Switch Selector             |   |   |   |    |  |

|       | Interconnection Diagram            | • | • | • | 11 |  |

| 2-3   | Switch Selector Register           |   |   |   |    |  |

|       | Word Format                        | • | • | • | 12 |  |

| 2-4   | Switch Selector (Model II)         |   |   |   |    |  |

|       | Simplified Diagram • • • • • • • • | • | • | • | 13 |  |

| 2-5   | Automatic Reset Circuitry,         |   |   |   |    |  |

|       | Simplified Diagram                 | • | • | • | 15 |  |

| 2-6   | Typical Switch Selector            |   |   |   |    |  |

|       | Timing Diagram                     | • |   | • | 17 |  |

| 2 - 7 | Stage Select Relay Configuration · | • | • | • | 18 |  |

| 2-8   | Input and Verify Relay Circuitry . | • |   |   | 19 |  |

Title

| Numbe | er Title Page                                |   |

|-------|----------------------------------------------|---|

| 2-9   | Read Command Relay                           |   |

|       | Configuration 21                             |   |

| 2-10  | Automatic Reset Circuitry 22                 |   |

| 2-11  | AG Signal Generation Logic 24                |   |

| 2-12  | Portion of Row NOT Signal                    |   |

|       | Generation Logic                             |   |

| 2-13  | Portion of Column Signal                     |   |

|       | Generation Logic                             |   |

| 2-14  | Zero Indicate Logic                          |   |

| 2-15  | Register Test Logic                          |   |

| 2-16  | Switch Selector Electrical                   |   |

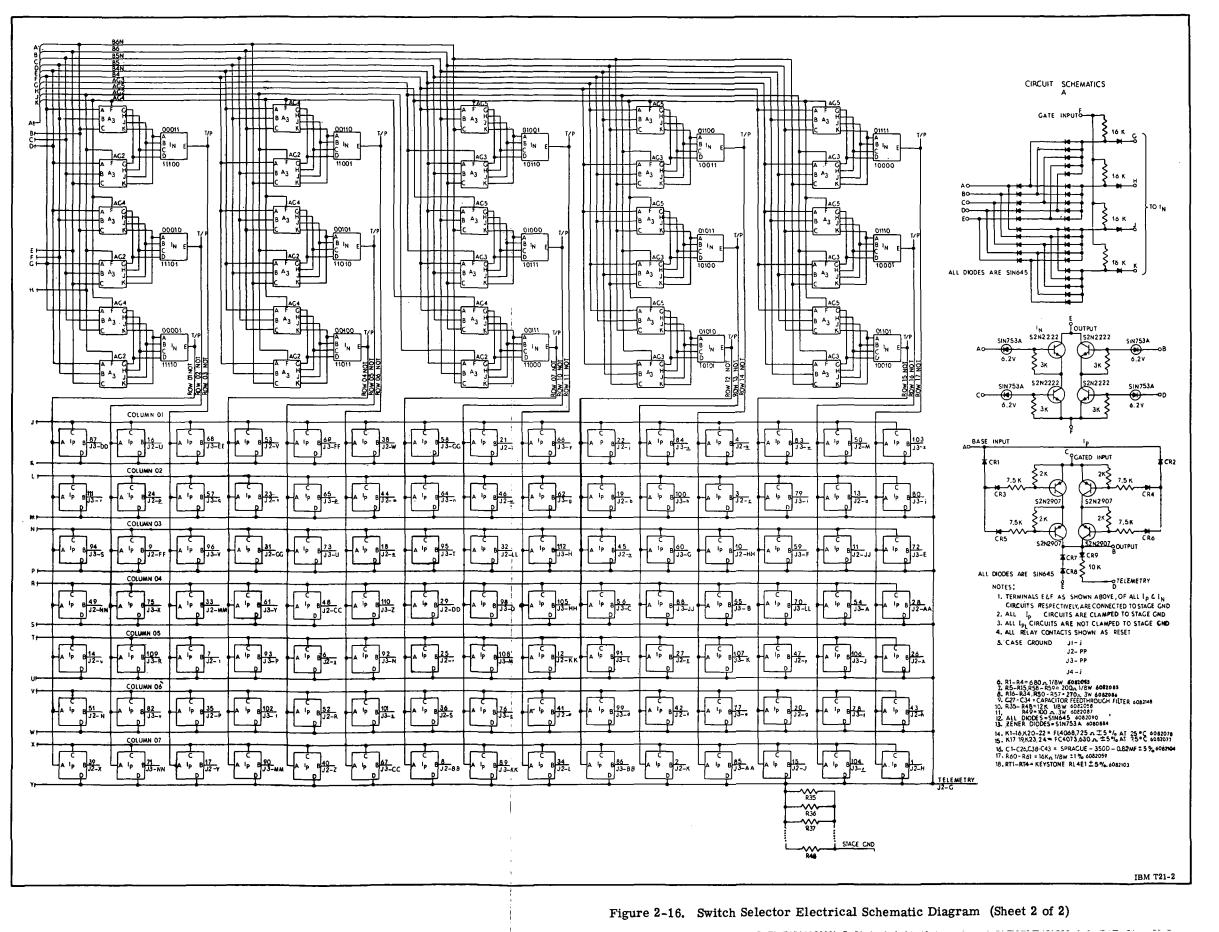

|       | Schematic Diagram (Sheet 1 of 2) 31          |   |

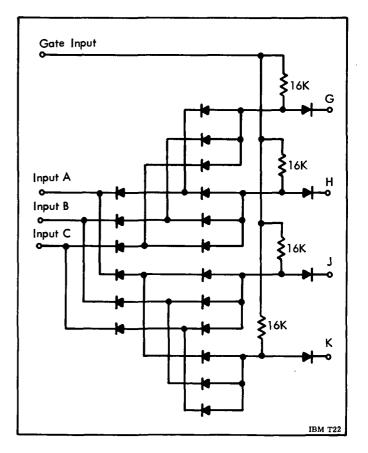

| 2-17  | Four Input AND Circuit (A <sub>4</sub> ) 35  |   |

| 2-18  | PNP Inverter Schematic Diagram 36            |   |

| 2-19  | NPN Inverter Schematic Diagram 36            | į |

| 2-20  | Latching Relay Schematic Diagram 37          |   |

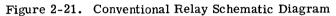

| 2-21  | Conventional Relay Schematic                 |   |

|       | Diagram • • • • • • • • • • • • • • • • • 37 |   |

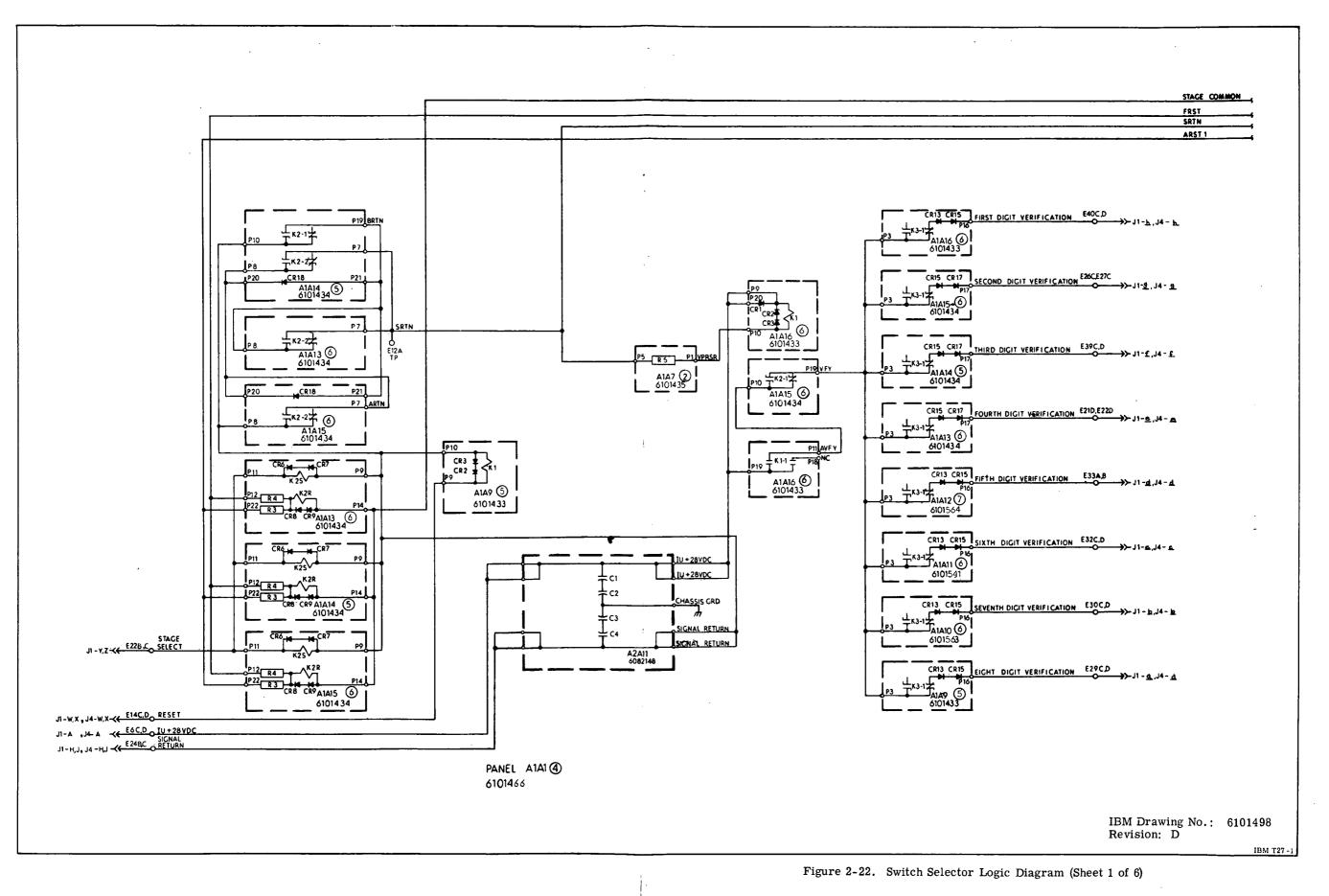

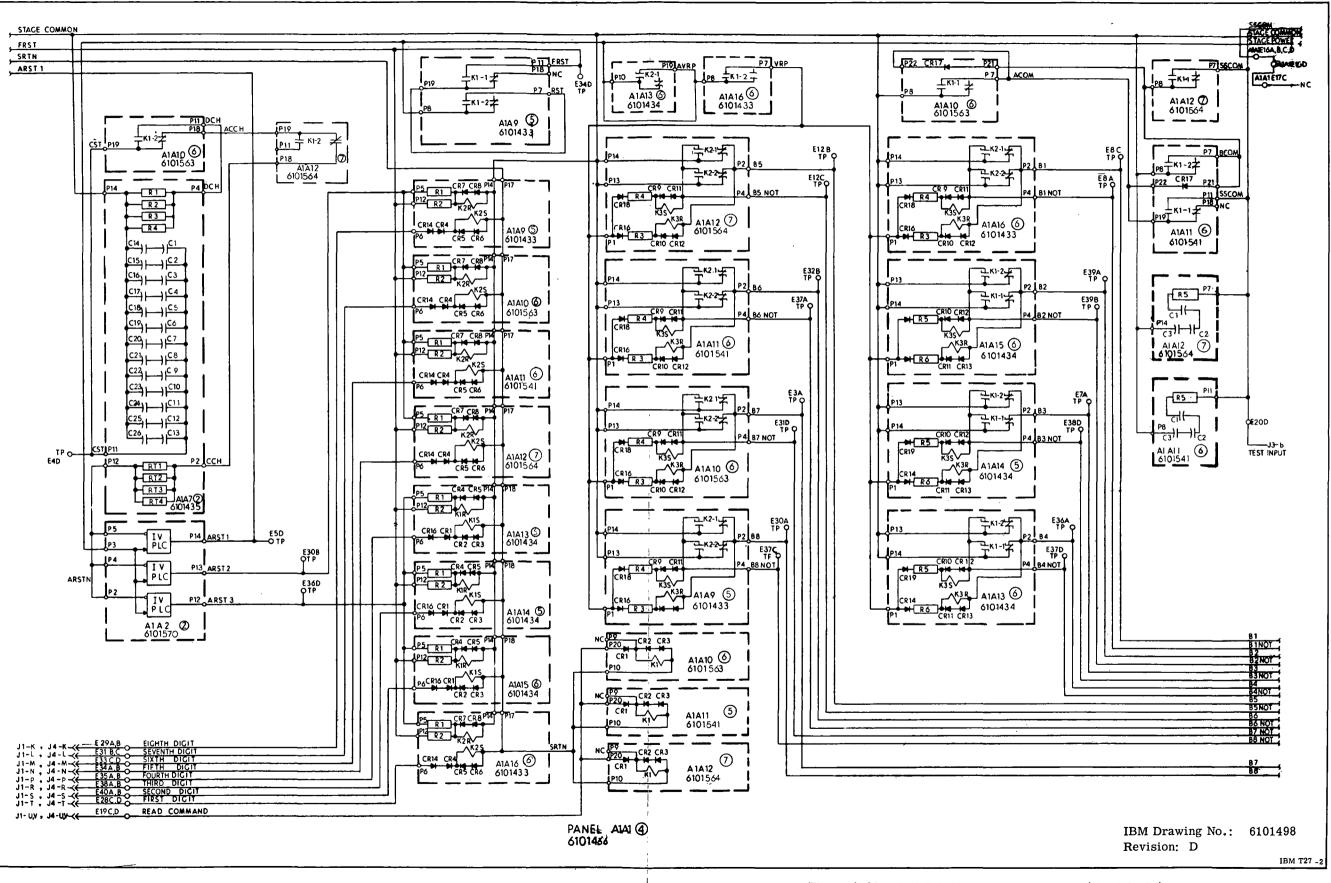

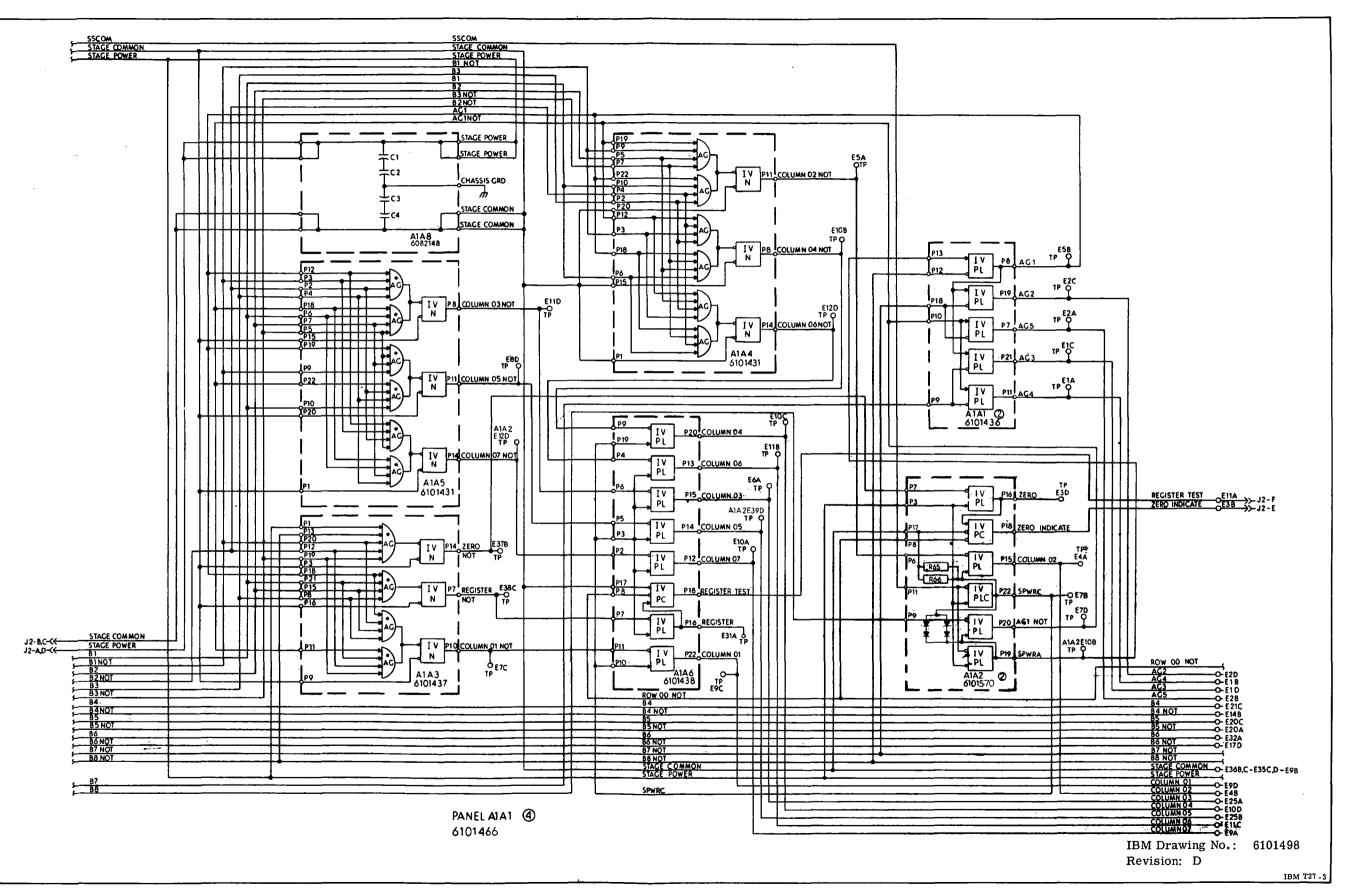

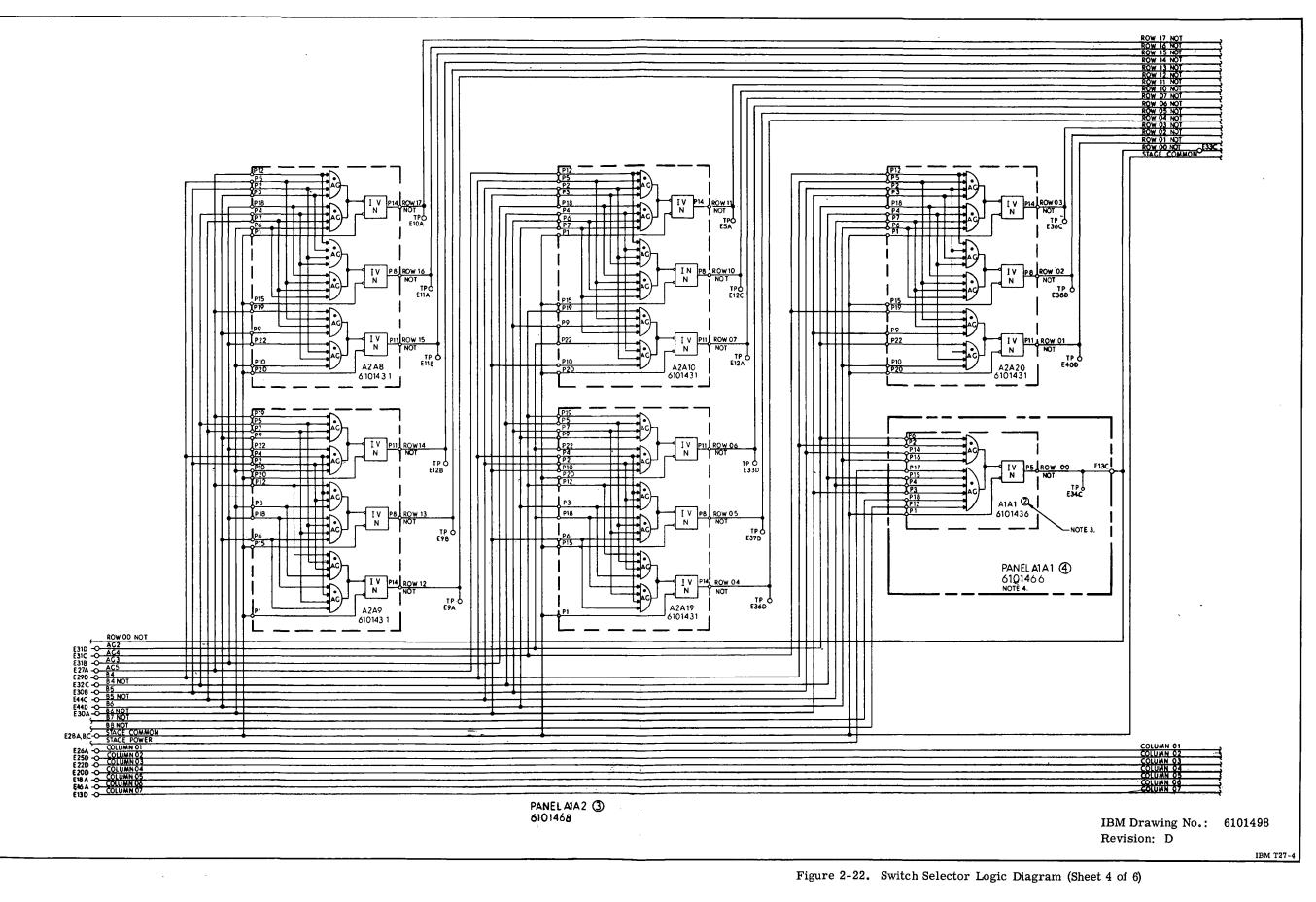

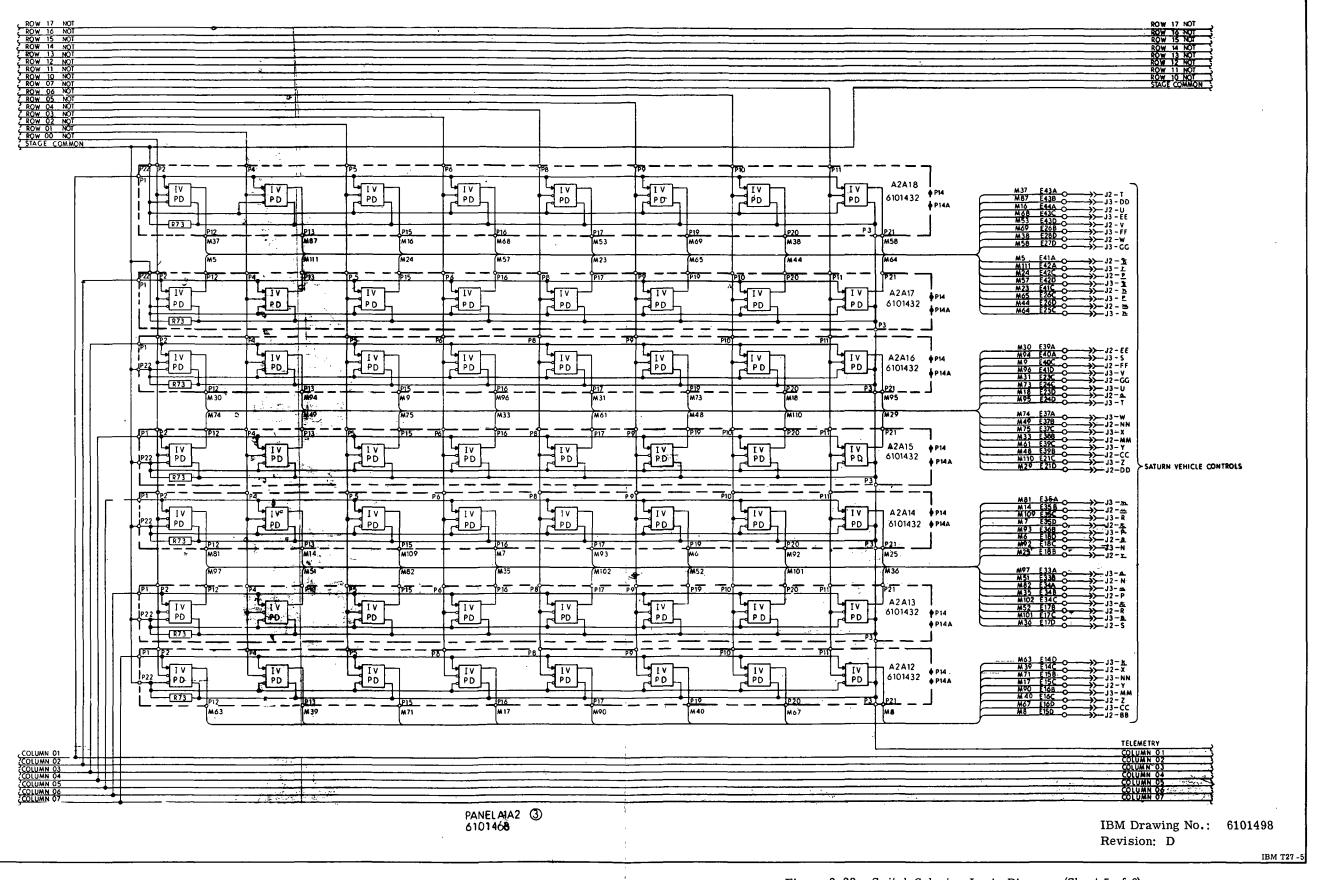

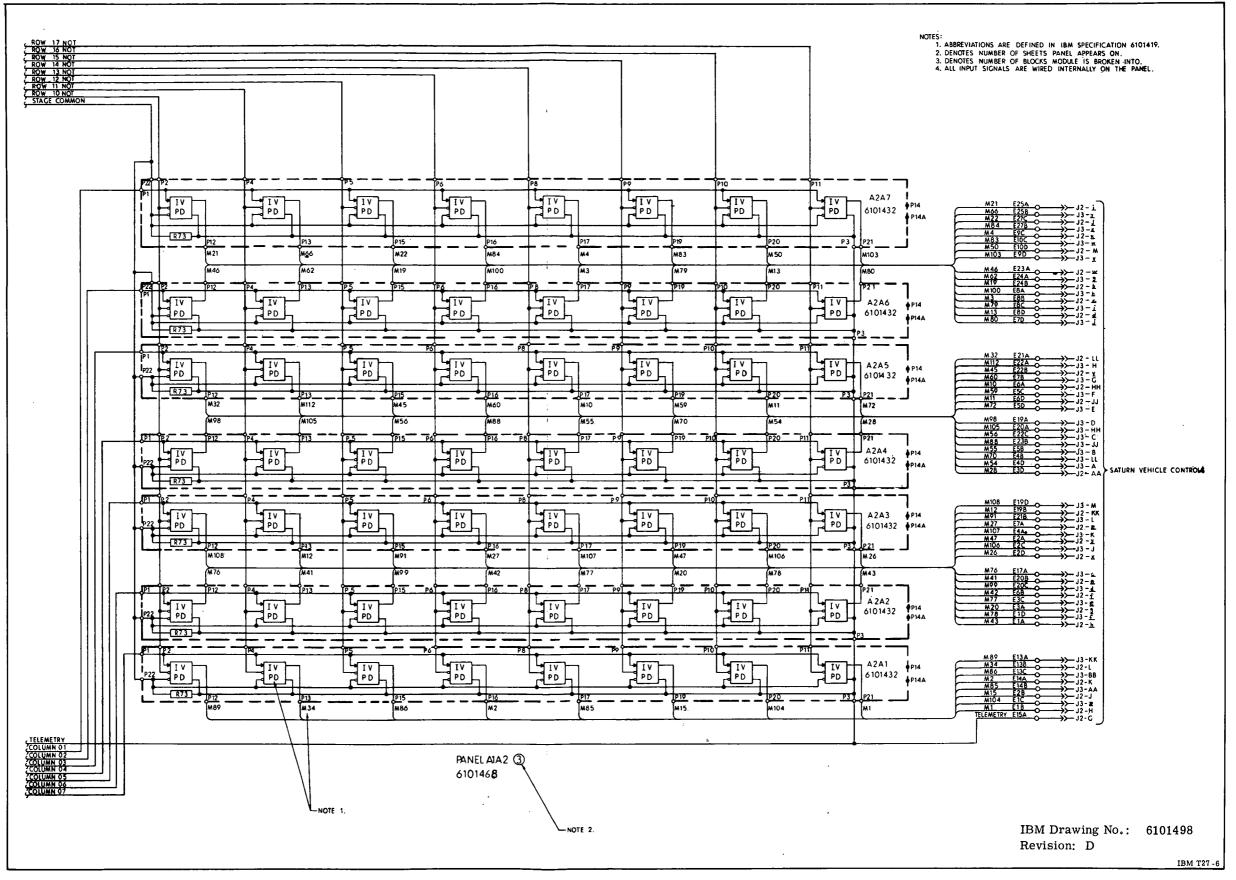

| 2-22  | Switch Selector Logic Diagram                |   |

|       | (Sheet 1 of 6)                               |   |

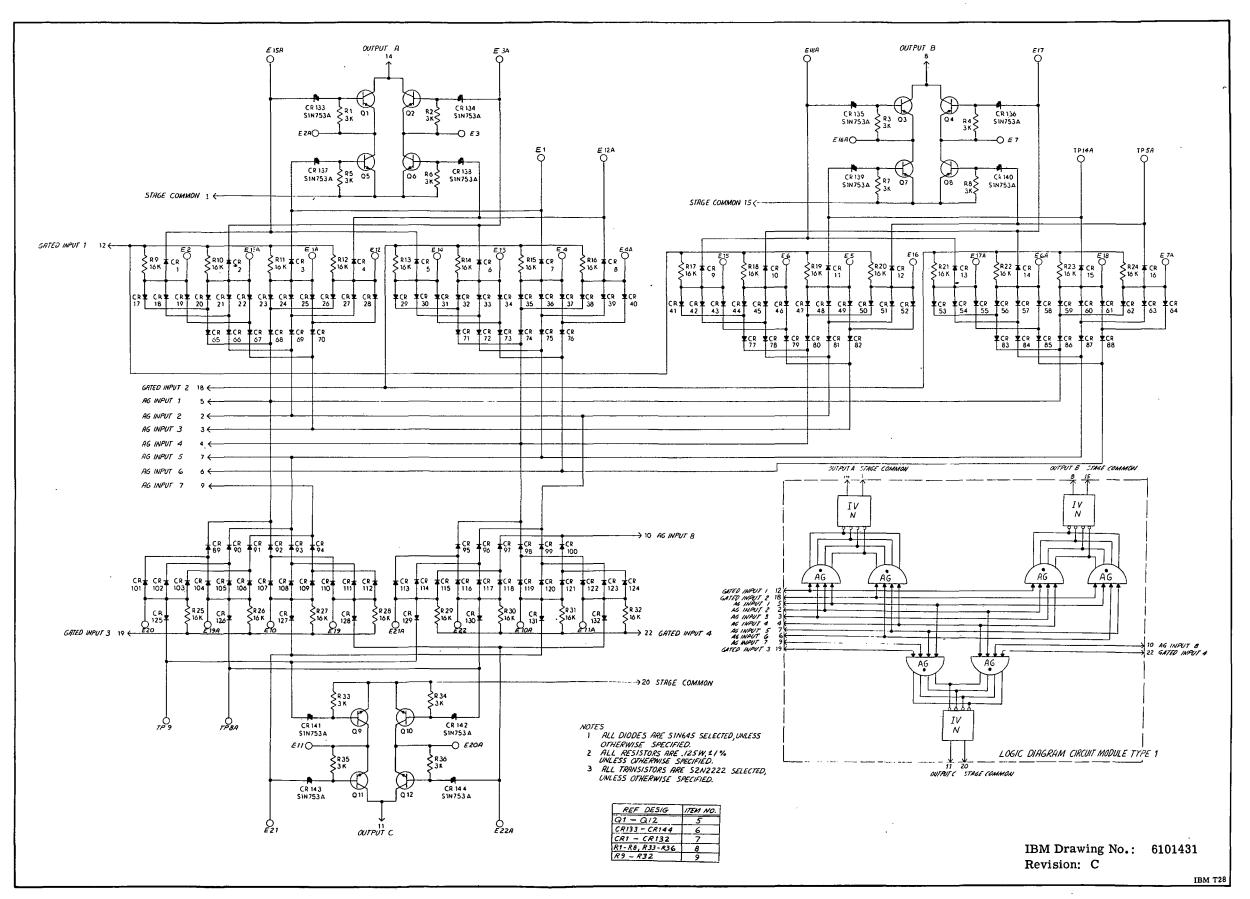

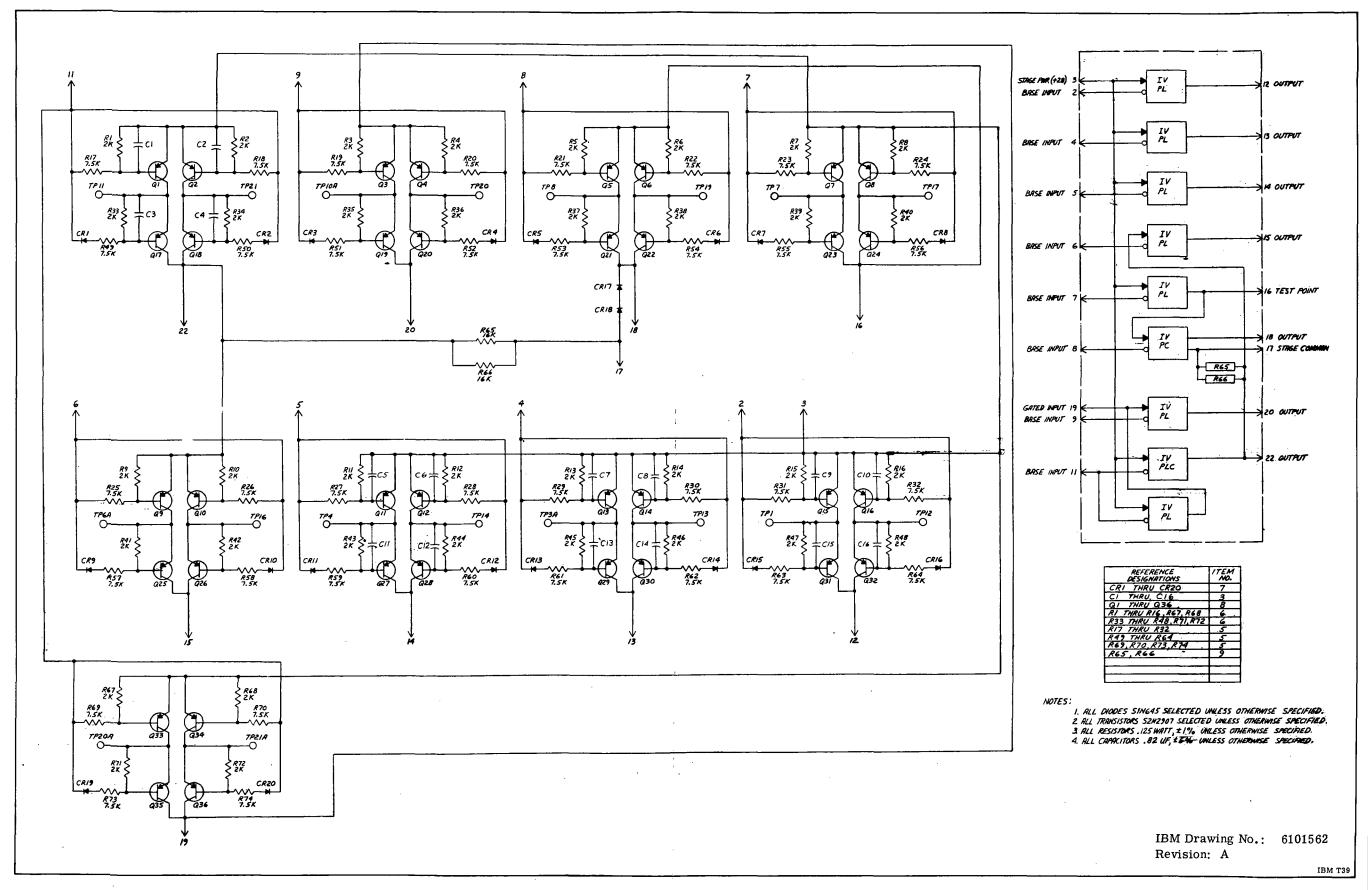

| 2-23  | Electrical Schematic, Circuit                |   |

|       | Module Type 1, Decode 51                     |   |

|       |                                              |   |

Number

## CONTENTS (Cont)

| Number | r Title Page                    |  |

|--------|---------------------------------|--|

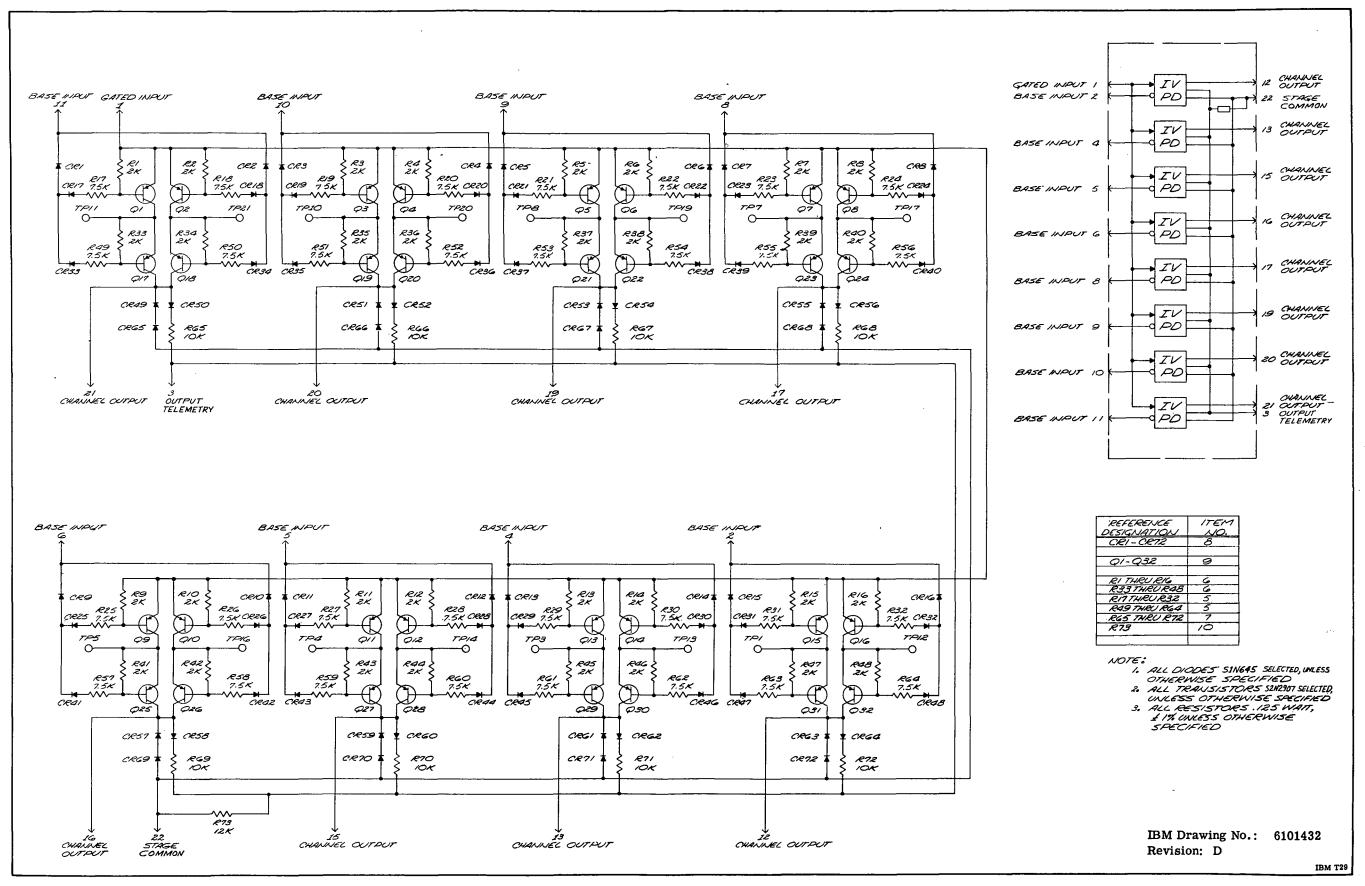

| 2-24   | Electrical Schematic, Circuit   |  |

|        | Module Type 2, Output Driver 53 |  |

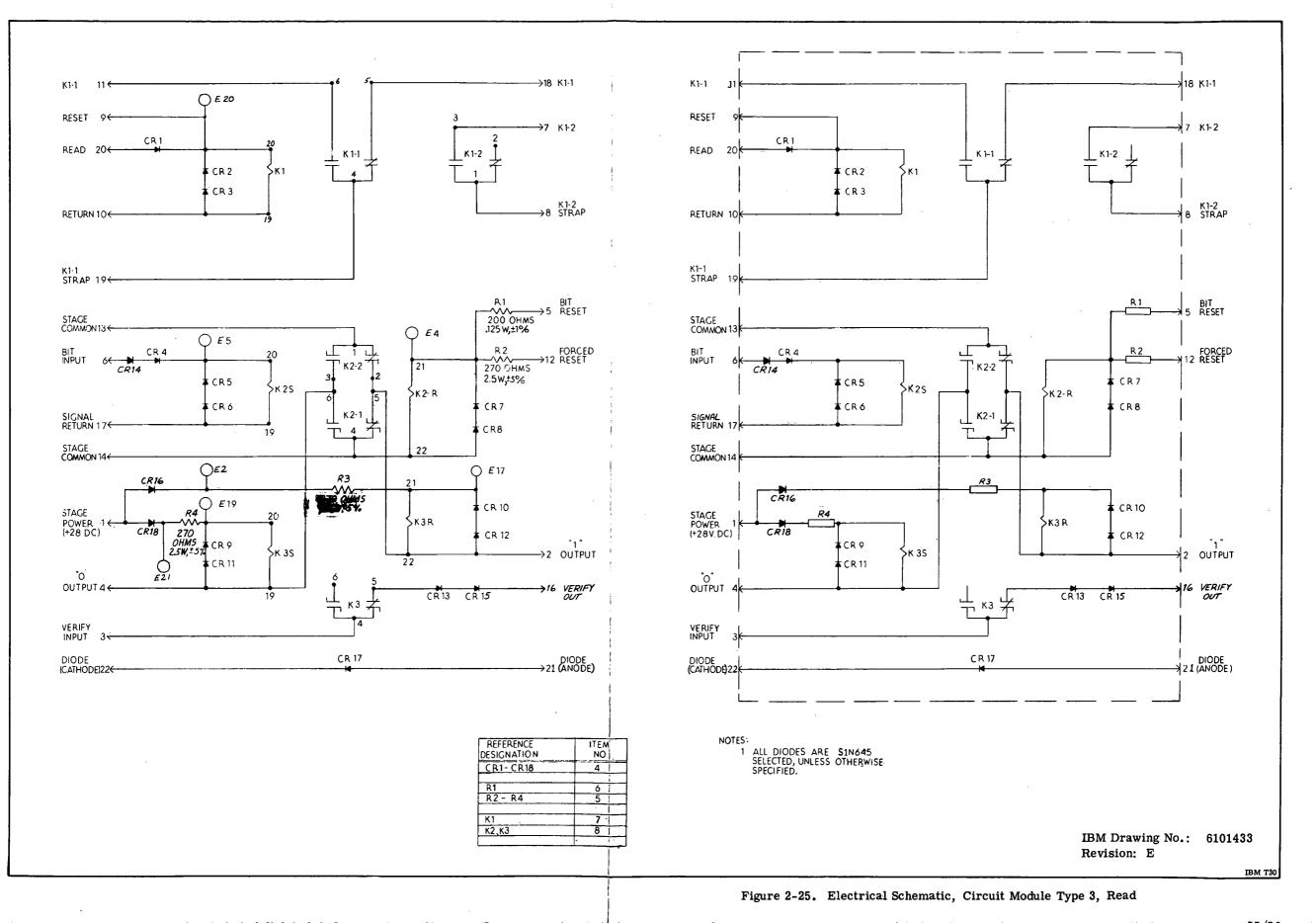

| 2-25   | Electrical Schematic, Circuit   |  |

|        | Module Type 3, Read 55          |  |

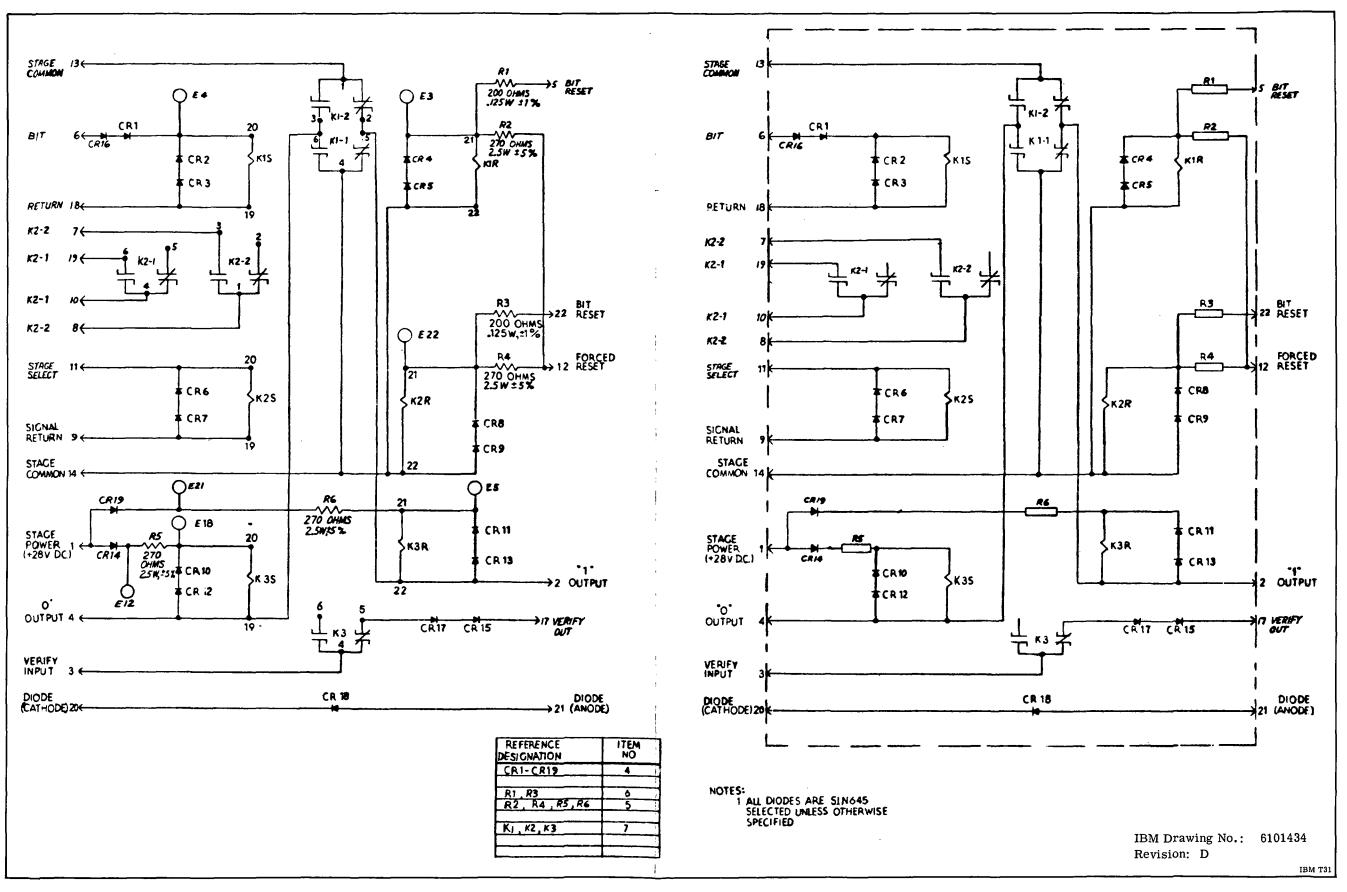

| 2-26   | Electrical Schematic, Circuit   |  |

|        | Module Type 4, Stage Select 57  |  |

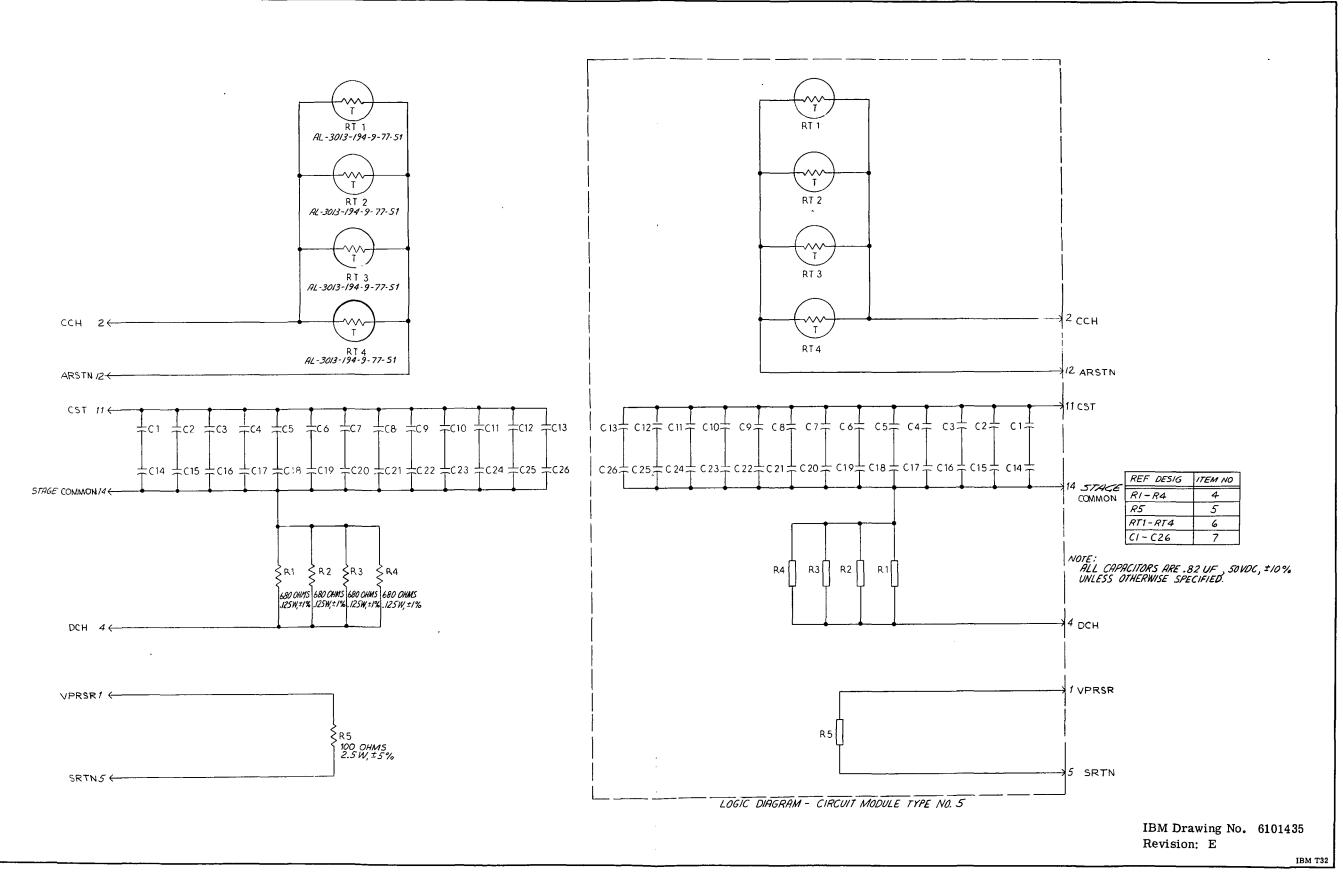

| 2-27   | Electrical Schematic, Circuit   |  |

|        | Module Type 5, Auto Reset 59    |  |

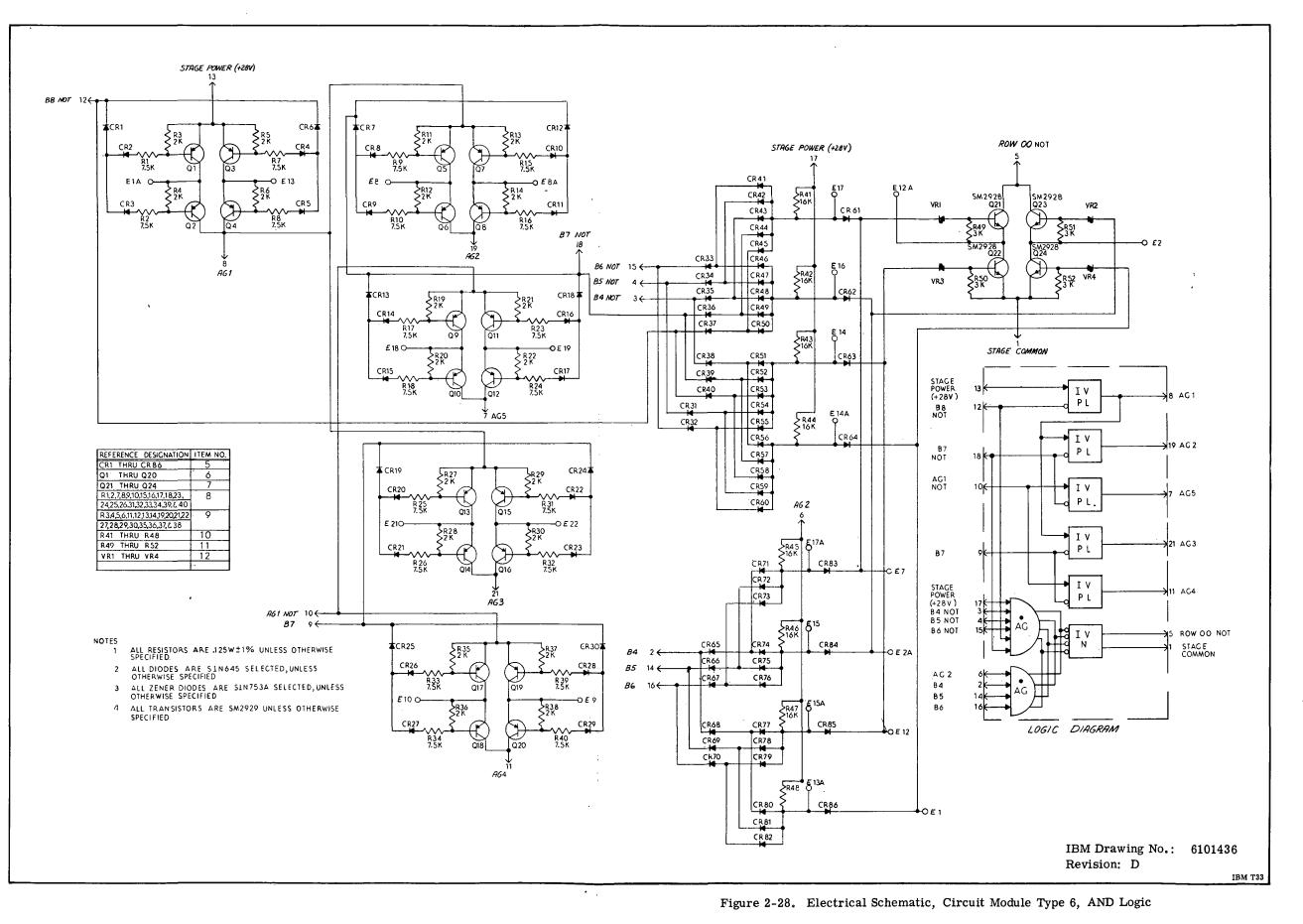

| 2-28   | Electrical Schematic, Circuit   |  |

|        | Module Type 6, AND Logic 61     |  |

| 2-29   | Electrical Schematic, Circuit   |  |

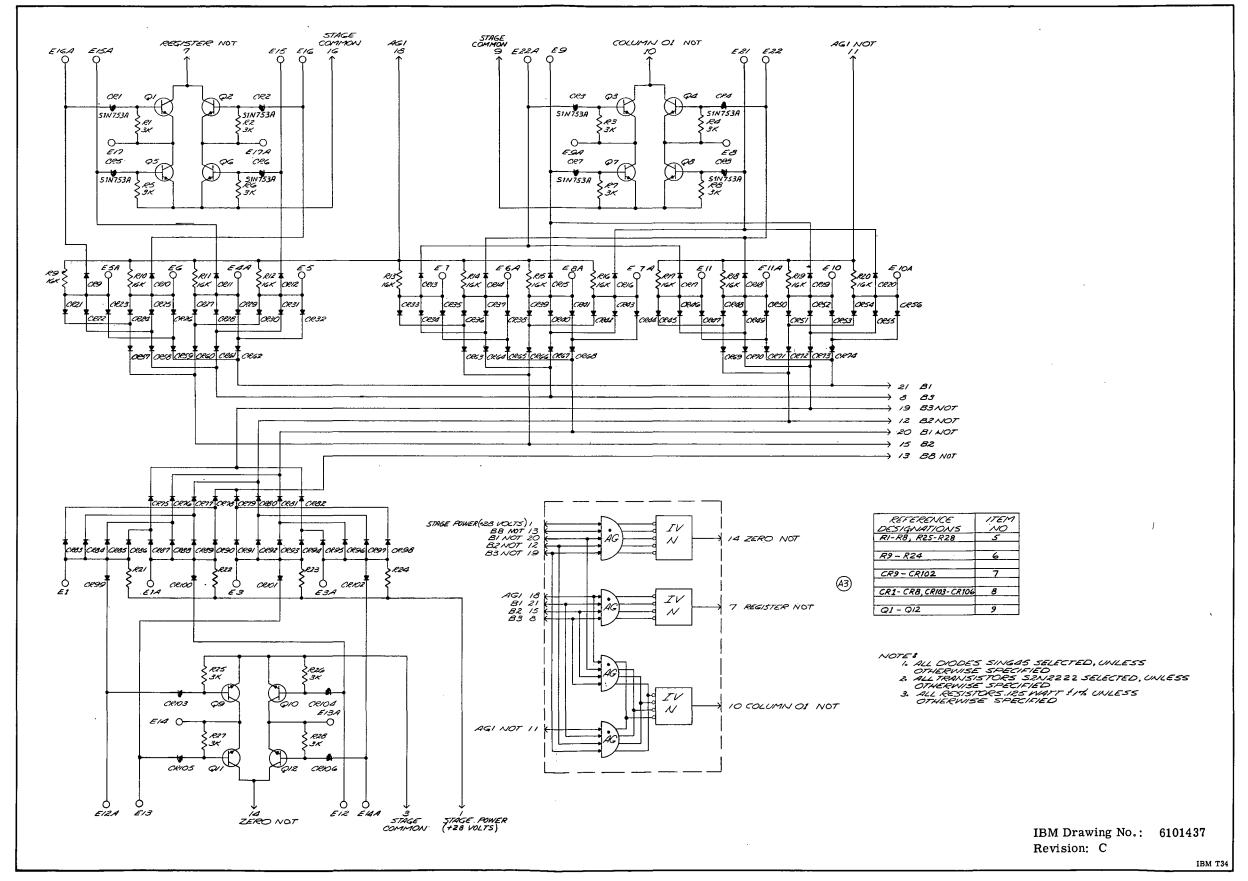

|        | Module Type 7, Decode 63        |  |

| 2-30   | Electrical Schematic, Circuit   |  |

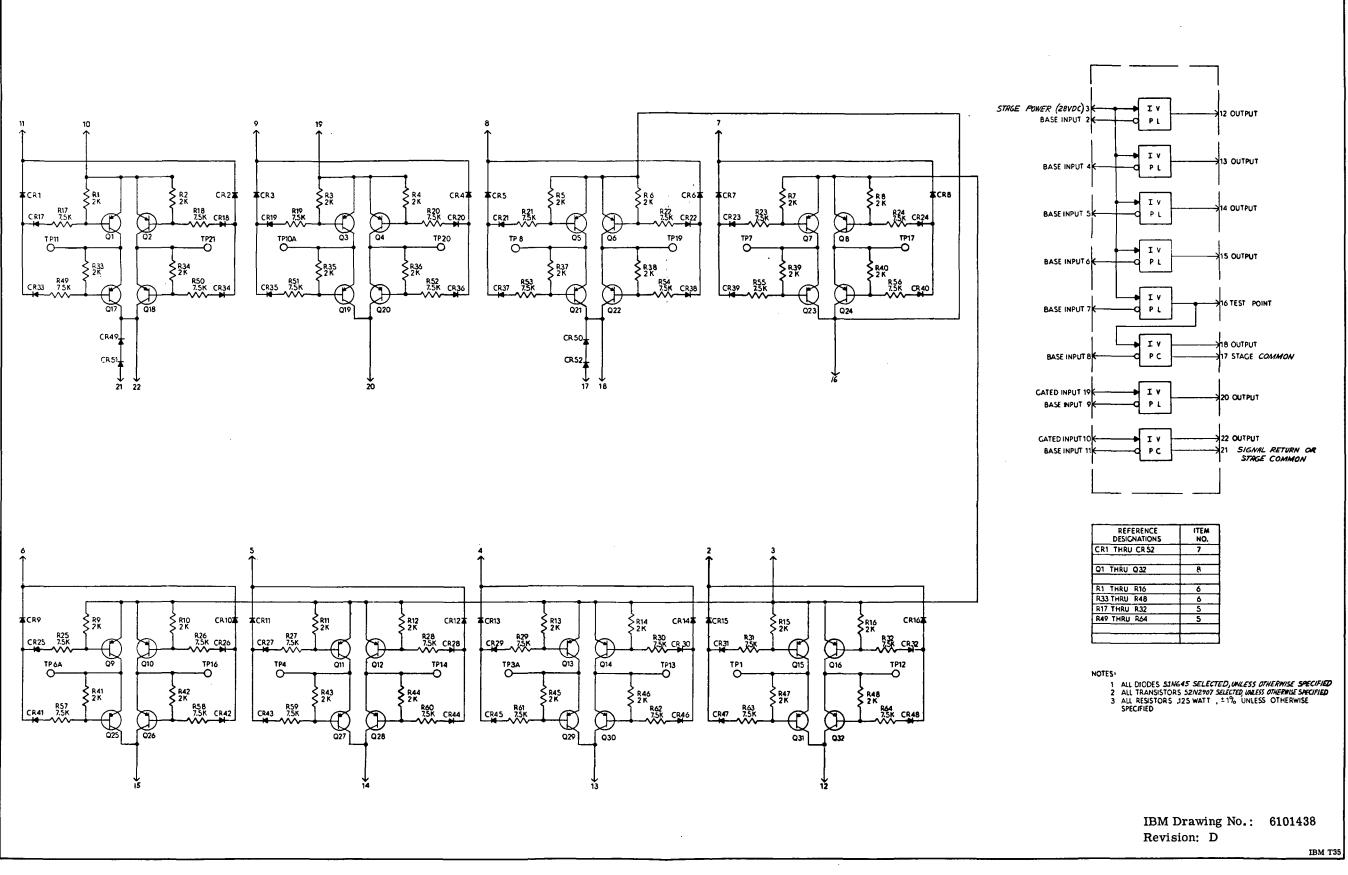

|        | Module Type 8, Miscellaneous    |  |

|        | Driver                          |  |

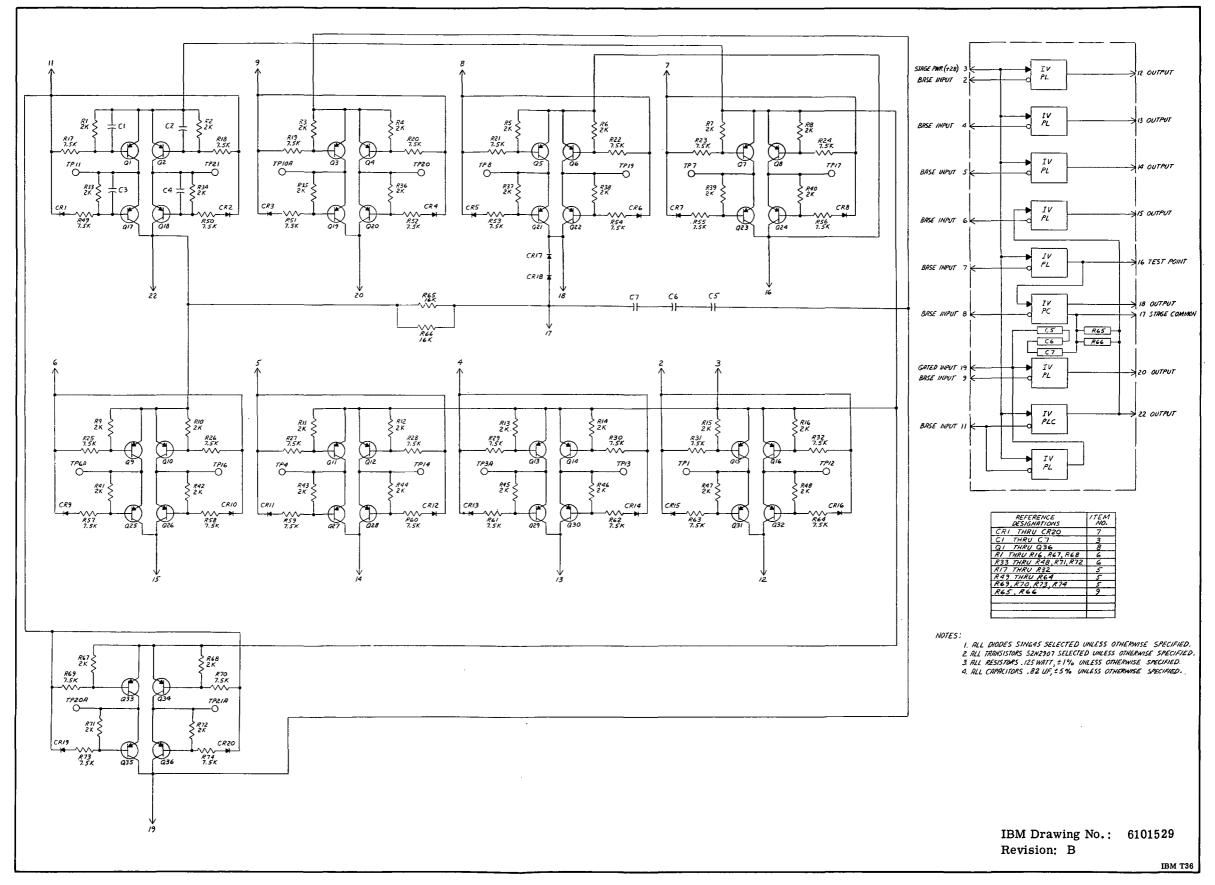

| 2-31   | Electrical Schematic, Circuit   |  |

|        | Module Type 9, Miscellaneous    |  |

|        | Driver                          |  |

|        |                                 |  |

Number

| Numbe | r Title Pa                        | age |

|-------|-----------------------------------|-----|

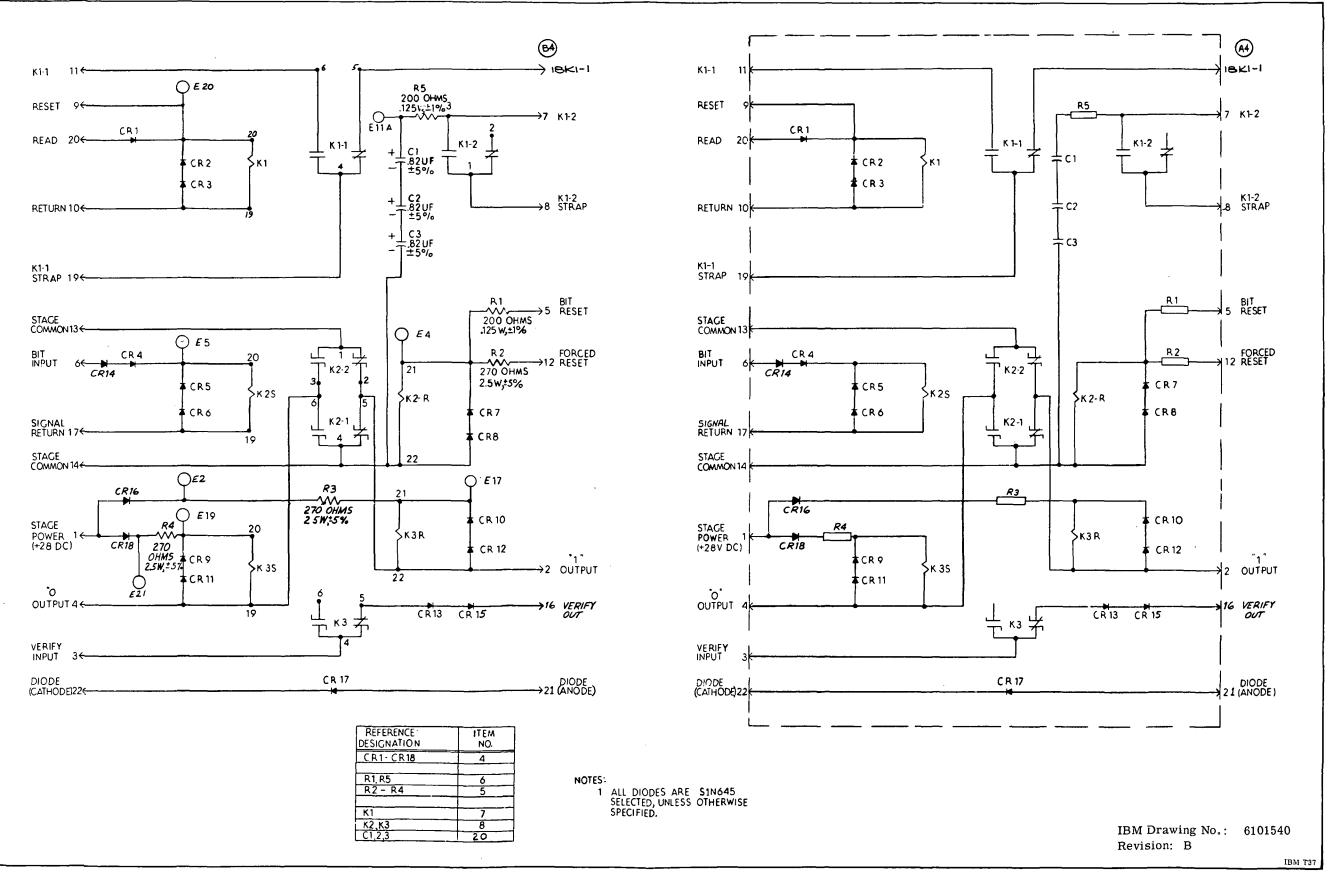

| 2-32  | Electrical Schematic, Circuit     |     |

|       | Module Type 10, Read              | 69  |

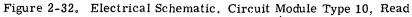

| 2-33  | Electrical Schematic, Circuit     |     |

|       | Module Type 11, Read              | 71  |

| 2-34  | Electrical Schematic, Circuit     |     |

|       | Module Type 12, Miscellaneous     |     |

|       | Driver                            | 73  |

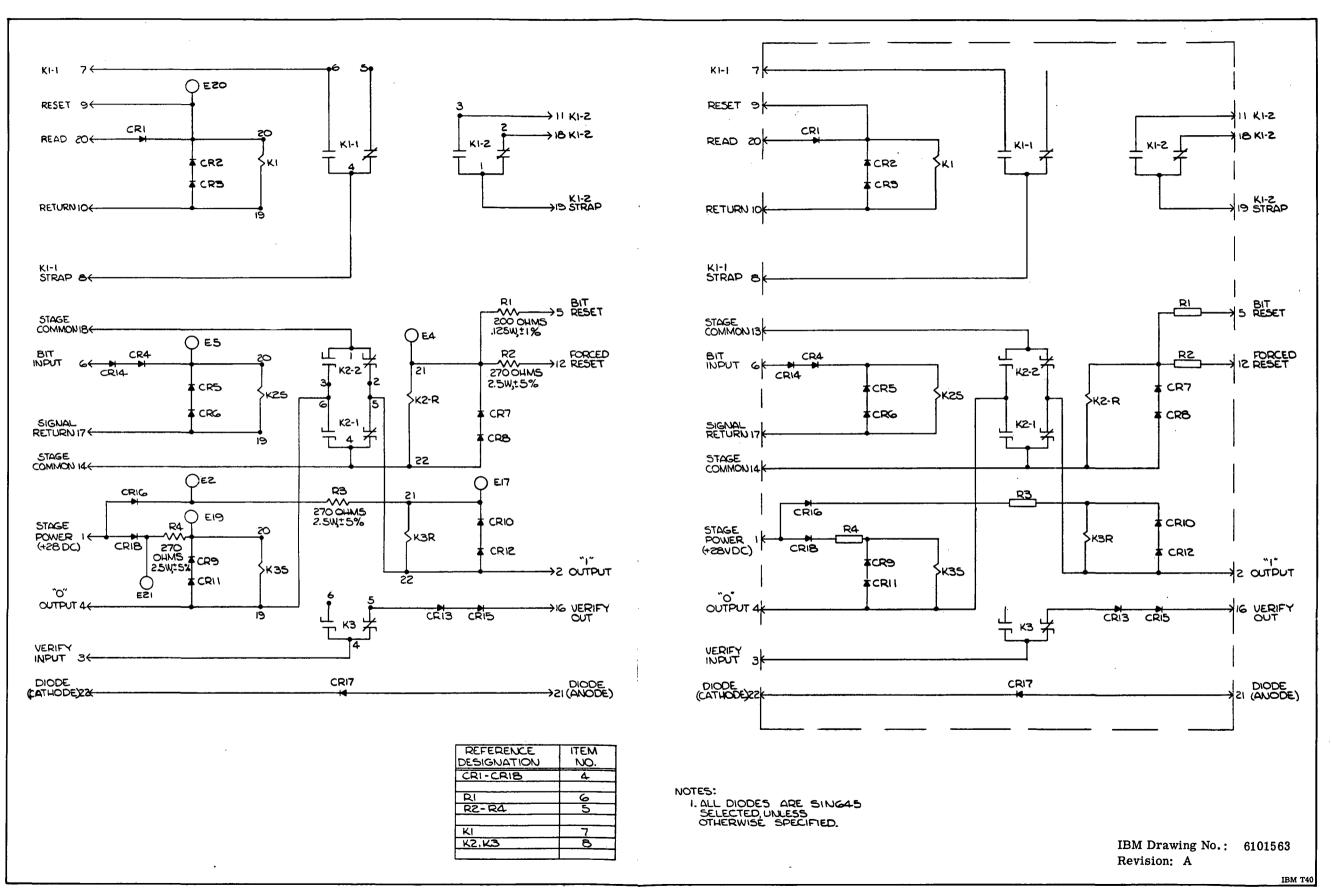

| 2-35  | Electrical Schematic, Circuit     |     |

|       | Module Type 13, Read              | 75  |

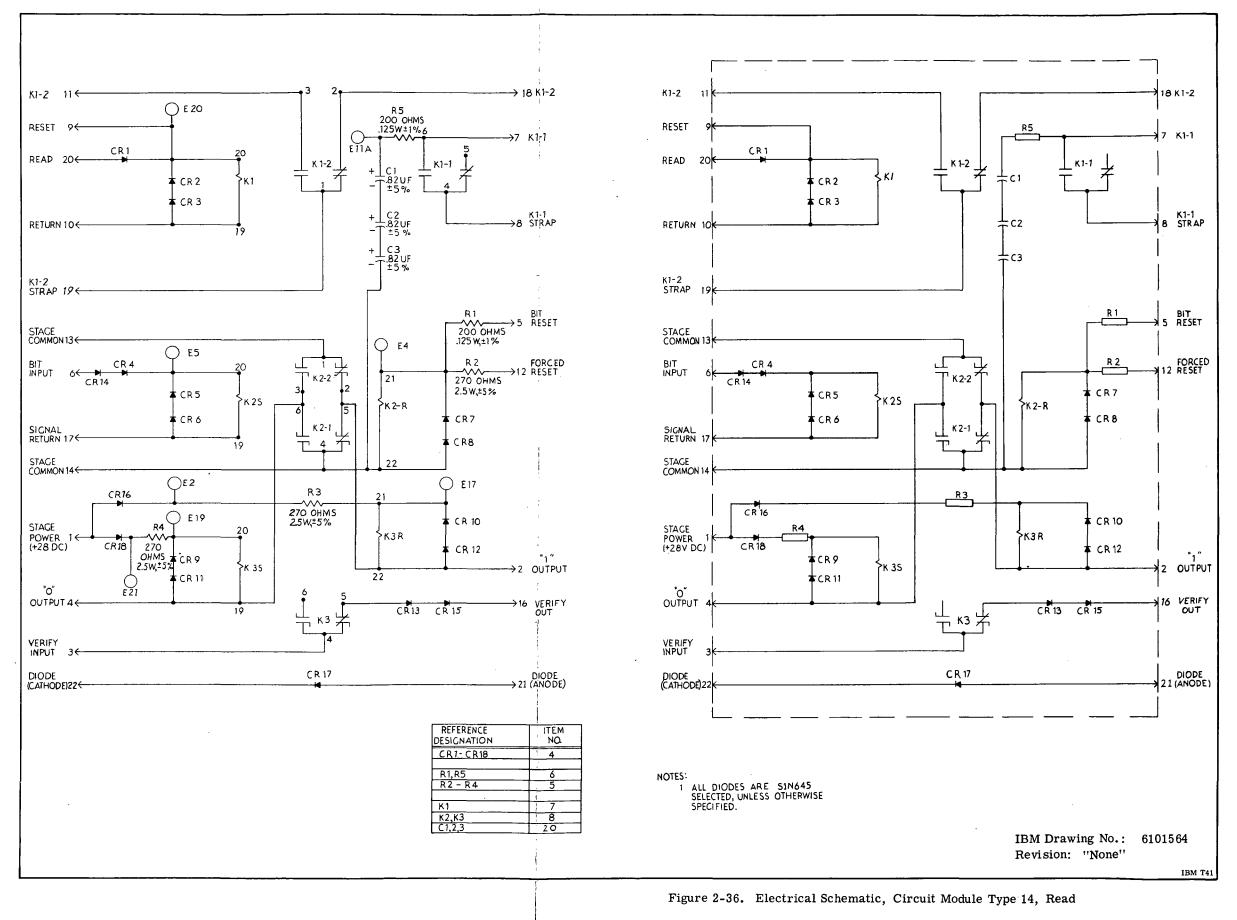

| 2-36  | Electrical Schematic, Circuit     |     |

|       | Module Type 14, Read              | 77  |

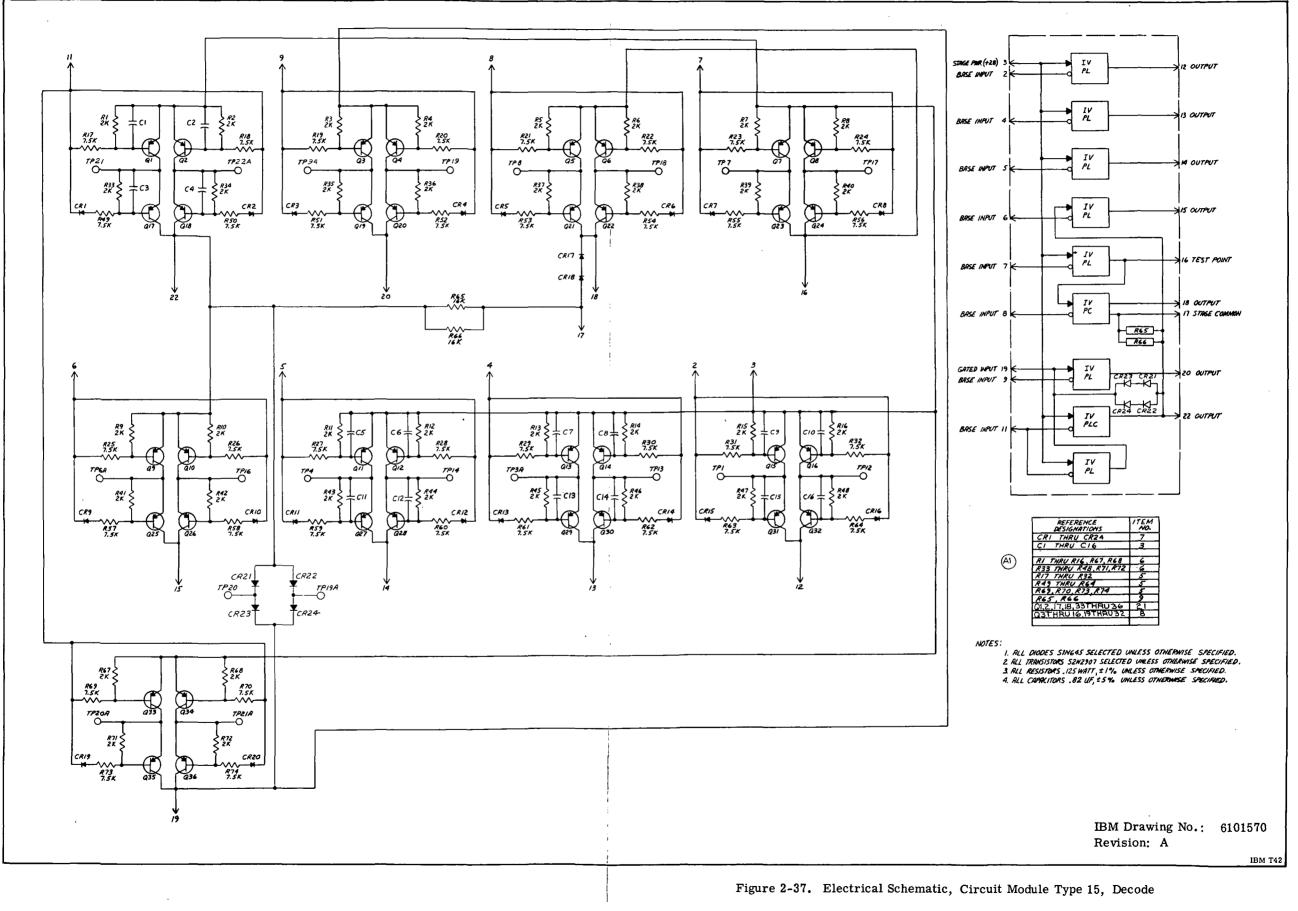

| 2-37  | Electrical Schematic, Circuit     |     |

|       | Module Type 15, Decode            | 79  |

| 2-38  | Electrical Schematic, Circuit     |     |

|       | Module Type 16, Stage Select      | 81  |

| 3-1   | Packaging Instructions for Switch |     |

|       | Selector Model II                 | 85  |

Page

## TABLES

Title

|     | 0                                  |

|-----|------------------------------------|

| 1-1 | Types and Use of Switch Selector   |

|     | Circuit Modules 2                  |

| 1-2 | Electrical Characteristics 6       |

| 2-1 | Switch Selector Relay Functions 37 |

# SECTION I INTRODUCTION AND DESCRIPTION

## 1-1 INTRODUCTION

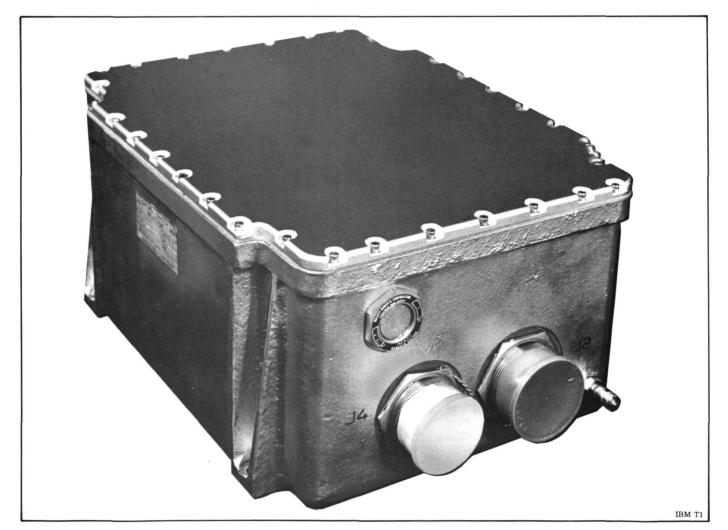

This technical manual defines the principles of operation, packaging procedures, and maintenance and repair instructions for the Model II Switch Selector (see Figure 1-1).

The Switch Selector is a combination solid state and electromechanical component which provides interstage mode and sequence control between the Launch Vehicle Digital Computer/Launch Vehicle Data Adapter (LVDC/LVDA) and the stage distributors. One Switch Selector is located in each stage and in the Instrument Unit of the Saturn Launch Vehicles.

By utilizing a digital coding-decoding technique, each Switch Selector can activate, one at a time, 112 different circuits in the stage in which it is located. Coding of the flight sequence commands and the decoding of these commands by the stage Switch Selectors has the following advantages: the number of interface lines between stages is reduced; flexibility of the system with respect to timing and sequencing is increased; and the discrete output circuitry of the LVDC/LVDA is conserved.

Figure 1-1. Switch Selector, Model II (Three-Quarter View)

## 1-2 DESCRIPTION

#### 1-3 MECHANICAL DESIGN

The mechanical design of the Switch Selector is comprised of a housing, cover, cover gasket, and an electrical assembly. The electrical assembly consists of two panel assemblies, a harness assembly, two RFI filters, and 34 circuit modules. There are 4,684 discrete electrical components packaged in the circuit modules.

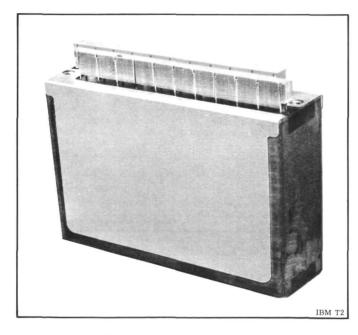

#### Circuit Modules

Figure 1-2 shows a typical Switch Selector circuit module. Electrical components (transistors, resistors, diodes, relays) are mounted between two epoxy-glass insulator plates which serve primarily as a holding fixture. Rectangular nickel wire (0.010 inch thick by 0.020 inch wide) is welded to the component leads to provide the circuit interconnections. Dual wires with separate welds for each wire are used where required, for circuit interconnections to improve reliability. A Fiberite FM-4005 molded connector is mounted at the bottom of the assembly. The connector contains 22 dual pins. Each pin is formed to a 90° bend such that one end of the pin protrudes from the side of the connector and the other end of the pin protrudes from the bottom of the connector. The interconnection wire is welded to the dual pins on the sides of the connector to provide inputs and outputs through the pins to the bottom of the module. Another

Figure 1-2. Switch Selector Circuit Module

connector is mounted to the top of the module and is utilized for testing to the detailed part and circuit function level. The interconnection wires to the test connector are simplex. The connectors on the top and bottom of the module are identical except that the pins on the test connector are cut to 0.015 inch to prevent interference. Two threaded inserts in the bottom of the module connector are used for attachment of the module to the panel assembly. Specific unused pins are cut off to provide polarized mounting for each module type.

The module is completely cast in Stycast 1090 except for the top surface of the test connector and the bottom surface of the module connector. Aluminum foil heat sinks, 0.10 inch thick are formed to the sides and bottom of the module and bonded in place.

The overall size of the module is 3.00 inches long by 0.80 inch wide by 2.00 inches high. The Switch Selector utilizes 13 of the 16 available types of modules to make up the 34 modules required for each Switch Selector. Table 1-1 lists the various types of modules and their function.

| Table 1-1. | Types and   | l Use of Switc | h |

|------------|-------------|----------------|---|

| Select     | tor Circuit | Modules        |   |

| Module  | Function                                                 | Number Required per<br>Switch Selector  |  |  |

|---------|----------------------------------------------------------|-----------------------------------------|--|--|

| Type 1  | Decode - provides<br>row and column<br>decode capability | 7                                       |  |  |

| Type 2  | Output driver                                            | 14                                      |  |  |

| Type 3  | Read command                                             | 2                                       |  |  |

| Type 4  | Stage select                                             | 3 until S/N 118,<br>2 on subsequent S/N |  |  |

| Type 5  | Automatic reset -<br>RC Network and<br>thermistors       | 1                                       |  |  |

| Туре б  | AG Logic<br>drivers                                      | 1                                       |  |  |

| Type 7  | Decode                                                   | 1                                       |  |  |

| Type 8  | Miscellaneous<br>drivers                                 | 1                                       |  |  |

| Type 9  | Miscellaneous<br>drivers                                 | None after<br>prototype 3               |  |  |

| Type 10 | Relay module                                             | None after<br>prototype 3               |  |  |

| Module  | Function                                                     | Number Required per<br>Switch Selector |

|---------|--------------------------------------------------------------|----------------------------------------|

| Type 11 | Relay module                                                 | 1                                      |

| Type 12 | Miscellaneous<br>driver                                      | None after S/N 104                     |

| Type 13 | Relay module                                                 | 1                                      |

| Type 14 | Relay module                                                 | 1                                      |

| Type 15 | Decode - switch<br>power, zero<br>indicate, and<br>column 02 | 1                                      |

| Type 16 | Relay module                                                 | 1 after S/N 117                        |

Table 1-1. Types and Use of Switch Selector Circuit Modules (Cont)

#### Panel Assemblies

The two panel assemblies (see Figure 1-3) provide electrical interconnections, thermal conduction, and mounting support for the circuit modules. A panel assembly consists of a printed wiring board, a heat-sink plate, harness supports, and harness connection terminals.

The printed wiring board is 0.062 inch thick glass-epoxy laminate with a wiring pattern on both sides and "plated through" holes. The harness connection terminals are swaged and soldered into specific "plated through" holes in the printed wiring board.

The heat-sink plate is magnesium alloy 0.091 inch thick. The plate has machined rectangular openings at each circuit module and harness terminal location which provide electrical clearance around the module pins and harness terminals. The plate is coated with a polyurethane resin for additional electrical insulation. The heat-sink plate is bonded with epoxy resin to the top side of the printed wiring board.

Two harness supports made of magnesium alloy are mounted at right angles to each other over the rows of harness terminals and between the circuit module locations and bolted to the panel assembly.

Figure 1-3. Switch Selector Panel Assembly

Switch Selector Section I

#### Harness Assembly

The harness is a conventional branched type utilizing 26 AWG tinned copper, polyolefin insulated, wire. The harness is layed out, formed, laced, and unit connectors attached prior to installation on the electrical assembly.

Harness wires are dual redundant for increased reliability. At the unit connector, each pair of redundant wires is terminated in one contact with a crimp and a solder connection. The back of the unit connectors are potted with a polyurethane compound to provide a seal and strain relief for the wires.

#### Electrical Assembly

The electrical assembly (see Figure 1-4) combines the harness, circuit modules, and the two panel assemblies on a frame for pre-acceptance electrical test prior to insertion of the assembly into the unit housing.

The panels are arranged so that the bottom sides face each other. The harness is assembled to the top side of each panel assembly and laced to the harness supports. The harness wires are inserted through a hole in the center of each connection terminal and soldered on the bottom side of the panel assembly. Shrink sleeving, assembled over the harness wire and terminal, provides strain relief on the wire. The harness assembly is branched at one end of the panel assemblies so that the panel assemblies may be opened to  $90^{\circ}$  for the solder operations and inspection.

The circuit modules are mounted on top of the heat sink. Each module is secured with 2 screws through the printed wiring board and the heat sink to the threaded inserts in the module connector. The module pins extend through the "plated through" holes in the printed wiring board and are soldered from the bottom side of the printed wiring board.

There are 19 circuit modules and a filter mounted on the top panel assembly and 15 circuit modules and a filter mounted on the bottom panel assembly. The filters are the same size as a circuit module. Each filter is secured with 4 screws to the panel assembly. Harness wires are soldered to 4 terminals on each end of the filter. Stage +28 Vdc and stage common (ground) are inputs to the unit in a common shield to one line filter. IU +28 Vdc and signal return (ground) are inputs to the unit in a common shield to the other line filter. These are the only shielded wires in the unit.

Six magnesium rails are bolted together to form a mounting frame. The frame is inserted between the bottom surfaces of the panel assemblies.

Figure 1-4. Switch Selector Electrical Assembly

The panel assemblies are bolted to the frame. A temporary test harness is attached to the electrical assembly for pre-acceptance testing. The test harness wires are attached to 61 terminals on the panel assemblies in the same manner as the system harness. After completion of pre-acceptance test, the test harness wires are cut off just above the test terminals and the harness is removed. Shrink sleeving is applied over the test terminals to seal them.

#### Housing, Cover, and Gasket

The component housing is a magnesium alloy casting. There are four unit mounting bosses with 0.281-inch diameter mounting holes at each corner of the casting. The bottom of the bosses is on the same plane as the bottom surface of the casting. The bosses are 0.250 inch thick. There are mounting holes for a 32-contact connector, a 62-contact connector, a pressure relief valve, and a purging valve in one end of the casting. In the other end of the casting there are mounting holes for a 32-contact connector, a 61-contact connector, and a purging valve. The top edge of the four side walls of the casting have 32 tapped holes for cover mounting. Inside the casting there are ten bosses which extend from the bottom surface and side walls. These bosses have one tapped hole in each for mounting

the electrical assembly. On the bottom inside surface of the casting, four silicone sponge pads are bonded with adhesive. These pads are compressed by the circuit modules when the electrical assembly is inserted and thereby provide additional support and dampening under mechanical environment. The casting is treated with iridite and coated with aluminum paint.

The unit cover is a machined magnesuim alloy plate with 32 clearance holes for mounting. Four silicone pads are bonded to the bottom surface of the cover. These pads are compressed when the cover is assembled to the housing by the circuit modules of the electrical assembly and serve the same purpose as the pads inside the housing. The cover is treated with iridite and painted with aluminum paint.

The cover gasket material is silicone filled stainless steel which provides both a pressure seal and RFI shielding. The gasket is 0.062 inch thick by 0.312 inch wide and forms a rectangle to fit the top edge of the housing. There are 32 clearance holes for the cover mounting screws.

#### Component Assembly

The electrical assembly is inserted through the top of the housing (see Figure 1-5). The harness

Figure 1-5. Switch Selector, Model II (Internal View)

connectors are drawn through their mounting holes and secured with hexagonal nuts and safety wire. The electrical assembly is bolted in 10 places to the bosses in the bottom of the housing. The shield ground wires are secured to the inside surface of the housing wall with screws and lock washers. The pressure relief valve, which is preset for a "cracking" pressure of 10 psi, and the two purging valves are assembled in their mounting holes. The cover gasket and cover are mounted on top of the housing and secured with 32 screws.

#### 1 - 4ELECTRICAL CHARACTERISTICS

The electrical characteristics of the Switch Selector Model II are specified in Table 1-2.

#### 1-5 DIMENSIONS AND WEIGHT

The Switch Selector has the following physical characteristics:

| Height: | 5.29 inches maximum  |

|---------|----------------------|

| Width:  | 8.56 inches maximum  |

| Length: | 12.50 inches maximum |

| Weight: | 19.8 pounds (approx) |

| Input Voltages                                                                                      |                                                                                                                          |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Verification                                                                                        | $\begin{array}{c} 28 \pm 4 \ \text{Vdc} \\ 28 \pm 2 \ \text{Vdc} \\ \end{array}$                                         |

| Input Power                                                                                         |                                                                                                                          |

| Peak                                                                                                | 17.6 Watts<br>1.9 Watts                                                                                                  |

| Input Signals                                                                                       |                                                                                                                          |

| Stage select                                                                                        | Up level: 17.5 Vdc<br>(min) to 32.0 Vdc (max)<br>Down level: open circuit<br>clamped to gnd for<br>negative suppression. |

| Output Signals                                                                                      |                                                                                                                          |

| Register verification       Channel outputs       Zero indicate       Register test       Telemetry | 28 Vdc<br>28 Vdc<br>28 Vdc<br>28 Vdc<br>28 Vdc                                                                           |

| No channel active                                                                                   | 0.2 Vdc<br>2.0 Vdc<br>3.0 Vdc                                                                                            |

| Operating Temperature                                                                               | -25 °C (-13 °F) to<br>+100 °C (+212 °F) in a<br>partial vacuum of not<br>greater than $10^{-4}$ mm<br>of mercury.        |

| Electrical Isolation                                                                                | 100 Megohms between all<br>points not connected by a<br>conductor.                                                       |

| Heat Dissipation                                                                                    | 3.0 Watts                                                                                                                |

Table 1-2. Electrical Characteristics

# SECTION II PRINCIPLES OF OPERATION

### 2-1 GENERAL OPERATION

#### 2-2 SYSTEM DESCRIPTION

Each stage, and the Instrument Unit, of the Saturn Launch Vehicle are equipped with a Switch Selector. The Switch Selector consists of electronic and electromechanical components which decode digital flight sequence commands from the LVDA/ LVDC and activate the proper stage circuits to execute the commands.

Each Switch Selector can activate, one at a time, 112 different circuits in its stage. The selection of a particular stage Switch Selector is accomplished through the command code. Coding of flight sequence commands and decoding of the stage Switch Selectors reduces the number of interface lines between stages and increases the flexibility of the system with respect to timing and sequence. In the Saturn V Launch Vehicle, which contains 4 Switch Selectors, 448 different functions can be controlled using only 28 lines from the LVDA. (Two IU + 28-volt and two signal return lines from the Control Distributor are also used.) Flight sequence commands may be issued at time intervals of 100 milliseconds.

Figure 2-1 illustrates the Saturn V Switch Selector configuration. As shown, all Switch Selector control lines are connected through the Control Distributor in the IU to the LVDA and the electrical support equipment.

To maintain power isolation between vehicle stages, the Switch Selector is divided into two sections: The input section (relay circuits) of each Switch Selector receives its power from the IU; the output section (decoding circuitry and drivers) of each Switch Selector receives its power from the stage in which the Switch Selector is located. The input and output are coupled together through a diode matrix. This matrix decodes the 8-bit input code and activates a PNP output driver, thus producing a Switch Selector output. Each Switch Selector is connected to the LVDA through 2 lines:

Stage select lines - 8 / Read command lines - 2 Reset (forced) lines - 2 Bit register output lines - 8 Verification lines - 8

In addition, there are 2 lines for IU + 28 Vdc and 2 lines for signal return between the Control Distributor and the Switch Selectors.

The wire pairs for stage select, read command, forced reset, IU + 28 Vdc, and signal return are redundant. Only one of each pair is required for normal operation.

All connections between the LVDA and the Switch Selectors, with the exception of the stage select inputs, are connected in parallel as shown in Figure 2-2.

The output signals of the LVDA switch selector register, with the exception of the 8-bit command, are sampled at the Control Distributor in the IU and sent to IU PCM telemetry. Each Switch Selector also provides 3 outputs to the telemetry system within its stage.

The Switch Selector is designed to execute flight sequence commands given by the 8-bit code or by its complement. This feature increases reliability and permits operation of the system despite certain failures in the LVDA switch selector register, line drivers, interface cabling, or Switch Selector relays.

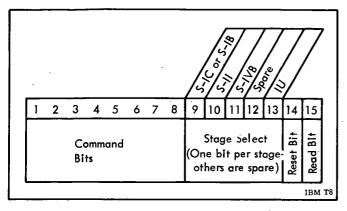

The flight sequence commands are stored in the LVDC memory and are issued according to the flight program. When a Programmed Input/Output (PIO) instruction is given, the LVDC loads the 15-bit switch selector register with the computer data. The LVDA switch selector register word format is shown in Figure 2-3. Switch Selector Section II

Switch selector register bits 1 through 8 represent the flight sequence command. Bits 9 through 13 select the Switch Selector to be activated. Bit 14 resets all the relays in the Switch Selectors in the event data transfer is incorrect as indicated by faulty verification information received by the LVDA. Bit 15 activates the addressed Switch Selector for execution of the command. The LVDC loads the switch selector register in two passes; bits 1 through 13 are loaded during the first pass and, depending on the feedback code, either bit 14 or bit 15 is loaded during the second pass.

After the Switch Selector input relays have been "picked" by the 8-bit command, the complement of the received code is sent back to the LVDA/ LVDC over eight parallel lines. The feedback (verification information) is returned to the digital input multiplexer of the LVDA and is subsequently compared with the original code in the LVDC. If the feedback agrees with the original code, a read command is given. If the feedback does not agree with the original code, a reset command is given (forced reset), and the LVDC/LVDA reissues the 8-bit command in complement form.

A typical operation cycle, to initiate a given function in a particular stage, is accomplished as follows:

- The 8 verify lines are sampled to ensure that all stage select relays have been reset, thereby ensuring an unwanted stage is not selected. Zero voltage on all lines indicates that this condition exists. The presence of IU + 28 Vdc on the verify lines indicates that the verify lines are enabled because a stage Switch Selector is not reset. Having detected this situation, the LVDC commands a "force reset" and then rechecks the verify lines.

- The LVDC inserts the 8-bit flight command into the LVDA switch selector register. At the same time, a stage select command is sent to the appropriate Switch Selector. Application of the stage select command completes the signal return path for the input relays and allows the 8-bit command to be stored in the Switch Selector input relays.

- The verification lines are sampled to determine if the command transfer was correct.

- If the verification is correct, the LVDC sends a read command to the Switch Selector; activating it, and causing the proper output to occur.

- If the verification is not correct, the LVDC initiates a reset command to prepare the Switch Selector to receive the complement of the original command.

- After the forced reset is completed, the LVDC loads the stage select command, and the complement of the previously sent command, into the LVDA switch selector register.

- Neglecting the verification information that occurs after the complement command is inserted, the LVDC initiates a read command which produces an output from the selected switch selector channel. The read command also energizes the automatic reset circuitry which returns the Switch Selector to the reset condition to prepare it for a new cycle.

#### 2-3 COMPONENT DESCRIPTION

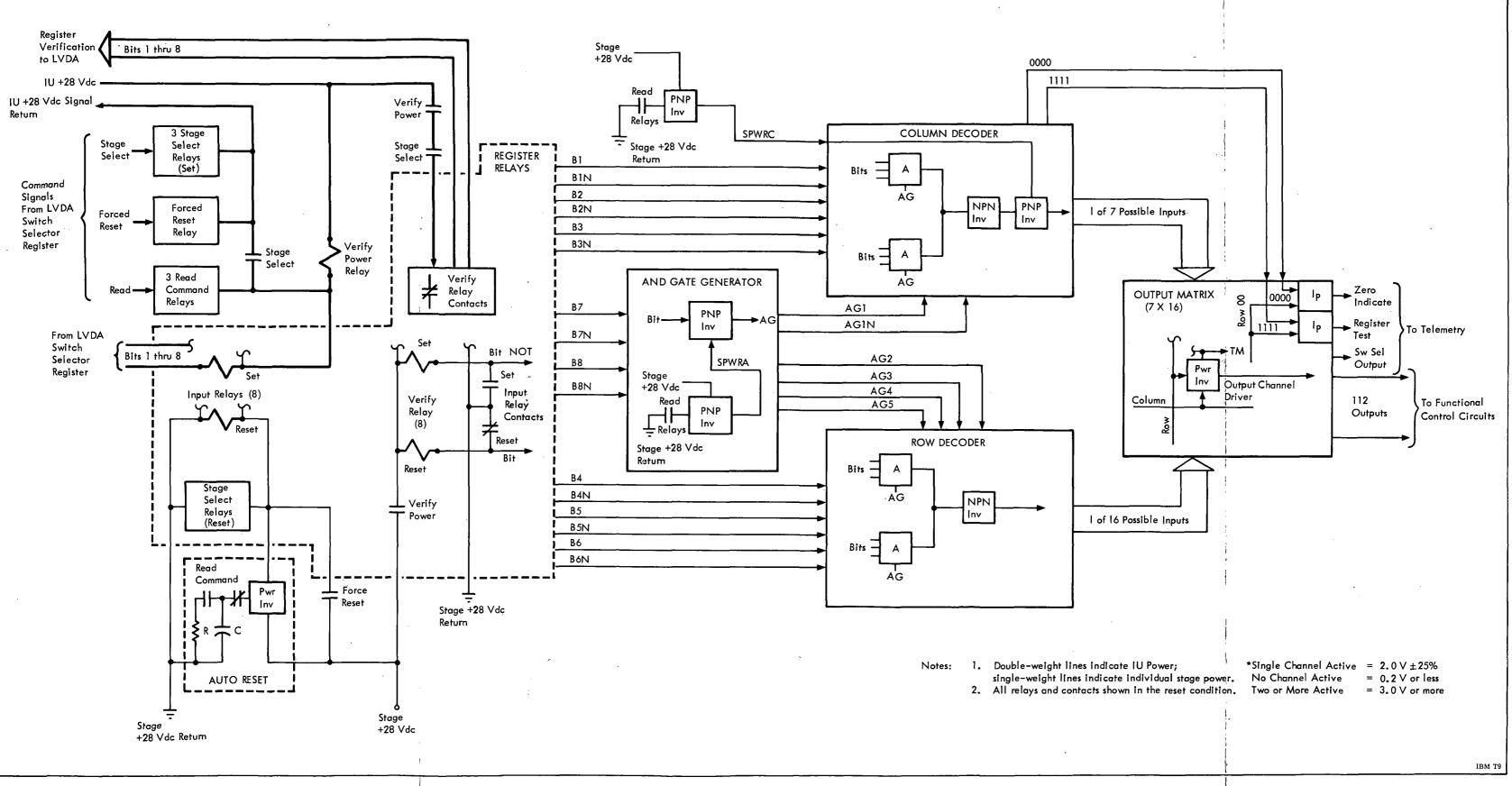

A description of Switch Selector operation is given in the following paragraphs (refer to the simplified schematic diagram shown in Figure 2-4). The circuit functions of the Switch Selector are as follows:

| Stage select                |

|-----------------------------|

| Input relays                |

| Verification                |

| Reset (forced)              |

| Read command                |

| Reset (automatic)           |

| Decoding matrix             |

| Output matrix and telemetry |

| Test outputs                |

8

Figure 2-1. Saturn V Switch Selector Configuration

9/10

The Switch Selector operates on positive logic (i. e., + 28 Vdc for a binary "1" and 0 Vdc for a binary "0").

#### Stage Select

The purpose of the stage select command is to enable the desired Switch Selector to receive the coded flight sequence command from the LVDA. The stage select command (1 bit) is transmitted individually on a separate line to each Switch Selector. Because of the danger of overloading the LVDA, no more than 2 Switch Selectors can be addressed simultaneously.

The stage select command sets three magnetic latch relays in the addressed Switch Selector. The setting of these relays completes a ground path

|                        |                   |        |       |          |    | 15-    | Bit Seria         | 1   |      |                |       |                        |              |                           |                      | 8-Bit S               | erial               |

|------------------------|-------------------|--------|-------|----------|----|--------|-------------------|-----|------|----------------|-------|------------------------|--------------|---------------------------|----------------------|-----------------------|---------------------|

| DA                     | Sto               | ige Se | elect |          |    | ~<br>  | Flight<br>Comman  | nd  | Rese | et į Re        | ead I | <b>ر</b>               |              |                           | Digital<br>Multip    |                       | <b>`</b>            |

| 12                     | 9                 | 10     | Ţ     | ļ        | 13 | 1      | throug            | h 8 | 14   |                | 5     |                        |              |                           | thro                 | ugh 8                 |                     |

| (Spare)                |                   |        | -     |          |    | ,      | 8 Line<br>Paralle |     |      |                |       |                        | Sign<br>Retu |                           | 8 Li<br>Para         |                       |                     |

| Control<br>Distributor |                   | -      |       |          |    |        |                   |     |      |                |       | 1∪<br>+28 ∨            | /dc 5        |                           | 3                    |                       |                     |

|                        |                   |        |       |          |    |        | •                 | •   |      | <br> <br> <br> | +     |                        | •<br>•       | <b>▲</b> ▲<br>  -   -<br> | •                    |                       | IU<br>Swi<br>Sele   |

|                        |                   |        |       |          |    | ∟<br>► |                   |     |      |                |       |                        |              |                           |                      | ·                     | <br>יו-s [          |

|                        |                   |        | L     |          |    | •      | •                 | •   |      |                |       |                        | •<br>        | $\left  \right $          |                      | •<br>•                | Swi<br>Seli         |

|                        |                   |        |       |          |    |        | •                 |     | •    |                |       |                        |              |                           | •                    | •                     | S-II<br>Swi<br>Sele |

|                        |                   |        |       | <u> </u> |    |        | •                 | •   |      |                |       |                        | •            |                           |                      |                       | S-IC<br>Swi<br>Sele |

| Notes:                 |                   |        |       |          |    |        |                   |     |      |                |       |                        |              |                           |                      |                       |                     |

| LV                     | DA.               |        |       |          |    |        | ctor and          |     |      | Sele           | ctors | from                   | LVDA         | (5 Sw                     | itch Sel             | e to Swit<br>ectors). |                     |

| 2. 26                  | lines l<br>DA (So |        |       |          |    |        |                   |     | 5.   | Swite          | ch Ś  | U +2<br>electo<br>Band | ors from     | and si<br>n Cont          | gnal ret<br>rol Dist | urn) to a<br>ributor  | 11                  |

## Figure 2-2. LVDC - Switch Selector Interconnection Diagram

11

Figure 2-3. Switch Selector Register Word Format

for the read command relay, the set side of the input relays, and the verify power relay (see Figure 2-4). This action conditions the read and input relays to receive commands from the LVDA and energizes the verify power relay. When the verify power relay contacts close, IU + 28 Vdc power is applied through a set of stage select contacts to the verify relay contacts; and stage + 28 Vdc is applied to the verify relays. The Switch Selector can now accept the 8-bit command from the LVDA, store it in the input relays, and make verification information available to the LVDA.

#### Input Relays

The input register of the Switch Selector is made up of eight magnetic latch relays, controlled by the 8-bit coded command from the LVDA. The coded command (consisting of 8 bits in parallel) is available to the Switch Selector during the same period of time the stage select signal is present. As soon as the stage select relays are set, a signal return path is provided for the coded command through the input relay coils (see Figure 2-4). This allows the coded command to be stored in the input register.

Once the coded command is stored in the input register, binary information is available to the verification register, column decoder, row decoder, and the AND gate generator.

#### Verification

A feedback circuit is used to provide verification information back to the LVDC. This circuit consists of 8 relays, and is controlled by the input relay contacts. When a "1" is applied to the input relay set coil, stage ground is switched to the verify relay set coil causing the normally closed verify relay contact to open; indicating a "0" to the LVDC. When a "0" is applied to the input relay set coil, the input relay contacts remain in the reset condition. Stage ground remains applied to one side of the verify relay reset coil, causing the verify relay contact to remain in its normally closed position. Therefore, the verification output of a Switch Selector is the complement of the input command.

#### Read Command

Immediately after verification of the original command, the read command is initiated. If verification of the original command proved to be false, the read command will not be initiated by the LVDC until the forced reset, stage select, and complemented command have been transmitted to the Switch Selector.

Three conventional (non-latching) relays are picked when the read command is received from the LVDA. One side of the coils of these relays is connected to the read command signal, the other side is connected to the IU signal return through the stage select relay contacts. Thus, a stage select signal must have been received before a read command relay can be energized. When the read relay contacts close, stage ground is applied to the switch power inverters (SPWRA and SPWRC) in the decoder matrix. These inverters generate voltages (SPWRA and SPWRC) which activate the AND gate generators and the column decoder circuitry allowing the coded command to be decoded and an output to occur.

#### Reset (Forced)

A forced reset is initiated by the LVDC when the LVDC determines that the verification information is not the complement of the given command. The reset signal is applied to the forced reset relay coil causing the forced reset contacts to close. This action applies stage + 28 Vdc to the stage select and input relay reset coils forcing the Switch Selector into the reset condition shown in Figure 2-4. After the forced reset has been completed, the stage select command and the complement of the original flight sequence command are transmitted to the Switch Selector. The complement command is not verified by the LVDC before the read command is issued.

#### Reset (Automatic)

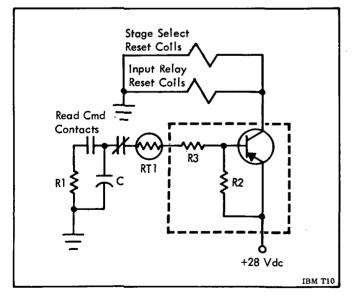

An automatic reset pulse is generated when stage power is initially applied to the Switch Selector and when the read command is issued. The

Figure 2-4. Switch Selector (Model II) Simplified Diagram

automatic reset circuitry consists of a power inverter, an RC network, and a set of read command contacts.

Activation of the read command relay contacts is not required to produce the "Power ON" reset pulse. Prior to the application of stage power to the Switch Selector, the read command contacts are in the reset condition (as shown in Figure 2-5) and capacitor C is in a discharged state. When power is applied to the Switch Selector, stage 28 Vdc is applied to the emitter of the power inverter and capacitor C begins to charge through base resistor (R3) and thermistor (RT1). Under these conditions the power inverter turns on, producing an output of approximately 28 Vdc at the collector. This output is applied across the input relay reset coils and the stage select reset coils forcing the Switch-Selector into a reset condition.

The duration of the reset pulse is determined by the charge time of capacitor C through base resistor R3 and thermistor RT1. When C charges sufficiently, the power inverter is turned off and the reset pulse is removed from the reset coils.

The automatic reset pulse initiated by the read command is developed exactly the same as the "Power ON" reset pulse. When the read command is issued, the normally open read command relay contact closes, and the normally closed read command relay contact opens. This allows capacitor C to discharge through resistor R1. The power inverter remains turned off (due to lack of base drive)

Figure 2-5. Automatic Reset Circuitry, Simplified Diagram

until the read command is removed. When the read command is removed, the read command relay contacts return to the reset condition. At this time, capacitor C begins to charge providing base drive for the power inverter. The power inverter turns on, producing an output of approximately 28 Vdc at the collector. The output is applied across the input relay and stage select relay reset coils forcing the Switch Selector into the reset condition as shown in Figure 2-4.

As previously stated, the duration of the reset pulse is determined by the charge time of capacitor C through base resistor R3 and thermistor RT1. When C is sufficiently charged, the power inverter is turned off and the reset pulse is removed from the reset coils.

#### Decoding Matrix

The decoding matrix is comprised of PNP inverters, NPN inverters, and AND circuits arranged so that selection of a particular output channel can be made by either the true or complement input code.

This matrix can be divided into three sections as follows (see Figure 2-4):

AND gate circuitry

Row decoder

Column decoder

The object of these circuits is to generate a particular column and row signal for each input code and to send these signals to the output matrix upon receipt of the read command signal.

The 8-bit coded command is transferred to the decoding matrix by operation of the input relay contacts. When a binary "1" is applied to an input relay set coil, the normally open input relay contact closes and the normally closed input relay contact opens.

This causes stage ground to be switched from the verify relay reset coil to the verify relay set coil. The bit NOT input to the decoding matrix is now tied to stage ground, while the bit input line to the decoding matrix is at stage + 28 Vdc. When a binary "0" is applied to an input relay set coil, the input relay contacts remain in the reset condition. With the input relay contacts in the reset condition, the bit NOT input to the decoding matrix is at stage + 28 Vdc and the bit input to the decoding matrix is a 0 Vdc.

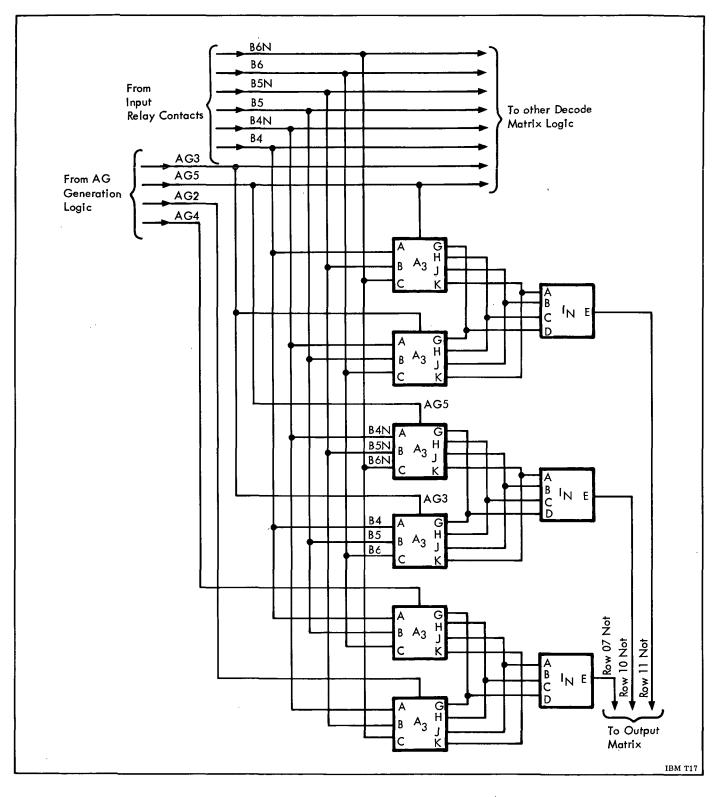

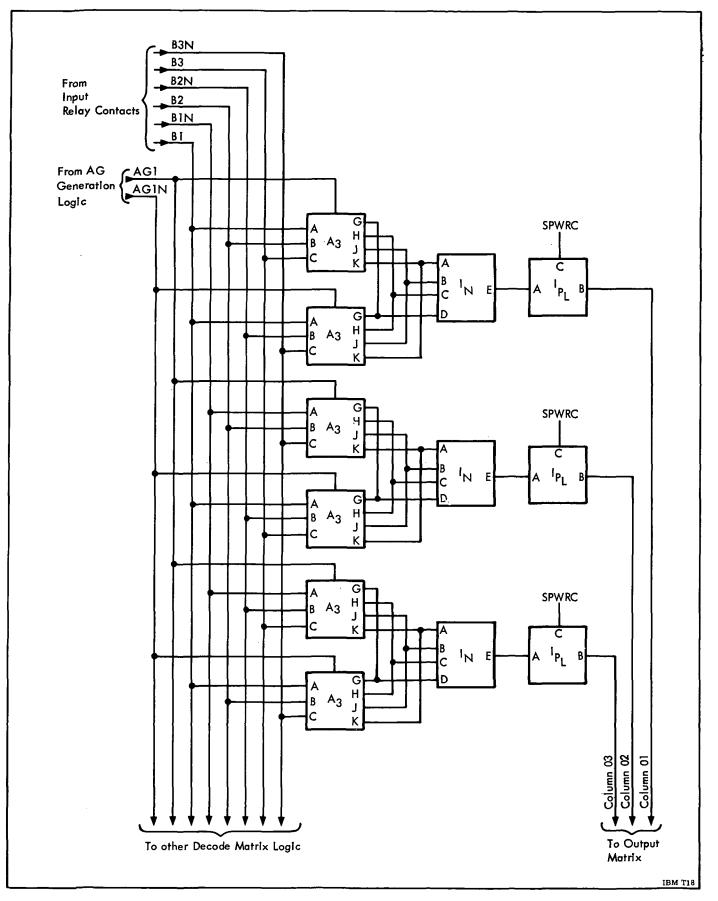

The 8-bit command is sub-divided into groups for decoding and output driver selection. The least three significant bits (1, 2 and 3) are decoded to enable the column selection circuitry. The next three bits (4, 5 and 6) are decoded to enable the row selection circuitry. Bits 7 and 8 and SPWRA (controlled by read command relays) are applied to the AND gate generator where they are decoded to supply the appropriate AND gates to the column and row decoders. Bit 8 is applied to the AND gate generator where it is decoded to determine whether the coded command is a true or complement word. The listing below illustrates the Boolean expressions for decoding bits 7 and 8.

| AG1  | = | B8 · Read Command        |

|------|---|--------------------------|

| AG1N | = | B8N $\cdot$ Read Command |

| AG2  | = | AG1 · B7                 |

| AG3  | = | AG1 · B7N                |

| AG4  | = | AG1N·B7N                 |

| AG5  | = | AG1N·B7                  |

where: B8 = Bit 8 = Bit 8 is a binary "1".

B8N = Bit 8 NOT = Bit 8 is a binary "0".

When decoding a typical word (01010101) where bits 8 through 1 are arranged from left to right, the column is determined by bits 8, 3, 2 and 1, or 0101, or more completely by AG1N · B3 · B2N · B1. Similarly, the row is determined by bits 8, 7, 6, 5, and 4, or 01010, or more completely AG5 · B6N · B5.B4N. However, if the input register transfer circuitry shows a failure, the complement of the original word must select the same output channel in the output matrix. Therefore, the location defined by 01010101 must also be defined by 10101010. This complement code is decoded in the same manner as the original code. The column is determined by bits 8, 3, 2, and 1, or 1010, or more completely by  $AG1 \cdot B3N \cdot B2 \cdot B1N$ . The row is determined by 8, 7, 6, 5, and 4, or 10101, or more completely by  $AG3 \cdot B6 \cdot B5N \cdot B4$ . Therefore, the total expression to define this particular output channel is:

> Channel XY =  $AG1N \cdot AG5 \cdot B6N \cdot B5 \cdot B4N \cdot B3 \cdot B2N \cdot B1$ +  $AG1 \cdot AG3 \cdot B6 \cdot B5N \cdot B4 \cdot B3N \cdot B2 \cdot B1N$

#### **Output Matrix and Telemetry**

The 112 output channels of the Switch Selector are arranged in a 7 by 16 matrix configuration (7 columns and 16 rows). The coordinate selection is similar to the X-Y coincidence method common to core memory technology. An output channel driver (PNP inverter) with the location X-Y in the matrix is activated when the row decoder circuitry (X) and the column decoder circuitry (Y) are turned ON by application of the read command. When activated, the output channel driver produces a + 28 Vdc output to the control circuitry of the selected function.

In addition to producing an output voltage, each output channel driver also produces a separate telemetry output. The 112 telemetry outputs are tied together to produce one switch selector telemetry output signal. This signal is transmitted via PCM and DDAS telemetry. The telemetry signal indicates whether none, one, or more than one output channel is ON at any given time. If one output channel is activated, the telemetry signal will have a magnitude of 2.0 Vdc  $\pm$  20 per cent; if no output channel is active, the telemetry signal will have a magnitude of 0.2 Vdc or less; and if more than one output channel is activated, the telemetry signal will have a magnitude of 3.0 Vdc or more. When the Switch Selector is operating properly, only one output channel will be active an any given time.

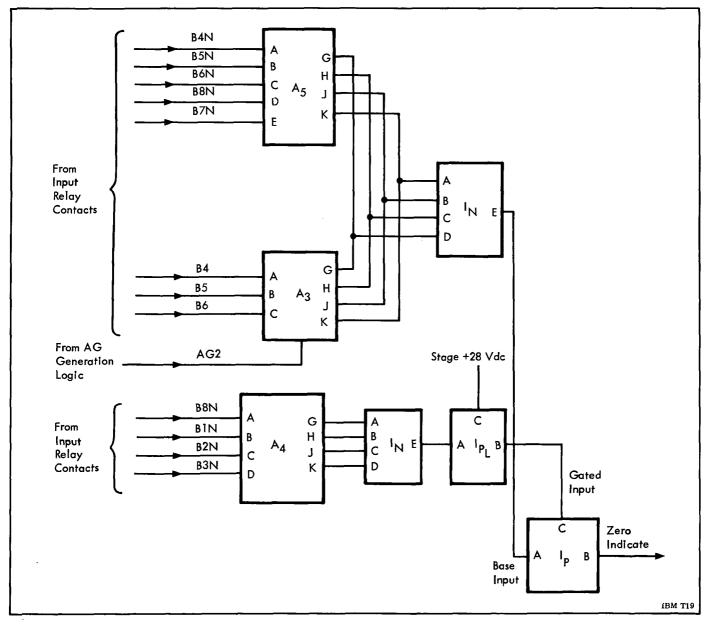

#### **Test Outputs**

In addition to the telemetry output described, each Switch Selector has two telemetry outputs which are used to verify that the input selection relays can be set and reset properly. These signals (register test and zero indicate) are special outputs of the output matrix. The register test output is generated by an output driver when the input address selection is all ones and the read command has been issued. The zero indicate output is generated when the input address selection is all zeros (read command is not required). The zero indicate and register test signals are transmitted via PCM and DDAS telemetry.

#### 2-4 DETAILED OPERATION

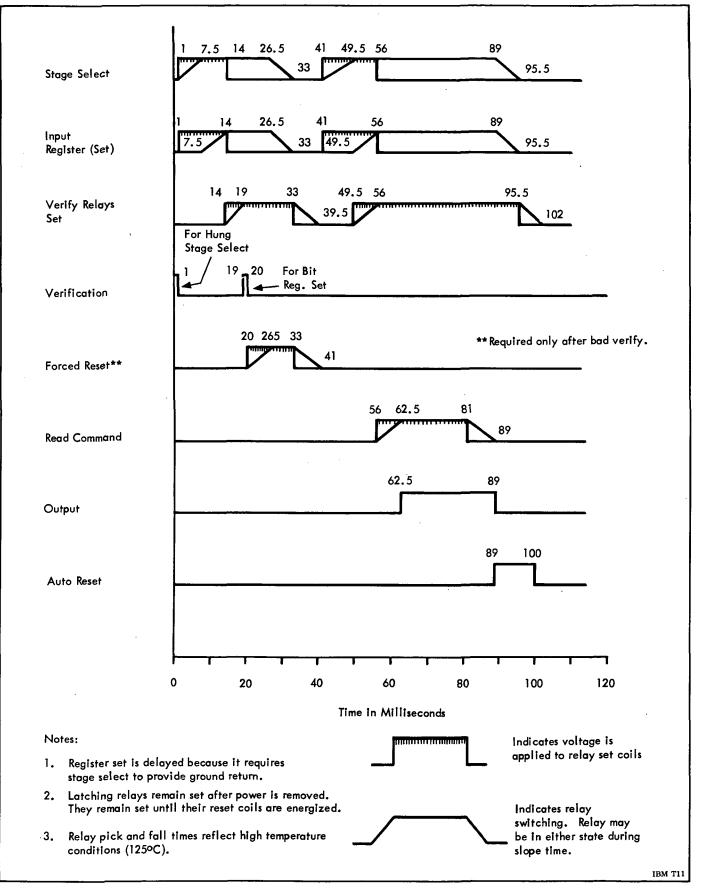

This section contains a more detailed description of the Switch Selector. During this discussion, reference will be made to the timing diagram, Figure 2-6, the simplified schematic diagrams, Figures 2-7 through 2-15, and to the detailed schematic diagram, Figure 2-16.

Figure 2-6. Typical Switch Selector Timing Diagram

Switch Selector Section II

. \*

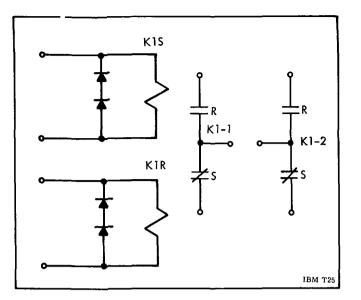

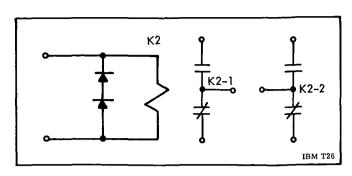

#### 2-5 STAGE SELECT

The stage select command is the signal which conditions a particular Switch Selector to receive the flight sequence command from the LVDA. Stage select relays K20, K21, and K22 (see Figure 2-16) are magnetic latch relays. One side of each relay coil is attached to the input line carrying the stage select command from the LVDA. The other side of each coil is connected to IU signal return.

Application of the stage select command energizes the set coils of the stage select relays. After a 5-millisecond relay pick time, the stage select relay contacts close (see Figure 2-6). Closure of contacts K20-2, K21-1, K21-2 and K22-2 (see Figure 2-16) complete the circuits for (1) the input relays (K1S through K8S), (2) the read relays (K17, K18, K19), and (3) the verify power relay (K24), by tying one side of the relay coils to IU signal return. When relay K24 is energized, contacts K24-2 close completing the circuit that applies stage + 28 Vdc to one side of the set and reset coils of the verify relays (K9 through K16). Operation of relay contacts K22-1 and K24-1 results in IU + 28 Vdc being applied to the contacts of the verify relays (K9 through K16). Thus, operation of the stage select relays allows the 8-bit flight sequence command to be stored in the input relays and prepares the Switch Selector to generate verification information.

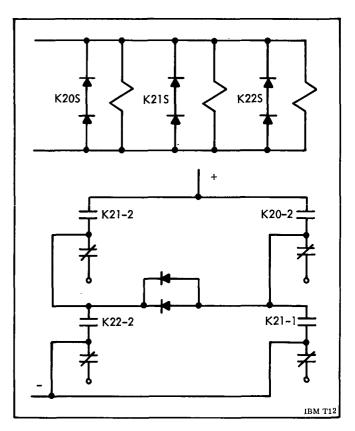

The stage select relays are double-pole, double-throw relays which are wired in a modified triple modular redundant configuration (see Figure 2-7).

This configuration will allow any one of the coils or contacts to fail and still provides a means to effect the desired function. It can be seen that transfer is effected by the proper operation of either K21-1 and K20-2, K22-2 and K21-2, or K20-2 and K22-2 and the diodes. The diodes prevent a failure in the event relay contacts K21-1 and K21-2 fail to open during the reset cycle.

The remaining set of stage select contacts, K22-1, is wired in a simplex configuration (see Figure 2-16). This set of contacts does not require additional redundancy because of the true and complement decoding capability of the Switch Selector. If K22-1 fails to close upon command, the Switch Selector will lose its verify capability and be forced to operate in the complement mode. Stage select contacts K20-1 are not used.

Figure 2-7. Stage Select Relay Configuration

#### 2-6 INPUT RELAYS

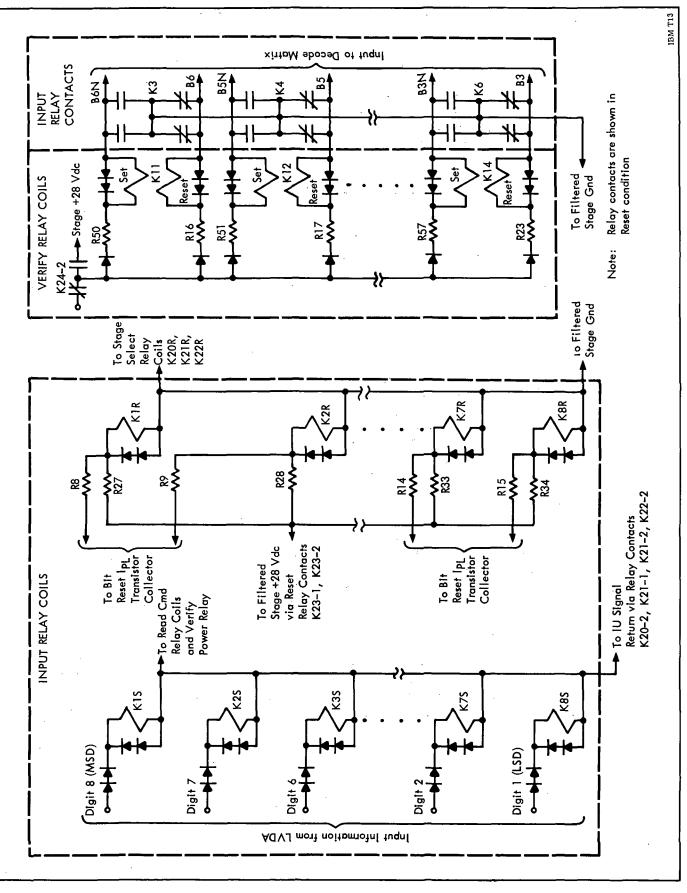

The input relays (K1 through K8) are the relays which receive the coded address from the LVDA (see Figure 2-8). The set coils of these relays are wired between the switch selector register in the LVDA and IU signal return. The reset coils are wired in parallel between stage ground and two separate sources of reset power; the PNP inverters in the automatic reset circuit and stage + 28 Vdc via the forced reset relay contacts K23-1 and K23-2. The contacts of the input relays are located between the decoding matrix and the verify relay coils. Therefore, the condition of the input relay contacts (set or reset) determines the input to the decode matrix and the operation of the verify relay set and reset coils.

The input relay contacts are connected to the verify relay set and reset coils as follows:

| Input Relay Contacts    | Verify Relay<br>Coil Energized |

|-------------------------|--------------------------------|

| Reset closed: Set open  | Reset                          |

| Reset open : Set closed | Set                            |

#### Switch Selector Section II

Figure 2-8. Input and Verify Relay Circuitry

The input relay contacts connect stage ground to one side of either the set or reset coils of the verify relays. This completes the circuit through the coils to stage + 28 Vdc, thereby providing verification information to the LVDA. In addition, the input relay contacts determine how the bit and bit NOT input lines to the decode matrix are conditioned. The following table shows the relationship between the input relay contacts and the inputs to the decode matrix.

| Input Relay   | Bit        | Bit NOT    |

|---------------|------------|------------|

| Contacts      | Function   | Function   |

| Reset closed: | Down level | Up level   |

| Set open      | (0 Vdc)    | (+28 Vdc)  |

| Reset open:   | Up level   | Down level |

| Set closed    | (+28 Vdc)  | (0 Vdc)    |

A down level voltage is obtained on a decode matrix input line when that line is tied to stage ground through the input relay contacts, and an up level voltage exists on the matrix input line which is not tied to stage ground. In the event relay contact K24-2 fails to close, an open circuit at the input to the decode matrix is considered to be an up level voltage.

It should be noted that the stage select command and the coded input command are sent from the LVDA at the same time (see Figure 2-6). However, the input relays will not pick until a maximum of 6.5 milliseconds after the initiation of these signals. The delay is due to the pick time of the stage select relays. It then takes a maximum of 6.5 milliseconds to pick the input relays. This means that after a maximum of 13 milliseconds after initial receipt of the stage select command, power will be applied to the verify relay coils. The power is applied in such a manner that the information contained in the verify relay coils is the coded input command held in the input relays.

The input relays are wired in a simplex configuration. Redundancy is provided by the true or complement decoding capability of the Switch Selector.

Resetting of the input relays will be discussed later under the headings RESET (FORCED) and RESET (AUTOMATIC).

#### 2-7 VERIFICATION

Verification is the process by which the Switch Selector automatically informs the LVDC (through the LVDA) that the correct input command is stored in the input relays of the Switch Selector.

This process is controlled by the operation of the stage select and input relays (see Figure 2-16). The stage select command results in stage + 28 Vdc being applied to the set and reset coils of the verify relays (K9 through K16) and IU + 28 Vdc being applied to the normally closed verify relay contacts (see paragraph 2-5, STAGE SELECT). The coded input address results in the input relay contacts being set to reflect the input address. Upon successful acceptance of the stage select command and the input address, the Switch Selector is fully conditioned to send verification information to the LVDA.

The information sent to the LVDA is determined by the condition of the input relay contacts (see Figure 2-8). When the input relay contacts are in the reset position, the verify relay reset coils are energized and the verify relay contacts remain in their normally closed position. When the input relay contacts are in the set position, the verify relay set coils are energized and the verify relay contacts are switched to the open position.

Thus, to energize the set coil of a verify relay, allowing no voltage to be sent to the LVDA, the corresponding input relay must be set, indicating a binary "1" for that particular bit of the input command. Conversely, to energize the reset coil of a verify relay, allowing + 28 Vdc to be sent to the LVDA, the corresponding input relay must be reset, indicating a binary "0" for that particular bit of the input command. The verification output is therefore the complement of the input command.

Power will be applied to the verification output circuitry a maximum of 13 milliseconds after receipt of the stage select command (see Figure 2-6). However, the verification output for a given input command will not be present until a maximum of 18 milliseconds after the stage select command has been received. This is due to the relay pick times of the stage select, input, and verify relays.

#### 2-8 RESET (FORCED)

One conventional double-pole, double-throw relay, K23, is used to control forced resetting of a

Switch Selector (see Figure 2-16). The forced reset command is issued only if a false verification has been received by the LVDC. When this occurs, it is necessary to clear the information stored in the input relays in order to prepare them to receive the complement of the original input command.

Forced reset is initiated upon receipt of the reset command from the LVDA. The reset command is applied to one side of the reset relay coil, K23. The other side is connected to IU signal return. When the coil of K23 is energized, normally open contacts K23-1 and K23-2 close, applying stage + 28 Vdc to one side of the stage select relay reset coils (K20R through K22R), and to one side of the input relay reset coils (K1R through K8R). Since relays K1R through K8R and K20R through K22R have the other side of their coils connected to stage ground, these relays will be reset. Series limiting resistors R24-R34 protect the reset relay coils agains current surges.

Resetting of the stage select and input relays results in stage ground being applied to the verify relay reset coils K9R through K16R, and power being removed from verify power relay K24. Under these conditions power will be applied to the verify relay reset coils for a period of time equal to the relay fall time of K24. During this time, the verify relays (K9 through K16) will be reset. The Switch Selector is now reset and ready to receive the complement of the original command. The reset cycle is completed 19.5 milliseconds after application of the forced reset command (see Figure 2-6).

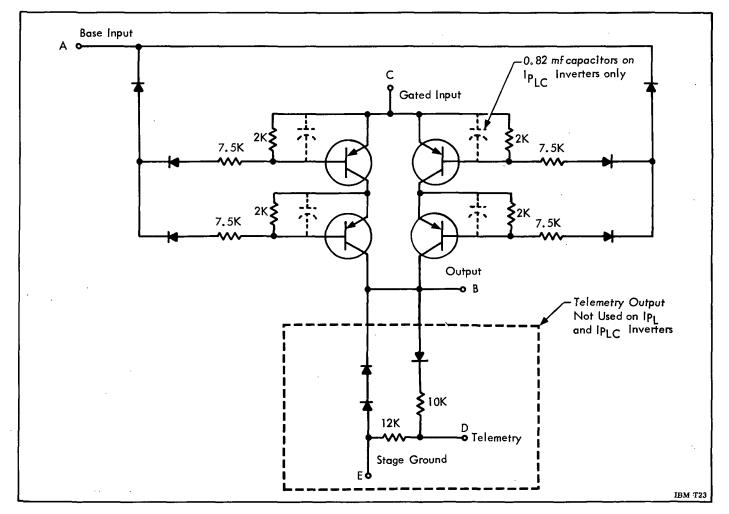

#### 2-9 READ COMMAND

The read command initiates two separate functions in the Switch Selector. First, the read command enables the decode matrix, allowing an output to be generated. Second, the read command initiates the automatic reset cycle.

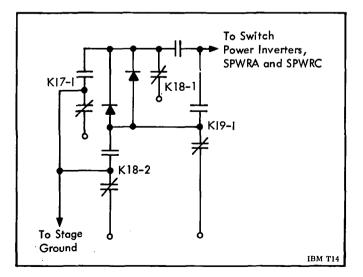

Three conventional relays, K17 through K19, receive the read command from the LVDA (see Figure 2-16). One side of the relay coils is connected to the read command signal; the other side of the coils is tied to IU signal return through stage select relay contacts K20-2, K21-1, K21-2 and K22-2. Because the read command relays are connected to IU signal return through the stage select relays, it can be seen that a stage select command must be received by the Switch Selector before a read command can be accepted. When the read relays are energized, the normally open contacts of K17-1, K18-1, K18-2, and K19-1 close resulting in stage ground being applied to the base circuits of the switch power inverters (SPWRA and SPWRC) in the AG portion of the decode matrix. This allows the decoding process to take place and an output to be generated. The Switch Selector output is present a maximum of 6.5 milliseconds after receipt of the read command and remains until the read command is removed and the read command contacts open (see Figure 2-6).

The read relays are wired in a modified triple modular redundant configuration (see Figure 2-9). This configuration allows any one of the coils or contacts to fail and still provides a means by which the desired function can be accomplished. It can be seen that transfer is effected by the proper operation of either K18-2 and K19-1, K17-1 and K18-1, or K17-1 and K19-2 and the diodes. The diodes prevent a failure in the event relay contacts K18-1 and K18-2 remain closed after the read command has been removed.

Read relay contacts K17-2 and K19-2 are used to control the automatic reset circuitry. The automatic reset function will be discussed in the following paragraph.

#### 2-10 RESET (AUTOMATIC)

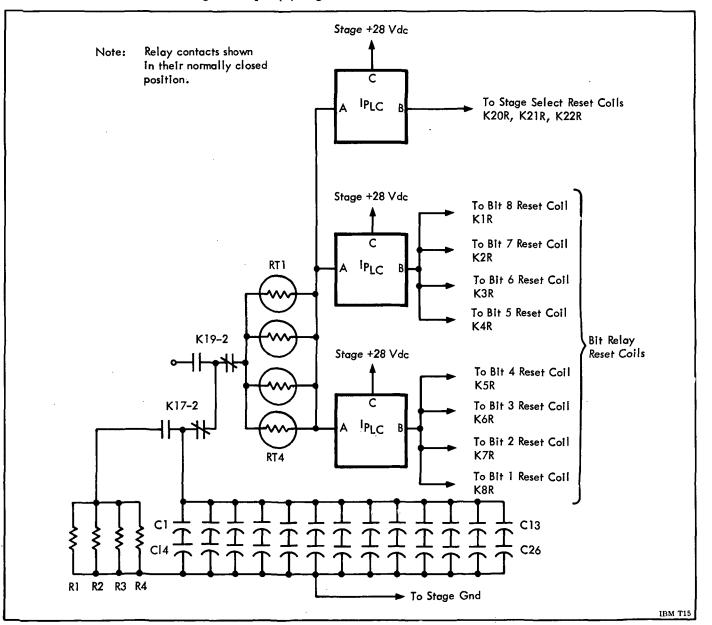

Automatic reset is accomplished by a pulse generated within the Switch Selector. The pulse is

Figure 2-9. Read Command Relay Configuration

initiated by operation of read command relay contacts K17-2 and K19-2 and accomplishes the same function as the forced reset.

A series-parallel network of capacitors, C1 through C26, is connected as shown in Figure 2-10. One side of the network is tied to stage ground; the other side is connected to read command relay contacts K17-2 and K19-2. When these contacts are in their normally closed position, the capacitor network is connected through four parallel thermistors, RT1 through RT4, to the base circuits (A) of three parallel PNP inverters ( $IP_{LC}$ ). (See paragraph 2-14 for a description of the inverter circuit.) If the capacitors are discharged, the inverters will be activated causing the output (B) to go

to approximately stage +28 Vdc. This condition allows the capacitors to charge to stage + 28 Vdc present at the gated input (C) of the inverters. The charge path is through the transistor, transistor base resistor, and the thermistors. The charge time is determined by the equivalent value of these resistances and the equivalent value of the capacitance of the capacitor network. When the capacitors have charged to a voltage equivalent to that needed to shut off the inverter, the voltage at B drops to 0 Vdc. The pulse thus generated at B of the inverters is the automatic reset pulse. These pulses are connected to reset coils K1R through K8R and K20R through K22R through series limiting resistors R5 through R15. The pulse width is equivalent to the time between turn ON and turn OFF of the inverters.

Figure 2-10. Automatic Reset Circuitry

The capacitor network is discharged through resistors R1 through R4 during the read command. When relay contacts K17-2 and K19-2 close, the high side of the capacitor network is connected to one side of the resistor network. The other side of the resistor network is tied to stage ground. The discharge time is determined by the RC time constant of the equivalent resistance of the resistor network and the equivalent capacitance of the capacitor network.

Because the output of the inverters (B) may vary with temperature, 4 thermistors, RT1 through RT4, were placed in the base circuits of the inverters. The thermistors compensate for output variations due to temperature change by adding or reducing resistance in the base circuit, thereby increasing or decreasing the base drive of the circuit as necessary. The effect of this compensation is to maintain a constant charge time and thereby maintain the width of the automatic reset pulse within the allowable design range of 3-1/2 to 12 milliseconds. The RC charge time determines the time duration between turn ON and turn OFF of the inverters.

The capacitor network was purposely made large so that a failure of one capacitor within the network can be tolerated without the automatic reset pulse width being forced out of tolerance, causing the Switch Selector to fail.

The automatic reset pulse commences 8 milliseconds after the read command has been removed (see Figure 2-6). This is due to the time required for the contacts of read command relays K17-2 and K19-2 to return to their normally closed positions.

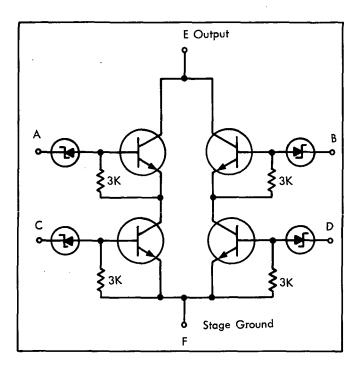

#### 2-11 DECODING MATRIX

The decoding matrix is comprised of PNP inverters, NPN inverters, and AND logic circuits (see paragraph 2-14 for description of electronic circuits). The circuits are arranged so that the input address can be decoded in either its true or complement form.

The output matrix is divided into three sections as follows:

AG generation logic

Row logic

Column logic

The object of these three sections is to generate column and row signals for each input code and to transfer these signals to the output matrix upon receipt of the read command.

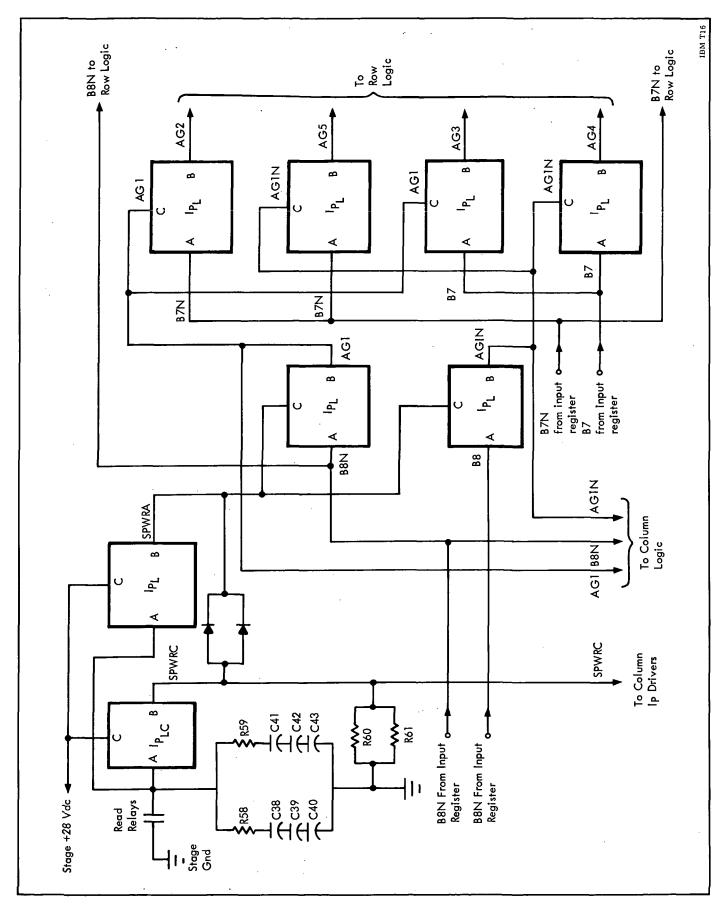

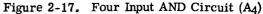

#### AG Generation Logic

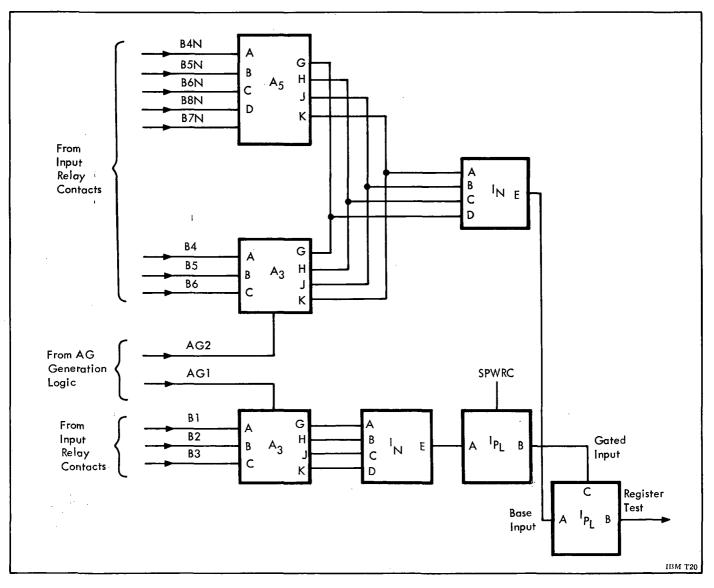

The AND gate circuitry (see Figure 2-11) develops the control signals for the output section of the Switch Selector. These signals (AG1 through AG5) are applied as gated inputs to the row and column decoders, which in turn condition the outpur matrix to produce the desired Switch Selector output.

Operation of the read command relays ties the inputs (A) of the switch power inverters to stage ground, resulting in the generation of the SPWRA and SPWRC signals.

The output of the SPWRA inverter is supplied as the gated input to the PNP inverters  $(I_{PL})$  that generate AG1 and AG1N signals. The binary value of bit 8 of the input code determines whether AG1 or AG1N is generated. Refer to paragraph 2-6, INPUT RELAYS, to determine the manner in which the input relays transfer the input code to the decoding matrix.

If bit 8 (B8) is a binary "1", approximately + 28 Vdc is applied to the input (A) of the  $Ip_L$  that generates AG1N. Since the input is + 28 Vdc, the inverter is turned OFF and the output (B) will be 0 Vdc, thus AG1N is a binary "0". If bit 8 (B8) is a binary "1", bit 8 NOT (B8N) is a binary "0" placing 0 Vdc on the input (A) of the inverter that generates AG1. With the input of the inverter at 0 Vdc, the inverter is turned ON and the output (B) will be + 28 Vdc, thus AG1 is a binary "1".

If the binary values of B8 and B8N are reversed, the inverter action described above will be reversed and the binary value of the AG1 signals will be reversed.

The AG1 and AG1N signals are sent to other  $IP_{L'S}$  to generate the AG2 through AG5 signals. The AG1 signal is applied as the gated input to the  $IP_{L'S}$  that generate the AG2 and AG3 signals. The AG1N signal is applied as the gated input to the  $IP_{L'S}$  generating AG4 and AG5 signals. Therefore, regardless of the binary value of B8 of the input code, two of the four inverters that generate AG2, AG3, AG4, and AG5 are supplied with a gated input. Switch Selector Section II

Figure 2-11. AG Signal Generation Logic

However, it is the binary value of B7 that determines which of the inverters supplied with a gated input is activated.

When B7 is a binary "1" and AG1 is present, + 28 Vdc is applied to the input (A) of the inverter that generates AG3. This signal (+ 28 Vdc) maintains the AG3 inverter in the OFF state making AG3 a binary "0". However, under these same conditions, B7N is a binary "0". When this signal (0 Vdc) is applied to the input of the AG2 inverter, the inverter is activated making AG2 a binary "1".