**E-**1699

SSACHUSETTS INSTITUTE OF TECHNOLOGY

A PROPOSED CIRCUIT STRUCTURE FOR COMPUTER LOGIC BASED ON SEMICONDUCTOR FLAT PACKS INTERCONNECTED BY MULTILAYER CIRCUIT BOARDS

> by Theodore C. Taylor

> > December 1964

E-1699

A PROPOSED CIRCUIT STRUCTURE FOR COMPUTER LOGIC BASED ON SEMICONDUCTOR FLAT PACKS INTERCONNECTED BY MULTILAYER CIRCUIT BOARDS

> by Theodore C. Taylor December 1964

DATE

OPR

PGM SUBJECT

SIGNATOR

# ACKNOWLEDGMENT

This report was prepared under DSR Project 55-191, sponsored by the Manned Spacecraft Center of the National Aeronautics and Space Administration through Contract NAS 9-153.

The publication of this report does not constitute approval by the National Aeronautics and Space Administration of the findings or the conclusions contained therein. It is published only for the exchange and stimulation of ideas.

TOKALI MOR

# TABLE OF CONTENTS

|              |                                                                                                                                                                  | Page |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| I.           | INTRODUCTION                                                                                                                                                     | 3    |  |  |  |

| II.          | PACKAGING SYSTEM CHARACTERISTICS                                                                                                                                 | 4    |  |  |  |

| III.         | PROPOSED STRUCTURE                                                                                                                                               | 6    |  |  |  |

| IV.          | $\operatorname{CONCLUSION} \ldots \ldots$ | 24   |  |  |  |

| V.           | APPENDIX                                                                                                                                                         | 25   |  |  |  |

| BIBLIOGRAPHY |                                                                                                                                                                  |      |  |  |  |

-

.

#### **E-**1699

# A PROPOSED CIRCUIT STRUCTURE FOR COMPUTER LOGIC BASED ON SEMICONDUCTOR FLAT PACKS INTERCONNECTED BY MULTILAYER CIRCUIT BOARDS

### ABSTRACT

The current interest in using weldable, multilayer circuit boards as a means for interconnecting the logic section of an aerospace digital computer has resulted in a study of some utility problems of circuit board structures. In addition to the necessary characteristics of reliability, thermal and structural integrity, manufacturability, and great interconnection capacity, a good circuit structure should also possess such features as small size per component, convenient shape, and convenient means of detailed electrical inspection and repair. A structure is proposed which appears to offer a favorable combination of the desirable features, along with those which are essential. The structure consists of a number of multilayer boards with flat packs mounted thereon, called module boards, and a masterboard, on both faces of which the module boards are mounted in mosaic fashion. The electrical, structural, and thermal integrity of the mosaic is secured by means of fastener hardware, including a special proposed type of leaf spring connector, the leaves of which are compressed between corresponding circuit run pads of a mated master and module board pair. The mosaic structure appears to offer a better distribution of wiring capacity between its two levels of multilayer board than can be offered by the more traditional edge-mounting of modules on a "motherboard". In addition, the mosaic structure allows greater detail in inspection and repair with less disassembly, and provides a modest capability for design modification. A follow-on study of the special connector is proposed.

> by Theodore C. Taylor December 1964

# A PROPOSED CIRCUIT STRUCTURE FOR COMPUTER LOGIC BASED ON SEMICONDUCTOR FLAT PACKS INTERCONNECTED BY MULTILAYER CIRCUIT BOARDS

# I. INTRODUCTION

A study is now in progress to consider the use of weldable, multilayer circuit boards as a basis for constructing the logic section of a computer, wherein the logic design is implemented with semiconductor integrated circuits enclosed in flat-packs. One phase of this study is a continuing effort to appraise the design characteristics, availability, and potential reliability of weldable multilayer boards. This phase involves a modest program of designing, purchasing, examining, and environmental testing of prototype boards. Details describing the test programs to date, and presenting results of analytical examinations and tests are presented elsewhere. (1, 2, 3, 4, 5, 6) Although it is presently known that multilayer boards, whether weldable or not, are subject to some reliability impairing defects which can occur in their manufacture, (see Appendix) it appears that the elimination of such defects is well within the reach of the present state of the art, and may already characterize the product of some manufacturers. Accordingly, a second phase of the study has been activated, to consider important aspects of the use of a number of multilayer circuit boards, combined so as to form an extensive circuit structure. It is the purpose of this report to propose a general method for the integration of a number of circuit boards into a circuit structure which is appropriate for aerospace application requirements, and which also possesses many of the characteristics desirable for the testing, checking, and repairing required in a newly-designed computer. The report will also present some

proposals for a specialized concept in circuit board connectors, new forms of which appear to be essential if substantial advantages are to be derived from a design based on multilayer circuit boards.

The construction scheme to be proposed is one which uses a multilayer board as the basic means of providing both the interconnections between flat packs and the structural and thermal integrity on the level of a single board, or module. In addition, a multilayer board is used in conjunction with special connectors and structural hardware to achieve the required interconnection and structural unification of a number of modular boards. Although the scheme is presented in the context of using weldable module boards, such as the opposed electrode Fusicon<sup>\*</sup> type or the weld-pad equipped parallel-gap type, it is equally applicable to cases where the soldering of flat packs to multilayer boards is preferred.

# II. PACKAGING SYSTEM CHARACTERISTICS

The contemplated use of a computer for control service in an aerospace application imposes a number of both essential and desirable characteristics on its packaging structure. Therefore, before proposing a packaging system, it is appropriate to present a brief listing of those intrinsic characteristics which should be evidenced in any suitable design. The following list is given, together with an acknowledgment that other writers might legitimately disagree with some of the distinctions between those characteristics which are essential and those which are desirable.

# **Essential Characteristics**

1. High reliability of the electrical interconnections and the structural integrity.

\*Trade name of Photocircuits Corp.

- 2. Suitable thermal and environmental designs.

- 3. Feasible (preferably easy) for manufacturing.

- 4. Large capacity for system interface connections.

#### **Desirable Characteristics**

- 1. Small volume, low weight.

- 2. Convenient overall shape.

- 3. Modular subdivision (to limit throwaway and redesign costs).

- 4. Reversibility of assembly (to permit disassembly for inspection and repair).

- 5. Good inspectability at little inconvenience in terms of disassembly.

- 6. Capability for accomodating design changes in the electrical interconnections.

Of those packaging characteristics listed as essential, the derivations of the first three are obvious, since these characteristics are prerequisite to the building and survival of a computer in its intended application. The fourth characteristic, a large capacity for system interface connections, is germane to the specific requirements of a control computer. For example, it has been estimated that the logic structure of an advanced version of the Apollo Guidance computer might require as many as five hundred lines to handle its system interface (control related) signals, while the total of all lines to the memory, to test points, and for power and ground distribution, should not exceed two hundred.

Of those packaging characteristics listed as desirable, the first two are derived from the aerospace application. The third item, modular subdivision, is not only of economic importance in redesign and repair, but also contributes to making design, manufacturing, and testing more manageable operations.

Also, in the case of multilayer circuit boards used for interconnection and structure, modular subdivision is presently the only workable basis for achieving a convenient overall shape in a structure containing a large number of flat packs. For example, the use of presently specified flat pack bodies, of maximum body dimensions 0. 190 by 0. 275 inch, requires a mounting area on weldable circuit boards, allowing for Kovar leads and weld clearances, on the order of 0. 13 square inch for each flat pack. Thus, a typical logic section, containing two-thousand flat packs, would require a mounting area of 260 square inches. The construction of a logic section on a single multilayer board would therefore pose the problem of an inconvenient shape for many applications, which problem is relieved by any scheme of modular subdivision, and stacking of the boards.

The desirable characteristics 4 through 6 are derived from the need for a considerable amount of testing, inspecting, trouble shooting, and repair that is found to be essential in the checking out of a new design, or the diagnosis of such problems as may occur in a more established design. The last characteristic, in particular, is a difficult one to incorporate into a small volume, high reliability structure, since small, reliable conductors and terminals are not, in general, amenable to partial remanufacture within a complex system. For this characteristic, as well as others on the desirable list, all that can be done presently is to make provision in some degree, the usefulness of which must be judged in the light of experience.

# III. PROPOSED STRUCTURE

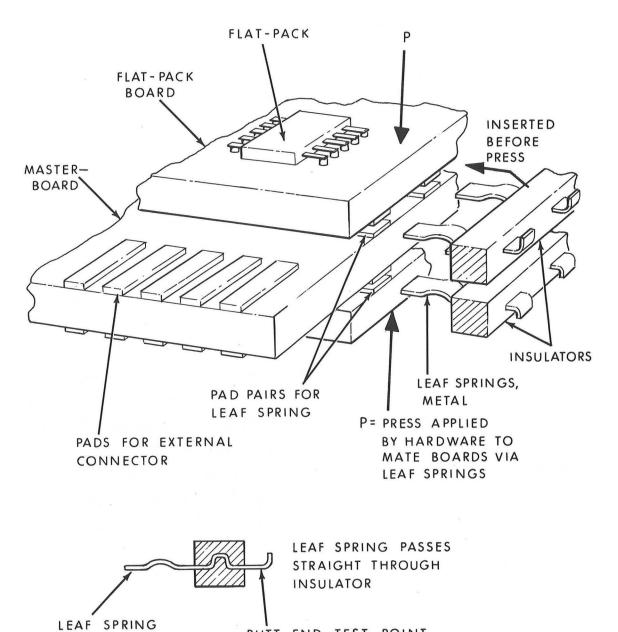

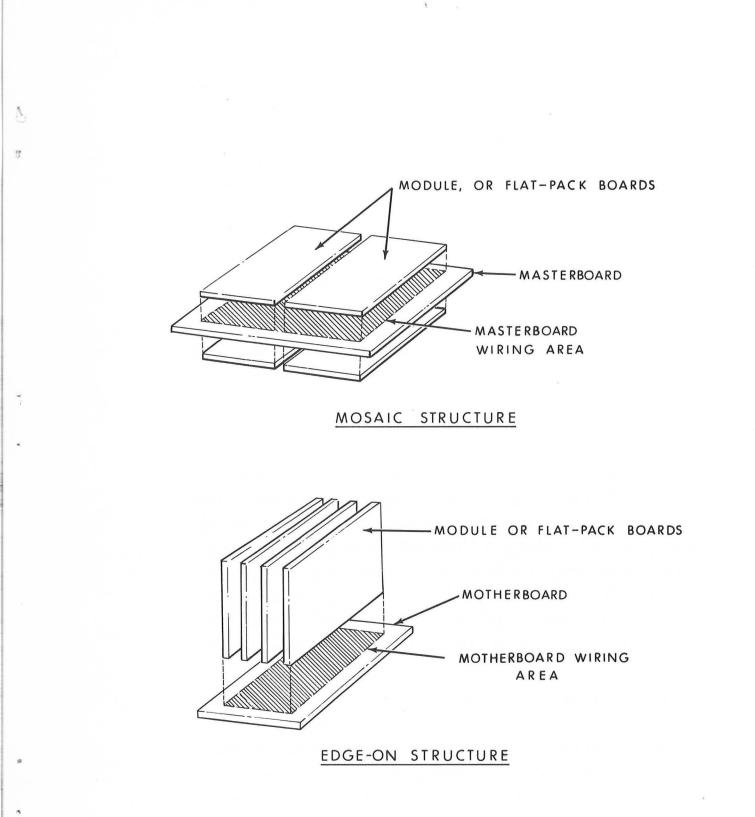

A circuit structure assembly based on multilayer boards which seems to possess all of the essential characteristics, together with a reasonable display of the desirable ones, is illustrated schematically in Fig. 1. In this structure, which can have many geometric variants, the flat pack laden circuit boards are arrayed as a mosaic on each flat face of a masterboard

X

BUTT END, TEST POINT

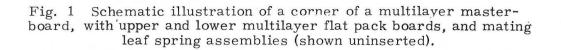

which is used to interconnect them. The mating of the flat pack boards to the masterboard is accomplished by means of a special connector device, to be described in greater detail later in this section. For the present, we describe this connector device as consisting, in the case of an individual contact, of a small curved leaf spring element which bears both on the conductor pad of a flat pack board and on the corresponding conductor pad of the masterboard, by being pressed flat between them. This affords, in the simplest of cases, a two-stage pressure contact between the boards via the leaf spring. Signal lines into and out of the masterboard are taken via a suitable board edge connector, of which there are a number of commercially available versions. This can be done from an edge, or edges, of the masterboard which are unoccupied with the problem of connection to flat pack boards. A variant of the leaf spring connector arrangement, which may be used to free more edges of the masterboard for external contacts, is illustrated schematically in Fig. 2.

Our reason for proposing a structure based on a mosaic of modular boards on a masterboard, rather than the more commonly described system of modular boards mated edge-on to a "motherboard", is three-fold. Firstly, the mosaic arrangement possesses an inherent inspectability and repairability down to the individual flat pack level, without disassembly at the module removal level. This is important if one is to keep patience with a connector device which, although capable of assembly-disassembly when necessary, is primarily designed for manufacturability, simplicity, reliability, and small size. Secondly, the mosaic arrangement can, if properly used in conjunction with the special connectors, result in some space economies, due both to the fact that board interleaving assemblydisassembly is eliminated, and to the fact that certain simplicities in connector design become possible. Thirdly, it has appeared from a study of the two basic arrangements that the mosaic structure has a much better allotment of inter-module wiring

yİ

capacity than the edge-on structure. The relationship between motherboard and masterboard wiring areas is indicated schematically in Fig. 3. In general, every step in the direction of modular subdivision imposes an added problem of inter-module wiring, and the edge-on structure appears to offer some difficulties in the design of motherboards, particularly where the maximum density of input-output lines is used on the mating module boards. Thus, the mosaic structure, if two-sided, has a masterboard wiring area approximately equal to one-half the area of all the module boards relatively uncluttered with module input-output connections, whereas, the edge-on structure has a motherboard wiring area equal only to the edge projection of the module boards and their stacking clearances, and even this area would be riddled with module board connection points. The reason that module board connections affect the useful wiring area of a master or motherboard is that the latter boards, in order to be multilayered, must in general have one platedthrough hole associated with each of their module board connection points. Since the latter must generally be present on the edge of module boards in high density, their restriction on the wiring capabilities of a small plan-area motherboard can be severe. The one feature of edge-on assembly which is most attractive is its design flexibility for producing more compact final assembly shapes than are feasible with the mosaic structure.

Experience with the design of multilayer circuit boards for service in the logic section of digital computers has shown that a large number of input-output lines to modular boards is usually required. It is therefore desirable to employ a standardized, basic shape for the modular board which provides a goodly amount of peripheral access to accomodate the input-output requirements. Further, considerations of thermal design, assembly, and disassembly may make it undesirable to involve more than a single edge of a modular board with its input-output access. It is therefore desirable to use a modular board shape

Fig. 3 Schematic illustration comparing a four module structure in mosaic (upper) and in edge-on (lower)arrangements. Note the greater wiring area in the mosaic masterboard. such as a rectangle of aspect ratio (length-to-width ratio) greater than one, so that a long edge is available for input-output access.

Consider a rectangular module board, of aspect ratio r, and having an area sufficient to mount n flat packs, such that the area is A = kn, where k is the required area per flat pack. If we crudely assume that the number of input-output lines required of a board is proportional to the number of flat packs on it, and that these lines will all be taken on one long edge of the board, then the ratio of the length of that edge to the area of the board must be independent of the area of the board, or

$$\sqrt{\frac{r}{kn}} = constant.$$

Thus,

$\left(\frac{\mathbf{r}}{\mathbf{n}}\right) = \text{ constant,}$

so that, the aspect ratio of the modular board must be proportional to the number of flat packs it holds. Assuredly, this is a very crude model, since the number of input-output lines is a function of the nature of the circuits, and also is expected to decrease as the modular subdivision of a computer logic section becomes less fine. Therefore, there should be a point in module size beyond which increases in number of input-output lines would not be as rapid as in direct proportion to module size. Nevertheless, it seems clear enough that large modules should, in general, be designed for a large aspect ratio. The interest in large modules derives from the fact that even though some modular subdivision is desirable, it is not desired that the structure be so finely divided as to suffer from the great volume penalty or reliability jeopardy that can result from large numbers of module connectors.

Similarly, the aspect ratio of a masterboard, as used in the mosaic structure, preferably should be such as to allow the input-output lines from the logic structure as a whole to be taken off one long edge of the board. If this is not possible, then

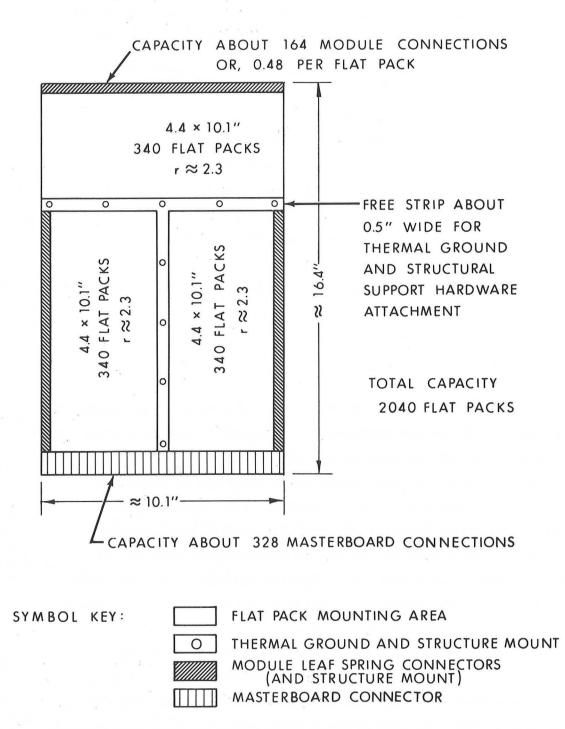

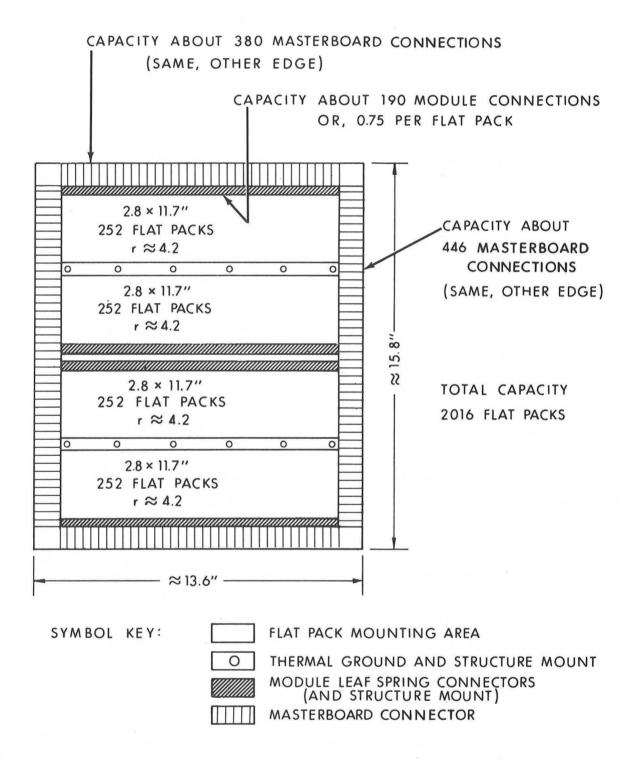

Fig. 4 Schematic map of a six module board mosaic structure, using the leaf-spring connector of Fig. 1 and three module boards on each face of the masterboard. Thickness of the structure, without covers is about one-half inch. the use of two adjacent edges would render the concept of aspect ratio, as applied to the masterboard, less important. In the absence of specific packaging design requirements, it would seem most fruitful to consider some general properties of mosaic arrangements, as they might be applied to a logic structure containing two-thousand flat packs.

The present state of the arts in both multilayer board fabrication and external connector fabrication are able to offer a density of input-output connections along a board edge, at either the module board or masterboard level, of about twenty per lineal inch. For the type of leaf spring connector shown schematically in Figures 1 and 2, some associated hardware parts to be described later will lower this density somewhat, resulting in a density estimated at 18 per lineal inch. For a masterboard, however, the connector is working at a true external periphery of the entire structure, so that it should be easy to design a connector which simultaneously contacts two electrically independent input-output pads, one on each face of the board. Thus, if an allowance is made of ten percent (as used above) of the edge for structural hardware, the net realized connector point density on the masterboard is approximately 36 per lineal inch. Figures 4 and 5 illustrate two examples of the mosaic structure for a logic section of about 2000 flat packs, based upon these densities. It may be noted that the leaf spring connector of Figure 1 requires access to an outside edge of the masterboard, and thus limits the edge length available for external connectors to the masterboard. In constructing the examples, an estimate has been made that a leaf spring connector and associated pads on the module board would require a total width of 0.375 inch, not available for mounting flat packs, and the flat pack mounting area has been taken as 0.4 by 0.325 = 0.13square inch. External connector pads on the masterboard are estimated as 0.1875 (3/16) inch wide. The size of the external connector is also included, estimated to overhang the edge of

Fig. 5 Schematic map of an eight module board mosaic structure, using the leaf spring, connector of Fig. 2, and four module boards on each face of the masterboard. Thickness without covers, about one-half inch.

the masterboard by about 0.8125 (13/16) inch to allow for some external cabling requirements on the connector back.

The plan area dimensions shown in the figures do not include edge covers for connectors, but do include all necessary internal structure. The leaf spring connectors, to be described in more detail shortly, include a structural supporting effect, so that each module board is supported and tied down to the masterboard along both of its long edges. The overall thickness of the two level mosaic structures, allowing 0.1 inch thickness for each of the three circuit boards, and 0.1 inch for each level of flat packs and leaf spring connectors, is about one-half inch. This does not include plan-area cover plates, whose thickness would depend on thermal design requirements, but a very generous allowance for them should result in a total thickness under one inch.

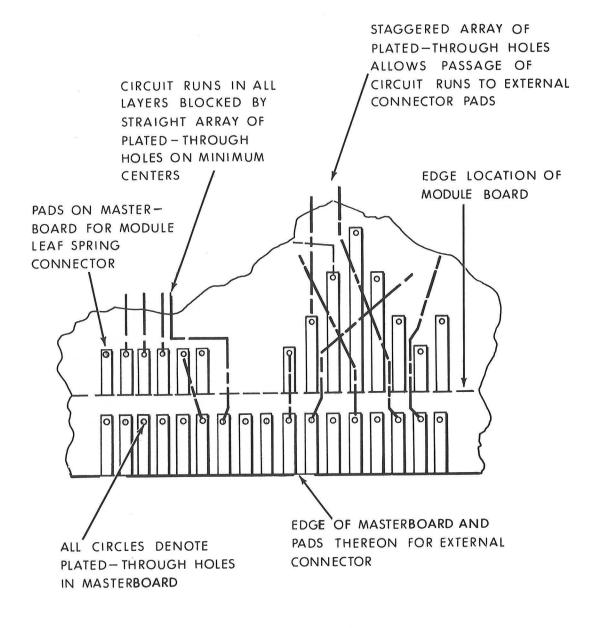

In comparing Figures 4 and 5, it may be noted that the use of the connector of Fig. 2 (in the mosaic of Fig. 5) together with the increased module board aspect ratio which it allows, has resulted in a substantial increase of available connector points, both on the level of the module board, and that of the masterboard. This has been accomplished by the fact that the Fig. 2 connector design frees up the edge of the masterboard, and allows any or all of its edges for external connector use. In general, the use of the Fig. 2 connector will require one more layer of circuitry in the masterboard than is required by the Fig. 1 connector. This is true because the plated-through holes associated with module board contact pads on the masterboard cannot be located in a straight line on 0.050 in. centers, as the pads themselves must be. If they were, these holes, on 0.050 inch centers, would block the passage of masterboard circuitry in all of its layers through the straight, unbroken line of plated-through holes on minimum centers. The extra layer, then, offsets the row of masterboard pads into an array of plated-through holes which is spaced to allow the passage of circuitry in all masterboard

1

Fig. 6 Illustration showing the need for an offset array of platedthrough holes of the pads on the masterboard, for mating with the module board connector of Fig. 2. The offset allows access of the circuit runs in the masterboard to external connector pads, or greater freedom in routing masterboard conductors. layers. The situation is illustrated schematically in Fig. 6. Of course, this extra layer may frequently have room for performing other interconnection functions as well, so that its presence in a finished design might not be recognized as a bona fide "extra" layer, except by the fact that its conductor runs are necessarily exposed, rather than imbedded in plastic.

Obviously, there is infinite variety to the mosaic patterns which might be used, the illustrations of Figures 4 and 5 being merely examples of two which are based upon a standardized shape and size of module board. If circumstances warranted it, there is no reason why mosaics could not be designed based upon a variety of module board shapes and sizes within a single mosaic structure.

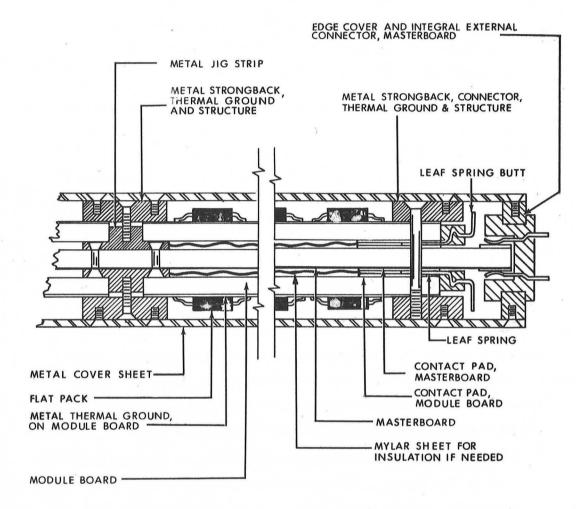

Having indicated the general architectural features of typical mosaic structures, it is now appropriate to present the details of the structure, particularly insofar as the assembly involves the connector hardware and thermal/structural hardware. The important details are presented in the schematic section of Fig. 7, which indicates the mating of a pair of module boards to their associated masterboard.

With the structure entirely assembled, as shown, the only points of electrical test available are the pins of the external connector, at the right hand edge of the Figure. With removal of the metal cover plates and their holding screws, a significantly greater degree of inspectability and testability develops, even though the structure is electrically fully assembled. With the cover plates removed, the inspector has access to the leaf spring butts as well as the leads of each flat pack. He may therefore test probe at the flat pack level, the module board connector level, and the external connector level. By using parallel-gap welding techniques, he may even effect removal and replacement of flat packs at this level of disassembly. If module board removal or replacement should be necessary, the structure may be disassembled completely by removing the

Fig. 7 Schematic illustration of the details, in edge view section, of a mosaic structure. Overall thickness is approximately 0.6 in.

connector strongbacks and their holding screws.

In addition to the extensive inspectability and repairability, the structure also has a modest capability for rewiring at the module board level. This may be accomplished by means of point-to-point wiring added at the component level on the module boards, or by means of point-to-point wiring added between the leaf spring butts on any module board connector.

The thermal grounding circuit of the structure is unusually straightforward. The first conductor in this circuit is a perforated metal sheet, laminated to the module board, which underlies all of the flat packs except in the area of weld pins or weld pads. Two edges of this sheet are fayed to the metal strongbacks, which are, in turn, fayed to the metal cover plates. The outside surface of the latter may in some cases be the area of application of an external cooling effect, or the cover plates may otherwise be used as conductors to convey heat to some more locally concentrated cooling effect. Their thickness, proportioning, and material are subject to design alteration, based upon the details of their thermal function. It is important to note, however, that major changes could be made in this aspect of the thermal circuit, without any changes whatever in the more internal features of the structure.

It may also be noted that the proposed leaf spring connector permits a reasonable degree of flexibility in the design of the module boards, in that it does not require a standardization of the module board thickness. Thus, depending on wiring density requirements, the different module boards of a given mosaic could each have different numbers of conductor layers in them, with different resulting thicknesses, the differences being accommodated by grinding corresponding thickness dimensions on the metal strongbacks, and on the metal ridges of the external connector.

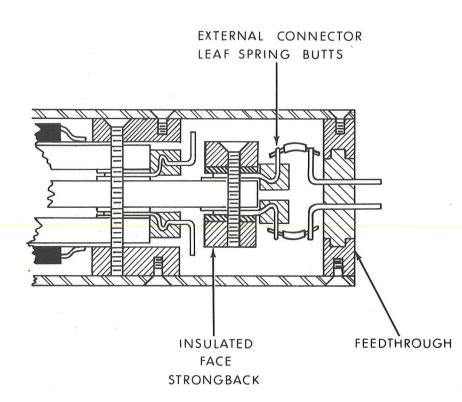

For the external connector design shown, it is necessary to standardize the design thickness of the masterboard. It is possible, however, to design an external connector which would accommodate design changes in the masterboard thickness, as shown schematically in Fig. 8. This arrangement uses leaf spring connectors fayed between strongbacks and the masterboard pads, wherein the strongbacks must be of insulating material, or have an insulated faying surface. Design changes in the module board and masterboard thicknesses are here accommodated entirely by tailored grinding to thickness of the module board strongbacks and the metal ridges of the feedthrough. Although this external connector scheme is more bulky than that of Fig. 7, it adds another possibility for wiring modification, by means of point-to-point wiring at the interface between the external connector leaf spring butts and the feedthrough pins.

It will be noted that the connector designs advocated for use with the mosaic structure are somewhat unusual, in that they derive their structural integrity in large measure from the parts which mate to them, and the associated hardware. Thus, the connector structure must in fact include the leaf spring assembly, the mating module and masterboards, and the associated strongbacks and screws which hold them together, before the whole can be considered an existing circuit closure, or connector. Therefore, one does not promiscuously assemble and disassemble the connector structure, as might be the case with more conventional designs. It is expected that the high degree of inspectability and repairability of the mosaic structure with cover plates removed will make the disassembly of connectors an infrequent event. There are, of course, advantages anticipated from the use of this unusual connector design. First, it will be noted that the faying together of a number of boards, strongbacks, and leaf springs makes possible the multiple purpose usage of the same materials, or parts.

Fig. 8 Schematic illustration, in edge view section, of an external connector and feed through arrangement alternative to that of Fig. 7. The device above allows for using master-boards of different thicknesses.

Thus, the connector assembly may simultaneously function as a circuit closure, a structural tie-down between one edge of a module board and the masterboard, and an element of the thermal circuit by thermally connecting the module board to the external cover plates. All three functions can be accomplished with a total usage of material, or bulk, that would ordinarily be used just to provide circuit closure by means of conventional connector designs. Second, it may be noted that the design does not use leaf spring deflection as a primary means of establishing electrical contact pressure. Although an originally curved leaf spring is indeed deflected to flatness on assembly, the final contact pressure is developed by the more substantial strongbacks and screws, which apply compressive force to elastically deform the multilayer glass-epoxy boards, and compress the springs between them. Thus, contact pressures are expected to be substantially higher than those available from connector spring elements alone, with a corresponding prospect of higher electrical contact reliability. The elastic deflection mechanism is built into the leaf springs simply to provide a small amount of wiping action on assembly, and to give a reserve of residual contact pressure, in the event of a substantial amount of loosening of the assembly. A third advantage, that these special connectors can be used with circuit boards of any and all thicknesses, has already been discussed. A fourth advantage is that the leaf spring and insulator bar is inherently susceptible to design standardization, and to inexpensive manufacturing techniques.

At present, there are a number of unexplored questions which might legitimately be asked about this special connector type. However, it is thought to be sufficiently promising to warrant a follow-on study which will consider such items as manufacturing techniques, stress-deflection studies, contact metallurgy, and configuration details. It is known, for example, that the requirement for an occasional location pin, as well as for a regular array of strongback screws, will affect the

maximum density of connector contacts which can be attained. In the estimates of packaging sizes given earlier (figures 4 and 5) this effect was taken as a ninety percent effectiveness on the total connector length, although a more accurate value will have to await a stress-deflection analysis of the structure.

# IV. CONCLUSION

It is proposed that the mosaic structure, based on multilayer circuit boards, affords a reasonable basis for the development of a computer logic assembly, or subassembly, which offers substantial promise in terms of the essential and desirable characteristics enumerated in Section II of this report. It is apparent, however, that the success of such a development depends critically on the availability both of reliable multilayer boards and of the reliable connector devices of the leaf spring type. The development and initial sales of weldable multilayer boards is currently underway in at least three industrial companies, and our laboratory is engaged in a program to evaluate their product. At present, it seems quite likely that a product of this type will be available in time for incorporation into a mosaic structure development. It would seem necessary, however, to initiate a connector development program, if the connector that is most appropriate to the mosaic structure is to be made available when needed. Therefore, the Advanced Study Laboratory, Digital Development Group, is presently mapping out a feasibility study of the leaf spring type of connector. The findings of this study will be the subject of a follow-on report.

#### V. APPENDIX

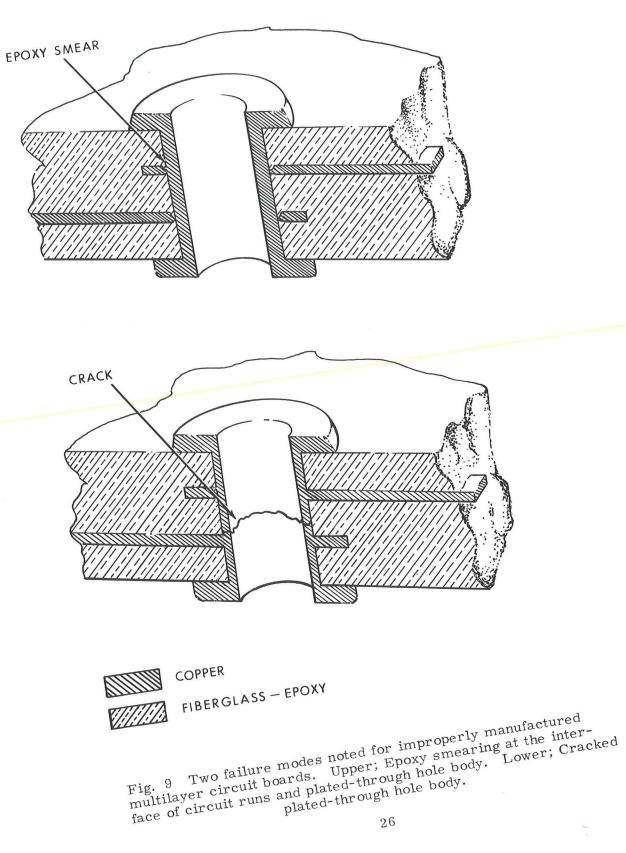

Our experiences to date with the environmental testing of multilayer circuit boards has exposed two failure modes which can occur in structures of this type. The two possible failure modes are illustrated in schematic section in Fig. 9, and are both the result of faulty manufacturing procedures. The epoxy smear type of failure is a result of the smearing of epoxy material over the inner surface of a conductor land, when the latter is drilled prior to the generation of the platedthrough hole body. In proper manufacturing, an etching process which attacks epoxy at a greater rate than copper is used to clean off such smeared material prior to plating of the hole body. If this etching is omitted, or is insufficient in extent, then epoxy may be present in a portion of the conductor land to hole body interface, as illustrated in the upper half of Fig. 9. Subsequently, the small amount of copper-to-copper bond area may be overstressed and fractured, due to the fact that the epoxy is present in a wedging position between the copper parts, and due to the fact that the epoxy has so much larger a coefficient of thermal expansion than does the copper. Thus, the first symptoms of this class of fault have been detected in the course of thermal cycling, either as an increasing resistance between a circuit run and a hole body, or as an open circuit. One might wonder at the fact that such a thermal expansion mechanism could fracture a piece of copper, when the latter is a metal of such great ductility. A possible explanation is that the copper is a coarse-grained electrodeposit, and the contact can be, in severely smeared cases, very small in area. Thus, the entire area of the copper-to-copper bond can consist of the boundary between a pair of adjacent grains. Ductility values based on the stress-strain study of macroscopic samples obviously do not apply to the situation described.

The second type of failure is illustrated in schematic section in the lower half of Fig. 9. This failure consists of a

cracking of the plated-through hole body, which is probably also caused by the differential thermal expansion between that copper body and the surrounding mass of glass-epoxy in which it is imbedded. Here again, the grain structure of the copper is probably important. It has been found that the use of hole body wall thicknesses on the order of 0.002 inch and greater eliminates this problem, whereas it can occur at thicknesses on the order of 0.001 inch. The failure is electrically manifest as a high resistance, or open circuit between the upper and lower lands of the plated-through hole.

There are, of course, other possible ways in which a multilayer circuit board might fail in service, or be found defective at incoming inspection. The two described above are presented only as examples which have been encountered to date, for which the manufacturing remedy is believed to have been found.

### BIBLIOGRAPHY

- T. C. Taylor, Digital Development Memo #82, "Evaluation of the Photocircuits Corp. Weldable Circuit Board", 23 April 1963.

- T. C. Taylor, T. A. Zulon, Digital Development Memo #151, "Technology of Manufacturing the Fusicon Multilayer Circuit Boards", 11 December 1963.

- T. A. Zulon, Digital Development Memo #182, "Environmental Test Results on Fusicon Multilayer Circuit Boards", 27 April 1964.

- T. A. Zulon, Digital Development Memo #204, "Environmental Test Results on Fusicon Multilayer Circuit Boards", 24 June 1964.

- 5. T. C. Taylor, T. A. Zulon, Digital Development Memo #221, "Loose Pins in Fusicon Boards", 18 November 1964.

- T. A. Zulon, Digital Development Memo #227, "Environmental Test Results on Melpar Parallel-Gap Weldable Multilayer Circuit Boards", 1 December 1964.

#### E-1699

# DISTRIBUTION LIST

| -     |      |          |

|-------|------|----------|

| Int   | 0 20 | nal      |

| ITTT. | E.L. | Id       |

|       | ~ -  | T T CO M |

R. Alonso L. Larson J. Lawrence (MIT/GAEC) J. Arnow (Lincoln) T.J. Lawton R. Battin T.M. Lawton (MIT/MSC) P. Bowditch R. Boyd D. Lickly G. Mayo R. Byers J. McNeil E. Copps R. Crisp James Miller J. Dahlen John Miller J. Nevins E. Duggan K. Dunipace (MIT/AMR) J. Nugent J.B. Feldman E. Olsson S. Felix (MIT/S&ID) R. Scholten Eldon Hall E. Schwarm I. Halzel N. Sears D. Hanley D. Shansky W. Shotwell (MIT/ACSP) E. Hickey W. Stameris D. Hoag A. Hopkins J. Stone F. Houston T. Taylor (4) L.B. Johnson M. Trageser A. Koso R. Weatherbee M. Kramer L. Wilk W. Kupfer R. Woodbury D. Ladd W. Wrigley A. La Pointe Apollo Library (2) J. Larsen MIT/IL Library (6)

| External                                                                                                                                                               | MSFC: | (2)                                                                                                                                                                        |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| (ref. PP1-64; April 8, 1964)                                                                                                                                           |       | National Aeronautics and Space Administration                                                                                                                              |      |

| P. Ebersole (NASA/MSC)                                                                                                                                                 |       | George C. Marshall Space Flight Center<br>Huntsville, Alabama                                                                                                              |      |

| W. Rhine (NASA/RASPO)                                                                                                                                                  | (1)   | Attn: R-SA                                                                                                                                                                 |      |

| L. Holdridge (NAA S&ID/MIT)                                                                                                                                            | (1)   | ERC:                                                                                                                                                                       | (1)  |

| T. Heuermann (GAEC/MIT)                                                                                                                                                | (1)   | National Aeronautics and Space Administration                                                                                                                              |      |

| AC Spark Plug                                                                                                                                                          | (10)  | Electronics Research Center<br>575 Technology Square                                                                                                                       |      |

| Kollsman                                                                                                                                                               | (10)  | Cambridge, Massachusetts                                                                                                                                                   |      |

| Raytheon                                                                                                                                                               |       | Attn: R. Hayes/A. Colella                                                                                                                                                  | (1)  |

| Major W. Delaney (AFSC/MIT)                                                                                                                                            |       | GAEC:                                                                                                                                                                      | (1)  |

| NAA RASPO:                                                                                                                                                             | (1)   | Grumman Aircraft Engineering Corporation<br>Bethpage, Long Island, New York<br>Attn: Mr. A. Whitaker                                                                       |      |

| National Aeronautics and Space Administration                                                                                                                          |       | NAA:                                                                                                                                                                       | (15) |

| Resident Apollo Spacecraft Program Office<br>North American Aviation, Inc.<br>Space and Information Systems Division<br>12214 Lakewood Boulevard<br>Downey, California | (2)   | North American Aviation, Inc.<br>Space and Information Systems Division<br>12214 Lakewood Boulevard<br>Downey, California<br>Attn: Mr. R. Berry                            |      |

| FO:                                                                                                                                                                    | (3)   | GAEC RASPO:                                                                                                                                                                | (1)  |

| National Aeronautics and Space Administration,<br>Florida Operations, Box MS<br>Cocoa Beach, Florida 32931<br>Attn: HB 23/ Technical Document Control Offic            |       | National Aeronautics and Space Administration<br>Resident Apollo Spacecraft Program Officer<br>Grumman Aircraft Engineering Corporation<br>Bethpage, Long Island, New York | (-)  |

| HDQ:                                                                                                                                                                   | (0)   | ACSP RASPO:                                                                                                                                                                | (1)  |

| NASA Headquarters<br>600 Independence Ave., SW<br>Washington 25, D.C. 20546<br>Attn: MAP-2<br>AMES:                                                                    | (2)   | National Aeronautics and Space Administration<br>Resident Apollo Spacecraft Program Officer<br>Dept. 32-31<br>AC Spark Plug Division of General Motors                     | (-/  |

| National Aeronautics and Space Administration                                                                                                                          |       | Milwaukee 1, Wisconsin<br>Attn: Mr. W. Swingle                                                                                                                             |      |

| Ames Research Center<br>Moffet Field, California<br>Attn: Library                                                                                                      |       | WSMR:<br>National Aeronautics and Space Administration                                                                                                                     | (2)  |

| LEWIS:<br>National Aeronautics and Space Administration                                                                                                                | (2)   | Post Office Drawer MM<br>Las Cruces, New Mexico<br>Attn: BW 44                                                                                                             |      |

| Lewis Research Center<br>Cleveland, Ohio                                                                                                                               |       | MSC:                                                                                                                                                                       | (45) |

| Attn: Library                                                                                                                                                          | (1)   | National Aeronautics and Space Administration<br>Manned Spacecraft Center<br>Apollo Document Control Group                                                                 |      |

| National Aeronautics and Space Administration                                                                                                                          |       | Houston 1, Texas 77058                                                                                                                                                     |      |

| Flight Research Center<br>Edwards AFB, California<br>Attn: Research Library<br>LRC:                                                                                    | (2)   | Mr. H. Peterson<br>Bureau of Naval Weapons<br>c/o Raytheon Company<br>Foundry Avenue                                                                                       | (1)  |

| National Aeronautics and Space Administration                                                                                                                          | 3     | Waltham, Massachusetts                                                                                                                                                     |      |

| Langley AFB, Virginia<br>Attn: Mr. A. T. Mattson<br>GSFC:                                                                                                              | (2)   | Queens Material Quality Section<br>c/o Kollsman Instrument Corporation<br>Building A 80-08 45th Avenue<br>Elmhurst, New York 11373<br>Attn: Mr. S. Schwartz                | (1)  |

| National Aeronautics and Space Administration<br>Goddard Space Flight Center<br>Greenbelt, Maryland<br>Attn: Manned Flight Support Office Code 512                     |       | Mr. H. Anschuetz<br>USAF Contract Management District<br>AC Spark Plug Division of General Motors<br>Milwaukee 1, Wisconsin 53201                                          | (1)  |