410-TM(700) REVISION No. 4

KW Smith

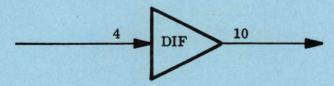

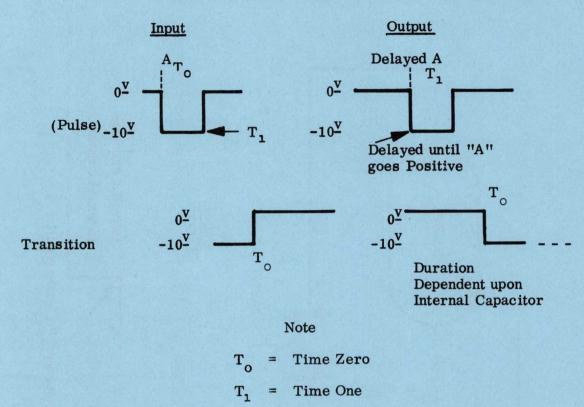

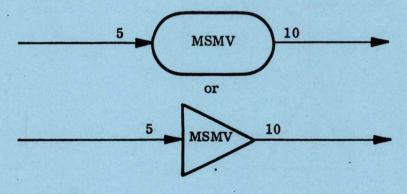

# TRAINING MANUAL

ACE-S/C

DATA ACQUISITION SYSTEM

(PCM DECOMMUTATOR)

CONTRACT NASW-410

TECHNICAL TRAINING UNIT

APOLLO SYSTEMS DEPARTMENT

MISSILE AND SPACE DIVISION

GENERAL ELECTRIC COMPANY

DAYTONA BEACH, FLORIDA

410-TM(700)

TRAINING MANUAL

ACE-S/C

DATA ACQUISITION SYSTEM

(PCM DECOMMUTATOR)

Contract NASw-410

1 April 1969

Technical Training Unit Apollo Systems Department Missile and Space Division General Electric Company Daytona Beach, Florida

FOR TRAINING PURPOSES ONLY

## TABLE OF CONTENTS

| Paragraph                 | Title                       | Page |

|---------------------------|-----------------------------|------|

|                           | SECTION 1—INTRODUCTION      |      |

| 1.1 GENERAL               |                             | 1-1  |

| 1.2 FUNCTIONAL DESCRI     | PTION                       | 1-1  |

| 1.3 SIGNAL CONDITIONER    | 3                           | 1-3  |

| 1.4 GROUP SYNCHRONIZE     | ER                          | 1-5  |

| 1.5 STORED PROGRAM PI     | ROCESSOR                    | 1-7  |

| 1.6 OUTPUT RACK           |                             | 1-11 |

| 1.6.1 Digital-to-Analog C | onverters                   | 1-13 |

| 1.6.2 MSB/LSB Parallel    | Outputs                     | 1-13 |

| 1.6.3 MSB/LSB Truncated   | d Outputs                   | 1-14 |

| 1.6.4 Decimal and Binary  | Displays                    | 1-14 |

| 1.7 DECOMMUTATOR/CO       | MPUTER INTERFACE            | 1-15 |

| 1.8 DIRECT ACCESS COM     | PUTER INTERFACE (DACI)      | 1-15 |

| 1.9 PHYSICAL DESCRIPT     | ION                         | 1-17 |

| 1.10 LEADING PARTICULA    | RS                          | 1-21 |

| 1.11 CAPABILITIES AND L   | IMITATIONS                  | 1-21 |

| S                         | ECTION 2—RADIATION LOGIC    |      |

| 2.1 INTRODUCTION          |                             | 2-1  |

| 2.2 MODULES               |                             | 2-1  |

| 2.2.1 General             |                             | 2-1  |

| 2.2.2 Logic Modules       |                             | 2-5  |

| 2.3 CARDS                 |                             | 2-19 |

| 2.4 DIAGRAMS              |                             | 2-19 |

| SECTI                     | ON 3—PCM SIGNAL CONDITIONER |      |

| 3.1 DESCRIPTION           |                             | 3-1  |

| 3.2 DC RESTORER           |                             | 3-7  |

| 3.3 BIT SYNCHRONIZER      |                             | 3-9  |

| 3.4 TRANSITION DETECT     | OR CIRCUITS                 | 3-14 |

| FOR                       | TRAINING BURBOSES ONLY      |      |

# TABLE OF CONTENTS (Cont.)

| Parag | <u>Title</u>                                        | Page |

|-------|-----------------------------------------------------|------|

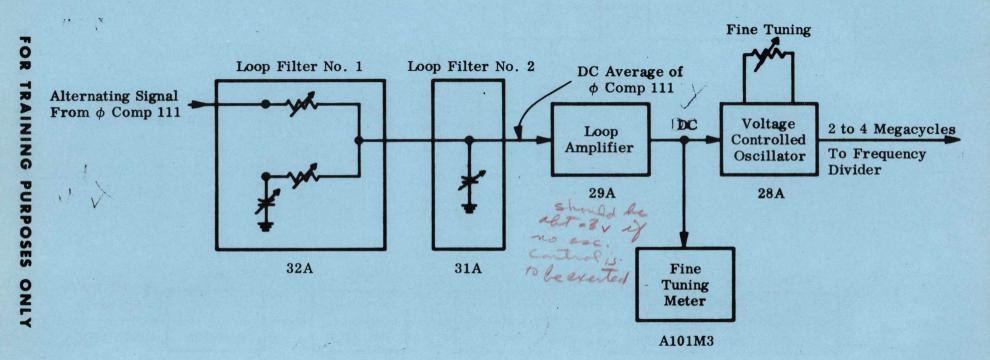

| 3.5   | PHASE COMPARATOR, LOOP AMPLIFIER, AND VCO CIRCUITS  | 3-16 |

|       | SYNC QUALITY CIRCUITS                               | 3-19 |

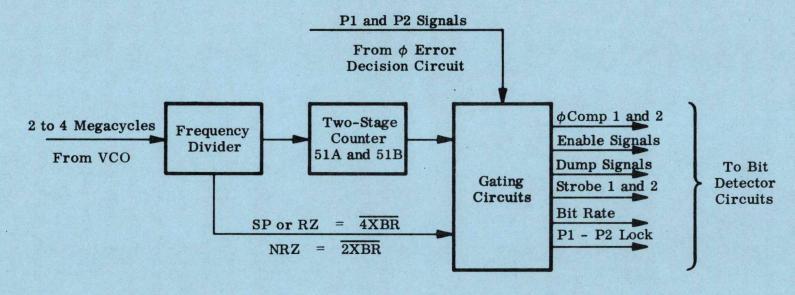

|       | FREQUENCY DIVIDER                                   | 3-19 |

|       | TIMING GENERATOR                                    | 3-21 |

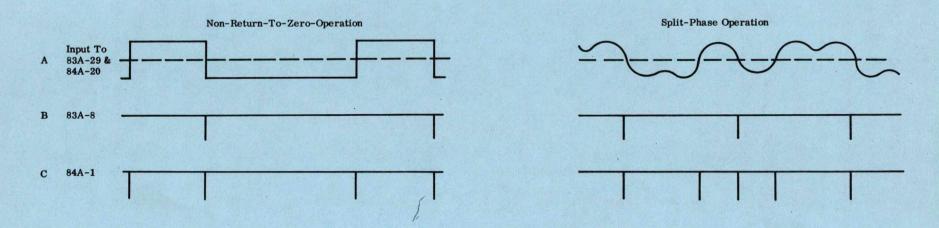

| 3.9   | BIT DETECTOR                                        | 3-23 |

| 3.10  | PROGRAMMING SYSTEM                                  | 3-32 |

| 3.10. | 1 Block Diagram Analysis                            | 3-32 |

| 3.11  | INDICATOR CIRCUIT                                   | 3-35 |

|       | SECTION 4—GROUP SYNCHRONIZER                        |      |

| 4.1   | GENERAL DESCRIPTION                                 | 4-1  |

| 4.1.1 | Operating Concepts                                  |      |

| 4.1.2 | Controls and Indicators                             | 4-2  |

| 4.1.3 | Capabilities                                        | 4-2  |

| 4.2   | PRIME FRAME SYNCHRONIZER                            | 4-3  |

| 4.2.1 | Block Diagram Analysis                              | 4-3  |

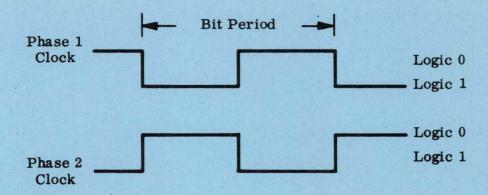

| 4.2.2 | Phase 1 and Phase 2 Clock Pulses                    | 4-6  |

| 4.2.3 | Memory Storage Logic                                | 4-6  |

| 4.2.4 | Shift Register                                      | 4-8  |

| 4.2.5 | PFS Correlation Logic                               | 4-8  |

| 4.2.6 | Word Length Counter                                 | 4-11 |

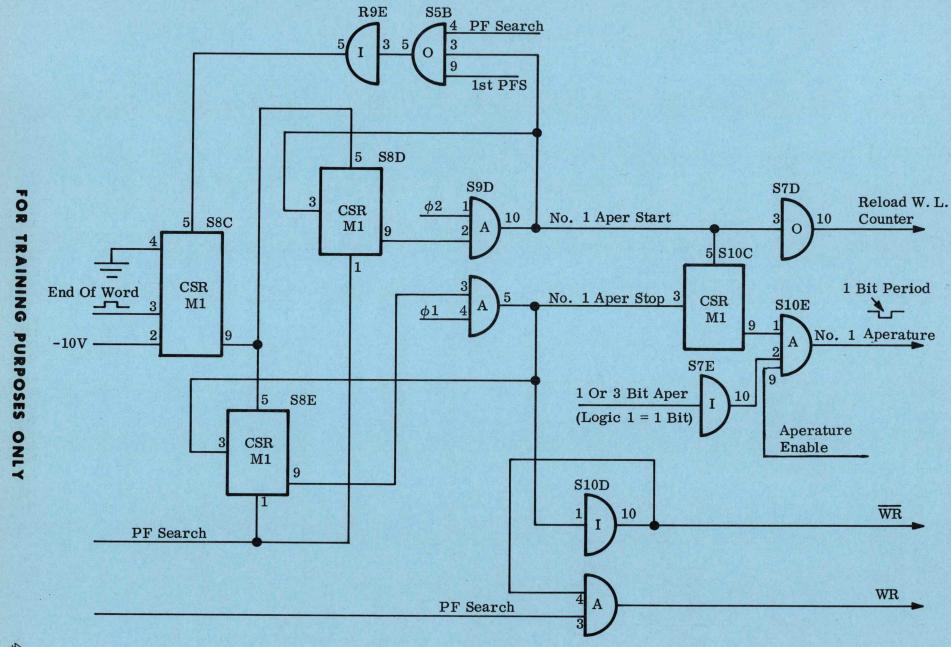

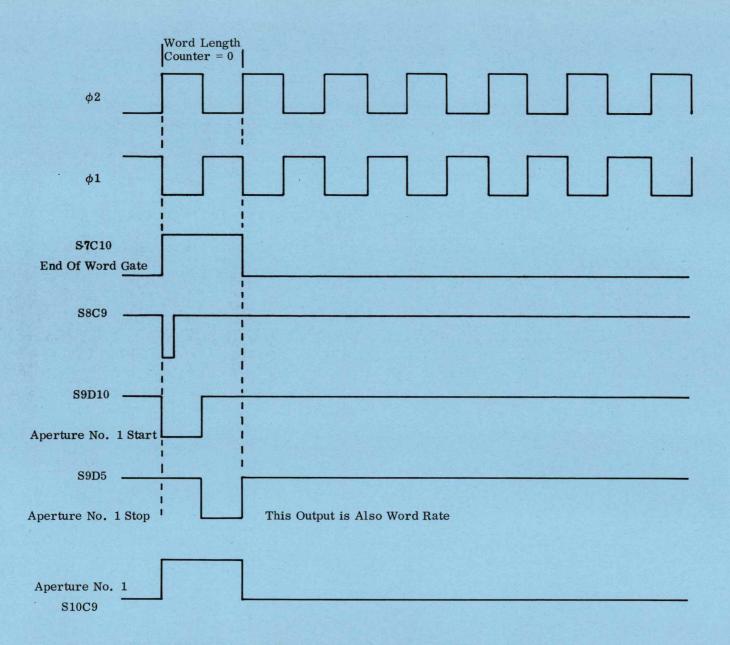

| 4.2.7 | Aperture 1 Generator and Word Rate Generator        | 4-12 |

| 4.2.8 | Aperture 3 Generator                                | 4-12 |

| 4.2.9 | Aperture Gating                                     | 4-16 |

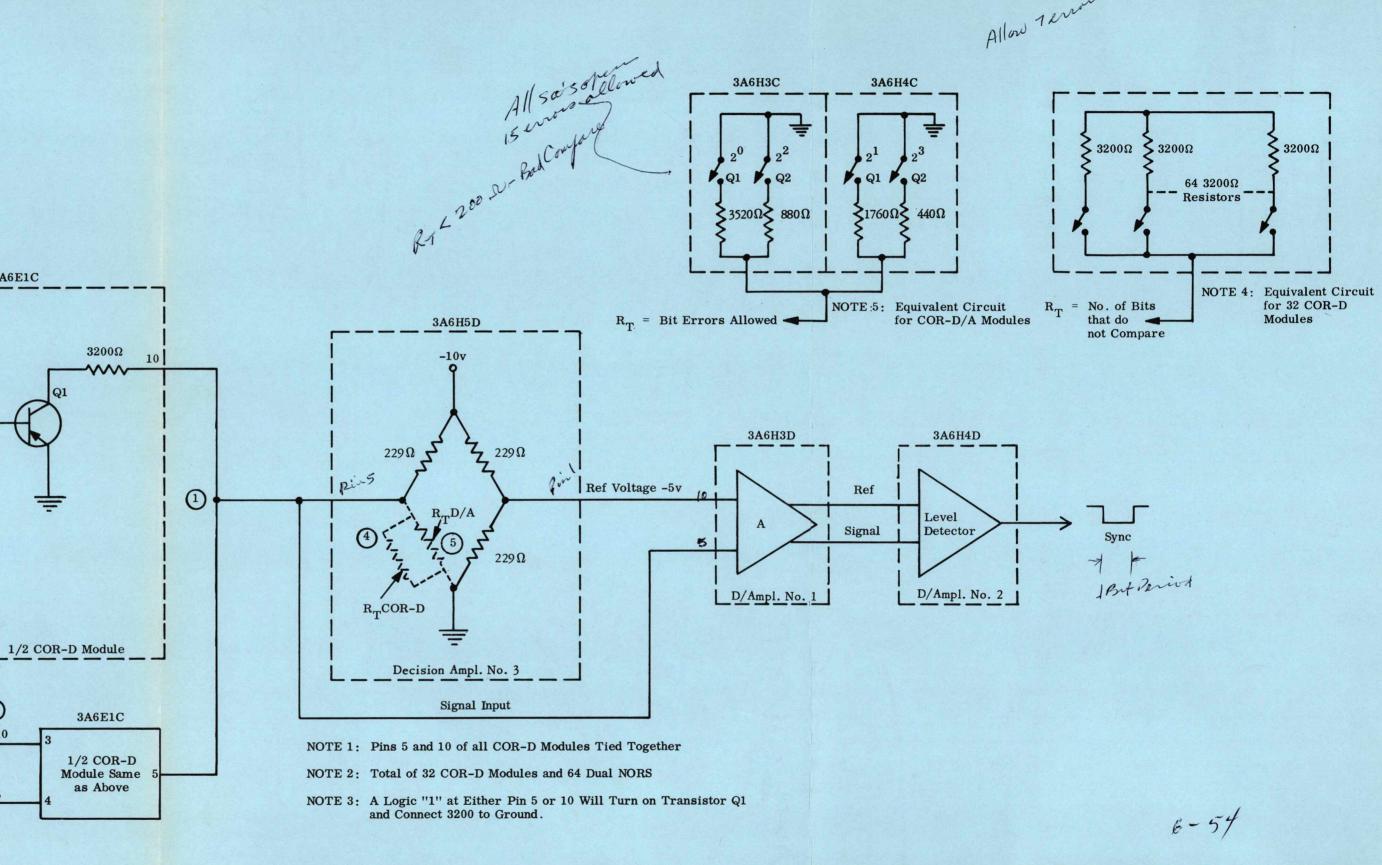

| 4.2.1 | 0 Aperture/PFS Comparison                           | 4-16 |

| 4.2.1 | 1 Misses Allowed Counter                            | 4-20 |

| 4.2.1 | 2 Words Sampled Counter                             | 4-20 |

| 4.2.1 | 3 Loading Words Sampled and Misses Allowed Counters | 4-24 |

| 4.2.1 | 4 Synchronization Status Logic                      | 4-24 |

| 4.3   | ID SYNCHRONIZER                                     | 4-24 |

| 4.3.1 | Block Diagram Analysis                              | 4-24 |

| 4.3.2 | ID Shift Register                                   | 4-28 |

| 4.3.3 | ID Up-Down Counter                                  | 4-28 |

## TABLE OF CONTENTS (Cont.)

| Paragra | <u>Ph</u> <u>Title</u>                    | Page  |

|---------|-------------------------------------------|-------|

| 4.3.4   | Updating                                  | 4-30  |

| 4.3.5   | Comparison Logic                          | 4-30  |

|         |                                           |       |

|         | SECTION 5—STORED PROGRAM PROCESSOR        |       |

| 5.1 GI  | ENERAL                                    | 5-1   |

| 5.2 M   | EMORY CONTROL                             | 5-1   |

| 5.3 PI  | ROGRAM CONTROL, CONTROLS, AND INDICATORS  | 5-7   |

| 5.4 PI  | REACQUISITION MODE                        | 5-10  |

| 5.5 DI  | CCOM MODE                                 | 5-18  |

| 5.6 PH  | ROGRAM LOADING AND CHECKING               | 5-25  |

| 5.6.1   | Paper Tape and Computer Layout Formatting | 5-26  |

| 5.6.2   | Manual Loading                            | 5-26  |

| 5.6.3   | Paper Tape Loading                        | 5-31  |

| 5.6.4   | Computer Loading                          | 5-31  |

| 5.6.5   | DACI Loading                              | 5-31  |

|         | SECTION 5A—MEMORY                         |       |

| 5A.1 GI | ENERAL                                    | 5A-1  |

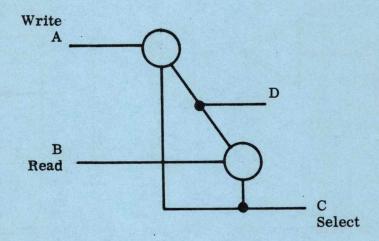

| 5A.1.1  | Read                                      | 5A-1  |

| 5A.1.2  | Write                                     | 5A-3  |

| 5A.2 CC | DRE MATRIX                                | 5A-3  |

| 5A.2.1  | Inhibit Circuits                          | 5A-9  |

| 5A.2.2  | Sense Circuits                            | 5A-9  |

| 5A.2.3  | Drive Line Selection                      | 5A-10 |

| 5A.3 FU | INCTIONAL DESCRIPTION                     | 5A-11 |

| 5A.3.1  | Clear/Write                               | 5A-11 |

| 5A.3.2  | Read/Write                                | 5A-12 |

| 5A.3.3  | Inhibit Selection                         | 5A-12 |

| 5A.3.4  | Address Selection                         | 5A-12 |

| 5A.4 IN | DIANA GENERAL LOGIC                       | 5A-16 |

| 5A.4.1  | Emitter Follower                          | 5A-16 |

| 5A.4.2  | Complementary Emitter Follower            | 5A-16 |

| 5A.4.3  | Flip-Flop                                 | 5A-16 |

|         |                                           |       |

FOR TRAINING PURPOSES ONLY

iii

# TABLE OF CONTENTS (Cont.)

| Paragra | <u>ph</u> <u>Title</u>                             | Page  |

|---------|----------------------------------------------------|-------|

| 5A.4.4  | Single Shot Multivibrator                          | 5A-18 |

| 5A.4.5  | Current Driver                                     | 5A-20 |

| 5A.4.6  | Drive Input Amplifier                              | 5A-20 |

| 5A.4.7  | Drive Transformer                                  | 5A-21 |

| 5A.4.8  | Sense Amplifier                                    | 5A-21 |

|         | Inhibit Driver                                     | 5A-22 |

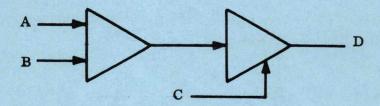

| 5A.4.10 | OR Gate                                            | 5A-22 |

| 5A.4.11 | AND Gate                                           | 5A-23 |

| 5A.4.12 | Amplifier                                          | 5A-23 |

|         | SECTION 6—OUTPUT RACK                              |       |

| 6.1 MS  | SB AND LSB PARALLEL REGISTERS                      | 6-1   |

| 6.1.1   | General                                            | 6-1   |

| 6.1.2   | MSB First-Word Sync Code and Parity Bits Present   | 6-3   |

| 6.1.3   | LSB First-No Word Sync Code or Parity Bits Present | 6-8   |

| 6.1.4   | Display Address Register                           | 6-8   |

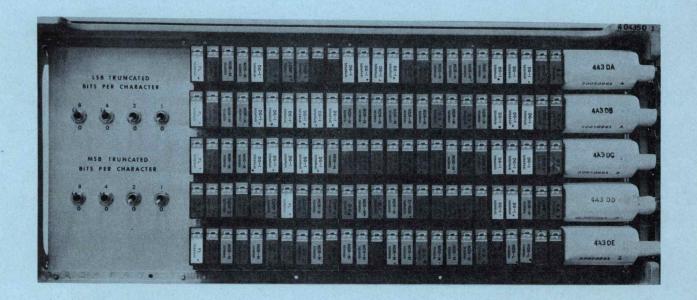

| 6.2 M   | SB AND LSB TRUNCATION                              | 6-9   |

| 6.2.1   | MSB and LSB Truncated Characters Controls          | 6-9   |

| 6.2.2   | MSB and LSB Truncated Characters                   | 6-10  |

| 6.3 DI  | CIMAL DISPLAYS CONTROLS AND INDICATORS             | 6-24  |

| 6.4 BI  | NARY DISPLAY CONTROLS AND INDICATORS               | 6-25  |

| 6.5 DI  | CCIMAL AND BINARY DISPLAYS                         | 6-26  |

| 6.5.1   | General .                                          | 6-26  |

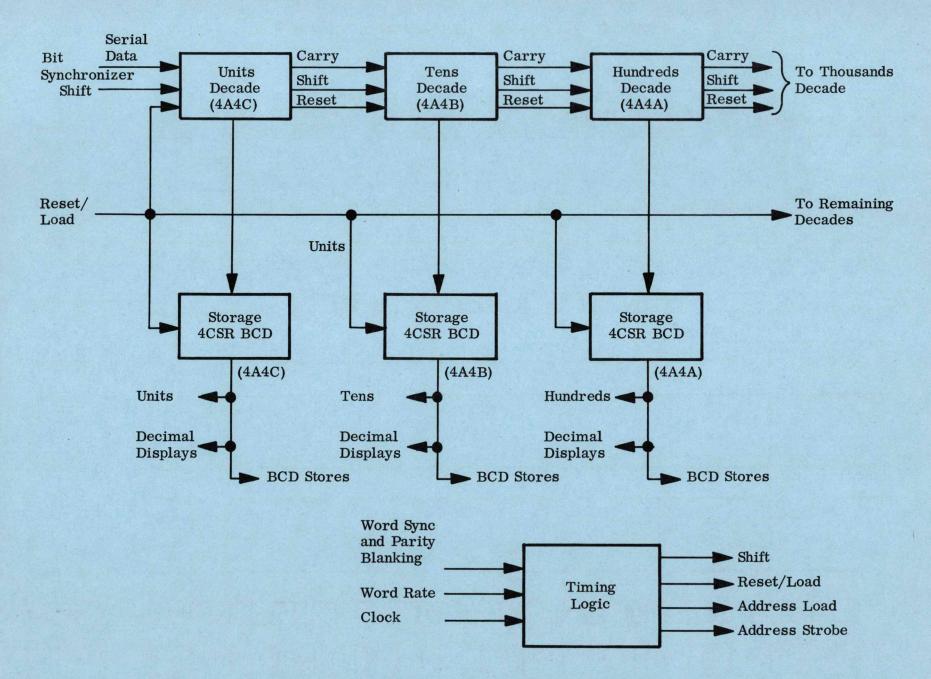

| 6.5.2   | Block Diagram Analysis                             | 6-27  |

| 6.5.3   | Decimal Display Logic Discussion                   | 6-29  |

| 6.5.4   | Binary Display Logic Discussion                    | 6-31  |

| 6.6 DI  | GITAL-TO-ANALOG CONVERTERS                         | 6-31  |

| 6.6.1   | General                                            | 6-31  |

| 6.6.2   | Block Diagram Analysis                             | 6-32  |

| 6.6.3   | Logic Analysis                                     | 6-35  |

| 6.7 BI  | NARY-TO-BINARY CODED DECIMAL CONVERTER             | 6-40  |

| 6.7.1   | General                                            | 6-40  |

| 6.7.2   | Functional Description                             | 6-42  |

# TABLE OF CONTENTS (Cont.)

| Paragra | <u>Title</u>                                                | Page |

|---------|-------------------------------------------------------------|------|

|         | SECTION 7—COMPUTER INTERFACE UNIT                           |      |

| 7.1 IN  | TRODUCTION                                                  | 7-1  |

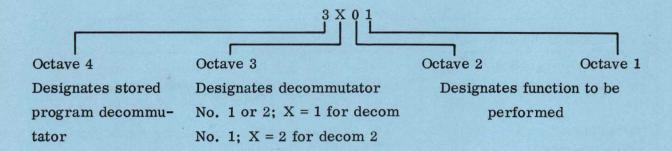

| 7.2 C   | OMPUTER INSTRUCTION WORDS                                   | 7-1  |

| 7.3 D   | ECOMMUTATOR WORDS                                           | 7-4  |

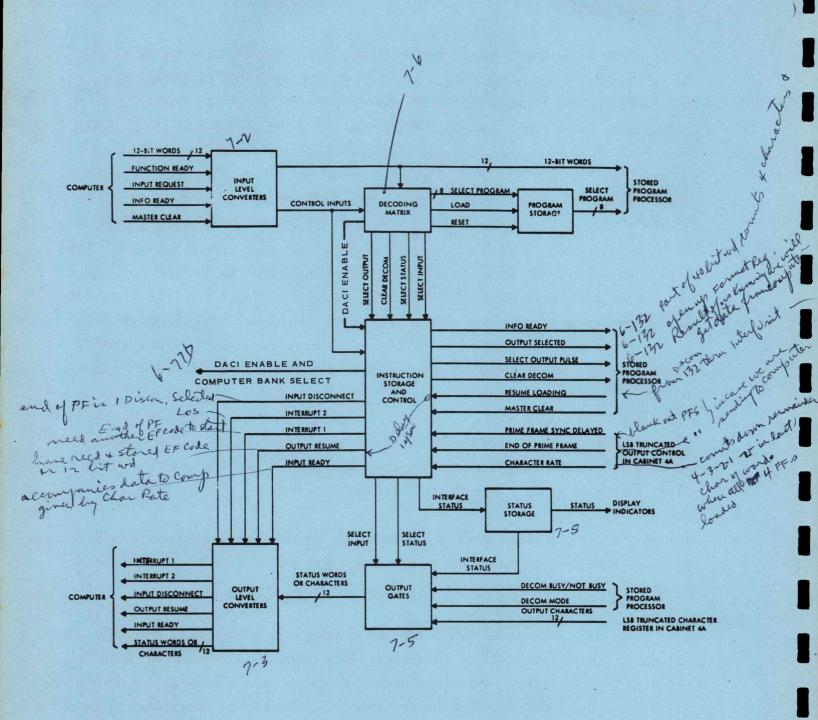

| 7.4 B   | LOCK DIAGRAM ANALYSIS                                       | 7-5  |

| 7.5 L   | OGIC ANALYSIS                                               | 7-11 |

| 7.5.1   | General                                                     | 7-11 |

| 7.5.2   | Function Ready Signal                                       | 7-12 |

| 7.5.3   | Store Strobe                                                | 7-13 |

| 7.5.4   | Input Request Signal                                        | 7-15 |

| 7.5.5   | Information Ready Signal                                    | 7-16 |

| 7.5.6   | Master Clear Signal                                         | 7-17 |

| 7.5.7   | Decoding Instruction Word 3X01 (Select Input)               | 7-17 |

| 7.6 S   | TATUS RESPONSE WORD                                         | 7-21 |

| 7.6.1   | General                                                     | 7-21 |

| 7.6.2   | Data Transfer                                               | 7-21 |

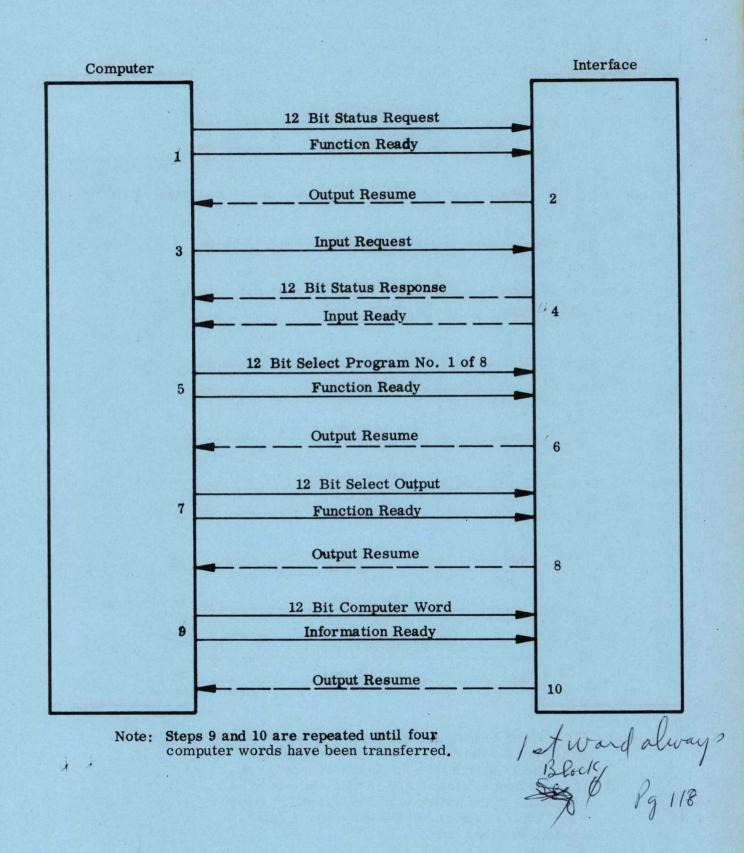

| 7.6.3   | Memory Loading                                              | 7-22 |

| 7.6.4   | Program Check                                               | 7-23 |

| 7.6.5   | Direct Access Computer Interface Instruction                | 7-29 |

|         | SECTION 8—PCM SIGNAL SIMULATOR                              |      |

| 8.1 P   | CM SIGNAL SIMULATOR CONTROLS AND INDICATORS                 | 8-1  |

| 8.2 P   | CM SIGNAL SIMULATOR                                         | 8-5  |

| 8.2.1   | General                                                     | 8-5  |

| 8.2.2   | Frequency Selection                                         | 8-9  |

| 8.2.3   | Bits-per-Prime-Frame Sync Word and per-Common-Word Counters | 8-10 |

| 8.2.4   | Words-per-Prime-Frame Counter                               | 8-12 |

| 8.2.5   | Prime-Frames-per-Major-Cycle Counter                        | 8-14 |

| 8.2.6   | Major Cycle Unique Word Channel Location Switches           | 8-16 |

| 8.2.7   | Output Shift Register Set Logic                             | 8-16 |

| 8.2.8   | Shift Register Output Logic                                 | 8-21 |

| 8.2.9   | Code Formatting                                             | 8-21 |

|         |                                                             |      |

## TABLE OF CONTENTS

| Paragraph               | <u>Title</u>                      | Page |

|-------------------------|-----------------------------------|------|

|                         | SECTION 9—PROGRAMMING             |      |

| 9.1 INTRODUCTION        |                                   | 9-1  |

| 9.2 PROGRAMMING EX      | XAMPLES                           | 9-21 |

| 9.3 PROGRAMMING W       | ITHOUT SECOND ACCESS              | 9-21 |

| 9.4 PROGRAMMING W       | ITH SECOND ACCESS                 | 9-25 |

| 9.5 ID PROGRAMMING      |                                   | 9-27 |

|                         |                                   |      |

| SECTION                 | 10-DIRECT ACCESS COMPUTER INTERFA | ACE  |

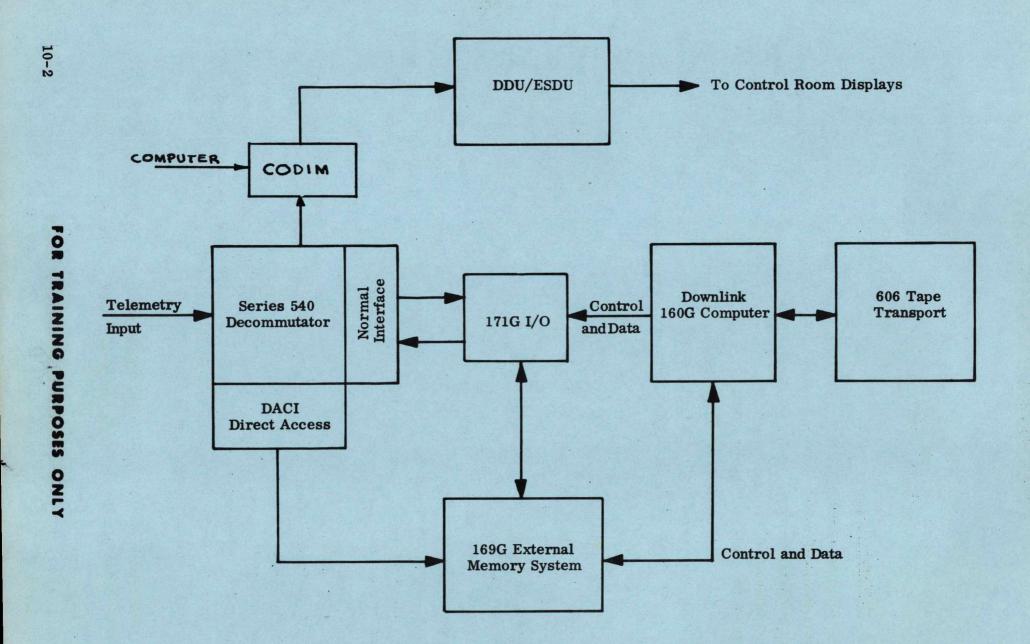

| 10.1 INTRODUCTION       |                                   | 10-1 |

| 10.2 FUNCTIONAL DES     | CRIPTION                          | 10-3 |

| 10.2.1 General          |                                   | 10-3 |

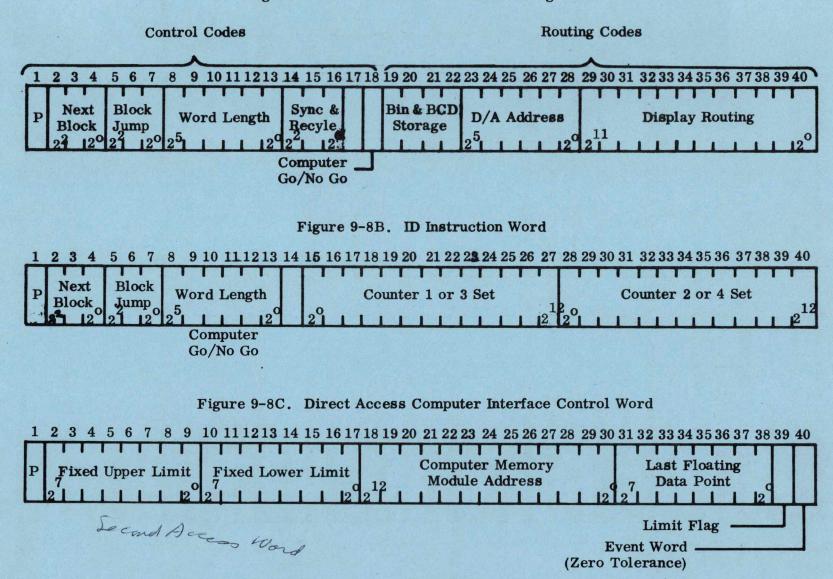

| 10.2.2 Instruction Word | d Formats                         | 10-3 |

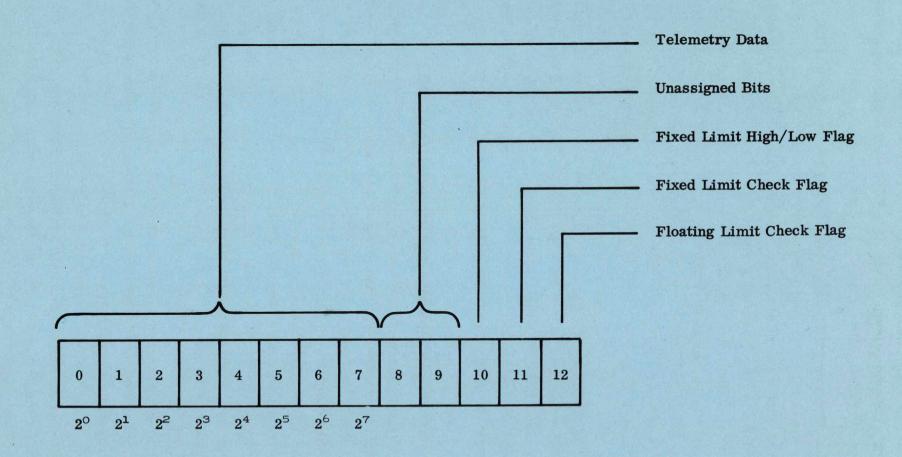

| 10.2.3 Computer Word    | Formats                           | 10-6 |

| 10.2.4 Floating Point T | olerance Check Technique          | 10-6 |

| 10 2 5 Sequence of One  | ration                            | 10_8 |

## LIST OF ILLUSTRATIONS

| Figure | <u>Title</u>                                               | Page |

|--------|------------------------------------------------------------|------|

| 1-1    | PCM Decommutator                                           | 1-2  |

| 1-2    | PCM Signal Conditioner                                     | 1-4  |

| 1-3    | Prime Frame Synchronizer                                   | 1-6  |

| 1-4    | ID Synchronizer                                            | 1-8  |

| 1-5    | Stored Program Processor                                   | 1-9  |

| 1-6    | Output Devices                                             | 1-12 |

| 1-7    | Interconnection Diagram                                    | 1-16 |

| 1-8    | DACI/Decommutator Interface                                | 1-18 |

| 1-9    | Series 540 PCM Acquisition and Stored Program Decommutator | 1-19 |

| 1-10   | Stored Program Decommutator Equipment Location             | 1-20 |

| 1-11   | Types of PCM Modulation                                    | 1-30 |

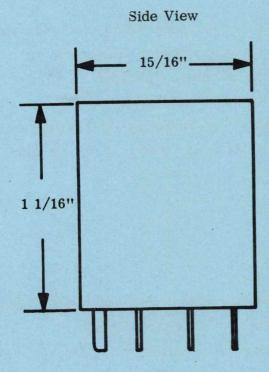

| 2-1    | Molded Modules                                             | 2-2  |

| 2-2    | Rectangular Card                                           | 2-3  |

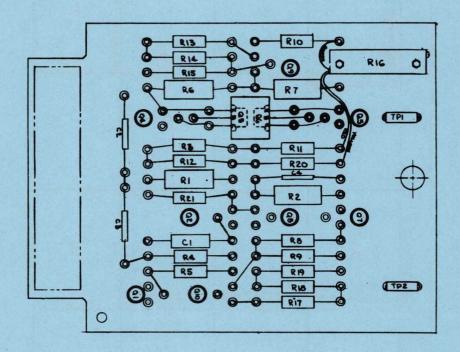

| 2-3    | Connector Panel Representation                             | 2-4  |

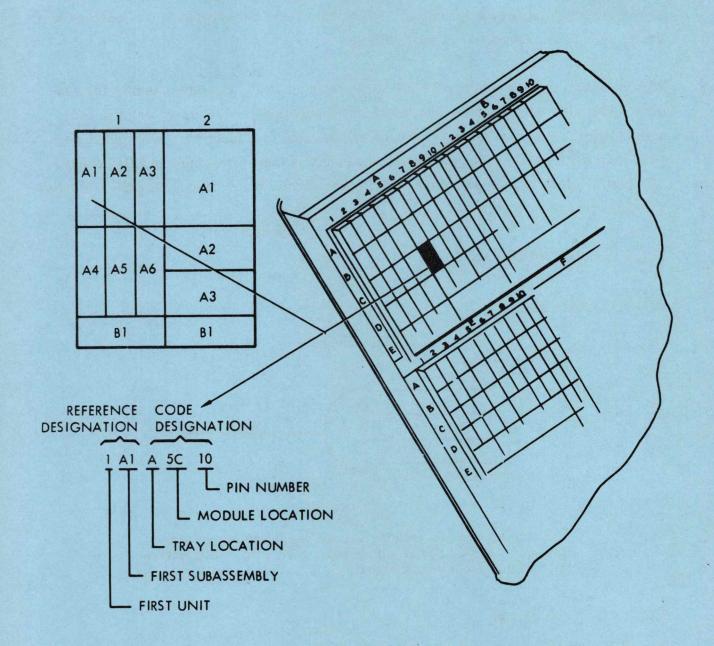

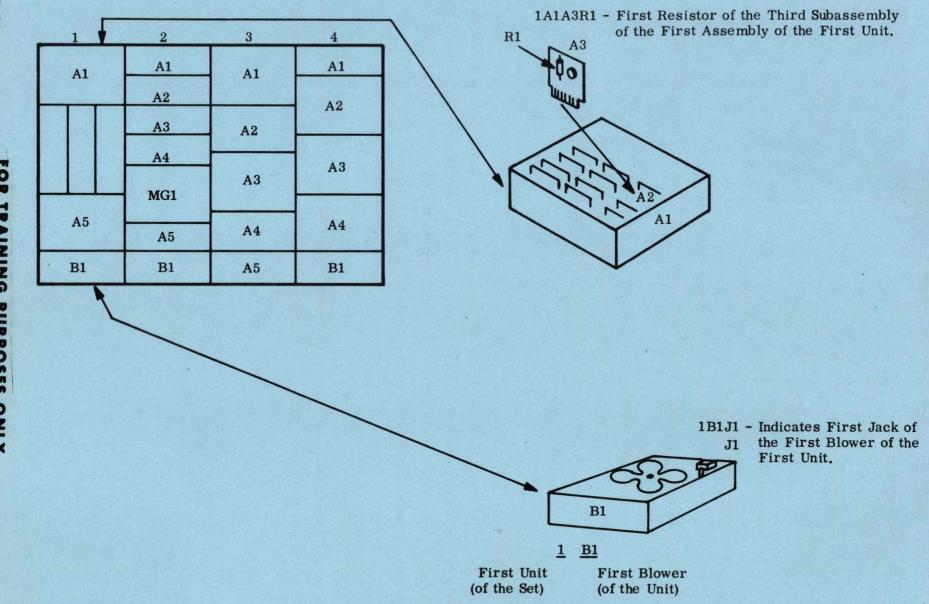

| 2-4    | Reference/Code Designation                                 | 2-6  |

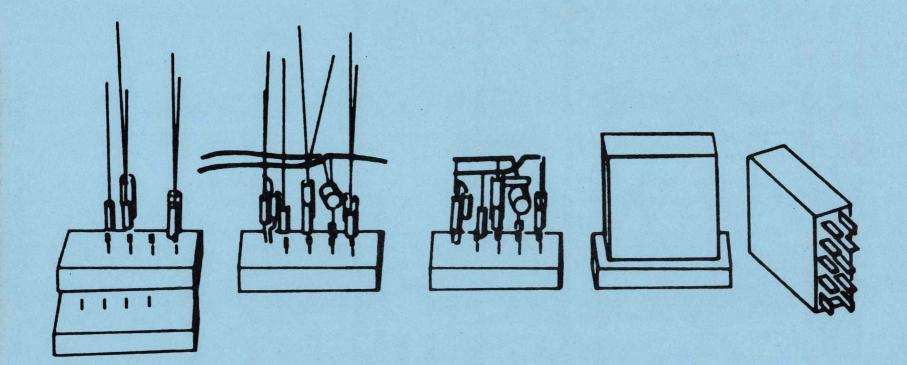

| 2-5    | Typical Module at Successive Stages of Construction        | 2-7  |

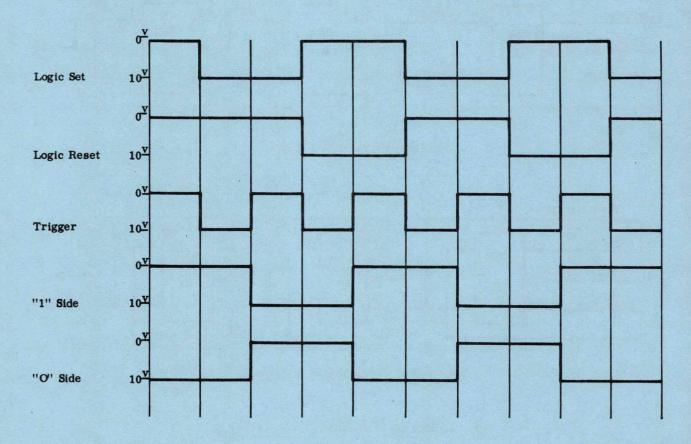

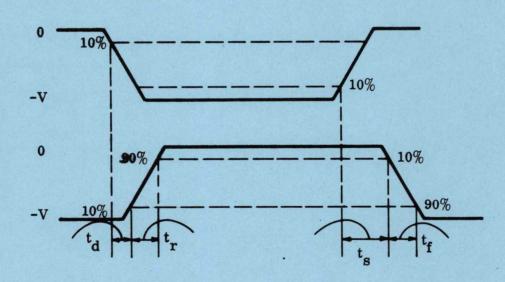

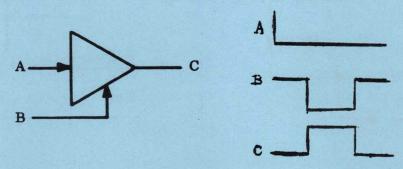

| 2-6    | CSR Waveshapes                                             | 2-11 |

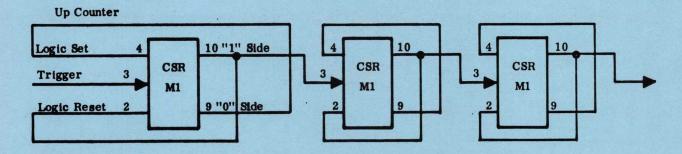

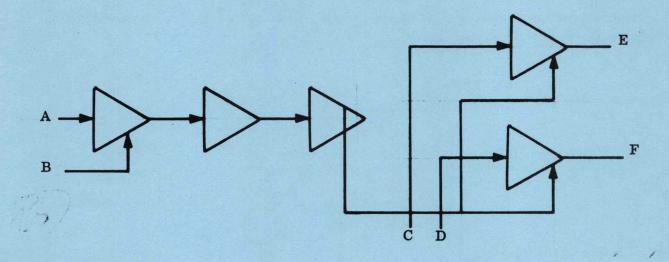

| 2-7    | CSR Up Counter                                             | 2-12 |

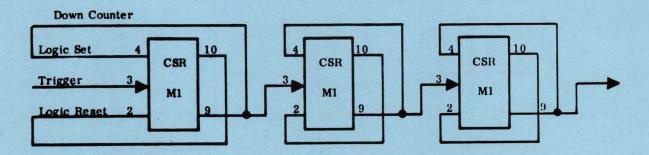

| 2-8    | CSR Down Counter                                           | 2-12 |

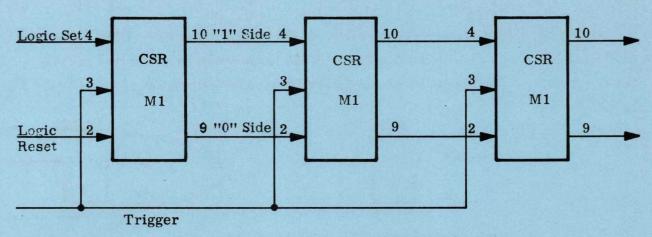

| 2-9    | CSR Shift Register                                         | 2-13 |

| 2-10   | Complete MSMV Circuit                                      | 2-16 |

| 2-11   | Two 2-Input AND Gates                                      | 2-18 |

| 2-12   | Two 2-Input AND with an OR Gate                            | 2-18 |

| 2-13   | Two 3-Input AND Gates                                      | 2-18 |

| 2-14   | Two 3-Input AND Gates Functioning as One 6-Input AND Gate  | 2-19 |

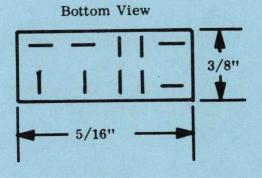

| 2-15   | Reference Designation Assignment                           | 2-20 |

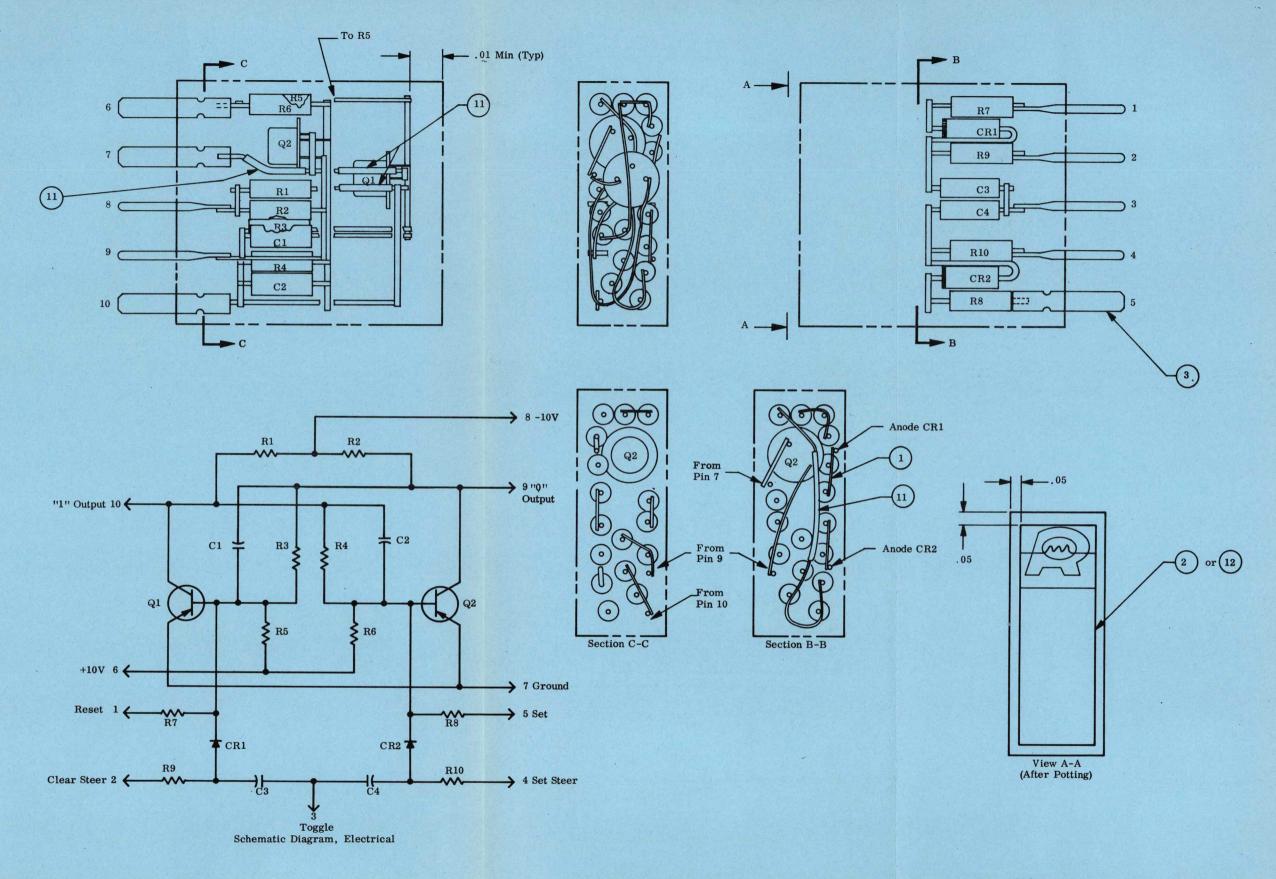

| 2-16   | Schematic and Assembly of CSRM Module                      | 2-21 |

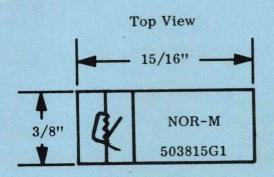

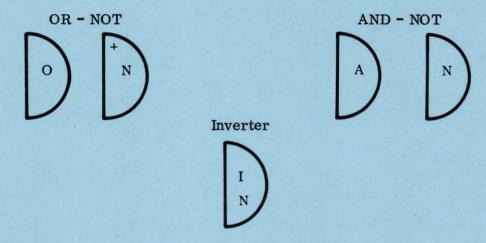

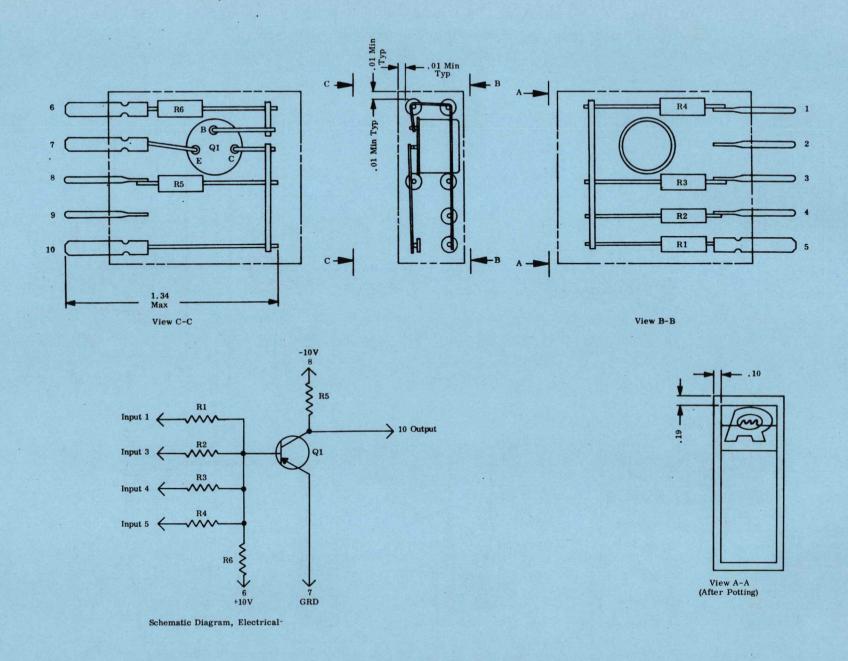

| 2-17   | Schematic and Assembly of Low and Medium Speed NOR         | 2-22 |

| 2-18   | Low and Medium Speed NOR Switching Characteristics         | 2-23 |

| 2-19   | Schematic and Assembly of CSR M1 Module - 506030           | 2-25 |

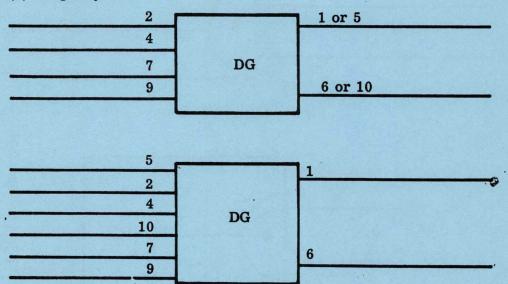

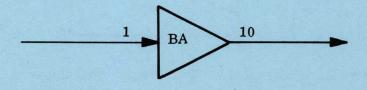

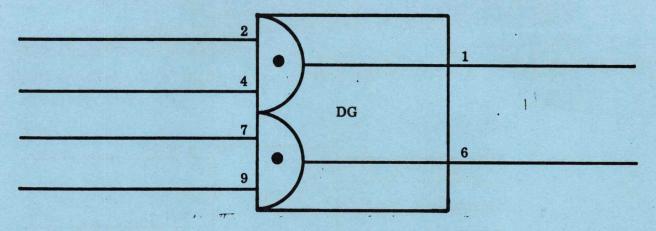

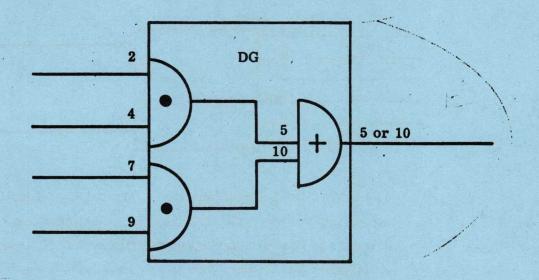

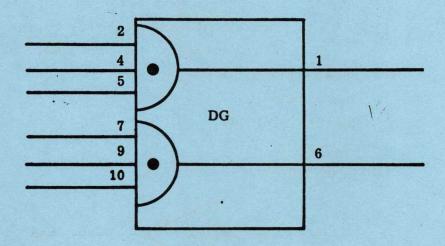

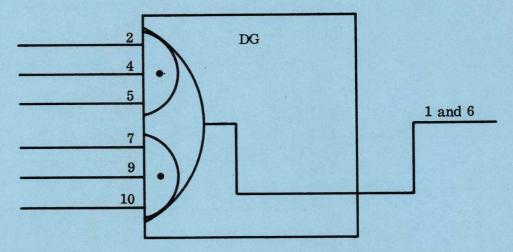

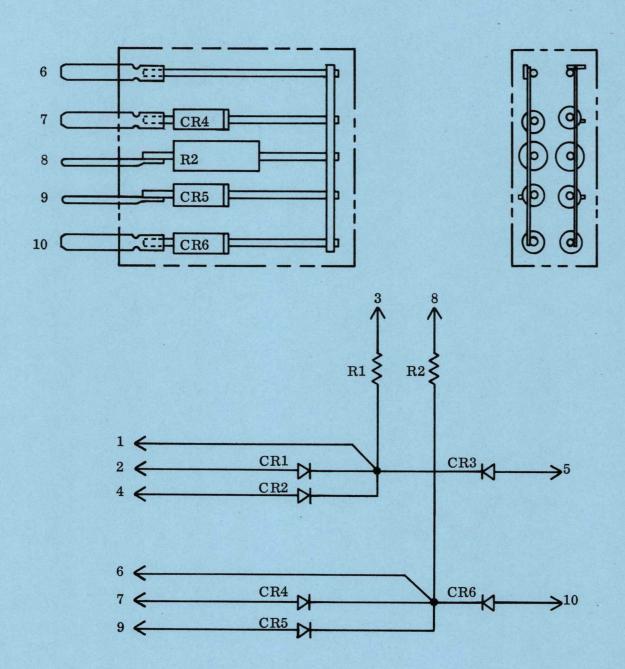

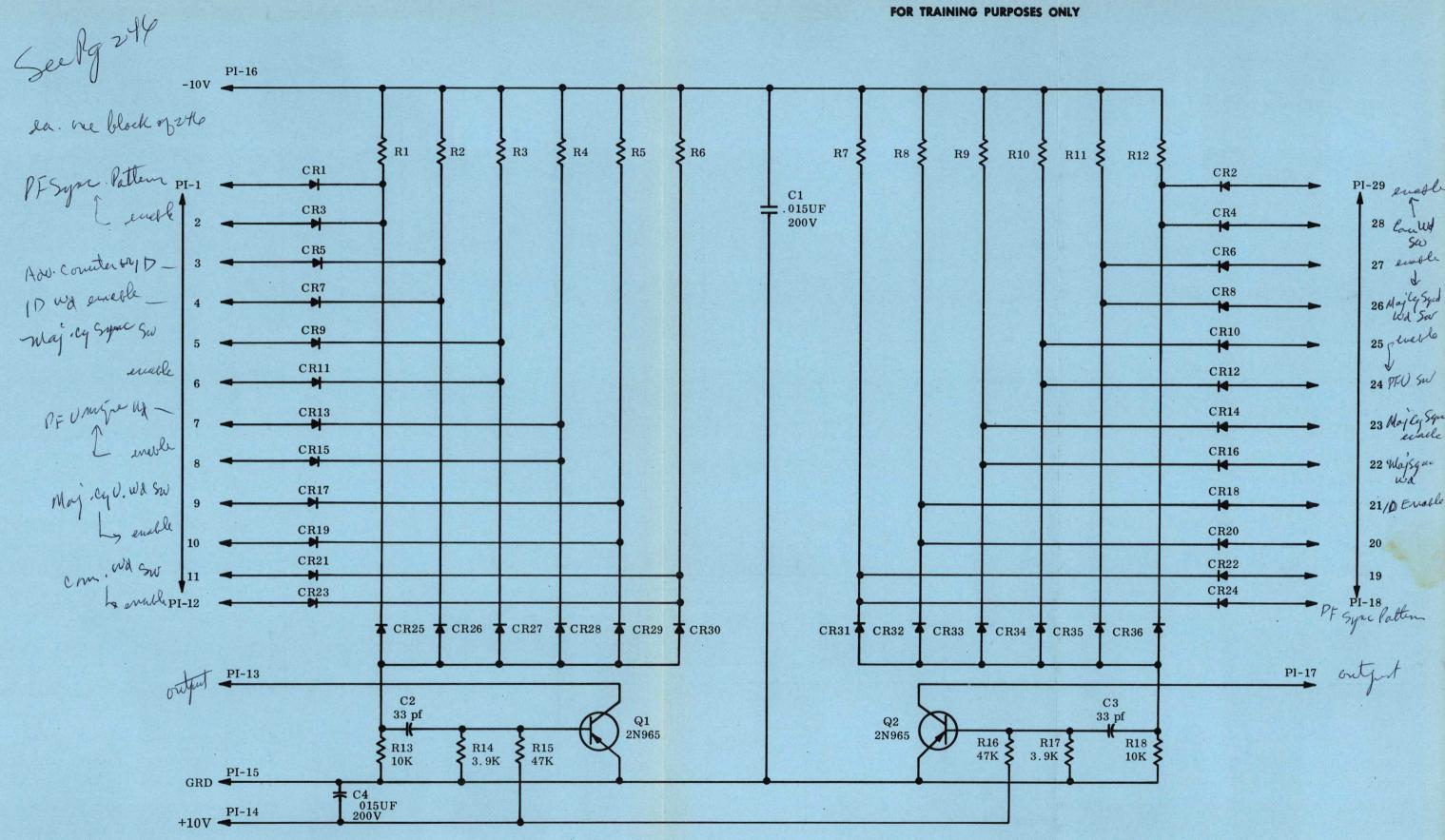

| 2-20   | Schematic of Diode Gate Module                             | 2-27 |

|        | FOR TRAINING PURPOSES ONLY                                 | vii  |

## LIST OF ILLUSTRATIONS (Cont.)

| Figure | <u>Title</u>                                                   | Page |

|--------|----------------------------------------------------------------|------|

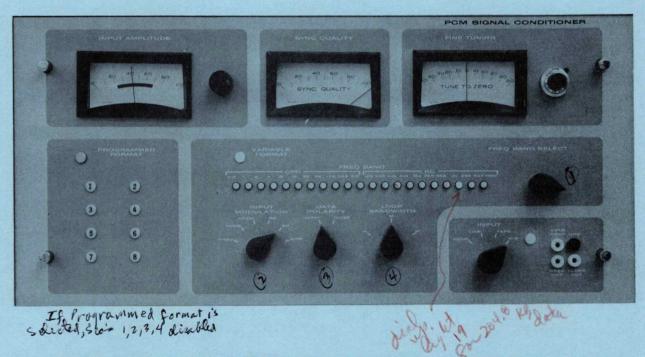

| 3-1    | PCM Signal Conditioner 1A2 Front Panel                         | 3-1  |

| 3-2    | PCM Signal Conditioner                                         | 3-5  |

| 3-3    | DC Restorer, Simplified Block Diagram                          | 3-8  |

| 3-4    | DC Restorer, Timing Diagram                                    | 3-10 |

| 3-5    | Bit Synchronizer (3 Sheets)                                    | 3-11 |

| 3-6    | Transition Detector, Timing Diagram                            | 3-15 |

| 3-7    | Phase Comparator Logic                                         | 3-17 |

| 3-8    | Phase Comparator Timing Diagram                                | 3-18 |

| 3-9    | Sync Quality Circuit Timing Diagram                            | 3-20 |

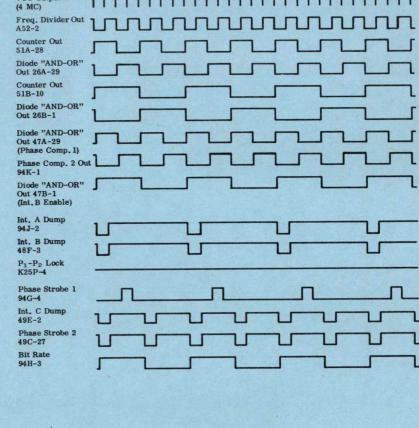

| 3-10   | Timing Generator, Timing Diagram                               | 3-22 |

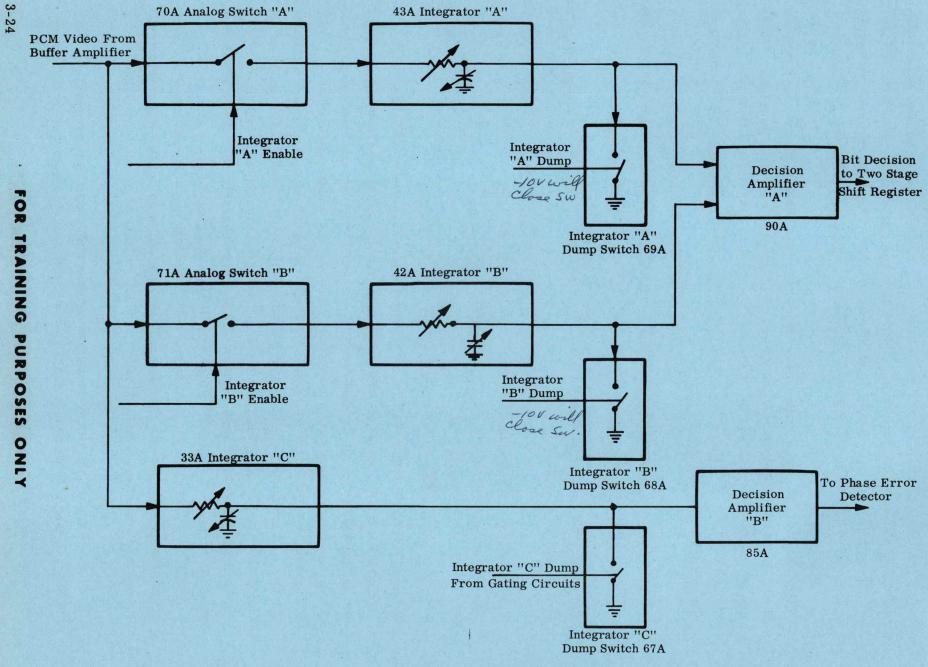

| 3-11   | Bit Detector                                                   | 3-24 |

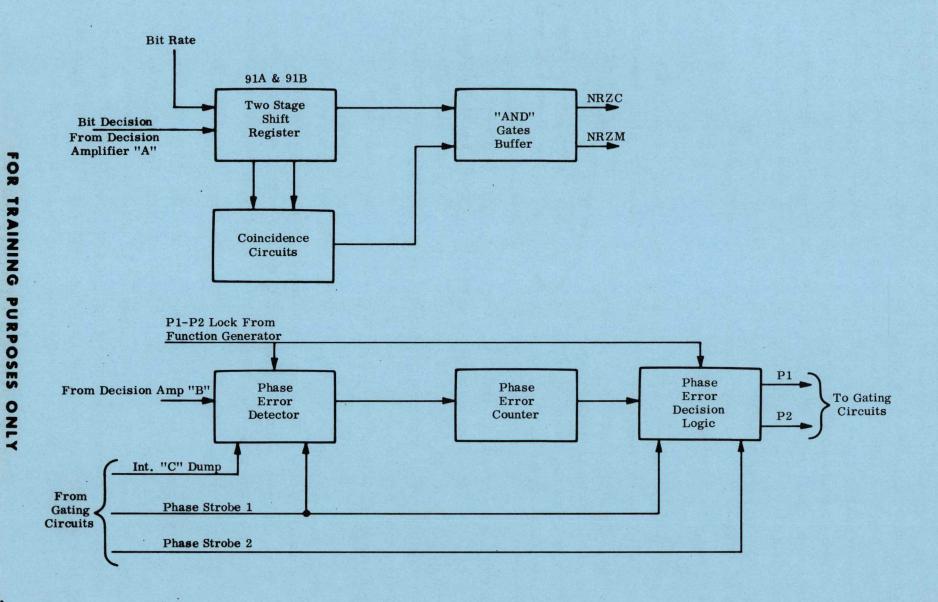

| 3-12   | NRZ Decoder and Phase Detector                                 | 3-25 |

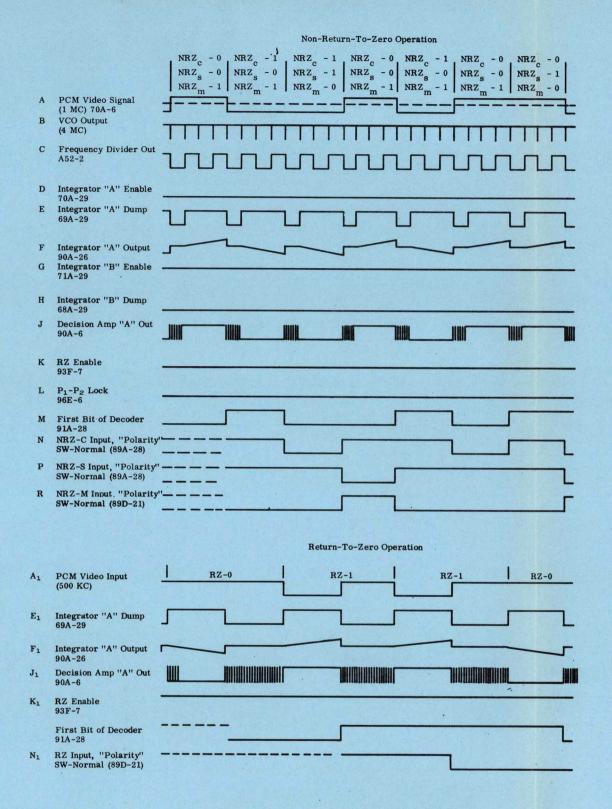

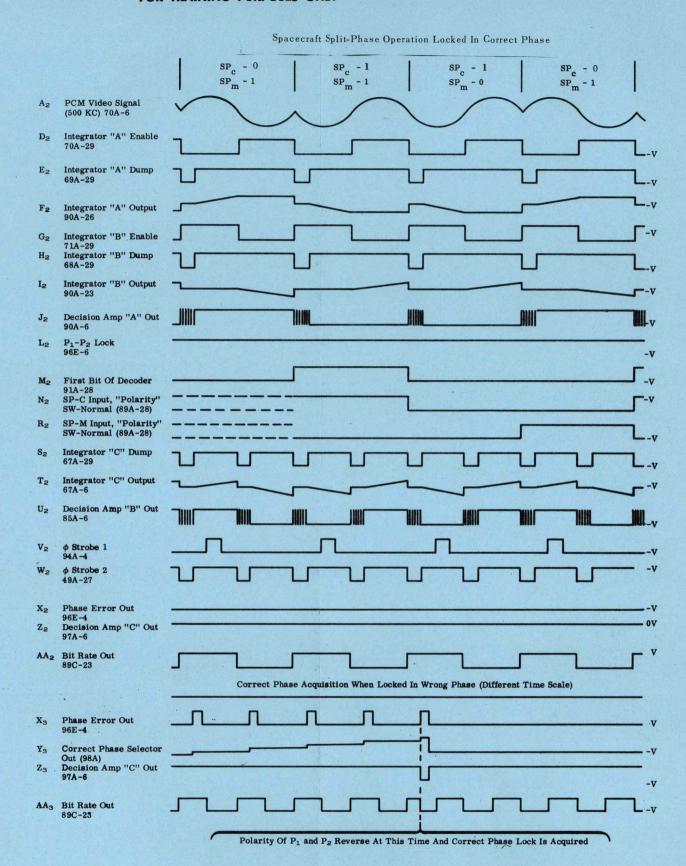

| 3-13   | All-Data-NRZ Decoder and Correct Phase Detector Timing Diagram | 3-29 |

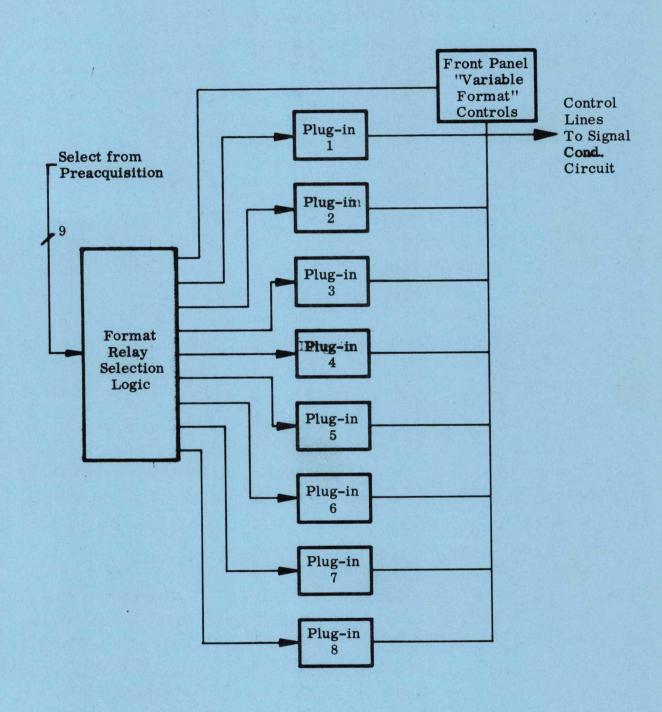

| 3-14   | Programmer System Simplified Block Diagram                     | 3-33 |

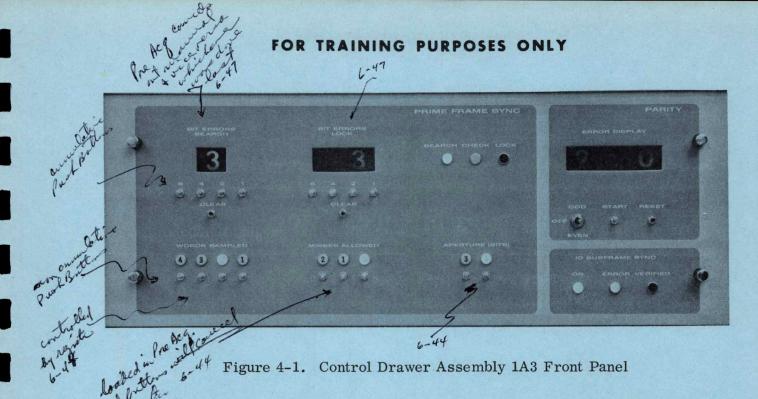

| 4-1    | Control Drawer Assembly 1A3 Front Panel                        | 4-3  |

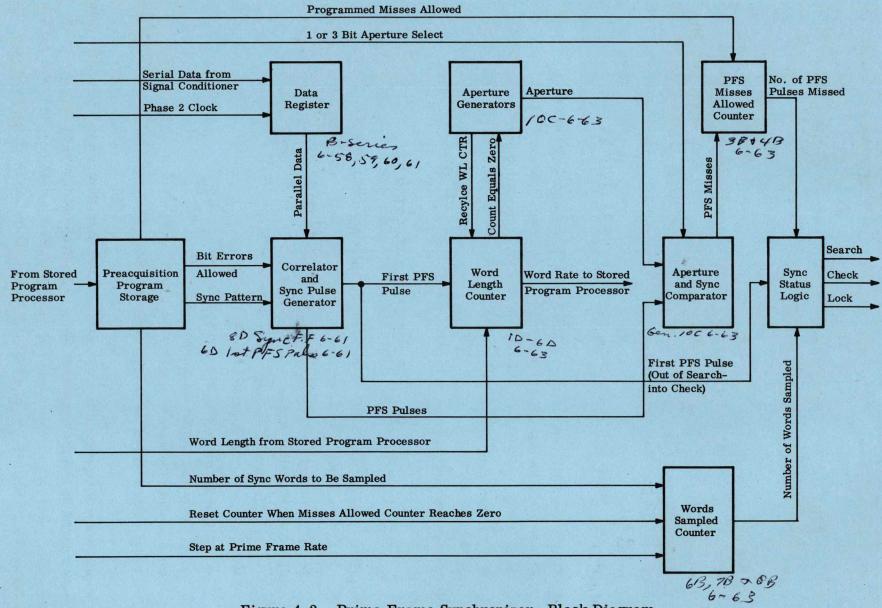

| 4-2    | Prime Frame Synchronizer, Block Diagram                        | 4-4  |

| 4-3    | Phase Relationship, Phase 1 and Phase 2 Clock                  | 4-7  |

| 4-4    | Prime Frame Sync Correlation Logic, Simplified Schematic       | 4-9  |

| 4-5    | Aperture 1 Generator and Word Rate Generator                   | 4-13 |

| 4-6    | Aperture 1 and Word Rate, Synchrogram                          | 4-14 |

| 4-7    | Aperture 3 Generator                                           | 4-15 |

| 4-8    | Timing Diagram, 1- and 3-Bit Apertures                         | 4-16 |

| 4-9    | Partial Schematic for Aperture Gating                          | 4-17 |

| 4-10   | Timing Diagram for Aperture Enable Gate                        | 4-18 |

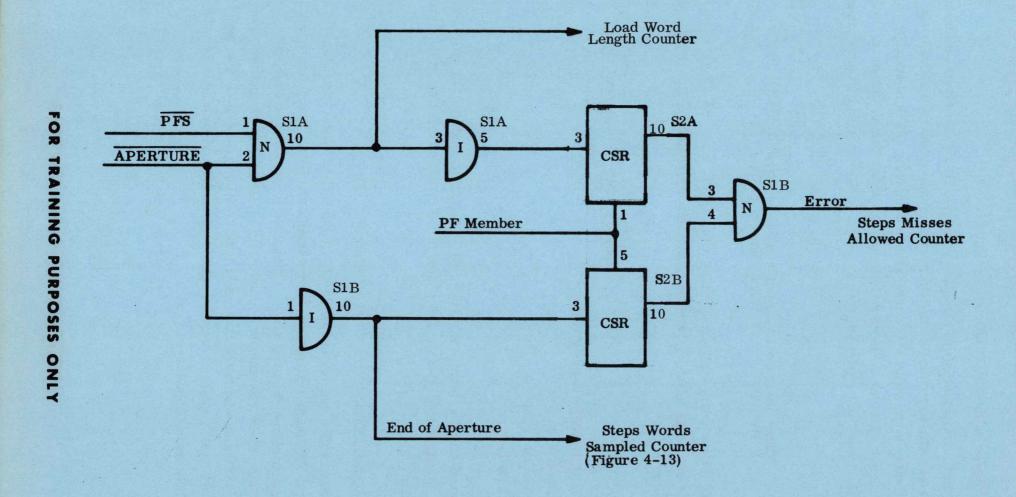

| 4-11   | Partial Schematic of Comparison Logic                          | 4-19 |

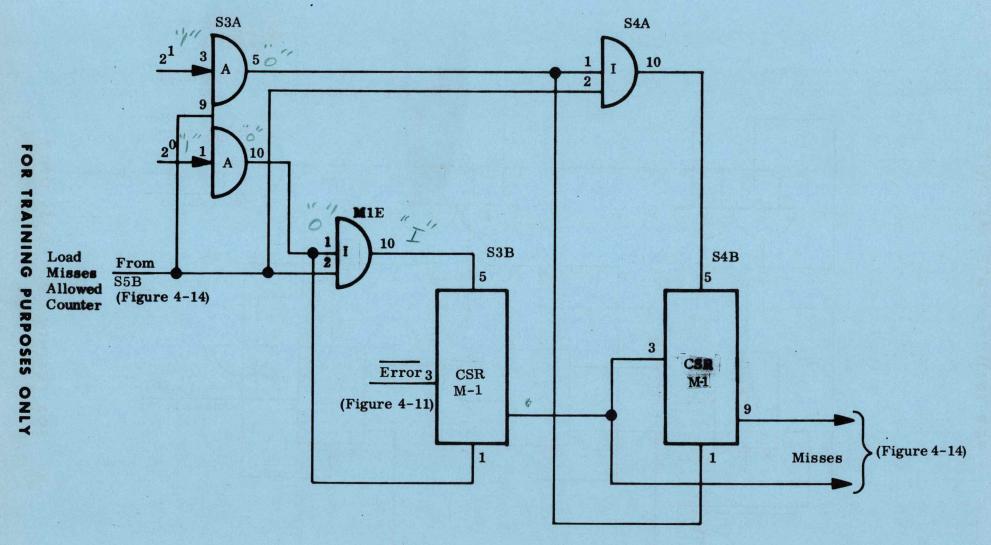

| 4-12   | Misses Allowed Counter 3A6 Sheet S                             | 4-21 |

| 4-13   | Words Sampled Counter                                          | 4-22 |

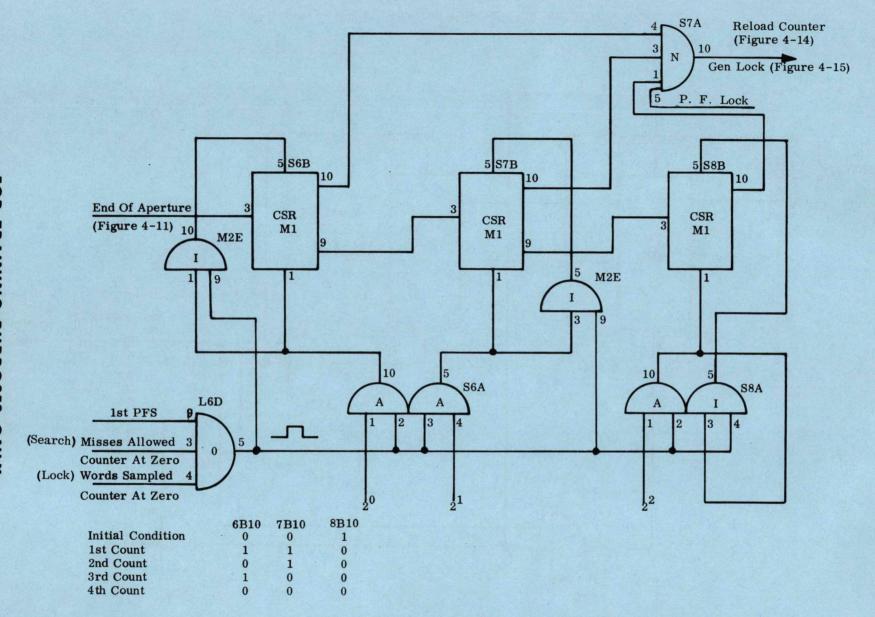

| 4-14   | Partial Logic Diagram of Synchronization Control               | 4-23 |

| 4-15   | Loading of Word and Misses Counters                            | 4-25 |

| 4-16   | ID Synchronizer, Simplified Block Diagram                      | 4-26 |

| 4-17   | Partial Diagram for Clocking ID Shift Register                 | 4-29 |

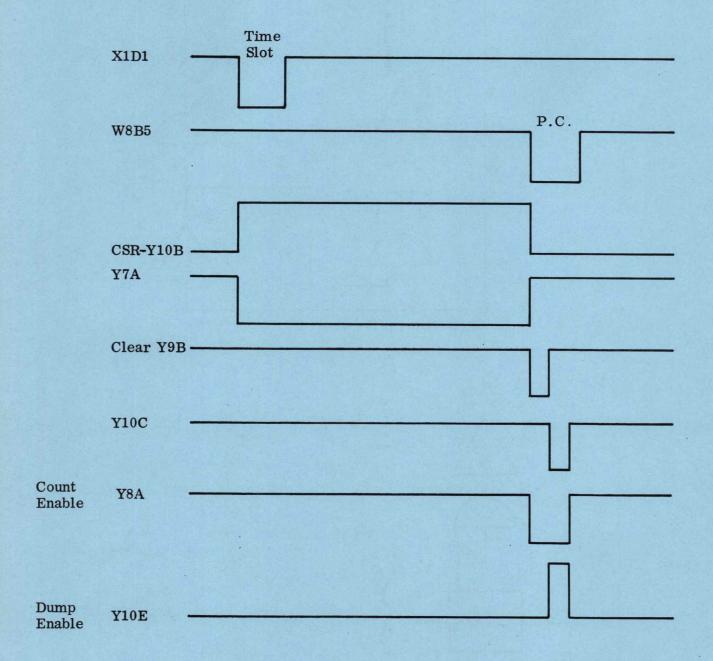

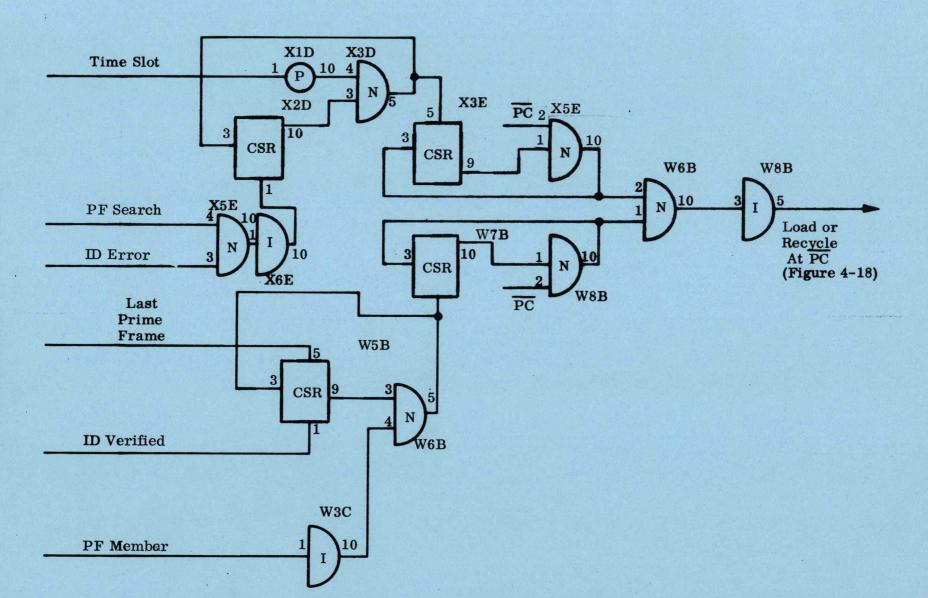

| 4-18   | Partial Diagram for Up-down Counter Loading Signals            | 4-31 |

| 4-19   | Synchrogram, Up-Down Counter Loading Signals                   | 4-32 |

# LIST OF ILLUSTRATIONS (Cont.)

| Figure | <u>Title</u>                                                  | Page  |

|--------|---------------------------------------------------------------|-------|

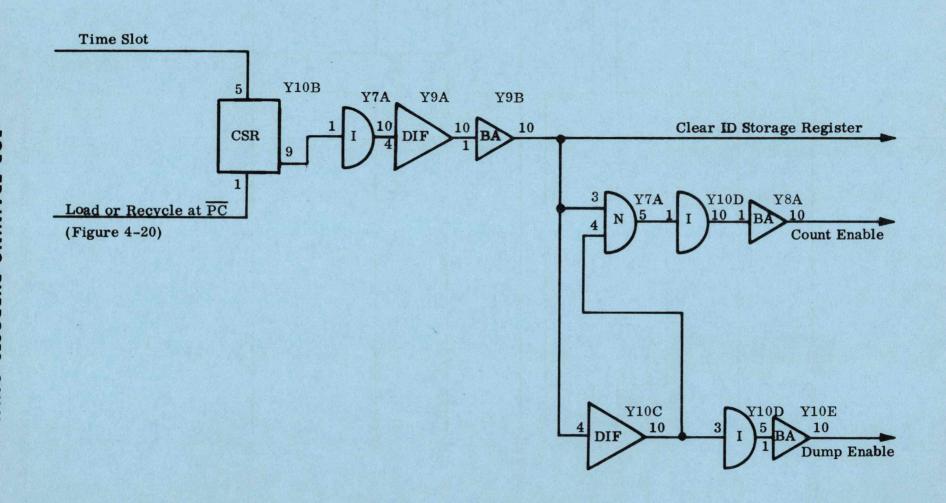

| 4-20   | Load or Recycle Generation                                    | 4-33  |

| 4-21   | Partial Schematic of Comparison Counter                       | 4-35  |

| 5-1    | Stored Program Processor Interconnection                      | 5-2   |

| 5-2    | Stored Program Processor                                      | 5-6   |

| 5-3    | Program Control Drawer 2A2 Front Panel                        | 5-7   |

| 5-4    | Stored Program Processor, Functional Flow Diagram             | 5-11  |

| 5-5    | Preacquisition Word Format                                    | 5-15  |

| 5-6    | Mode/Function Timing Diagram                                  | 5-17  |

| 5-7    | Memory Control Section—Decom Mode                             | 5-21  |

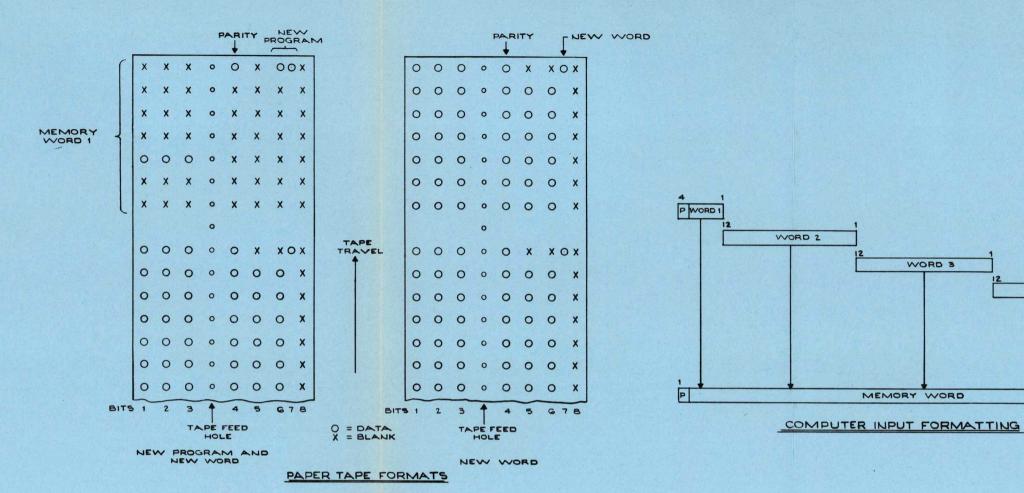

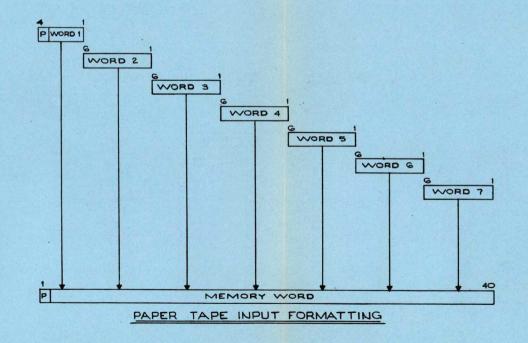

| 5-8    | Computer and Tape Word Formats                                | 5-27  |

| 5-9    | Functional Block Diagram, Decom Memory Load Logic             | 5-29  |

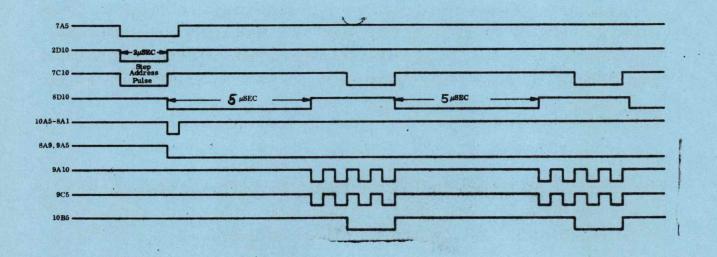

| 5A-1   | Memory/Decom Interconnection                                  | 5A-2  |

| 5A-2   | Memory Section                                                | 5A-4  |

| 5A-3   | Magnetic Core Storage Geometry                                | 5A-6  |

| 5A-4   | Typical Hysteresis Loop                                       | 5A-8  |

| 5A-5   | Decom Memory                                                  | 5A-13 |

| 5A-6   | Decom Memory Address Decoder                                  | 5A-15 |

| 5A-7   | Flip-Flop Circuit                                             | 5A-19 |

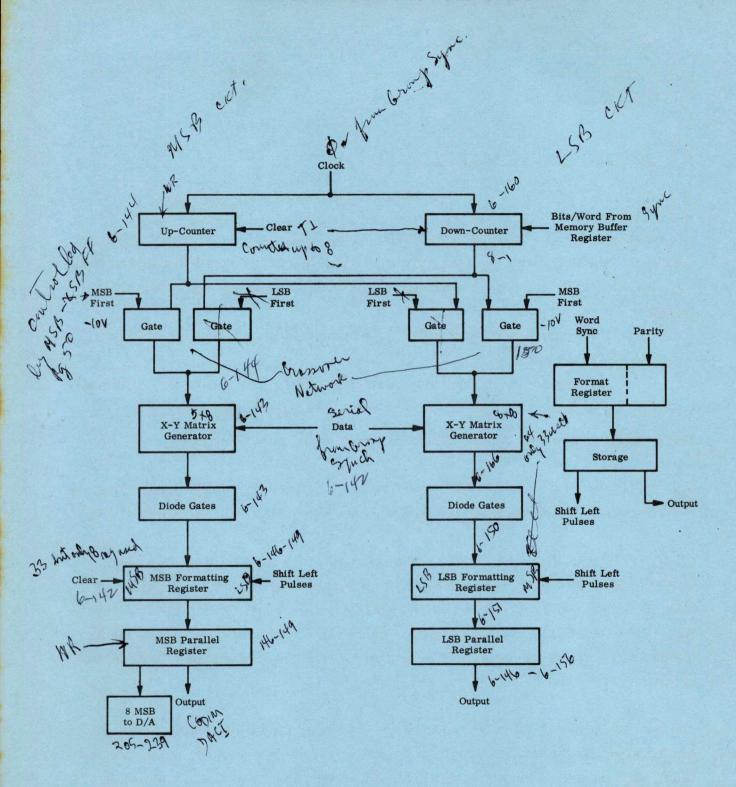

| 6-1    | MSB and LSB Parallel Register, Simplified Block Diagram       | 6-2   |

| 6-2    | MSB and LSB Truncated Characters Controls                     | 6-9   |

| 6-3    | MSB and LSB Truncation Registers, Simplified Block Diagram    | 6-11  |

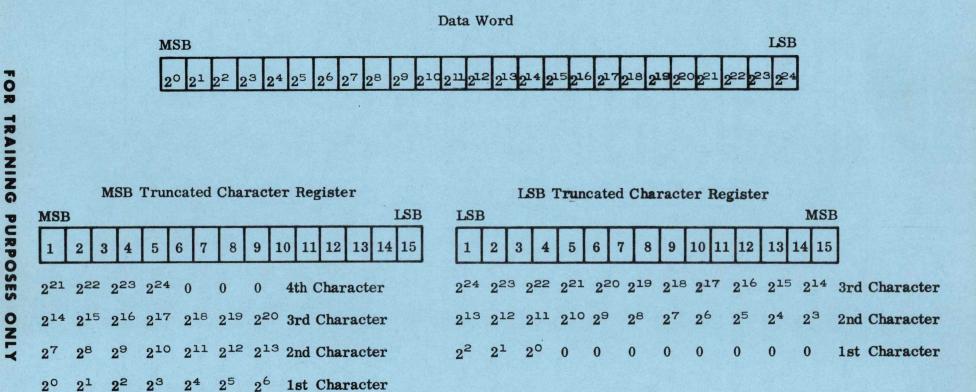

| 6-4    | MSB and LSB Truncated Characters Formation Simplified Diagram | 6-14  |

| 6-5    | MSB and LSB Truncation Registers, Timing Diagram              | 6-15  |

| 6-6    | Decimal Display 2A3, 2A4, and 2A5 Front Panel                 | 6-25  |

| 6-7    | Binary Display 2A6 Front Panel                                | 6-25  |

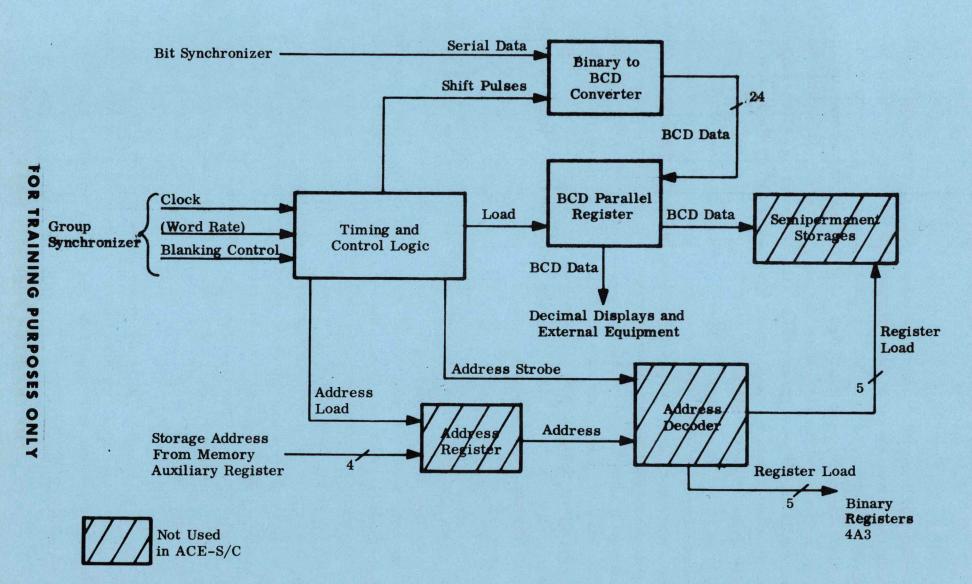

| 6-8    | Decimal and Binary Displays Block Diagram                     | 6-28  |

| 6-9    | Decimal and Binary Display Timing Diagram                     | 6-30  |

| 6-10   | Digital-to-Analog Converters Block Diagram                    | 6-33  |

| 6-11   | Digital-to-Analog Converters, Normal Operation Timing Diagram | 6-36  |

| 6-12   | Digital-to-Analog Converters, Test Operation Timing Diagram   | 6-39  |

| 6-13   | Binary-to-BCD Converter, Simplified Block Diagram             | 6-41  |

| 6-14   | Binary-to-BCD Register and Converter                          | 6-43  |

| 6-15   | Binary-to-BCD Converter Timing Diagram                        | 6-44  |

# LIST OF ILLUSTRATIONS (Cont.)

| Figure | <u>Title</u>                                                 | Page  |

|--------|--------------------------------------------------------------|-------|

| 7-1    | Computer Interface Unit Front Panel View                     | 7-2   |

| 7-2    | Twelve-Bit Status Response Word from Computer Interface Unit | 7-6   |

| 7-3    | Computer Interface Unit Block Diagram                        | 7-8   |

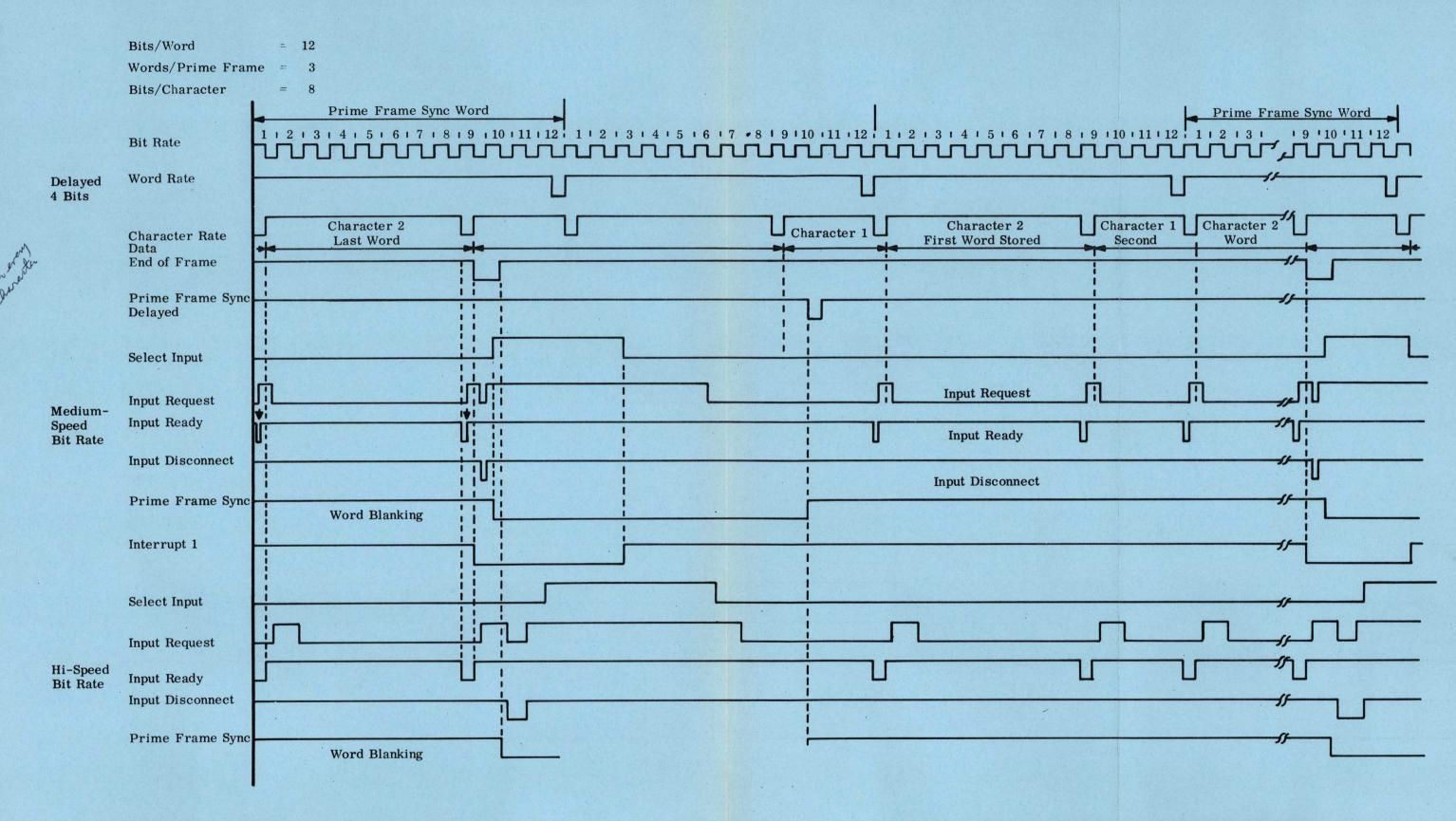

| 7-4    | Computer Interface Unit Timing Diagram                       | 7-9   |

| 7-5    | Program Check Function Timing Diagram                        | 7-24  |

| 7-6    | Sequential Loading of Decommutator Memory From Computer      | 7-27  |

| 7-7    | Sequential Transfer of Data Words to Computer                | 7-28  |

| 8-1    | PCM Signal Simulator 1A6 Front Panel                         | 8-1   |

| 8-2    | PCM Signal Simulator 1A6 Rear Panel                          | 8-1   |

| 8-3    | PCM Signal Simulator Simplified Block Diagram                | 8-7   |

| 8-4    | PCM Signal Simulator Timing Diagram                          | 8-13  |

| 8-5    | Shift Register Set                                           | 8-17  |

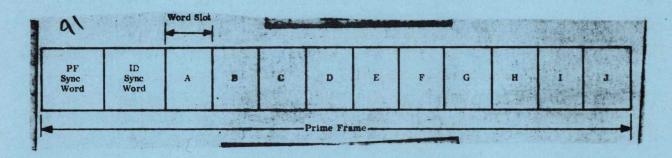

| 9-1    | Serial PCM Data Train (Normal Commutation)                   | 9-2   |

| 9-2    | Serial PCM Data Train (Super Commutation)                    | 9-2   |

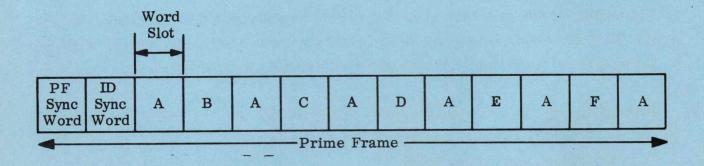

| 9-3    | Prime Frame/Major Cycle                                      | 9-3   |

| 9-4    | Samples per Second, Sub-Commutated Words, Time Slots 4 and 9 | 9-5   |

| 9-5    | Preacquisition Word Formats                                  | 9-13  |

| 9-6    | Example of Preacquisition Block                              | 9-15  |

| 9-7    | Example of PCM Data Train With Two Subcommutated Rates       | 9-16  |

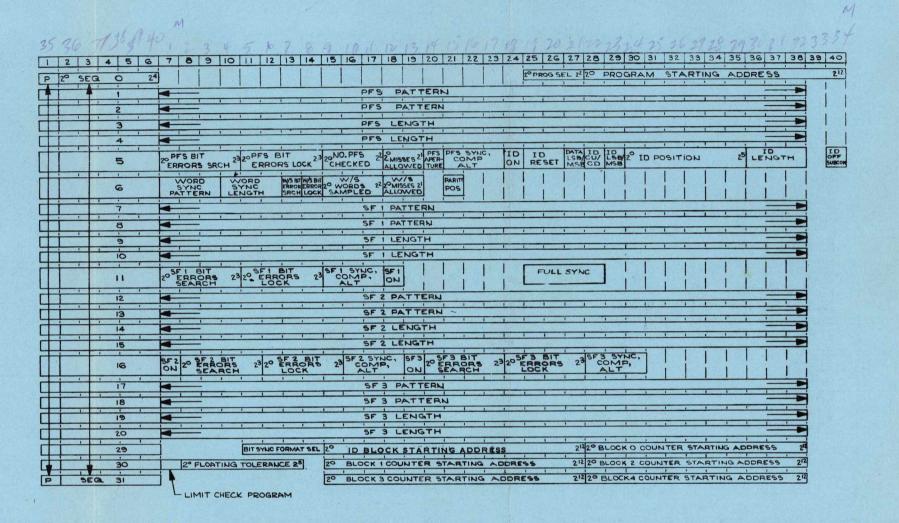

| 9-8    | Instruction Word Formats                                     | 9-17  |

| 9-9A   | Apollo Format (A/B) (51.2 kbs)                               | 9-22  |

| 9-9B   | Apollo Format (A/B) (51.2 kbs)                               | 9-23  |

| 10-1   | Interconnection Diagram                                      | 10-2  |

| 10-2   | DACI/Decommutator Interface                                  | 10-4  |

| 10-3   | Computer Word Format                                         | 10-7  |

| 10-4   | Deviation of psi Versus Time                                 | 10-9  |

| 10-5   | Direct Access Computer Interface                             | 10-11 |

| 10-6   | Direct Access Computer Interface Timing Diagram              | 10-14 |

## LIST OF TABLES

| Table | <u>Title</u>                                                  | Page  |

|-------|---------------------------------------------------------------|-------|

| 1-1   | Leading Particulars                                           | 1-22  |

| 1-2   | Condensed Data                                                | 1-23  |

| 3-1   | Bit Sychronizer Controls and Indicators                       | 3-2   |

| 3-2   | Parameters for Incoming Formats                               | 3-7   |

| 5-1   | Memory Contents                                               | 5-3   |

| 5-2   | Program Control, Controls and Indicators                      | 5-8   |

| 5A-1  | Characteristics of Model 8192 I 42 Memory                     | 5A-10 |

| 6-1   | MSB and LSB Controls                                          | 6-10  |

| 6-2   | Logic Decisions and Steps in Forming Truncated Characters     | 6-13  |

| 6-3   | Decimal Display Controls and Indicators                       | 6-24  |

| 6-4   | Binary Display Controls and Indicators                        | 6-26  |

| 6-5   | Digital-to-Analog Converter Address Assignments and Locations | 6-32  |

| 6-6   | LSB                                                           | 6-45  |

| 7-1   | Controls and Indicators                                       | 7-3   |

| 7-2   | Computer Instruction Words                                    | 7-4   |

| 8-1   | PCM Signal Simulator Controls and Indicators                  | 8-2   |

| 9-1   | Comparison of PCM Data with Writing                           | 9-1   |

| 9-2   | Preacquisition Word Contents                                  | 9-7   |

| 9-3   | Operational Codes                                             | 9-19  |

| 9-4   | Routing Codes                                                 | 9-20  |

|       |                                                               |       |

#### FOREWORD

Throughout this manual many references are made to figures that are not a part of this manual. These figures are logic diagrams in a separately bound document. The callouts for these diagrams are recognizable in this text by the word "figure" being in all lower case letters. Callouts for illustrations that are a part of this manual are referred to with an upper case (Figure \_\_) designation.

#### SECTION 1

#### INTRODUCTION

#### 1.1 GENERAL

The purpose of the series 540 PCM decommutator is two fold. First, to decommutate serial PCM telemetry data from the Apollo spacecrafts, assign routing addresses and drive digital and analog displays such as meters, lights, and recorders in the ACE-S/C control room. Second, to decommutate serial PCM telemetry data from the Apollo spacecrafts, perform preprocessing, storage assignment, and route to the ACE-S/C downlink computer for further processing and display.

The decommutator is a programmable device; therefore, many variables could be introduced if presented as a general-purpose system. However, this manual will describe only the usage as it applies to the ACE-S/C present programmed equipment configuration. But, bear in mind that as a result of the evolution of the ACE-S/C programming philosophy, certain inconsistencies between this written description and actual programs may exist.

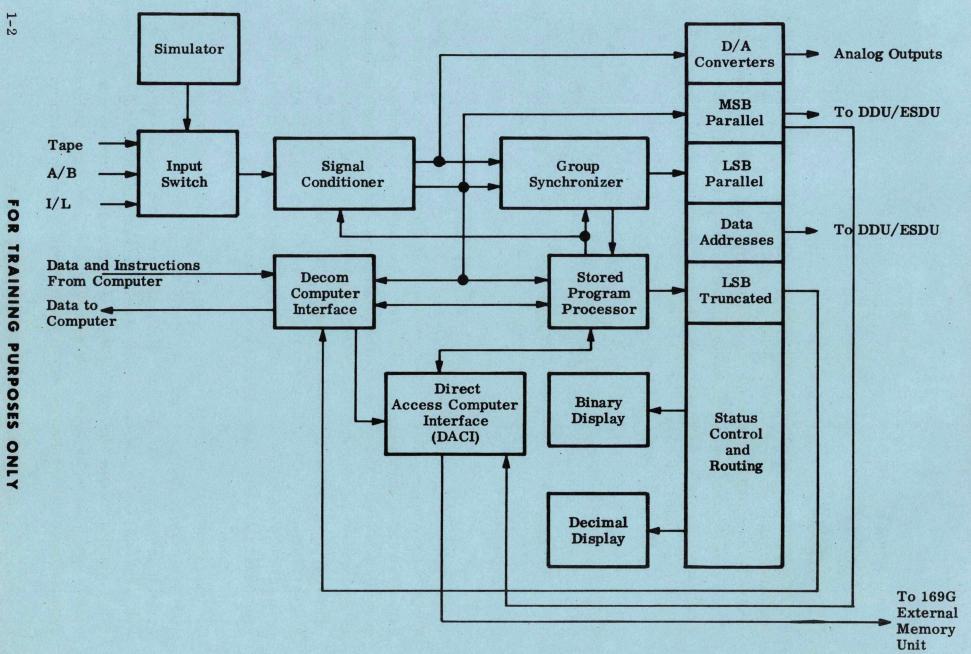

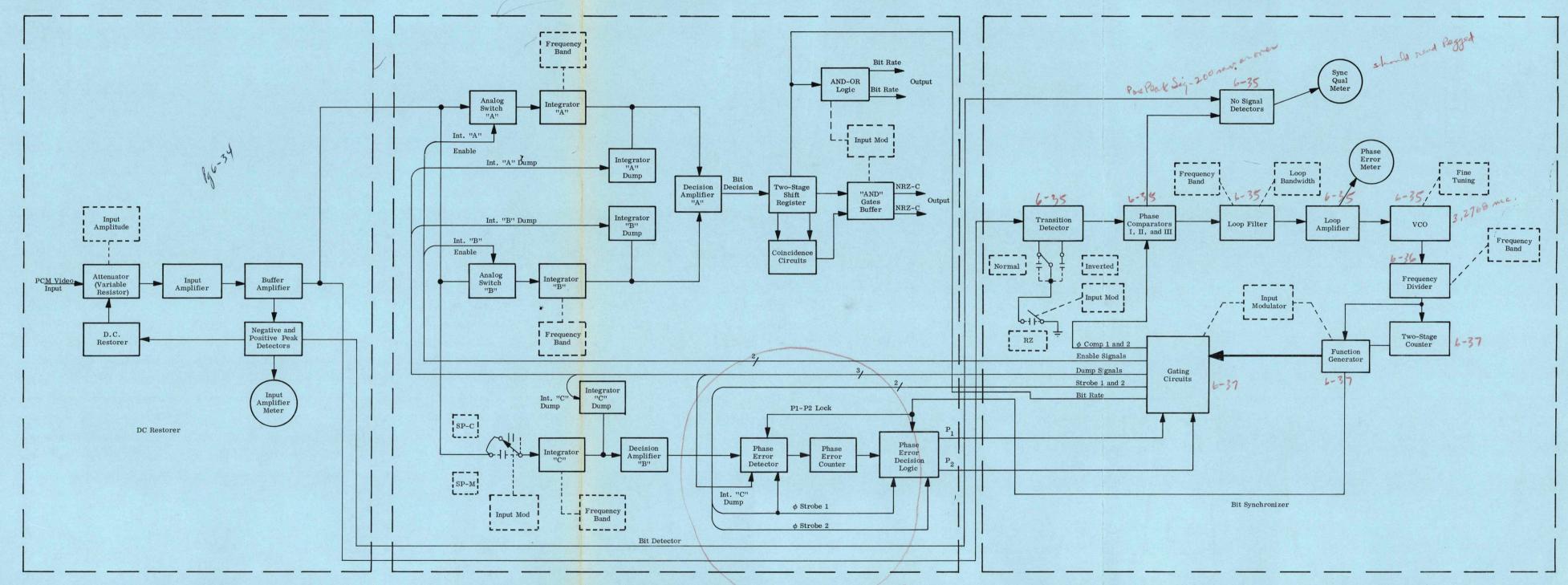

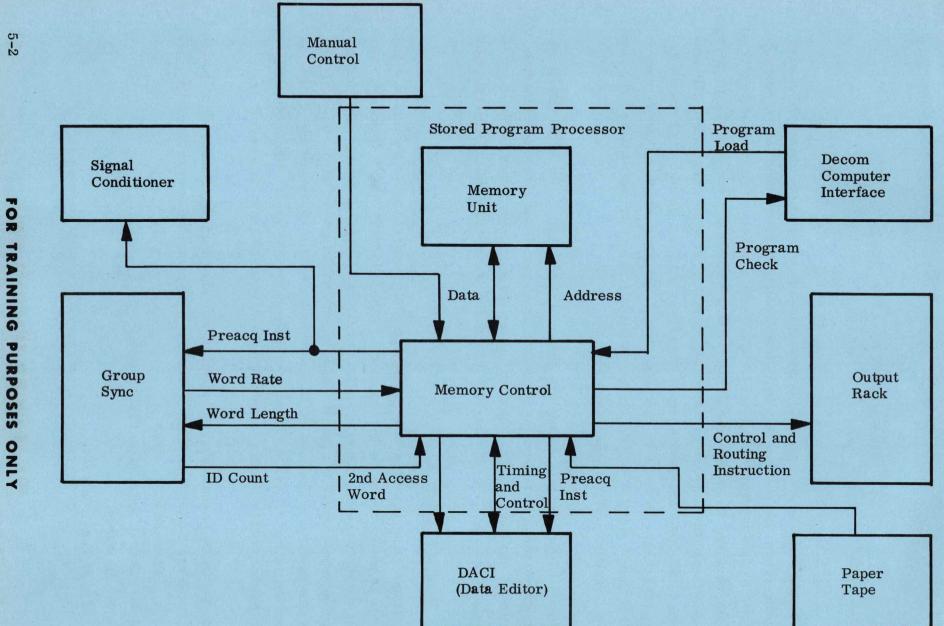

## 1.2 FUNCTIONAL DESCRIPTION

The PCM decommutator (Figure 1-1) is capable of operating over a wide range of input telemetry data and can also accept a variety of types of PCM coding and various arrangements of parameter data specified by the telemetry system. To meet the demands of versatility in operating range and the requirements of recording, display, and data processing systems, the decommutator operates under program control. In the ACE-S/C configuration, both the interleaved and the airborne decommutation programs can be stored by the decommutator memory simultaneously. This gives the capability of rapid acquisition for each type of input available.

To obtain synchronization on the incoming data, the decommutator must be programmed with the criteria for bit synchronization, prime frame synchronization, and major cycle synchronization. Bit synchronization exists when the decommutator defines the exact same period of time as was generated by the telemetry system and decodes the weighted digit in its true form. Prime frame synchronization exists when the decommutator recognizes the beginning of a repetitive group of coded bits which divide a given amount of time into equal parts. In the ACE-S/C telemetry system this code

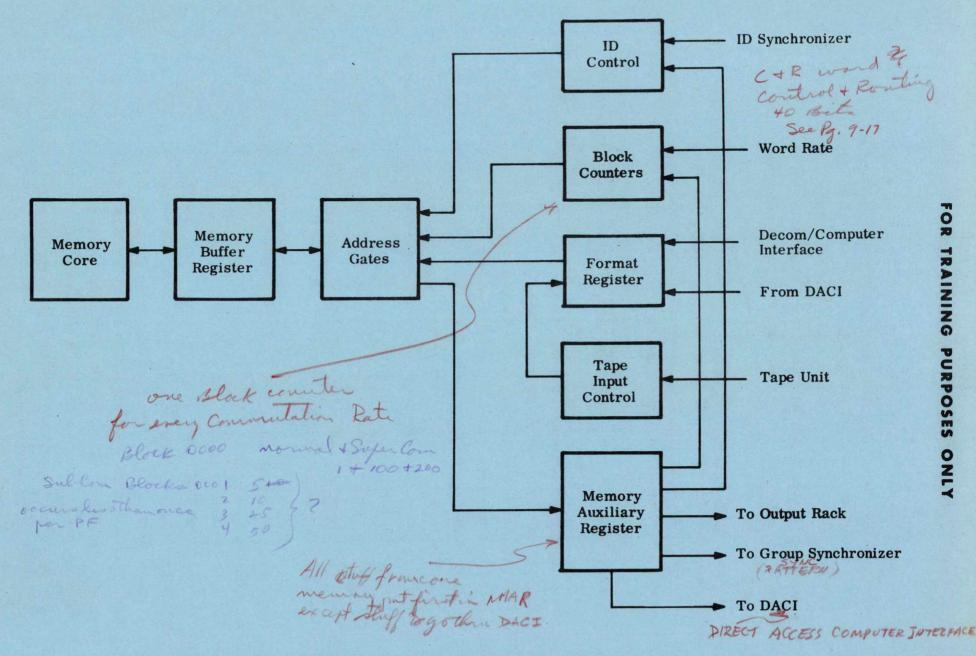

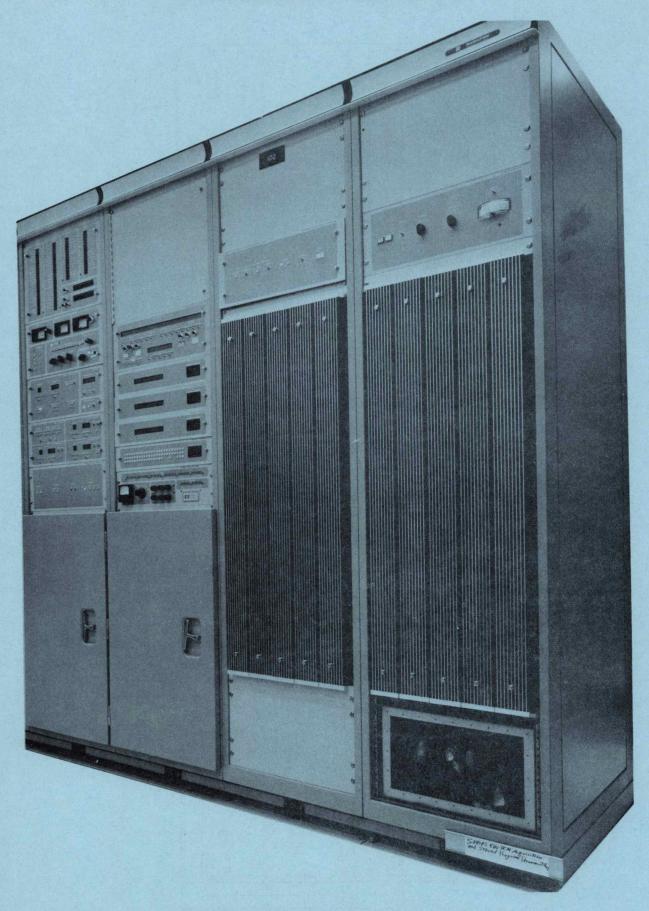

Figure 1-1. PCM Decommutator

appears 50 times per second; therefore, the system divides a one-second time span into 50 equal units. Major cycle synchronization is when the decommutator recognizes a specific prime frame and can then define the same real-time second as generated by the telemetry system. After completing these three steps of synchronization the decommutator memory is synchronous with the input data; therefore, the decommutation process can be initiated.

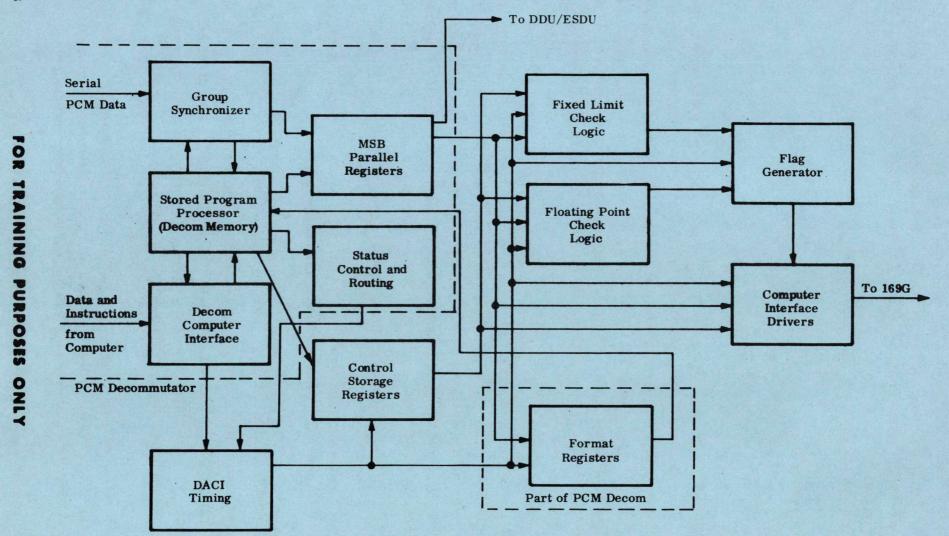

The basic parts of the decommutator are the signal conditioner, the group synchronizer, the stored program processor (memory), the output rack, and the decom/computer interface (normal and DACI). All operate under program control of the particular program in operation.

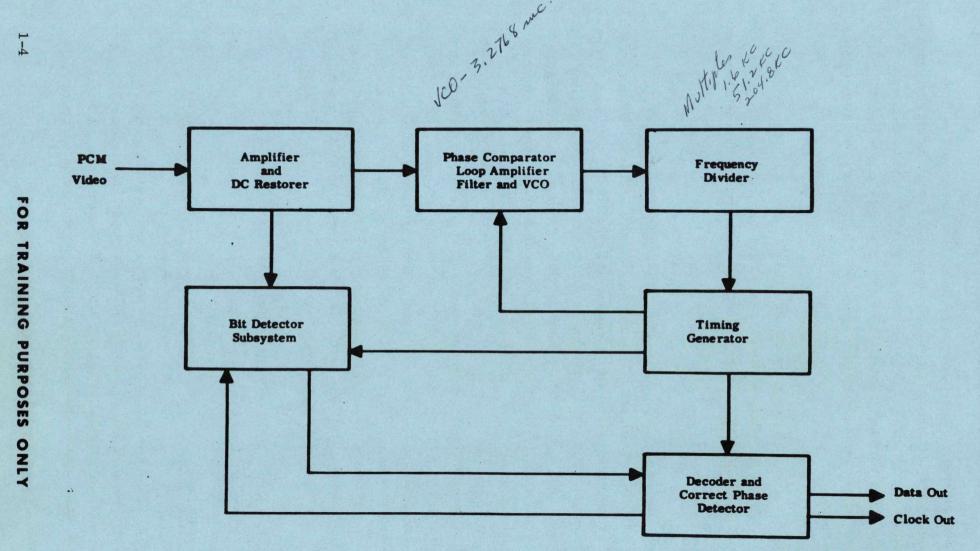

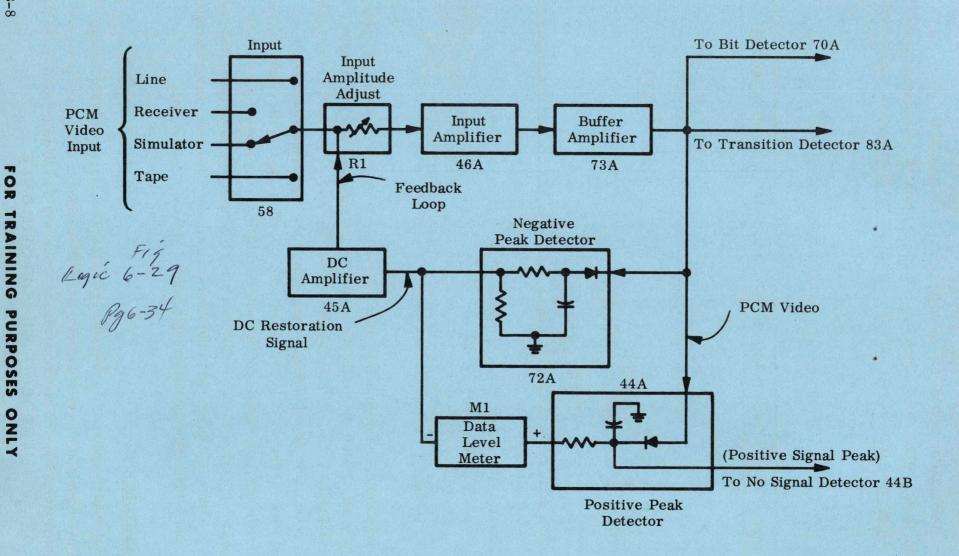

#### 1.3 SIGNAL CONDITIONER

The PCM signal conditioner (Figure 1-2) accepts the incoming split-phase pulse code modulated telemetry signal, conditions the pulses, and synchronizes with each bit to control the decommutator timing. The signal conditioner acts upon the incoming PCM signal to restore the data to a ground level and provide a stable output for the entire decom. This is performed to enable more efficient decommutation by the remaining sections of the decommutator.

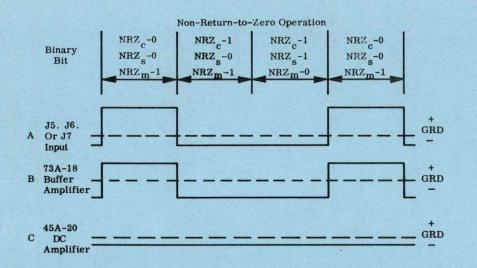

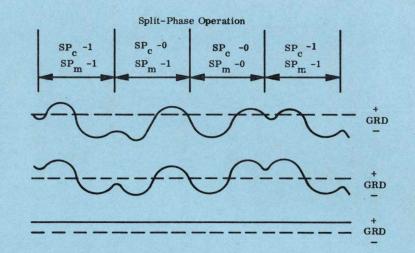

Decommutation of the incoming PCM data can only be performed if the decommutator timing is synchronized with the bit rates of the commutation processes. Therefore, various time slots containing discrete words can be processed or decommutated to reproduce the exact data used in modulation during the commutation of the spacecraft parameters. The input signal to the decommutator when used in the ACE-S/C capacity is split-phase-C PCM data. This input signal is then converted to NRZ-C and NRZ-M with the NRZ-C being sent to the group synchronizer.

The signal conditioner consists of three principal subsystems:

- a. A dc restorer.

- b. A bit synchronizer.

- c. A bit detector.

The dc restorer accepts the serial data train as an input and supplies level-restorer signal to the bit synchronizer and bit detector. The bit synchronizer outputs are a clock at the bit rate of the data and timing signals for the system. The bit detector accepts the clock timing signals from the bit synchronizer and the data train from the

Figure 1-2. PCM Signal Conditioner

dc restorer. It then produces reconstructed serial NRZ-C digital data as an output. Thus, the bit detector performs the basic decision of whether a binary "one" or "zero" exists for each bit.

For split-phase data, the clock defines only the carrier frequency, for the bit location is subject to an ambiguity. The bit detector resolves this ambiguity, locates the bit position, and makes the bit polarity decision. The phase decision is made on the basis of several bits to reduce the probability of an error as a result of noise and uses as criteria the definition of SP-C data where two adjacent half cycles of a bit period are never equal.

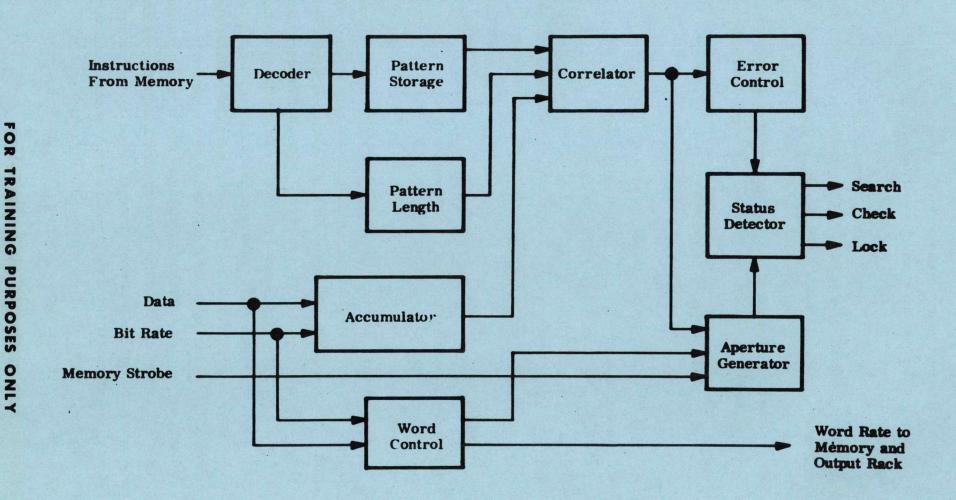

#### 1.4 GROUP SYNCHRONIZER

The group synchronizer performs two different types of synchronization. First, it must establish prime frame synchronization and then major cycle or ID synchronization. The information used as criteria to perform these functions must be programmed in memory and called up as instructions for the synchronizer as follows:

- a. Prime frame length.

- b. Prime frame pattern.

- c. D counts up or down.

- d. Location of ID word.

- e. Number of errors accepted in synchronization.

- f. Number of prime frames to be checked.

- g. ID MSB/LSB first.

The serial data from the signal conditioner is shifted through a shift register (accumulator) of the frame synchronizer (Figure 1-3) where a bit-by-bit comparison of the input data is made with the pattern and length placed in storage after memory callup. When the pattern of the prime frame sync word (32 bits in ACE-S/C) matches the stored pattern, a first prime frame sync signal is generated and enables the check mode of operation. Heretofore, the synchronizer has been in the search mode looking for a correlating pattern. This first prime frame sync signal not only enables the check mode but informs memory that a pattern has been found. Since it is highly possible that a sync pattern can be found any place in a prime frame with an arbitrary group of data bits, memory must instruct the frame synchronizer where the next pattern is located. To do this, it generates a signal call aperture which enables a prime frame sync pulse to be checked the next time it should appear. If the first sync pulse was a valid one, then the next prime frame sync pulse should fall within the aperture; however,

Figure 1-3. Prime Frame Synchronizer

if the first sync pulse was invalid, it is extremely unlikely that at the same time in the next frame an arbitrary group of 32 bits will match the pattern and generate a sync pulse; therefore, the pulse would not fall within the aperture and would generate an error. If this exceeds the number of errors allowed, then the system returns to the search mode to obtain the proper sync word.

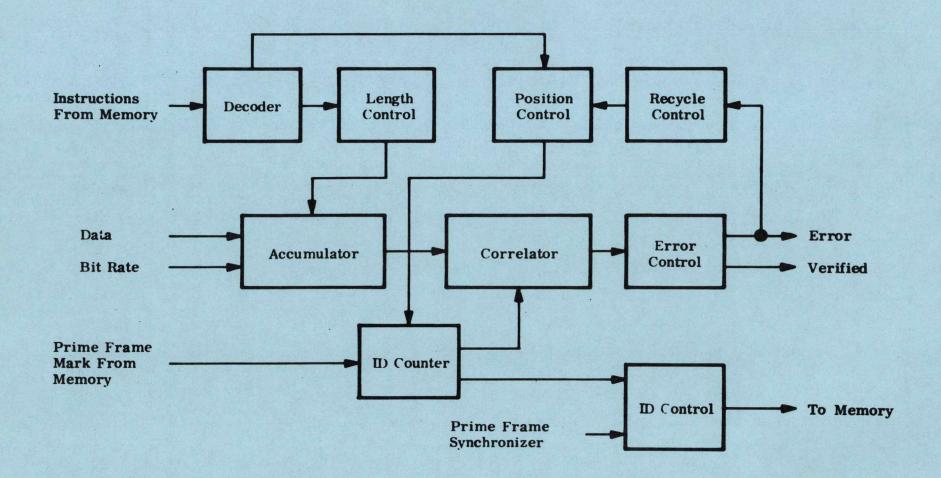

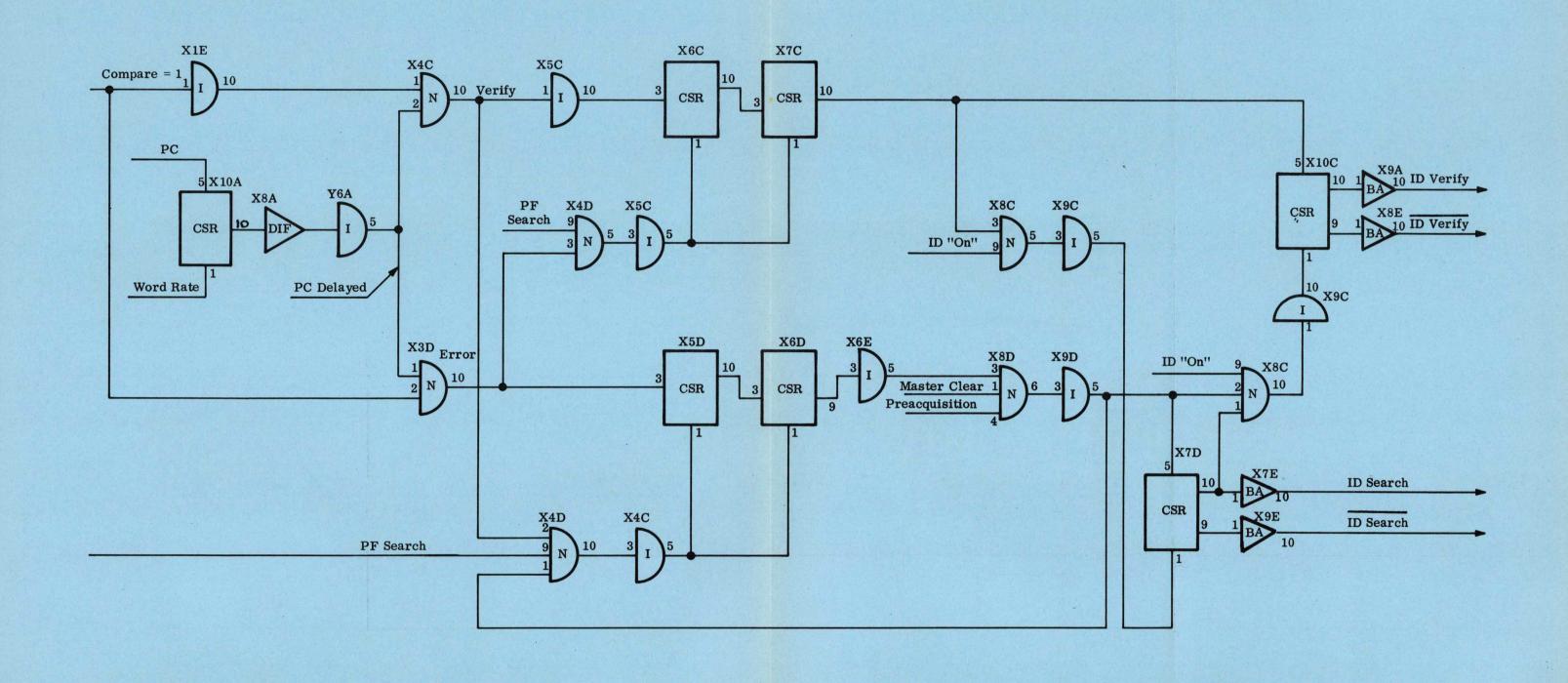

After the proper sync word is obtained and the check mode entered, the synchronizer checks the sync word with the pattern a predetermined number of times to establish that proper synchronization has been obtained. During this mode, the ID synchronizer is enabled.

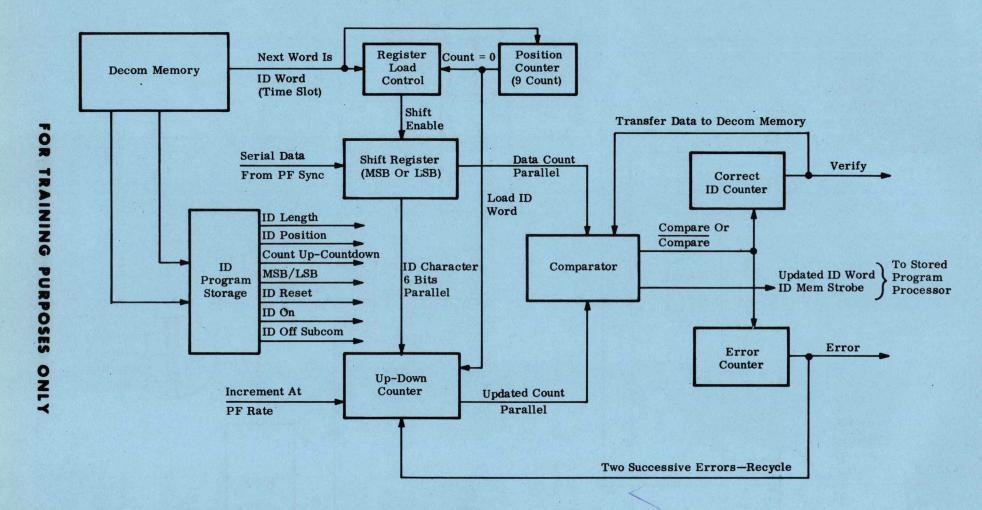

The function of the ID synchronizer (Figure 1-4) is to enable the unit to begin decommutation as readily as possible. Memory instructs the group synchronizer where the ID word occurs and enables the ID word to be detected. This detected word is sent to memory control where it jumps the memory sequence to the prime frame detected. At this point, major cycle sync has been obtained. Each prime frame contains an ID word and during this time slot the new ID is checked against the updated contents of the synchronizer. If these two do not correlate, the ID synchronizer returns to search.

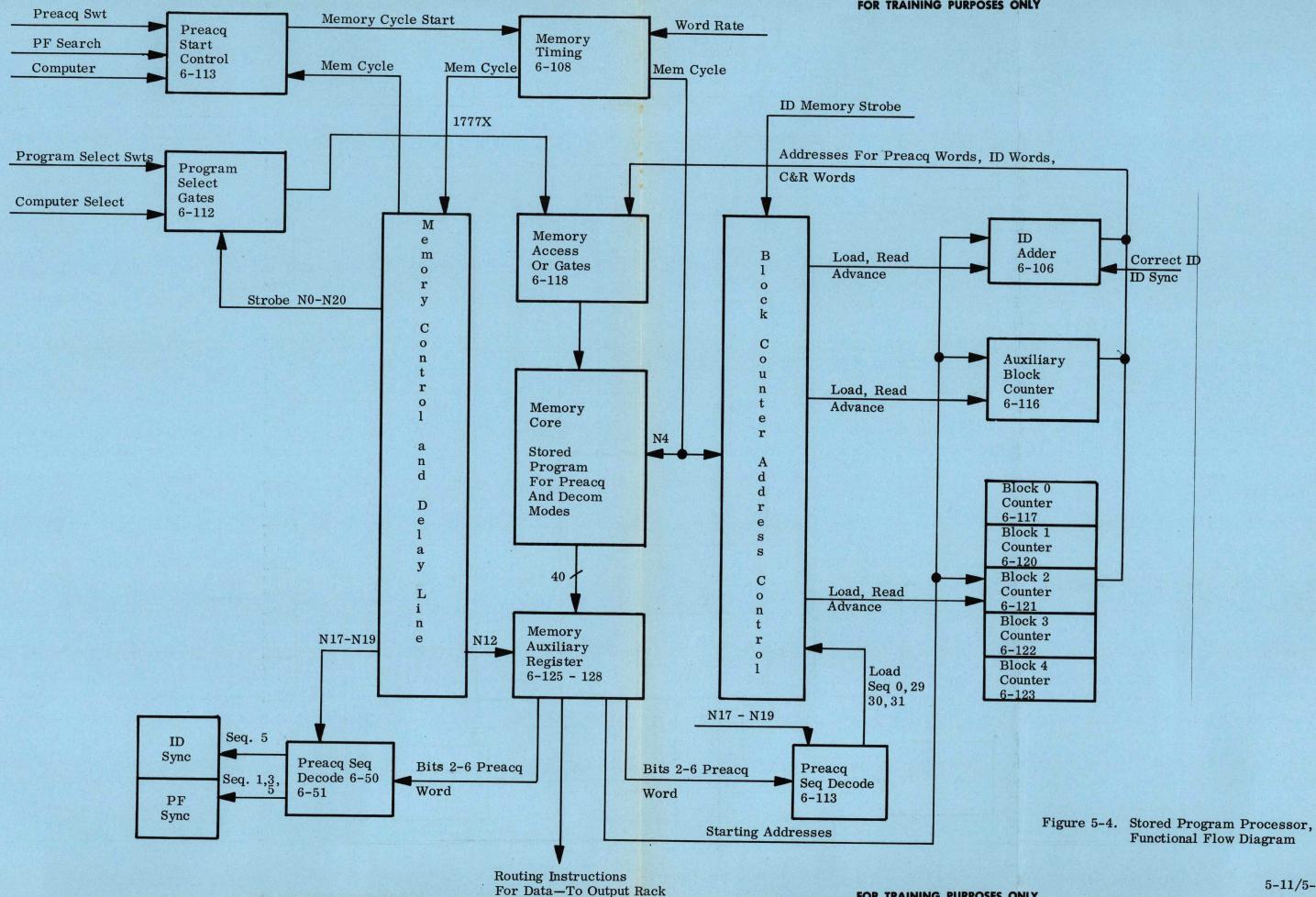

## 1.5 STORED PROGRAM PROCESSOR

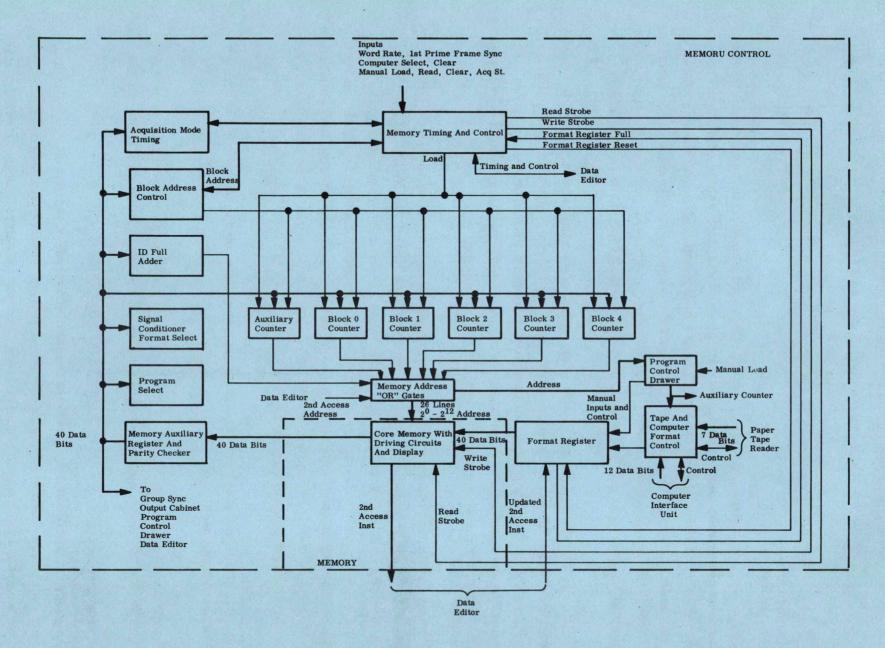

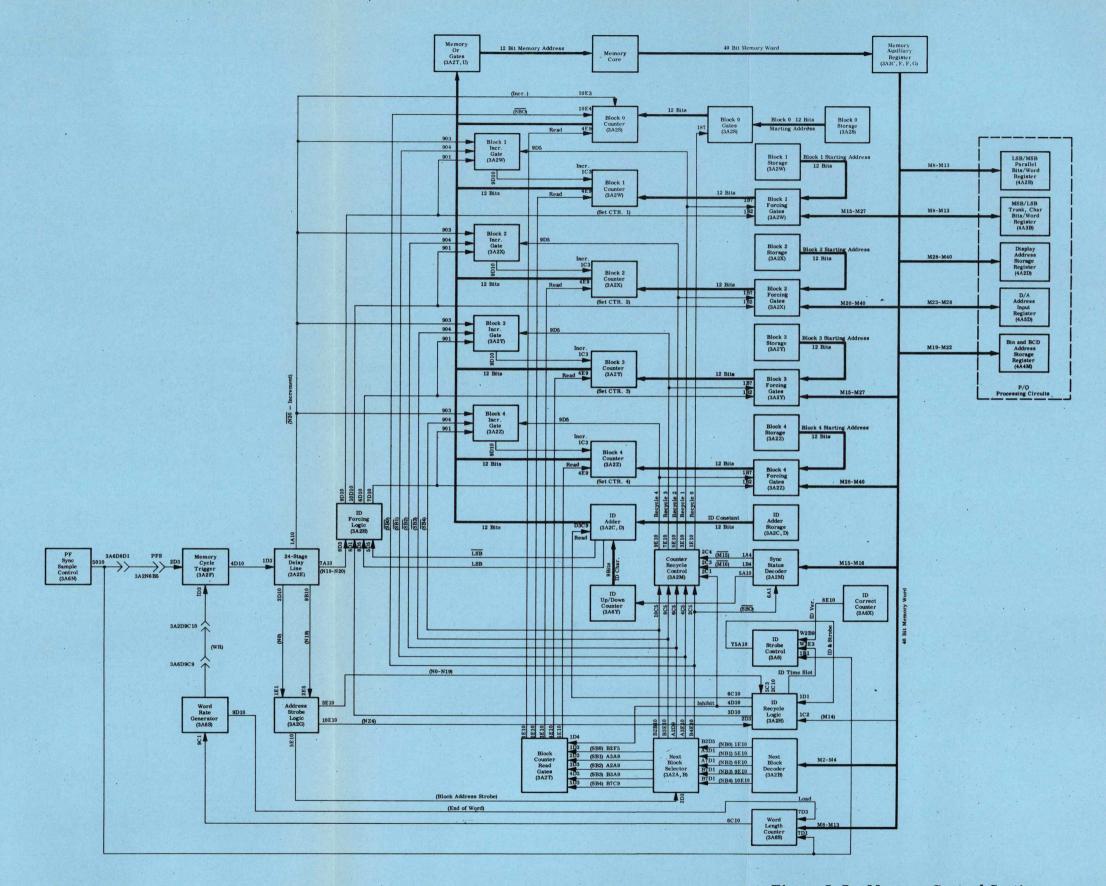

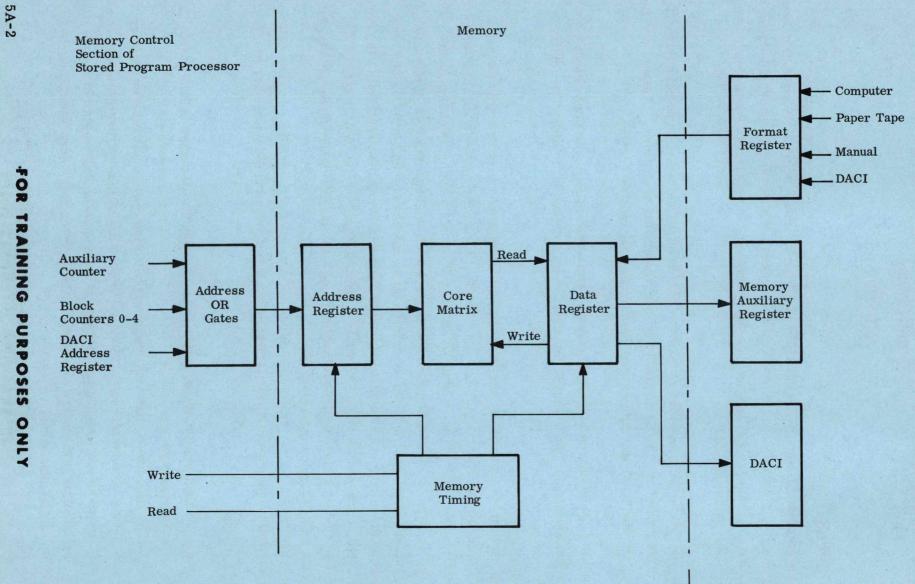

The stored program processor (Figure 1-5) provides storage for key instruction words used by the group synchronizer, DACI and the output rack for processing data under program control. It also stores synchronized code information that enables the group synchronizer to get in step with the data train and to reacquire synchronization with a minimum of words if synchronization is lost. The stored program processor consists of random-access core-memory, input/output devices for formatting, control logic for loading and unloading instructions, and a memory control panel for entering or selecting data manually. The core-memory has a storage capability for 8192, 40-bit words.

The stored program processor is capable of operating on one decommutation program while loading another into the memory on a priority basis (from tape and control panel only). This is accomplished by arbitrarily dividing the core memory into eight program stored sections designated 1 through 8. If this arbitrary division is adhered to, each section of memory is capable of storing 1024, 40-bit words. Of course, it is entirely possible to have only one or two programs take up the entire 8192, 40-bit storage locations.

Figure 1-4. ID Synchronizer

Figure 1-5. Stored Program Processor

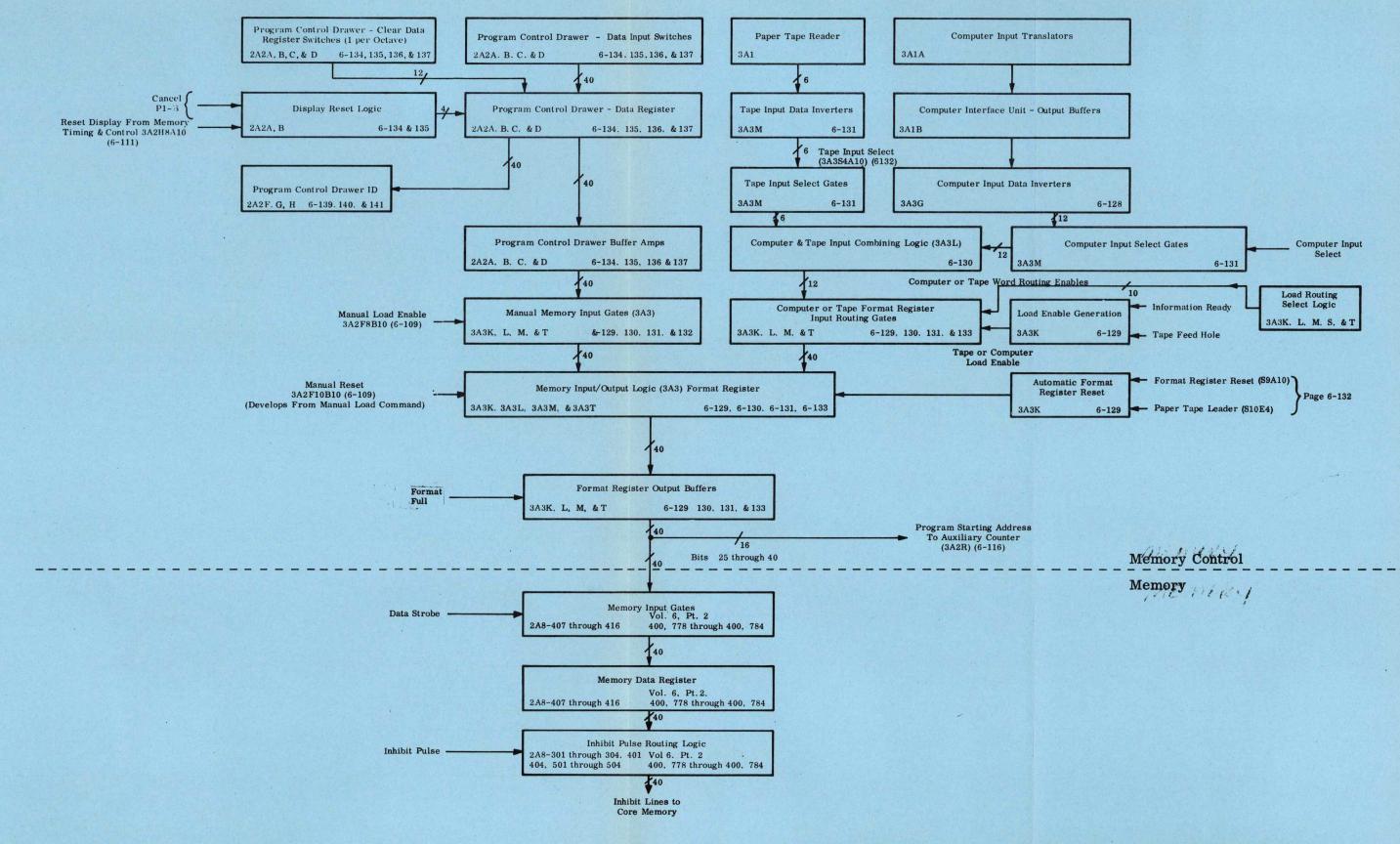

A program can be loaded into the stored program processor from a digital computer, the paper tape reader, or manually from the program control panel. For the program entry, a 13-bit address for starting the loading is the first word in a given program. Thereafter, the stored program processor updates the address for sequential loading of memory slots. A program can be loaded into one program section of memory, while the stored program processor is operating from another program section, provided the word being decommutated has a word length of at least seven bits.

Program instruction words from a computer and the paper tape reader are formatted into the instruction word format used by the stored program processor. If the instruction word is from a computer, it is furnished in the form of four words or characters. one 4-bit and three 12-bit words or characters. The words or characters are formatted into a 40-bit word by the formatting gates and the 40-bit word is loaded into the data register. Word formatting is controlled by the format counter and decoder. This functional area loads the correct set of formatting gates based upon the number of words or characters transferred. For the first four-bit word or character transferred from the computer, the format counter loads the first four most significant bit formatting gates. It notes the fact that a word has been transferred and when another word is ready, loads the next set of formatting gates (corresponding to the 12 next most significant bits of the instruction word). Upon completion of word formatting, the word is transferred to the core-memory register by the master load gates. The word is subsequently stored in the address designated by the program. When this word is stored, the computer sends another program word, and the counter address is updated, and another word is stored in the next sequential address of the memory. The process continues until a complete program is loaded.

A similar process is required for loading instruction words from the paper tape reader. The starting address for program loading is the first word on the tape. The tape reader furnishes input words in the form of one 4-bit word or character and six 6-bit words or characters. These input words are formatted and stored in the memory by the same process described for computer inputs. The process continues until a completed program is loaded. Instruction words entered from the program control panel do not require formatting. The starting address for storing the words is manually entered at the program control panel. Thereafter, the load/unload counter updates the address for sequential loading of the memory. No manual loading can be performed during decommutation; however, the address of stored instruction words can be changed using controls on the program control panel.

The stored program processor operates in two basic modes—preacquisition and decommutation. In the preacquisition mode, all the criteria is called out of memory and is the criteria for memory control in the same manner discussed in the synchronizer. Memory is controlled during the decommutation process by block counters which are jammed to the starting addresses of the data contained in prime frame one of the telemetry input format for a particular program. These block counters fall into two categories—ID and control and routing. When the ID word is verified, the ID block counter causes the block counters used for control and routing to be jammed to the address of the prime frame when major cycle synchronization is found. At this time, the exact location of every word is known in the major cycle.

The control and routing format contains instructions for memory control and the formatting process performed by the output rack. The next block instruction causes the block counters to access the next memory location applicable to the incoming data word. The instructions contained in a memory location are for the next incoming word. Therefore, the decommutator operates one word time ahead of the incoming data.

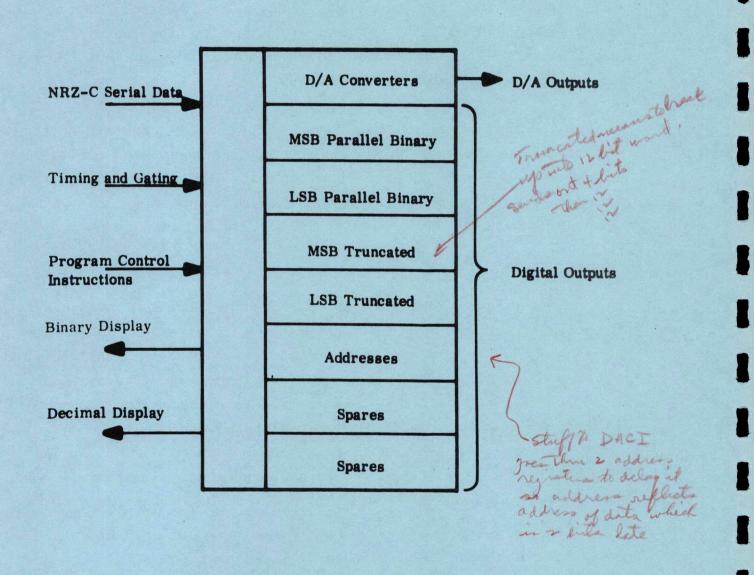

## 1.6 OUTPUT RACK

The output format devices (Figure 1-6) are used to convert the NRZ-C data into the proper format determined by the equipment to receive the data word. The gating of the data word into the proper output register is determined by the program in the stored program processor. The output format control unit receives serial reconstructed NRZ-C data from the output of the PCM signal conditioner, timing from the group synchronizer, and program control instructions from the memory. The output format control unit provides analog and digital data outputs to the external units. Parallel binary and binary-coded-decimal (BCD) data are also provided to data displays on the system control panel, which gives the operator the capability of displaying any incoming data word in its time binary or decimal value.

The outputs of the digital-to-analog converter circuit are routed to the event distribution and recorder patching unit to be distributed to the analog recorders located in the computer room. The data routed to the downlink computer comes from the least significant bit truncated register or DACI where they are transferred as 12-bit and 30-bit parallel data words respectively. The data transmitted to the decommutator distribution and event storage and distribution unit, in the control room, are routed through the MSB parallel register. The addresses (from memory) applied to the data of the

Figure 1-6. Output Devices

MSB parallel register are routed through the data address register. The remaining output devices are not used in the application with ACE-S/C.

#### 1.6.1 DIGITAL-TO-ANALOG CONVERTERS

The digital-to-analog (D/A) converters convert the incoming digital data to analog voltages to be distributed to the event distribution and recorder patching unit. The decommutator contains a total of 60 D/A converters of which 40 are used in the transmission of data to the recording and patch unit. The D/A converters are selected by the stored program processor. The memory instruction performs three functions in controlling the D/A devices:

- a. Controlled designation of which D/A will convert the incoming data word.

- b. When the D/A will be selected.

- c. Synchronization of gating the incoming data into the converter.

#### 1.6.2 MSB/LSB PARALLEL OUTPUTS

The function of this group is to provide as an output all data words in both MSB and LSB first formats at the same time. Any data word may be from 4 to 64 bits long. The different conditions under which the registers can accept data are:

- a. No parity or word synchronization code bits in the data word and either MSB or LSB first.

- b. Parity and word synchronization code bits present in the data word either at the beginning or the end of the word and either MSB or LSB first.

The program of the system being monitored dictates the mentioned conditions. The data is serial when received and is converted to parallel by a formatting process.

After the entire word has been formatted, the new data word is shifted left the number of places corresponding to the number of parity and word synchronization code pulses contained in the word. The action takes place if word parity and word sync are used. In the ACE-S/C application, word parity and word sync are not used.

The MSB formatting and parallel registers are composed of 33 stages while the LSB formatting and parallel registers are composed of 64 stages. The reason for this is that it is only necessary to acquire one more MSB bit than half the word length to determine the value of the measurand while the entire word in LSB form must be gathered to determine which bits are the MSB of the word.

Also contained in the MSB/LSB parallel registers logic is the 12-bit display address register which feeds the ESDU and the console control logic circuits. This address with a read pulse is gated out in parallel with the contents of the MSB parallel register. The LSB parallel drives the decom binary display.

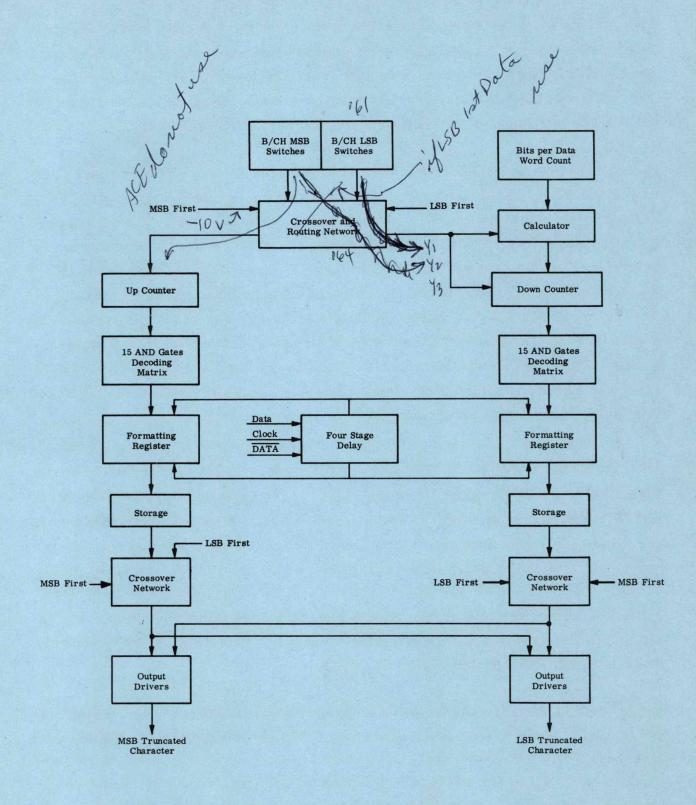

#### 1.6.3 MSB/LSB TRUNCATED OUTPUTS

Truncate means to cut up or cut off. Truncation circuitry is used when the decommutator operates in conjunction with 160G computer. If the incoming data word is too large, the truncated output will be in characters whose lengths are compatible with the computer input. This allows the decommutator to maintain its versatility and still allow the remaining units of the ACE-S/C system to function at their specific capability. The MSB/LSB truncated unit operates basically identical to the MSB/LSB parallel unit with the exception of a calculator which divides the incoming word by a factor of two until a remainder is obtained. This remainder is outputted as the first truncated character which will vary in length with varying lengths of incoming data. However, the remaining characters will all be the same dependent upon the initial size of the incoming data word.

The ACE-S/C application utilizes the least significant truncated circuits and outputs the data words to the decommutator/computer interface unit.

#### 1.6.4 DECIMAL AND BINARY DISPLAYS

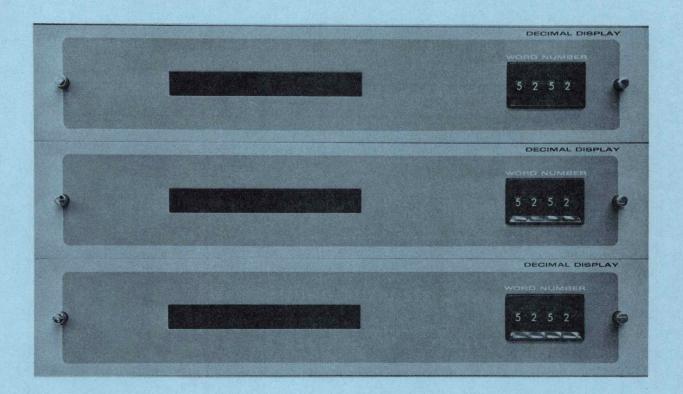

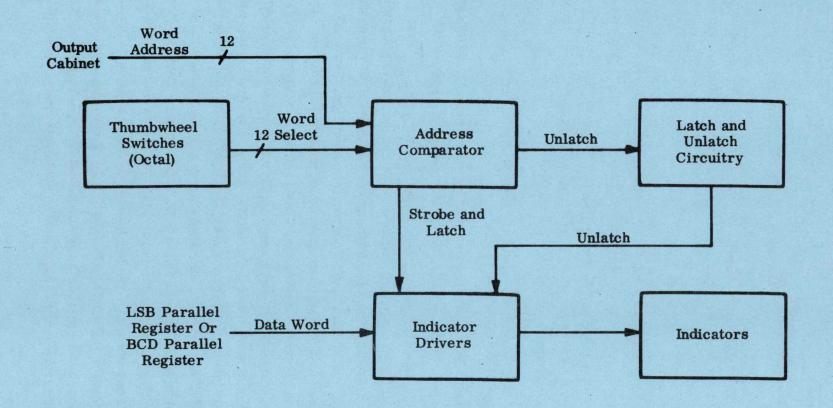

Three decimal displays and one binary display provide the capabilities for selecting and displaying the decimal and binary values of words from registers in the output rack.

The three decimal displays operate independently; that is, all three can be used concurrently to select and display one word or three different words. Any word in the data train up to octal 7777 (decimal 4095) can be selected on any one display. The decimal displays are wired for word values up to 999, 999; however, the displays only contain modules for word values up to 999.

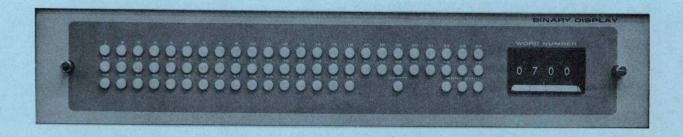

The binary display provides the capabilities for selecting and displaying any of 4095 data words. A 64-bit word plus parity can be displayed. In addition, word synchronization can also be displayed.

The decimal and binary displays function identically, except for the fact that the decimal displays must decode the BCD inputs. The decoding operation performed for decimal displays can be ignored when evaluating the operation of the binary display.

## 1.7 DECOMMUTATOR/COMPUTER INTERFACE

The computer interface unit is designed so that a free interchange of data and instructions can be carried on between the Radiation Series 540 PCM acquisition and stored program decommutation system and a digital computer. The unit converts the logic level of the decom to that required by the computer. The unit also decodes the various instructions from the computer and causes the decommutator to comply with them. In addition, the unit provides a path through which a complete program can be inserted into the decommutator memory or an existing program can be modified or checked. All interchange between the computer and the computer interface unit is performed by parallel transfer.

The decommutator sends two types of words to the computer through the computer interface unit. Both types of words are sent upon request of the computer. The two types are truncated data words (characters) with a maximum of 12 bits per character and a status word. The truncated characters are routed from the decommutator LSB truncated character register through the computer interface unit which converts the logic levels to be compatible with that required by the computer. The status word is partially generated within the decommutator and tells the computer the status of the decommutator at the time of receiving the request from the computer.

All data transferred into the computer memory from the decommutator and all data transferred from the computer into the decommutator memory must be under the direct and complete control of the computer program. The decommutator can be synchronized on the incoming data train and, in effect, to the entire decommutation process. However, no data is transferred through the interface unit until requested by the computer. Initiation of this transfer is effected by control words and control functions generated by the computer.

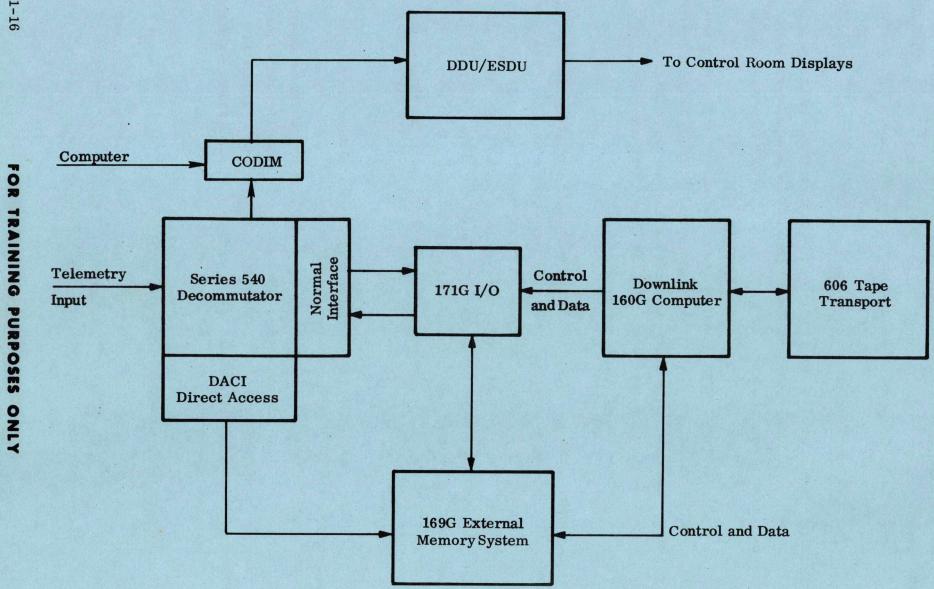

# 1.8 DIRECT ACCESS COMPUTER INTERFACE (DACI)

The DACI is essentially in parallel with the decommutator normal interface circuitry (Figure 1-7) and enables the ACE-S/C decommutator to input addressed data directly into the 169G external memory unit. The decommutator output circuitry (normal or

Figure 1-7. Interconnection Diagram

DACI) will be selected by the preacquisition block of the decom program. The DACI is then enabled by the 160G downlink computer. The decommutator control and routing words define which PCM words are to be transferred to the 169G. The information transfer from DACI to the 169G will be as follows:

a. 17 address bits: 4 Memory bank select

13 Memory address

b. 13 data bits: 8 Data

2 Blank

3 Flags

The decommutator also has the capability to perform parameter limit checks, floating point checks, and event transition checks (Figure 1-8). The limit checks are performed on the upper and lower parameter values for each PCM word determined by the loaded decommutator program. The values for the upper and lower limits are predetermined and are preprogrammed into the decommutator memory prior to testing. Thus, the values provide unique checking for each telemetry word input into the PCM decommutator system.

The floating point check is performed on those parameters where the change is of significance rather than the exact upper or lower values. In this capability the last known value of a parameter is used as the next point of reference, thus the floating point technique. The event transition checking is performed in the same manner as the floating point technique in that the last event word input from the telemetry system is used as the next reference.

A flag is sent to the computer as part of the data word to tell the computer any time the limit check or floating point check was out of tolerance.

## 1.9 PHYSICAL DESCRIPTION

The stored program decommutator is housed in four equipment cabinets, each 84 inches high, 21 inches wide, and 30 inches deep (Figures 1-9 and 1-10). In addition to the Radiation-built equipment, the stored program decommutator includes a number of modified vendor equipments and off-the-shelf vendor items.

The individual cabinets are assigned assembly reference designations 1A, 2A, 3A, and 4A, from left to right. Cabinets 1A and 2A house various-sized rigid-mounted assemblies and sliding drawer assemblies, on which are mounted the operating controls of the

Figure 1-8. DACI/Decommutator Interface

Figure 1-9. Series 540 PCM Acquisition and Stored Program Decommutator

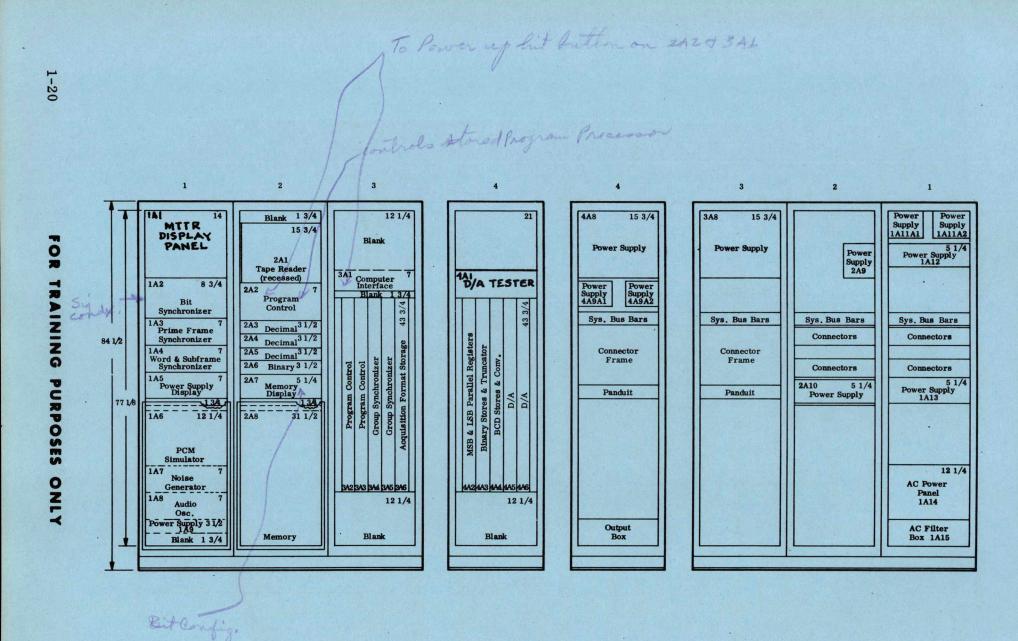

Figure 1-10. Stored Program Decommutator Equipment Location

system. Cabinet 2A also contains a core memory. Cabinet 3A contains five module panel assemblies, each capable of housing 1000 modules. Cabinet 4A also contains five module panel assemblies, each capable of housing 1000 modules. The module panel assemblies are cable-connected to terminal boards at the rear of each cabinet. They are mounted on slides for easy access to the modules, test points, and wiring.

Within the cabinets the major components (rigid-mounted assemblies, sliding drawer, and module panel assemblies) are assigned reference designations composed of the cabinet designation plus an arabic number. For example, 3A2 is a module panel assembly in cabinet number 3 drawer 2 and the modules are assigned a letter of the alphabet A through Z. These blocks are further divided into ten rows (assigned arabic number 1 through 10 and five columns, assigned A through E).

The stored program decommutator uses repairable printed circuit cards and low-cost, transfer-molded, throwaway modules. The printed circuit cards are Radiation standard printed circuit cards. The modules are assembled into 4-inch by 6 3/4-inch contact blocks, 50 modules per block. Four of these blocks are mounted into 7 1/2 by 17-inch castings, and these castings are assembled into drawers or panels. Further explanation is given under the section pertaining to Radiation logic.

## 1.10 LEADING PARTICULARS

The leading characteristics of the stored program decommutator are listed in Table 1-1.

## 1.11 CAPABILITIES AND LIMITATIONS

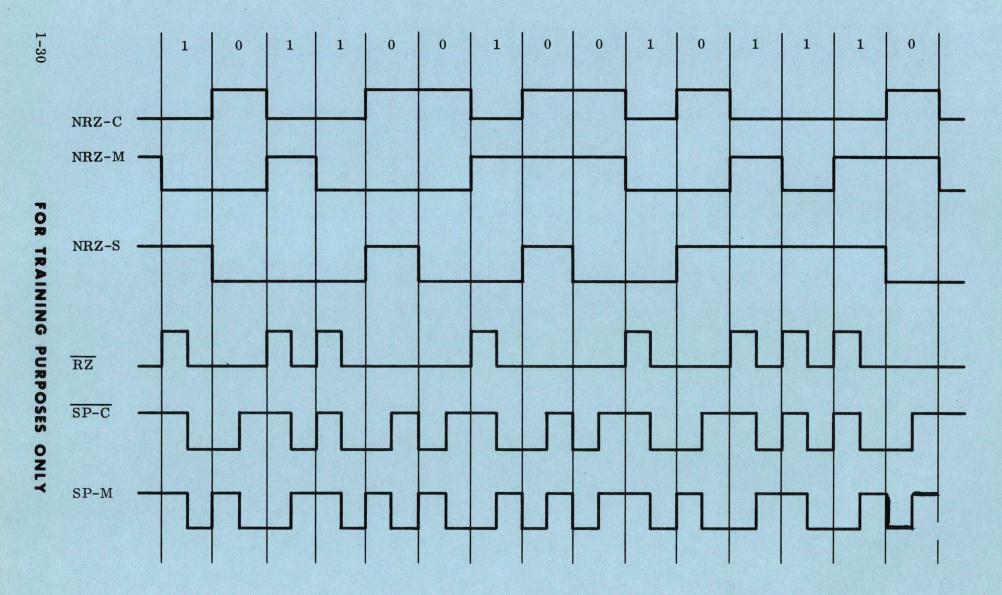

The pertinent data for determining the capabilities and limitations of the stored program decommutator are listed in Table 1-2. Types of PCM modulation are shown in Figure 1-11.

Table 1-1 Leading Particulars

| Dimensions                                              |                                                                                                           |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| (Each cabinet)                                          | 84 inches high<br>21 inches wide<br>30 inches deep                                                        |

| Weight                                                  |                                                                                                           |

| (Total of four cabinets with full complement)           | 3200 pounds (approximately)                                                                               |

| Primary Power                                           |                                                                                                           |

| Voltage<br>Frequency<br>Phase<br>Current<br>Total Power | 110 volts ± 10 percent 60 ± 3 cps Single-phase, 2-wire 40 amps, maximum 5 kw, maximum                     |

| Temperature                                             |                                                                                                           |

| Operating Non-operating Room Ambient                    | 60° to 125°F<br>-30° to 125°F<br>30° to 110°F                                                             |

| Heat Dissipation                                        |                                                                                                           |

| Cabinet 1A<br>Cabinet 2A<br>Cabinet 3A<br>Cabinet 4A    | 1200 watts (approximately) 1500 watts (approximately) 500 watts (approximately) 800 watts (approximately) |

| Cabinet Cooling Conditions                              |                                                                                                           |

| Inlet                                                   | 60°F, +3.0°, and -0.0°<br>Dry bulb temperature                                                            |

|                                                         | 58°F maximum dew point (approximately 90 percent relative humidity)                                       |

| Outlet                                                  | 15°F expected temperature rise through cabinets.                                                          |

# Table 1-2 Condensed Data

| Input                  |                                                                                                                                                                                                                     |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Frequency          | 1 to 1,000,000 bits per second, NRZ; 0.5 to 500,000 bits per second; SP and RZ.                                                                                                                                     |

| Amplitude Range        | 0.5 to 30 volts peak-to-peak.                                                                                                                                                                                       |

| DC Offset              | 60 percent of input amplitude.                                                                                                                                                                                      |

| Dynamic Range          | 15 to 1 without adjustment.                                                                                                                                                                                         |

| Input Impedance        | Greater than 10,000 ohms, shunted by not more than 30 $\mu\mu$ f. May be reduced by external shunt to 120 ohms.                                                                                                     |

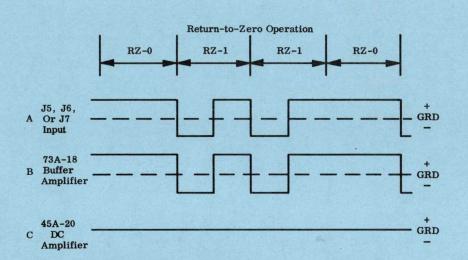

| Codes (See Figure 1-3) |                                                                                                                                                                                                                     |

| RZ                     | In RZ modulation a logic "one" is represented<br>by a pulse half of a bit-period wide; a logic<br>"zero" is represented by lack of pulse during<br>a bit period.                                                    |

| NRZC                   | In NRZC modulation a logic "one" is represented by one level and a "zero" is represented by another level.                                                                                                          |

| NRZM                   | In NRZM modulation a logic "one" is represented by a change in level; a logic "zero" is represented by no change in level.                                                                                          |

| NRZS                   | In NRZS modulation a logic "one" is represented by no change in level; a logic "zero" is represented by a change in level.                                                                                          |

| SP                     | In split-phase modulation a logic "one" bit is represented by a "one-zero" code element combination. A logic "zero" bit is represented by a "zero-one" code element combination.                                    |

| SPM                    | In split phase-M modulation a logic "one" bit is represented by a change from a "one-zero" code element to a "zero-one" code element or vice-versa. A logic "zero" bit is represented by no change in code element. |

| Arrangement Word-Bit   | MSB first or LSB first.                                                                                                                                                                                             |

| Polarity               | Reversible.                                                                                                                                                                                                         |

| Connection             | Three single-ended inputs and one balanced input.                                                                                                                                                                   |

| Bit Synchronization    |                                                                                                                                                                                                                     |

| Bit Error Rate         | Within 1 db of theoretical. Maintains synchronization with a 3 percent bit jitter frequency or jitter of ± 25 percent of a bit period at frequencies up to the bit rate with a signal-to-noise ratio of 15 db.      |

Table 1-2

Condensed Data (Cont.)

| Bit Synchronization (Cont.)             |                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tracking Range                          | Follows variations in the bit rate of ±20 percent, with 50 percent transitions at a signal-to-noise ratio of 15 db.                                                                                                                                                                |

| Sensitivity                             | Bit slippage threshold of 8 db or better. (Bit slippage threshold is defined as the signal-to-noise ratio in an FM receiver IF, normalized to a bandwidth equal to the bit rate, at which the bit synchronizer slips one or more bits in one of 10,000 bit frames on the average.) |

| Synchronization Mainte-<br>nance of Bit | The system maintains bit synchronization within ±25 percent of a bit period with a signal-to-noise ratio of -4 db and a noise bandwidth equal to the bit rate.                                                                                                                     |

| Acquisition Range                       | The system will lock onto the incoming bit rate at ±10 percent of the predetermined bit rate with 50 percent transitions at a signal-to-noise ratio of 15 db or greater with the noise bandwidth equal to the bit rate.                                                            |

| Clock Outputs                           | Two-phase clock corresponding to 0 and 180 phase displacement.                                                                                                                                                                                                                     |

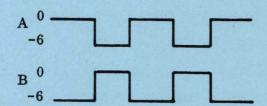

| Data Output                             | Regenerated serial NRZ; "Zero" level is 0 volt; and "One" level is -10 volts.                                                                                                                                                                                                      |

| Monitors                                | Meter provided for input amplitude level, sync status (quality), and fine tuning.                                                                                                                                                                                                  |

| Input Switching                         | Front panel selector switch for four input sources.                                                                                                                                                                                                                                |

| Automatic Mode                          | Stored program or manual selection of up to eight predetermined bit rates and other associated parameters. Automatic switch-over takes place in approximately 2 milliseconds.                                                                                                      |

| Prime Frame Synchronization             |                                                                                                                                                                                                                                                                                    |

| Prime Channels                          | 512 words per prime frame or greater, depending on format stored in memory.                                                                                                                                                                                                        |

| Sync Word                               | 7 to 33 bits. Can be expanded to 64 bits by the addition of logic modules.                                                                                                                                                                                                         |

| Modes of Operation                      | Search, check, and lock.                                                                                                                                                                                                                                                           |

| Aperture                                | Width is programmable for 1 to 3 bits.                                                                                                                                                                                                                                             |

# Table 1-2 Condensed Data (Cont.)

| <b>新聞的表現的社會是否的特別的表現的地區的基礎的意思的</b>   |                                                                                                                                                                                         |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prime Frame Synchronization (Cont.) |                                                                                                                                                                                         |

| Search Mode                         | Sync word error bits are programmable for 0 to 15. (Only 8 displayed.)                                                                                                                  |

| Check Mode                          | Sync word error bits are the same as in the lock mode. "Quality Test - Words Sampled" is programmable for 1 to 4. "Quality Test - Allowable Words" in error is programmable for 0 to 2. |

| Lock Mode                           | Sync word bits in error are programmable for 0 to 15.                                                                                                                                   |

| Status Indicators                   | Search, check, and lock.                                                                                                                                                                |

| Programming                         | All of the above quality parameters are controlled by programming or may be controlled manually from the front panel controls.                                                          |

| Subframe Recycle Synchronization    |                                                                                                                                                                                         |

| Number                              | One subframe recycle synchronizer is provided; expansion to three can be made by addition of logic modules.                                                                             |

| Subchannels                         | 512 or more, depending on program stored in memory.                                                                                                                                     |

| Sync Word                           | 7 to 33 bits. Can be expanded to 64 bits by the addition of logic modules.                                                                                                              |

| Modes of Operation                  | Search and lock.                                                                                                                                                                        |

| Search Mode                         | Sync word bits in error are programmable for 0 to 8.                                                                                                                                    |

| Lock Mode                           | Sync word bits in error is 0 to 15.                                                                                                                                                     |

| Status Indicators                   | Search and lock.                                                                                                                                                                        |

| Programming                         | Each of the quality parameters listed above can be controlled by the memory program or manually for each synchronizer.                                                                  |

| Major Cycle ID Synchronization      |                                                                                                                                                                                         |

| Number                              | One major cycle ID synchronizer is provided.                                                                                                                                            |

| ID Code Words                       | Maximum code length is 9 binary bits and is programmable. Can accept MSB or LSB arrangement.                                                                                            |

|                                     |                                                                                                                                                                                         |

Table 1-2

Condensed Data (Cont.)

| Major Cycle ID Synchroniza-<br>tion (Cont.) |                                                                                                                                                                                                  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Location                                    | An ID word may appear in any position in either a data word or a sync word.                                                                                                                      |

| Status Indication                           | ID error and ID verified. An ID ON indicator lights when an ID code is included in the format.                                                                                                   |

| Word Synchronization                        |                                                                                                                                                                                                  |

| Sync Word                                   | Up to three bits programmable.                                                                                                                                                                   |

| Modes of Operation                          | Search, check, and lock.                                                                                                                                                                         |

| Aperture                                    | Width is one bit wide and remains constant for all modes.                                                                                                                                        |

| Search Mode                                 | Sync word bits in error are programmable for 0 or 1.                                                                                                                                             |

| Check Mode                                  | Sync word bits in error remain the same as in the Search mode. "Quality Test - Words Sampled" is programmable from 0 to 4.                                                                       |

| Lock Mode                                   | Sync word bits in error is 0 or 1 bit.                                                                                                                                                           |

| Status Indicators                           | Search, check, lock, and an ON indicator.                                                                                                                                                        |

| Programming                                 | Each of the parameters listed above can be controlled by program or manually.                                                                                                                    |

| Supercommutation                            | Programming capability is provided to accommodate any number of supercommutated channels at any rate.                                                                                            |

| <u>Parity</u>                               | The start of an ODD or EVEN parity count sequence is programmed or manual. A decimal display indicates up to 999 parity errors in 1 to 99 frames. Manual or remote reset capability is provided. |

| Stored Program Decommutation                |                                                                                                                                                                                                  |

| Word Length                                 | Any length up to 64 bits.                                                                                                                                                                        |

| Word Rate                                   | Prime or subcommutated word rates up to 200,000 per second can be accommodated by the basic system.                                                                                              |

| Prime Frame Length                          | 512 or more, depending on arrangement of memory.                                                                                                                                                 |

| TOP TRAINI                                  | NG BURBOSES ONLY                                                                                                                                                                                 |

Table 1-2

Condensed Data (Cont.)

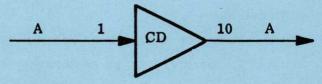

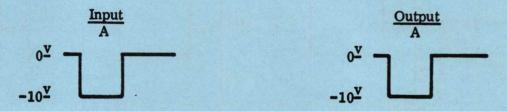

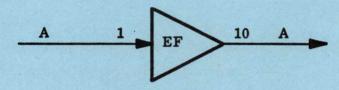

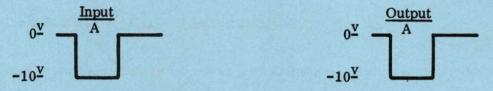

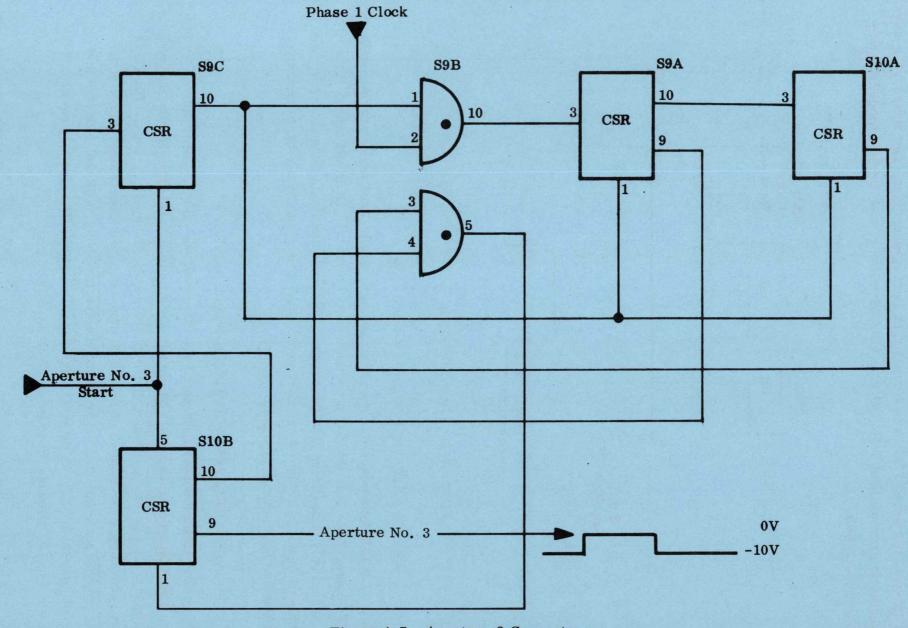

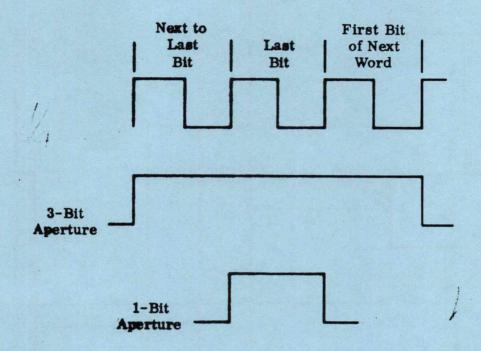

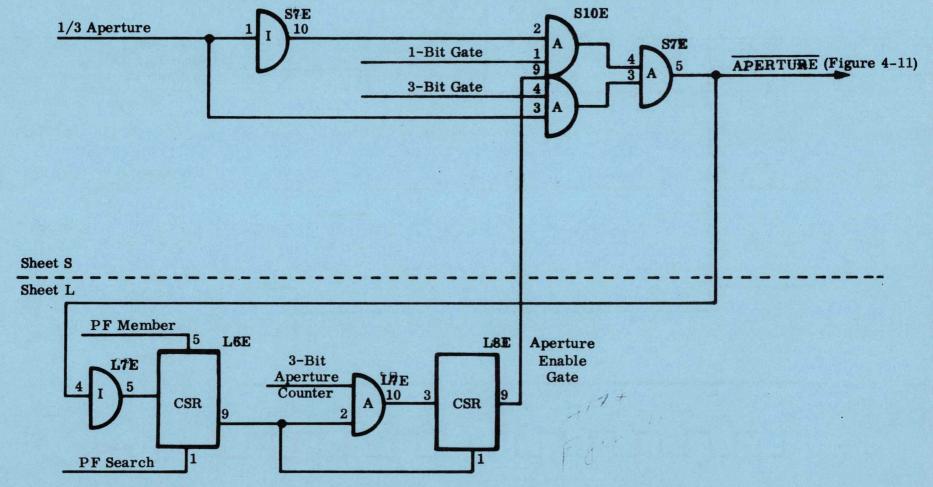

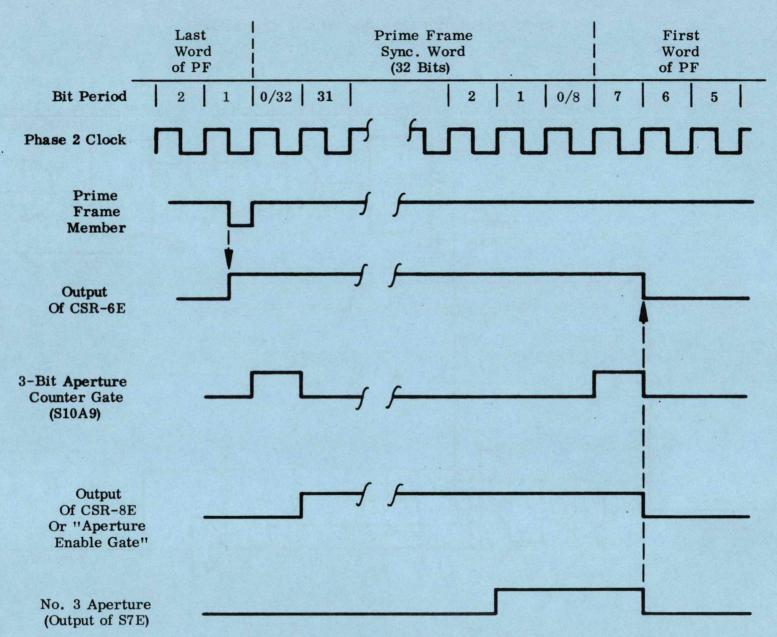

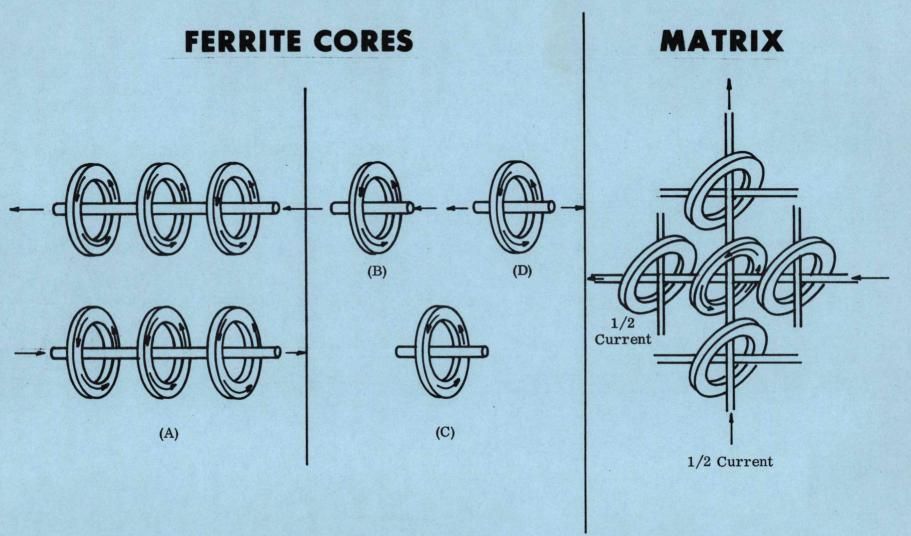

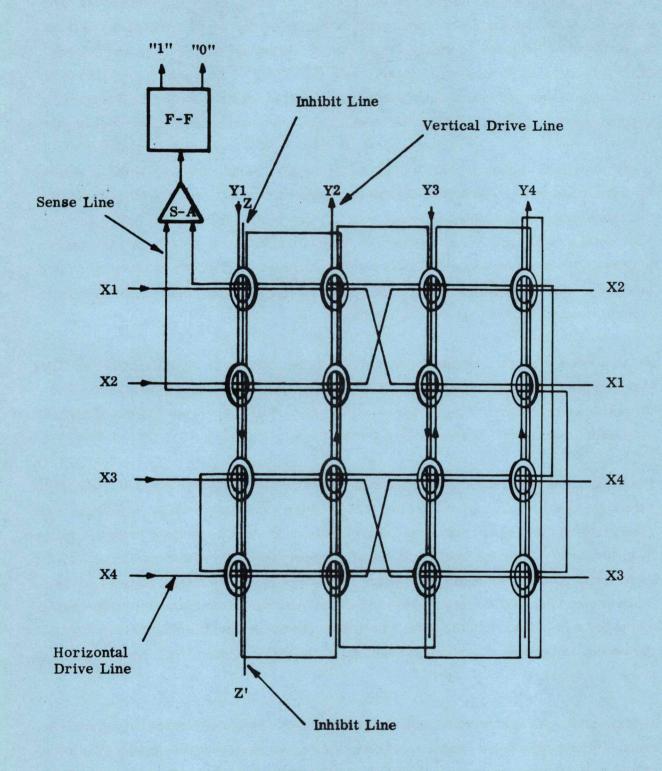

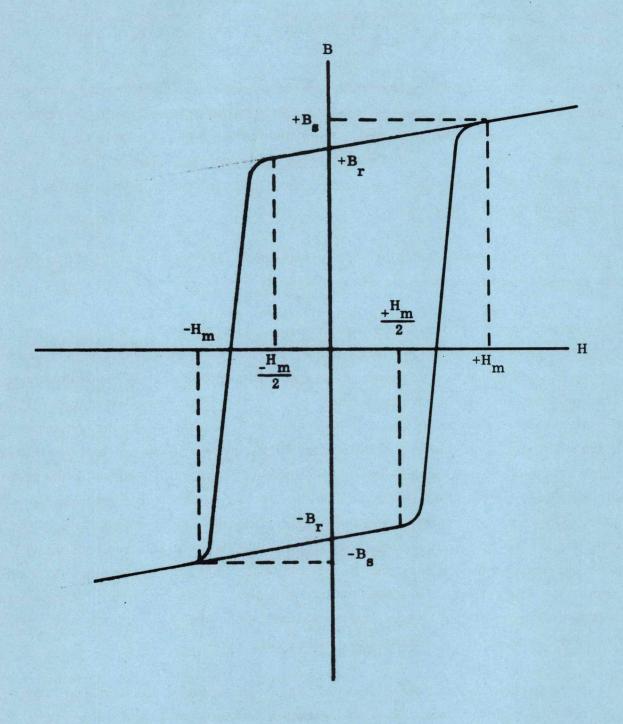

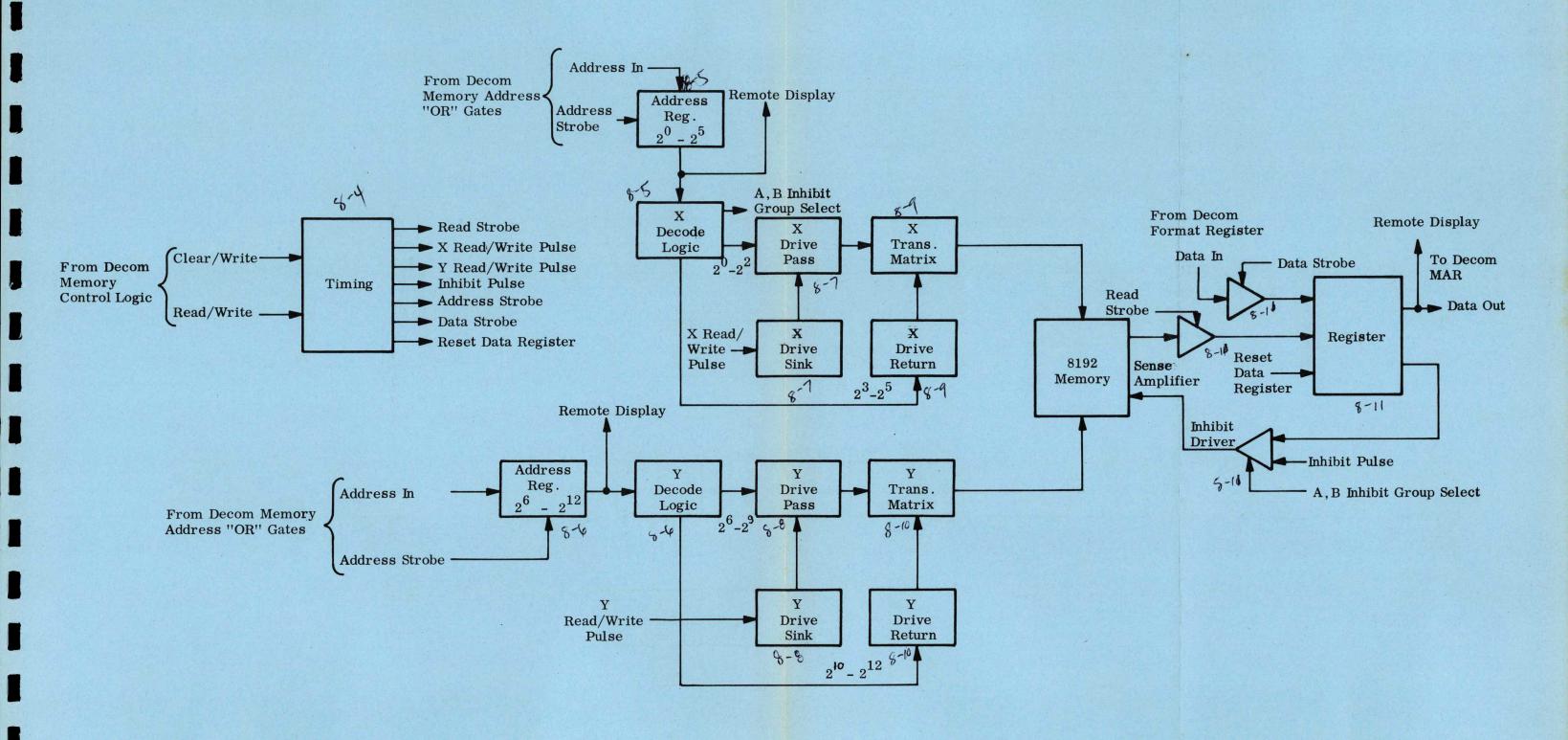

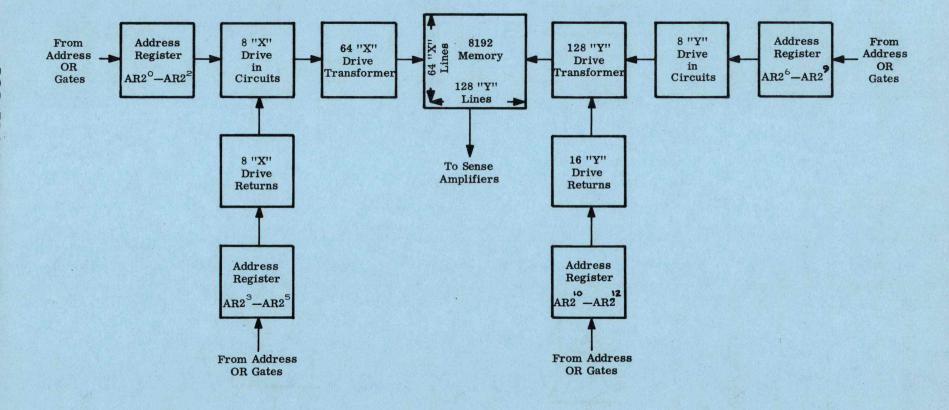

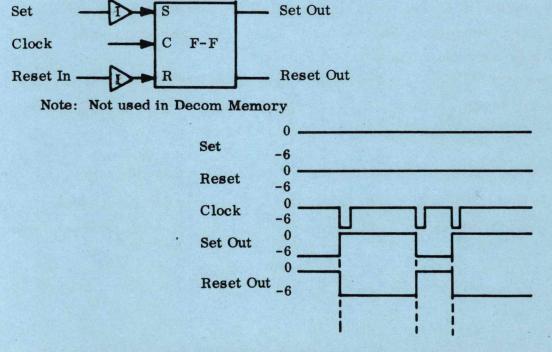

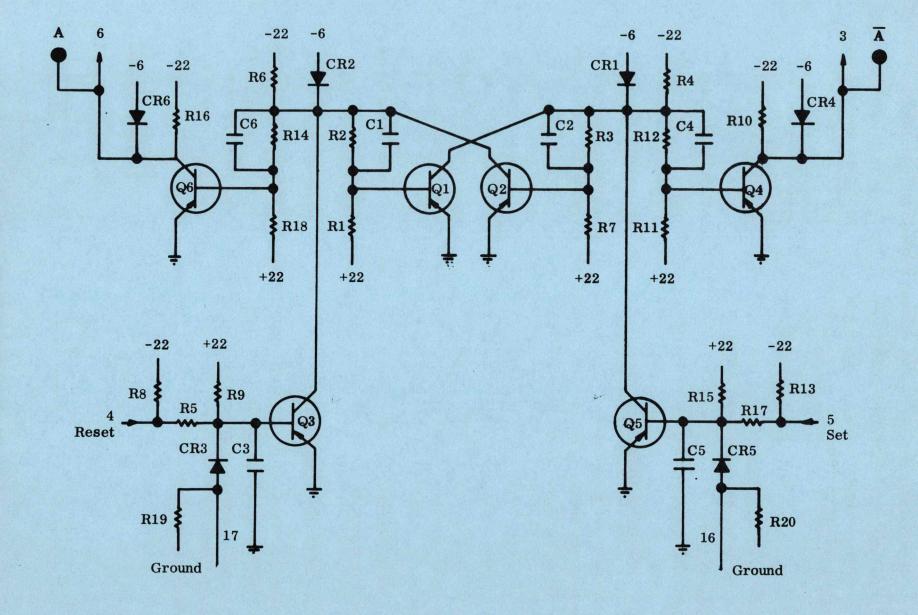

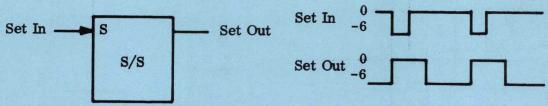

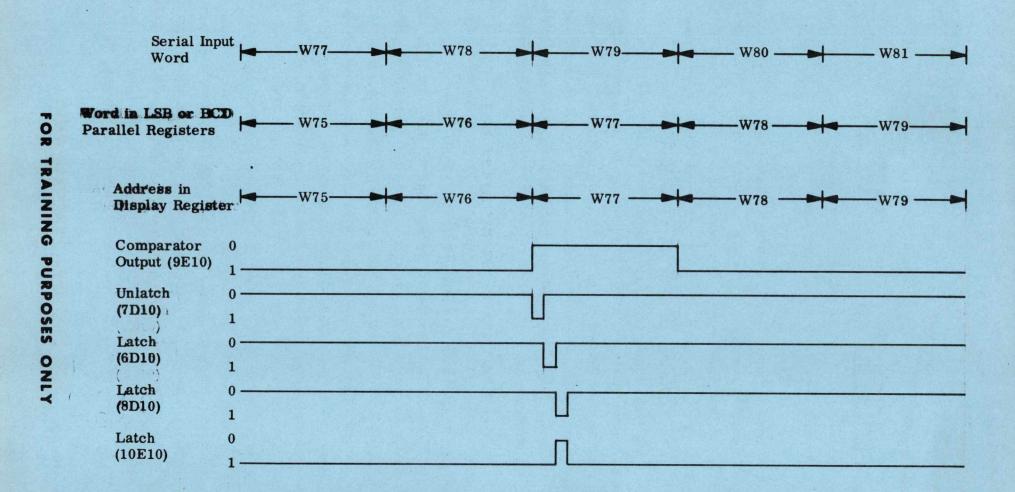

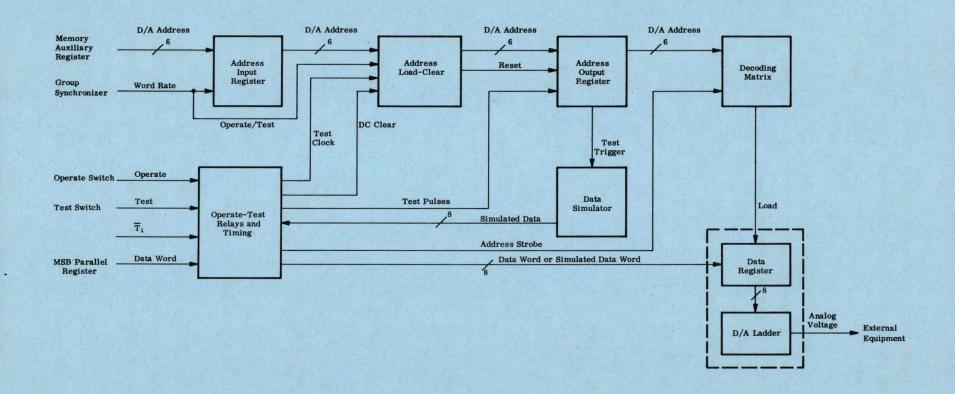

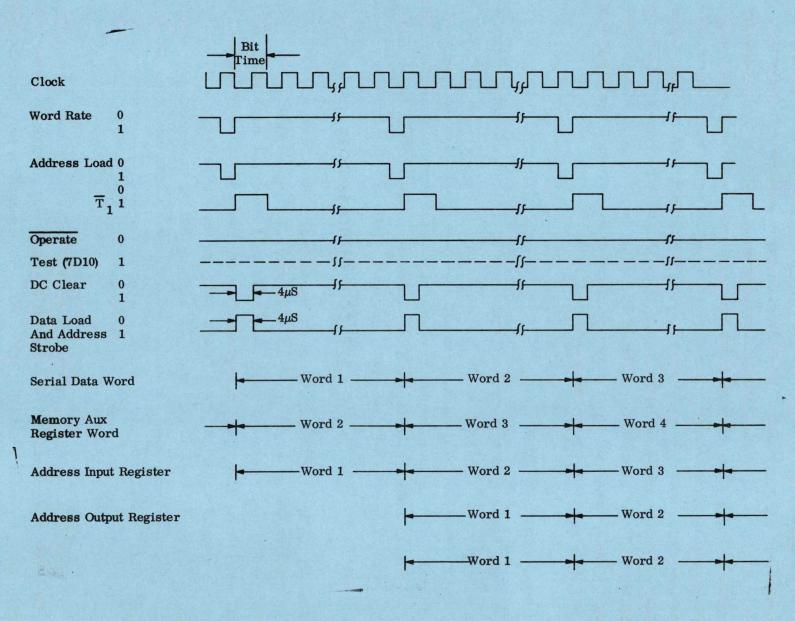

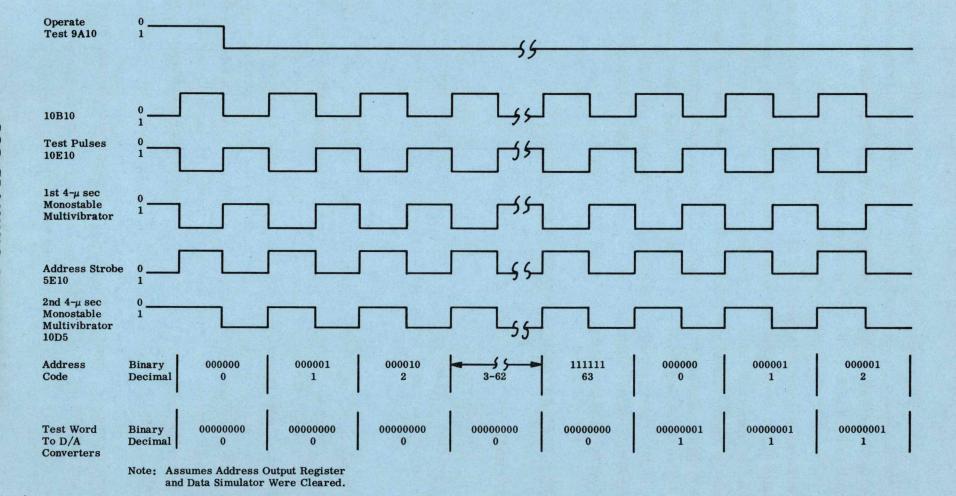

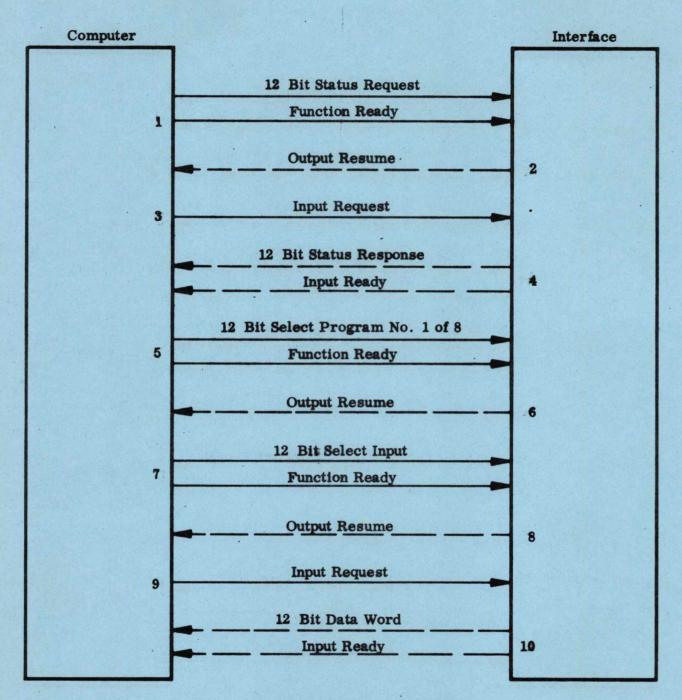

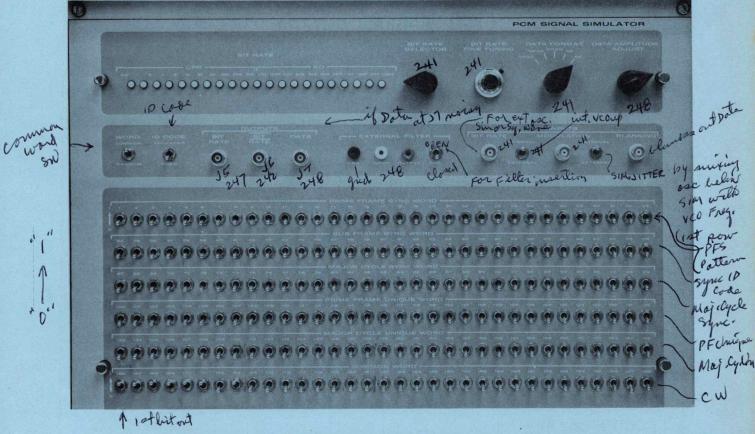

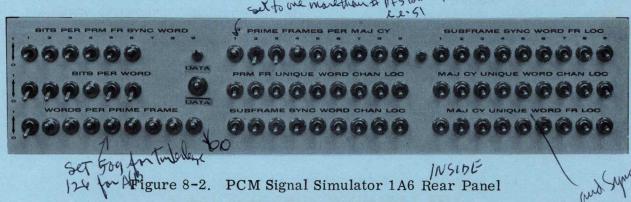

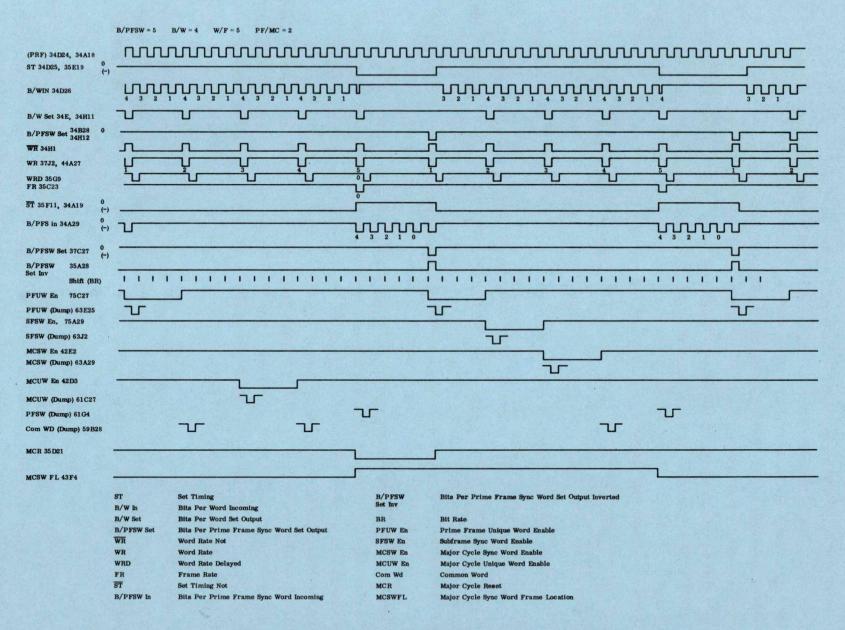

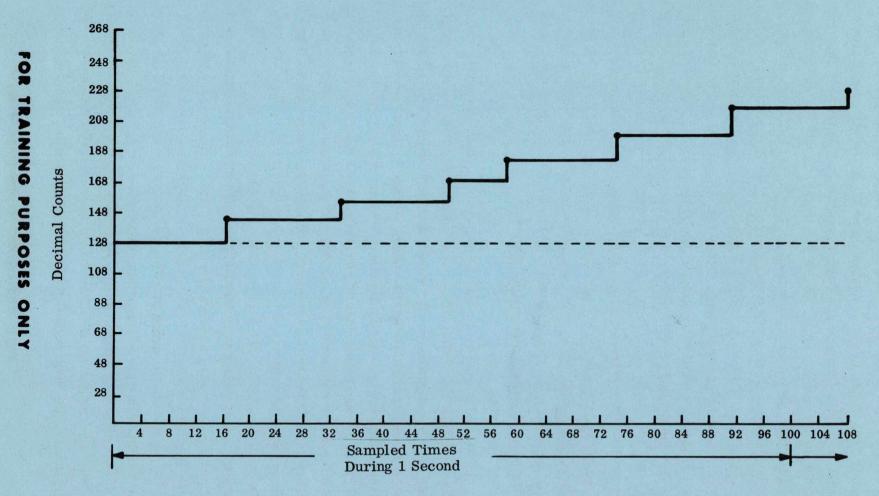

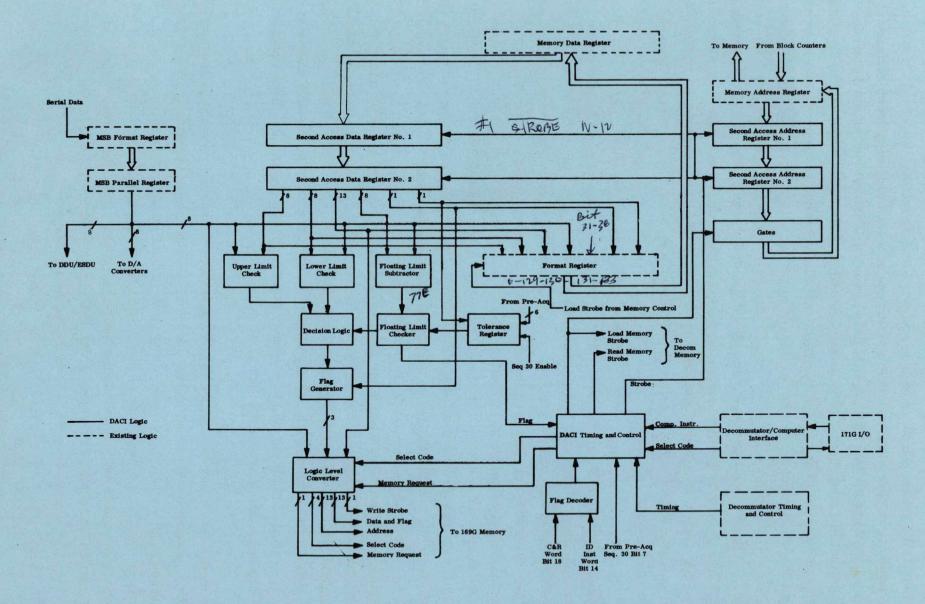

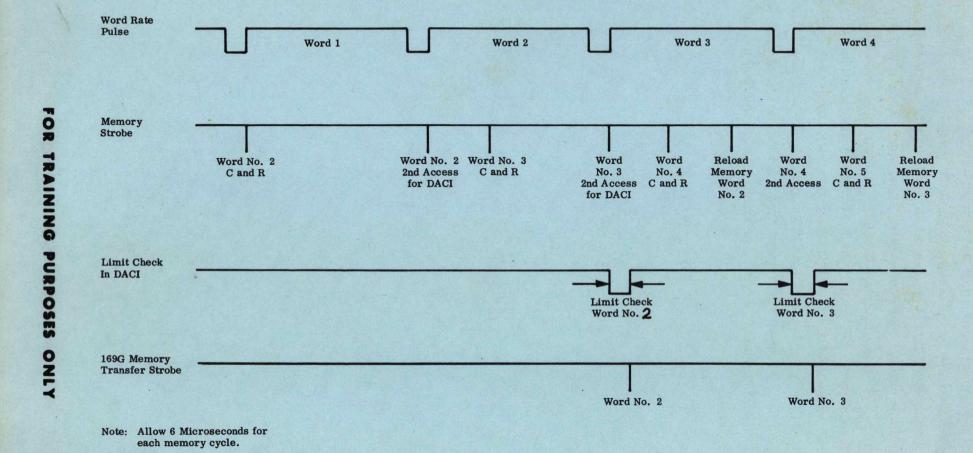

| HEARING WATER TO THE PARTY OF T |                                                                                                                                                                                          |