APOLLO SUPPORT DEPARTMENT

# ACE-5/C DESCRIPTION MANUAL

ACCEPTANCE CHECKOUT EQUIPMENT—SPACECRAFT

SYSTEM NO. 1 INSTALLED AT NORTH AMERICAN AVIATION—DOWNEY, CALIF.

JOHN A. WISHARD NASW-410-AM-13

# DESCRIPTION MANUAL for

# ACCEPTANCE CHECKOUT EQUIPMENT-SPACECRAFT

GROUND STATION No. 1

INSTALLED AT NORTH AMERICAN AVIATION

DOWNEY, CALIFORNIA

1 JUNE 1964

This document was prepared for the National Aeronautics and Space Administration/Apollo Spacecraft Program Office under Contract NASw-410 Task Order MSC/POD-1. Preparation of this Type II document is required by paragraph 10.3 of Exhibit D to the existing contractual requirements.

APOLLO SUPPORT DEPARTMENT GENERAL ELECTRIC COMPANY DAYTONA BEACH, FLORIDA JOHN A. WISHAKE

Insert Latest Changed Pages. Destroy Superseded Pages.

# LIST OF EFFECTIVE PAGES

TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS  $\underline{417}$  CONSISTING OF THE FOLLOWING:

| Page<br>No.    | Issue    |

|----------------|----------|

| Title          | Original |

| A              | Original |

| i thru xii     | Original |

| 1-0 thru 1-0   | Original |

| 1-1 thru 1-32  | Original |

| 2-1 thru 2-92  | Original |

| 3-1 thru 3-190 | Original |

| 4-1 thru 4-88  | Original |

\*The asterisk indicates pages changed, added, or deleted by the current change

NASA

Manuals will be distributed as directed by the NASA-Apollo Program Office. All requests for manuals should be directed to the NASA Apollo Spacecraft Program Office at Houston, Texas.

## TABLE OF CONTENTS

| Paragraph      |                                                               | Page              |

|----------------|---------------------------------------------------------------|-------------------|

|                |                                                               |                   |

|                | INTRODUCTION                                                  |                   |

|                | GEOTION I GENERAL DESCRIPTION                                 |                   |

|                | SECTION I. GENERAL DESCRIPTION                                |                   |

| PART 1         | FUNCTIONAL DESCRIPTION                                        | 1-1               |

| 1-1            | Acceptance Checkout Equipment - Spacecraft System Description | 1-1               |

| 1-5            | Command Equipment                                             | 1-1               |

| 1-12           | Data Recording and Display Equipment                          | 1-5               |

| 1-18           | Support Systems                                               | 1-6               |

| 1-22           | Command Equipment Description                                 | 1-6               |

| 1-24           | R START Module                                                | 1-6               |

| 1-26           | C START Module                                                | 1-9               |

| 1-28           | K START Module                                                | 1-9               |

| 1-30           | Communications Unit Executor                                  | 1-9               |

| 1-33           | Command Computer                                              | 1-10              |

| 1-37           | Data Transmission and Verification Converter                  | 1-10              |

| 1-42           | Receiver-Decoder                                              | 1-11              |

| 1-51           | Recording and Display Equipment Description                   | 1-12              |

| 1-53           | Spacecraft and Spacecraft Vicinity Equipment                  | 1-12              |

| 1-60           | Data Acquisition and Decommutation Equipment (DADE)           | 1-13              |

| 1-64           | Alphanumeric Display System                                   | 1-14              |

| $1-74 \\ 1-83$ | Analog and Event Display System                               | 1-15              |

| 1-03           | Quick Reference Table of Major Unit Functions                 | 1-17              |

| PART 2         | PHYSICAL DESCRIPTION                                          | 1-22              |

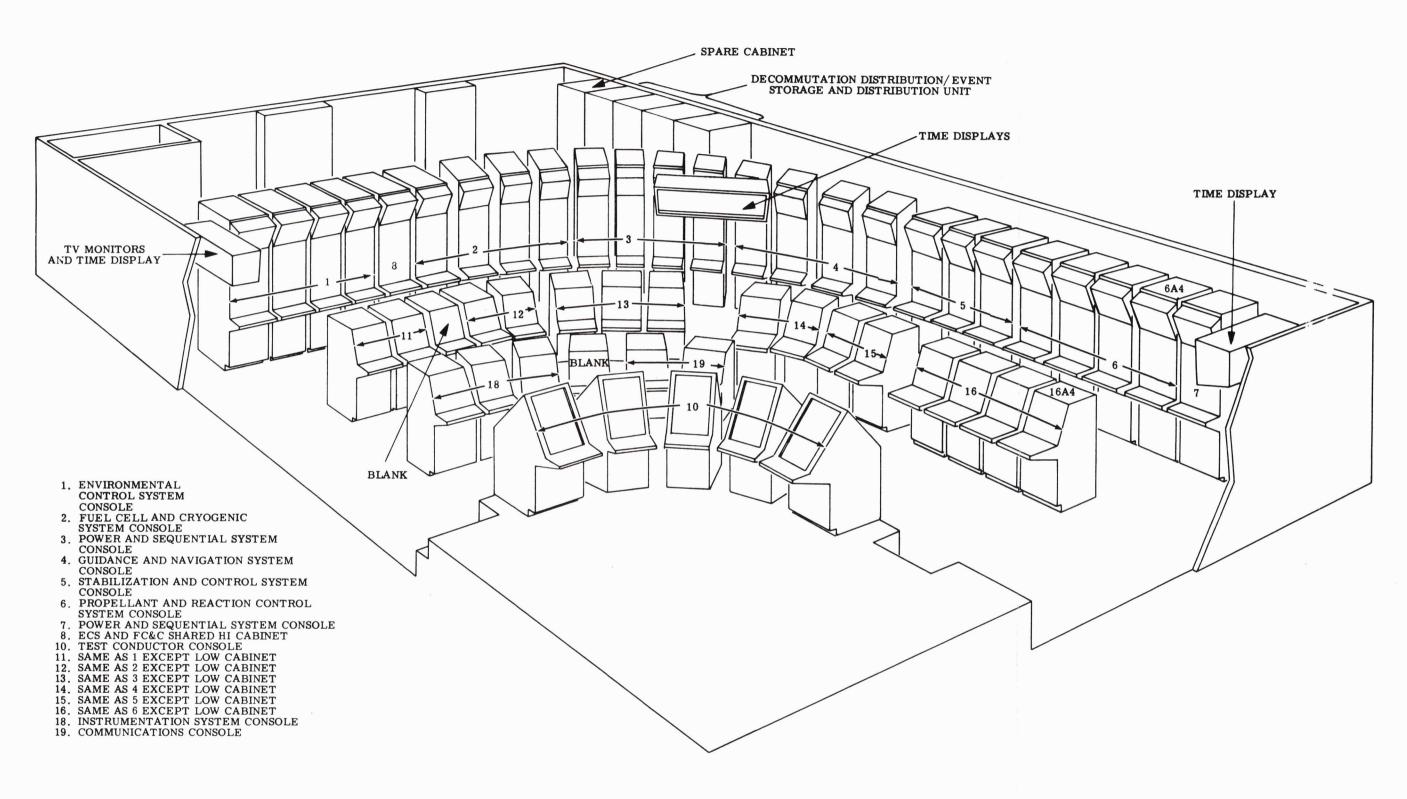

| 1-85           | ACE-S/C Station Physical Configuration at Downey, California  | 1-22              |

| 1-90           | Control Room Equipment                                        | 1-22              |

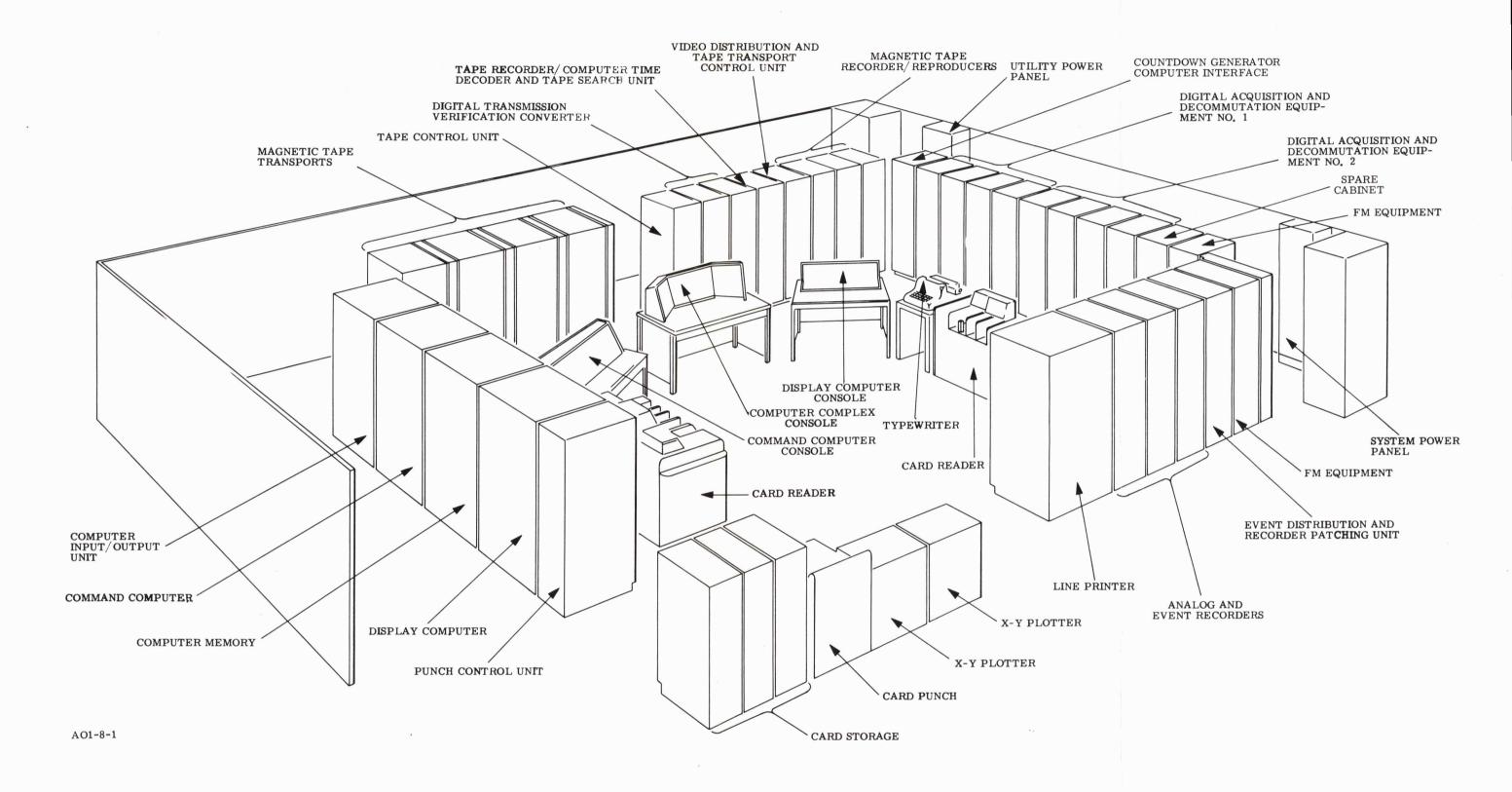

| 1-93           | Computer Room Equipment                                       | 1-23              |

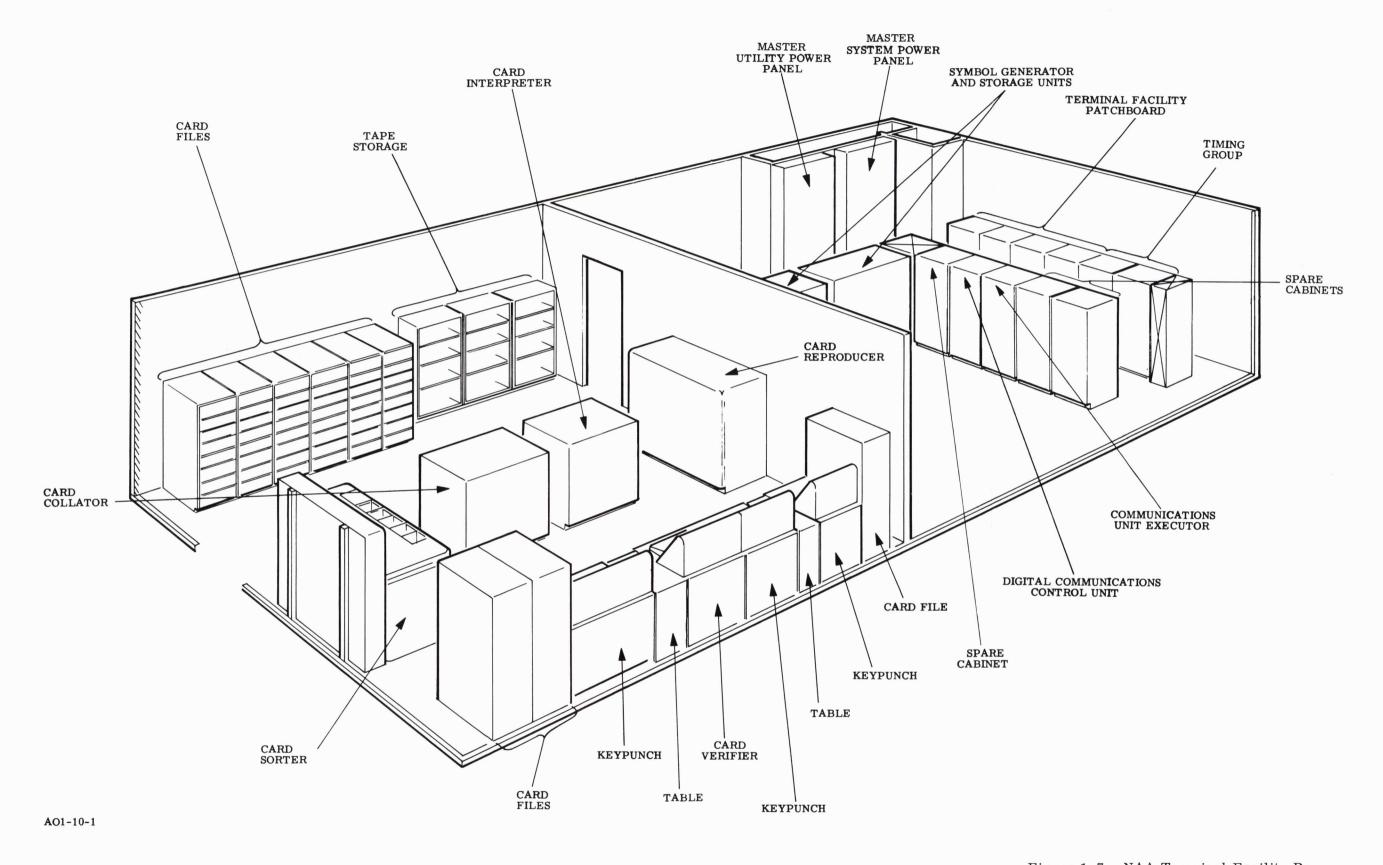

| 1-99           | Terminal Facility Room Equipment                              | 1-23              |

|                | SECTION II. COMMAND EQUIPMENT                                 |                   |

|                | SECTION II. COMMIND EQUI MENT                                 |                   |

| 2-1            | Data Entry Equipment                                          | 2-1               |

| 2-3            | Interrupt Mode                                                | 2-1               |

| 2-12           | Manual Mode                                                   | 2-5               |

| 2-14           | Maintenance Mode                                              | $\frac{2-5}{2-5}$ |

| 2-16           | R START Functions                                             | $\frac{2-5}{2-5}$ |

| 2-18           | R START Operation                                             | $\frac{2-5}{2-5}$ |

| 2-20           | C START Functions                                             | 2-6               |

| 2-22           | C START Operation                                             | 2-6               |

|                |                                                               |                   |

| Paragraph    |                                                        |   |     |   |   | Page              |

|--------------|--------------------------------------------------------|---|-----|---|---|-------------------|

| 2-24         | K START Functions                                      |   |     |   |   | 2-7               |

| 2-26         | Tape Mode                                              |   |     |   |   | 2-7               |

| 2-29         | Manual Mode                                            | • | • • | • | • | $\frac{2-7}{2-7}$ |

| 2-31         | Keyboard                                               | • | • • | • | • | 2-8               |

| 2-33         | K START Operation                                      | • | • • | • | • | 2-8               |

| 2-35         | J-Box Functions                                        |   |     |   |   | 2-15              |

| 2-37         | CUE Functions                                          |   |     |   |   | 2-15              |

| 2-39         | Standby Mode                                           |   |     |   |   | 2-15              |

| 2-41         | Interrupt Mode                                         |   |     |   |   | 2-15              |

| 2-54         | Maintenance Mode                                       |   |     |   |   | 2-15              |

| 2-54         | Manual Mode                                            |   |     |   |   | 2-21              |

| 2-62         |                                                        |   |     |   |   | 2-21              |

| 2-62<br>2-64 | CUE Description                                        |   |     |   |   |                   |

| 2-64<br>2-66 | Standby Mode                                           |   |     |   |   | 2-22              |

| 2-79         | Interrupt Mode                                         |   |     |   |   | 2-22              |

|              | Maintenance Mode                                       |   |     |   |   | 2-25              |

| 2-81         | Manual Mode                                            |   |     |   |   | 2-25              |

| 2-83         | Data Processing Equipment                              |   |     |   |   | 2-26              |

| 2-86         | Nonpriority Operation                                  |   |     |   |   | 2-26              |

| 2-90         | Priority Operation                                     |   |     |   |   | 2-27              |

| 2-120        | Computer Complex Functions                             |   |     |   |   | 2-37              |

| 2-124        | Computer Complex Description                           |   |     |   |   | 2-37              |

| 2-125        | Compute Module                                         | • | • • | • | • | 2-37              |

| 2-149        | Memory Module                                          |   |     |   |   | 2-45              |

| 2-160        | Input/Output Module                                    |   |     |   |   | 2-47              |

| 2-183        | Line Printer                                           |   |     |   |   | 2-55              |

| 2-193        | Card Reader                                            | • |     | • | • | 2-58              |

| 2-206        | Magnetic Tape Transport Units                          |   |     |   |   | 2-64              |

| 2-236        | Tape Control Unit.                                     |   |     |   |   | 2-71              |

| 2-248        | Card Punch Controller and Card Punch                   |   |     |   |   | 2-74              |

| 2-256        | X-Y Plotter                                            |   |     |   |   | 2-77              |

| 2-262        | Typewriter                                             |   |     |   |   | 2-79              |

| 2-267        | Data Transmission Equipment                            |   |     |   |   | 2-80              |

| 2-269        | Transmission                                           |   |     |   |   | 2-83              |

| 2-271        | Reception                                              |   |     |   | • | 2-83              |

| 2-273        | Status Response                                        |   |     |   | • | 2-83              |

| 2-276        | Function Words                                         |   |     |   | • | 2-83              |

| 2-278        | Receiver Interrupt                                     |   |     |   | • | 2-84              |

| 2-280        | Interrupt on Error                                     |   |     |   |   | 2-84              |

| 2-282        | Interrupt on Fake Ready                                |   |     |   |   | 2-84              |

| 2-284        | Data Transmission and Verification Converter Functions |   |     |   |   | 2-84              |

| 2-286        | Transmit Mode                                          |   |     |   |   | 2-84              |

| 2-288        | Receive Mode                                           |   |     |   |   | 2-85              |

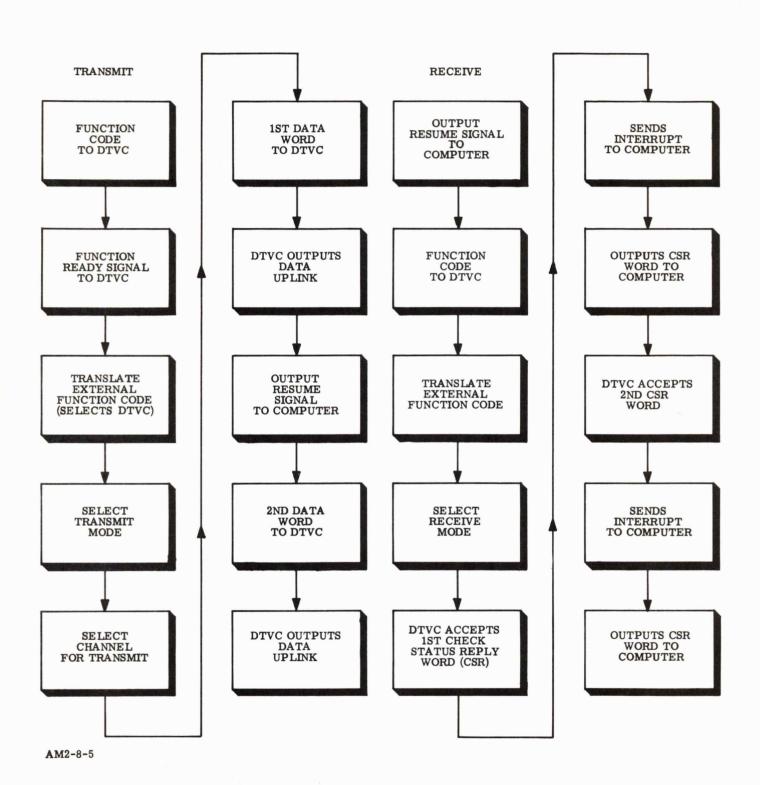

| 2-290        | Transmit Cycle                                         |   |     |   | • | 2-85              |

| 2-296        | Receive Cycle                                          |   |     |   | • | 2-89              |

| 2-302        | Program Control                                        |   |     |   |   | 2-90              |

| Paragraph                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                    | SECTION III. DISPLAY AND RECORDING EQUIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                        |

| 3-1                                                                                                                                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-1                                                                                                                                                                                                    |

| PART 1 3-3 3-10 3-15 3-18 3-20 3-21 3-24 3-27 3-28 3-41 3-63 3-64 3-78 3-79 3-80 3-85 3-92 3-93 3-95 3-102 3-103 3-104 3-108 3-115 3-116 3-120 3-150 3-151 3-153 3-166 3-175 3-176 | DATA ACQUISITION AND DECOMMUTATION EQUIPMENT. Data Acquisition and Decommutation Equipment Functions Interleaved PCM Test Data Description Airborne PCM Test Data Description Frequency Modulated Test Data Description Video Distribution and Tape Transport Control Unit Video Distribution and Tape Transport Control Functions Video Distribution and Tape Transport Control Functions Video Distribution and Tape Transport Control Unit Description Magnetic Tape Recorder Functions Magnetic Tape Recorder Punctions Magnetic Tape Recorder Description Tape Search Control Unit Tape Search Control Functions Tape Search Control Description Signal Mixer Assembly Signal Mixer Functions Signal Mixer Description Reference Oscillator/Mixer Assembly Reference Oscillator/Mixer Functions Reference Oscillator Description Mixer Amplifier Description Signal Separator Assembly Signal Separator Description FM Discriminator Unit FM Discriminator Functions FM Discriminator Description FM Calibration Unit FM Calibration Unit FM Calibration Unit Functions FM Telemetry Indicator Description FM Telemetry Calibrator Description Frequency Counter Description Decommutator Unit. | 3-1<br>3-2<br>3-5<br>3-6<br>3-6<br>3-6<br>3-10<br>3-12<br>3-12<br>3-18<br>3-29<br>3-32<br>3-32<br>3-32<br>3-34<br>3-36<br>3-40<br>3-40<br>3-40<br>3-40<br>3-43<br>3-53<br>3-53<br>3-53<br>3-54<br>3-58 |

| 3-177<br>3-189                                                                                                                                                                     | Decommutator Unit Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 3-58<br>. 3-69                                                                                                                                                                                       |

| PART 2<br>3-253<br>3-256                                                                                                                                                           | ANALOG AND EVENT DISPLAY EQUIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 3-96<br>. 3-96                                                                                                                                                                                       |

| Paragraph |                                                         | Page    |

|-----------|---------------------------------------------------------|---------|

| 3-257     | Decommutator Distribution Unit Functions                |         |

| 3-263     | Decom Distribution Unit Description                     |         |

| 3-269     | Event Storage and Distribution Unit                     | 3-102   |

| 3-270     | Event Storage and Distribution Unit Functions           | 3-102   |

| 3-282     | Event Storage and Distribution Unit Description         |         |

| 3-298     | Control Consoles                                        |         |

| 3-299     | Control Console Functions                               |         |

| 3-318     | Control Console Circuit Descriptions                    |         |

| 3-334     | Eight-Channel Analog Recorder Description               |         |

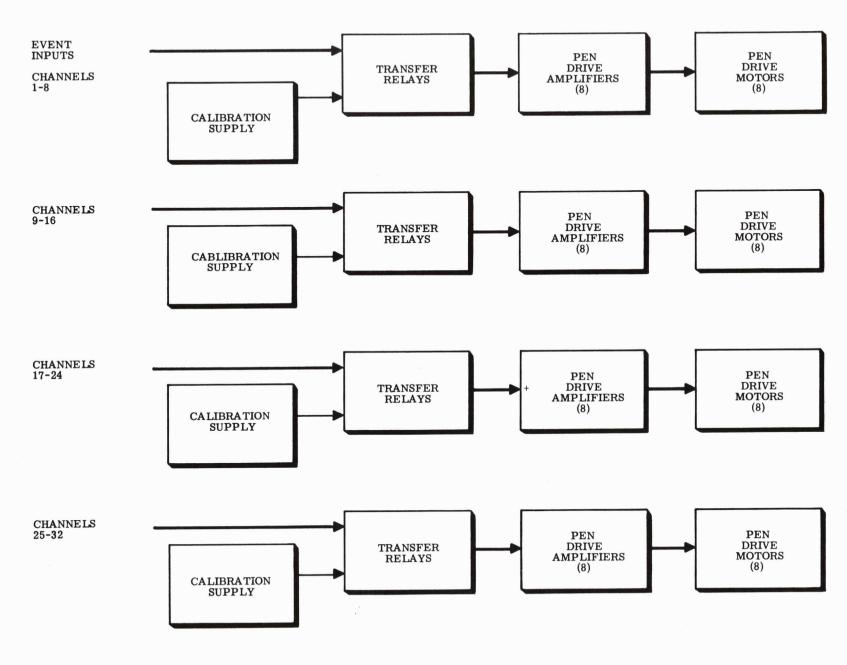

| 3-338     | 32-Channel Event Recorder Description                   | 3-137   |

| 3-342     | 100-Channel Event Recorder Description                  |         |

| 3-345     | Computer Room Test Data Display and Recording Equipment |         |

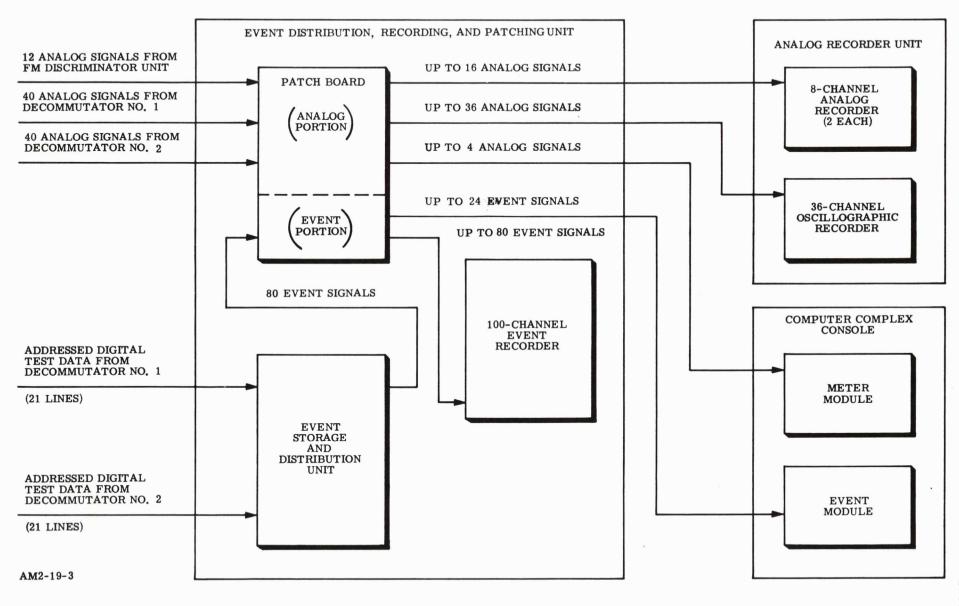

| 3-348     | Event Distribution Recording and Patching Unit          | 3-140   |

| 3-350     | Event Processing Logic Description                      | 3-142   |

| 3-352     | Patchboard Description                                  | 3-142   |

| 3-354     | 100-Channel Event Recorder Description                  | 3-142   |

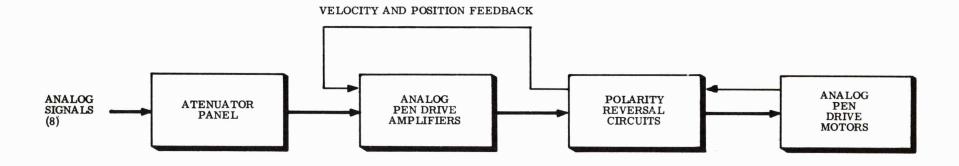

| 3-356     | Analog Recorder Unit                                    | 3-142   |

| 3-357     | 8-Channel Analog Recorder Description                   | 3 - 142 |

| 3-359     | 36-Channel Oscillographic Recorder Description          | 3-142   |

| 3-369     | Computer Room Meter and Event Modules                   | 3-145   |

| 3-370     | Meter Module Description                                | 3-145   |

| 3-372     | Event Module Description                                |         |

| PART 3    | ALPHANUMERIC DISPLAY EQUIPMENT                          | 3-146   |

| 3-374     | Alphanumeric Display Equipment Functions                | 3-146   |

| 3-378     | Data Processing Functions                               | 3-149   |

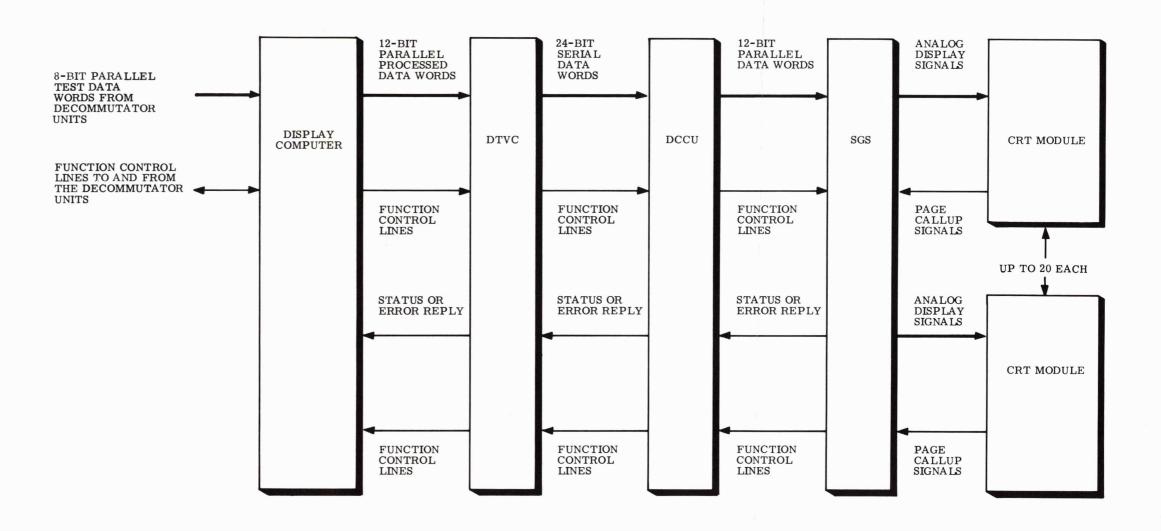

| 3-401     | Data Transmission Functions                             |         |

| 3-413     | Symbol Generation and Display Functions                 | 3-163   |

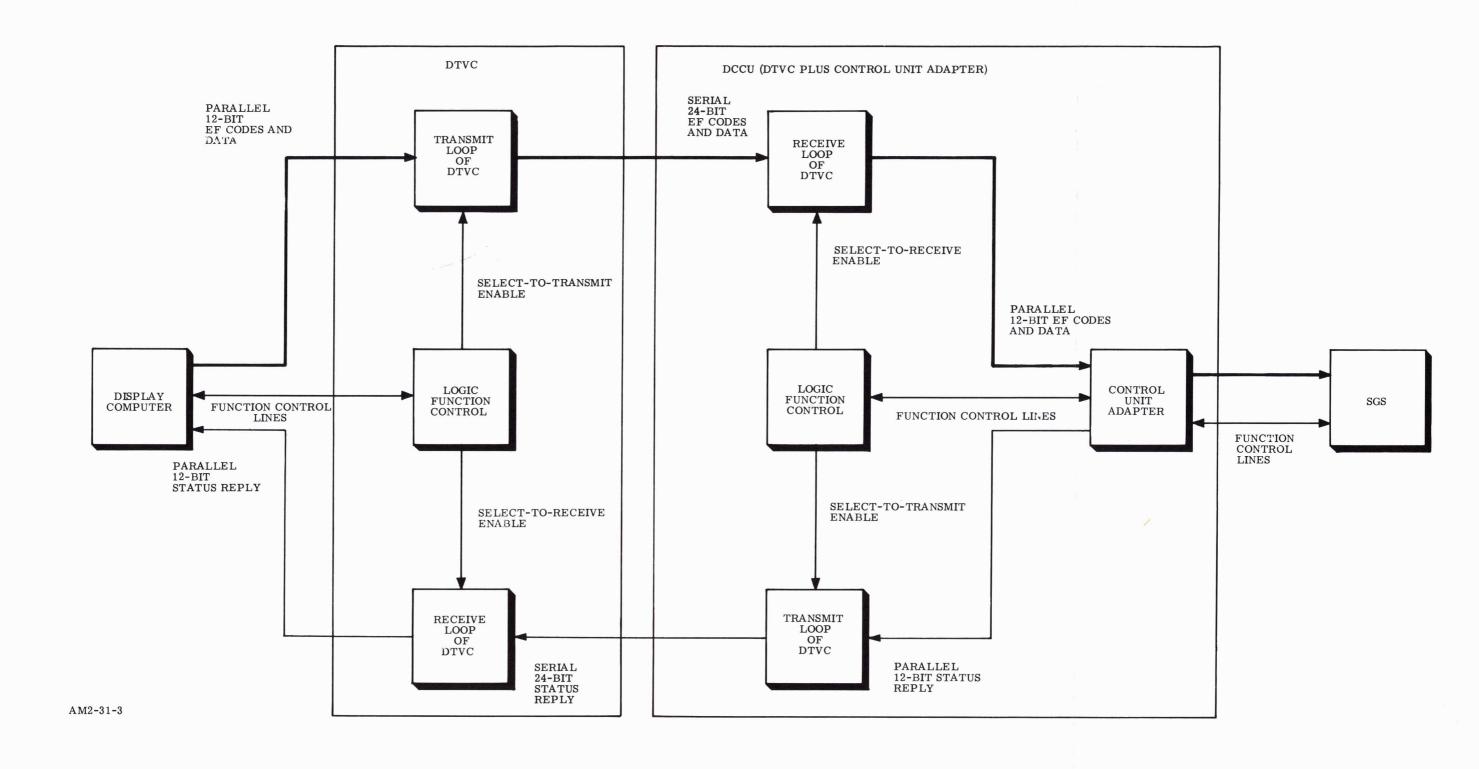

| 3-415     | DTVC and DCCU Equipment Description                     | 3-164   |

| 3-416     | DTVC Description                                        | 3-164   |

| 3-418     | DCCU Description                                        |         |

| 3-420     | Control Unit Adapter Description                        |         |

| 3-421     | SGS and CRT Equipment Description                       |         |

| 3-435     | Display Control                                         |         |

| 3-437     | Main Timing and Control                                 |         |

| 3-439     | Resynchronization Circuits                              | 3-169   |

| 3-447     | Memory Lockout                                          |         |

| 3-449     | Input Register                                          |         |

| 3-452     | Input Gates                                             | 3-170   |

| 3-454     | Input To Z Control                                      |         |

| 3-456     | Write-Over Period                                       | 3-173   |

| 3-459     | Memory Timing and Control                               |         |

| 3-462     | Control Circuits                                        |         |

| 3-464     |                                                         | 3-176   |

| Paragraph |                                                            | Page  |

|-----------|------------------------------------------------------------|-------|

| 3-467     | Address Selection                                          | 3-176 |

| 3-472     | Memory Circuits                                            |       |

| 3-474     | Beam Positioning                                           | 3-179 |

| 3-480     | Deflection                                                 |       |

| 3-484     | Character Generation                                       |       |

| 3-486     | Primary Translation                                        |       |

| 3-491     | Character Timing                                           | 3-184 |

| 3-493     | Translator Timing                                          |       |

| 3-495     | Secondary Translation                                      | 3-186 |

| 3-497     | Character Positioning                                      |       |

| 3-501     | Unblanking                                                 |       |

| 3-504     | CRT Module                                                 |       |

| 3-507     | Deflection Preamplifier                                    | 3-187 |

| 3-509     | Deflection Amplifier                                       | 3-187 |

| 3-511     | Focus and Astigmatism                                      |       |

| 3-515     | Cathode Ray Tube                                           |       |

| 3-517     | Deflection                                                 | 3-189 |

|           | SECTION IV. SUPPORT EQUIPMENT                              |       |

| 4-1       | Introduction                                               | 4-1   |

| 4-3       | Timing Equipment                                           | 4-1   |

| 4-8       | Time Signal Distribution                                   | 4-2   |

| 4-20      | Time Code Generator                                        | 4-17  |

| 4-23      | Time Code Generator Functions                              | 4-17  |

| 4-36      | Time Code Generator Description                            | 4-21  |

| 4-107     | Countdown Time Code Generator                              | 4-35  |

| 4-109     | Countdown Time Code Generator Functions                    | 4-35  |

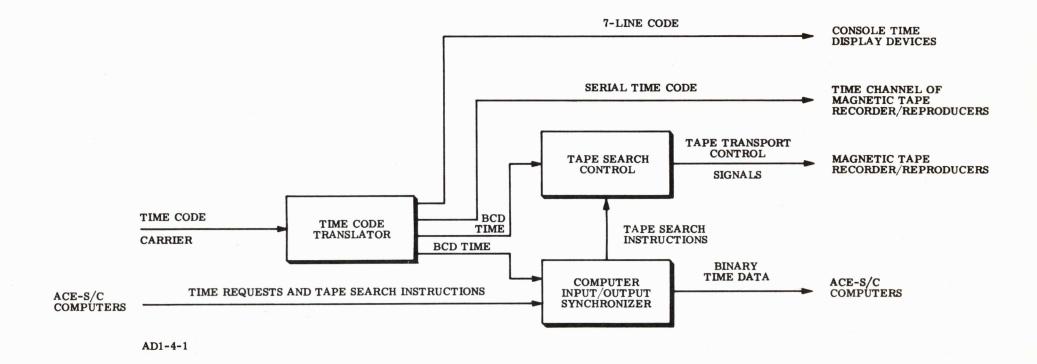

| 4-116     | Countdown Time Code Generator Description                  | 4-36  |

| 4-153     | Tape Search/Time Code Translator/Computer I/O Synchronizer | 4-49  |

| 4-155     | Tape Search/Time Code Translator/Computer I/O              |       |

|           | Synchronizer Functions                                     | 4-49  |

| 4-169     | Tape Search/Time Code Translator/Computer I/O              |       |

|           | Synchronizer Description                                   | 4-55  |

| 4-269     | Countdown Time Code Translator and Computer Input/Output   |       |

|           | Synchronizer                                               | 4-73  |

| 4-270     | Countdown Time Code Translator and Computer Input/Output   | 4 = 0 |

| 4 0 70    | Synchronizer Functions                                     | 4-73  |

| 4-272     | Countdown Time Code Translator and Computer Input/Output   | 4 === |

| 4 000     | Synchronizer Description                                   | 4-73  |

| 4-298     | Time Code Distribution Unit                                | 4-78  |

| 4-302     | Decommutator Distribution Unit                             | 4-79  |

| Paragraph |                                                              | Page |

|-----------|--------------------------------------------------------------|------|

| 4-304     | Remote Time Display Units                                    | 4-79 |

| 4-306     | Wall Clock Display Functions                                 |      |

| 4-310     | Countdown Generator Remote Control Unit Functions            | 4-82 |

| 4-312     | Remote Time Display Unit Description                         | 4-82 |

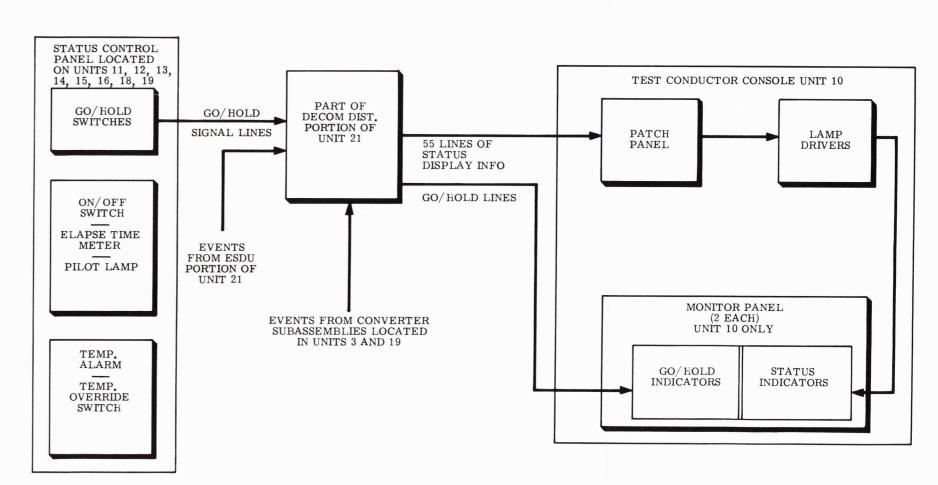

| 4-317     | Status Monitoring and Display Equipment                      | 4-83 |

| 4-319     | Control Console Status Control Panel Functions               | 4-87 |

| 4-324     | Decommutator Distribution Unit Status Distribution Functions | 4-87 |

| 4-327     | Test Conductor Console Status Subassembly Functions          | 4-88 |

## LIST OF ILLUSTRATIONS

| SECTION I. GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2       ACE-S/C Equipment Block Diagram       1-7         1-3       First Floor Plan of NAA Building 290       1-25         1-4       Second Floor Plan of NAA Building 290       1-26         1-5       NAA Control Room Perspective View       1-27         1-6       NAA Computer Room Perspective View       1-29         1-7       NAA Terminal Facility Room Perspective View       1-31         SECTION II. COMMAND EQUIPMENT         2-1       Command Equipment Block Diagram       2-3         2-2       R START Module Block Diagram       2-9         2-3       C START Module Block Diagram       2-11         2-4       K START Module Block Diagram       2-13         2-5       J-Box Block Diagram       2-16         2-6       Communications Unit Executor Block Diagram       2-17         2-6       Command Equipment Functional Block Diagram       2-29         2-8       Computer Complex Block Diagram       2-39 |

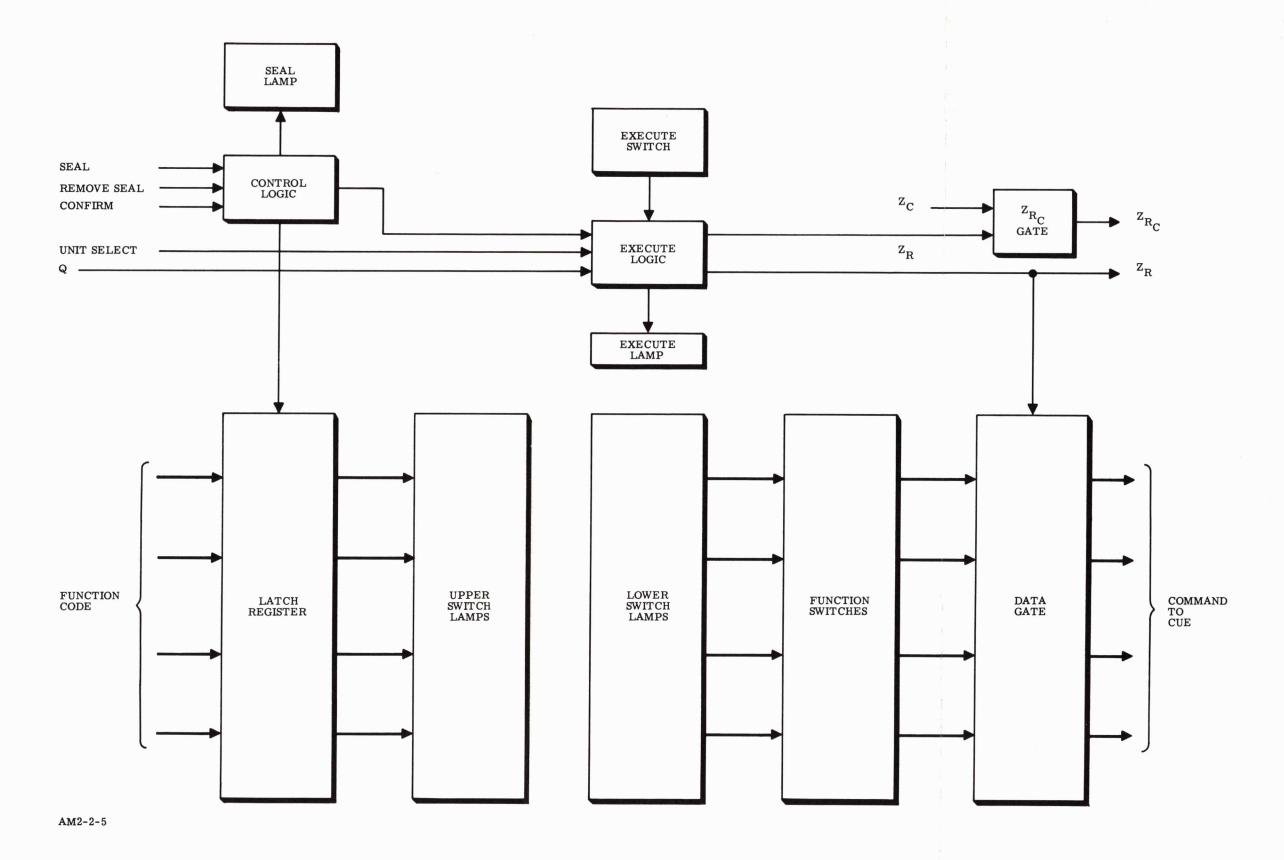

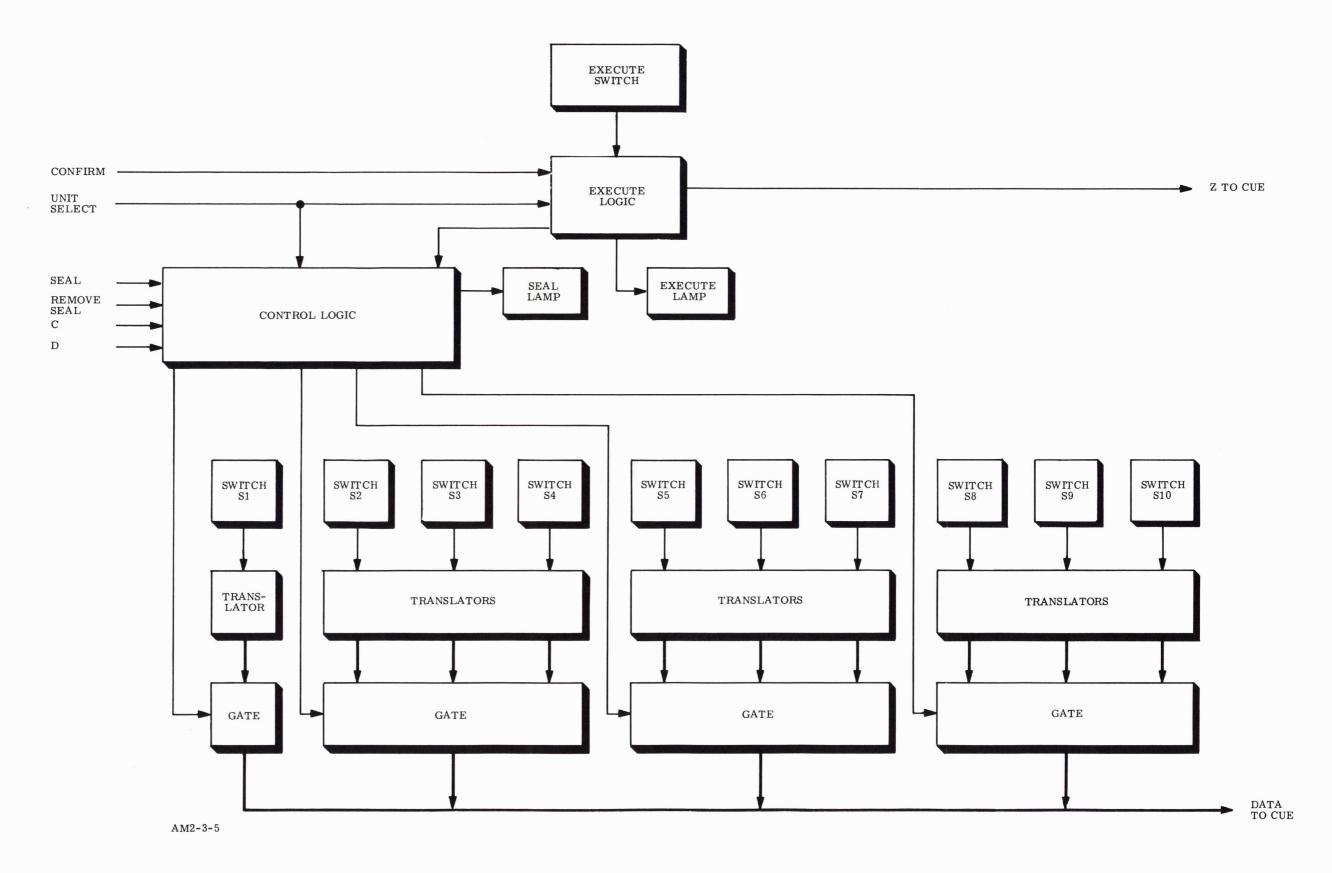

| 2-1 Command Equipment Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

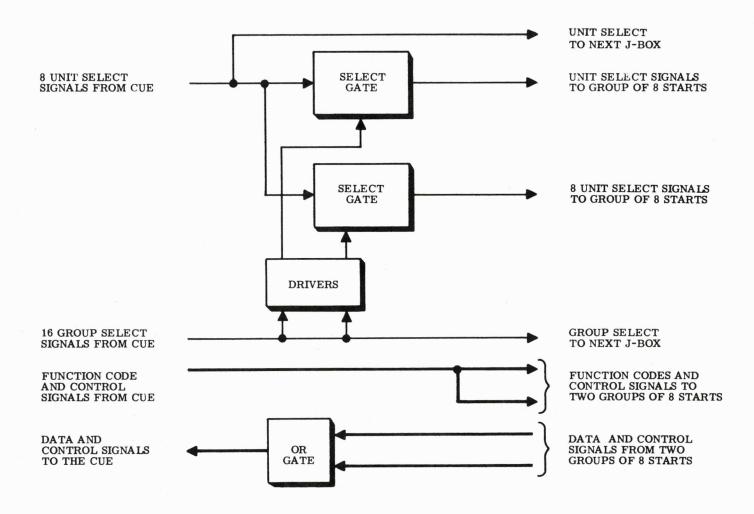

| 2-2 R START Module Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

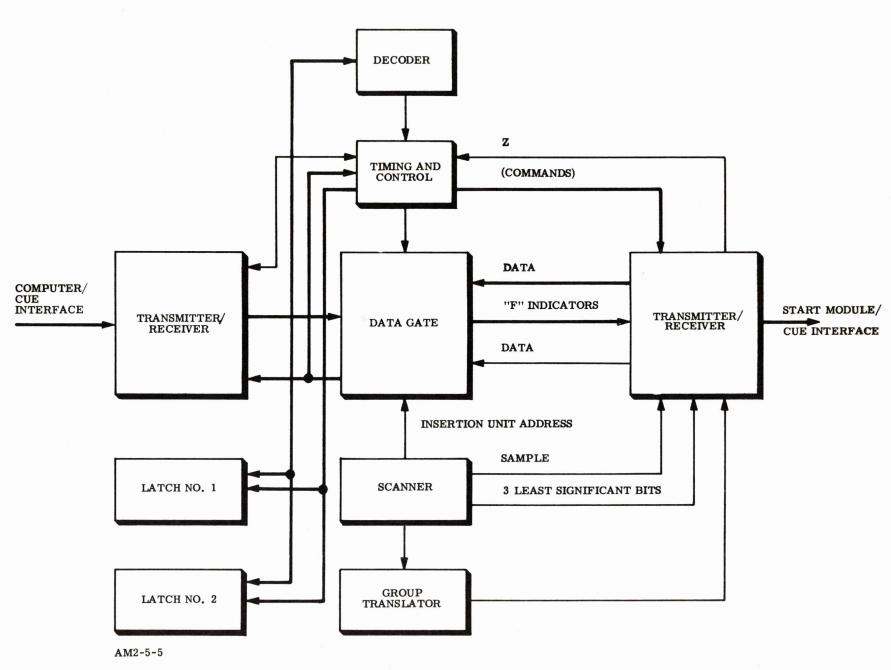

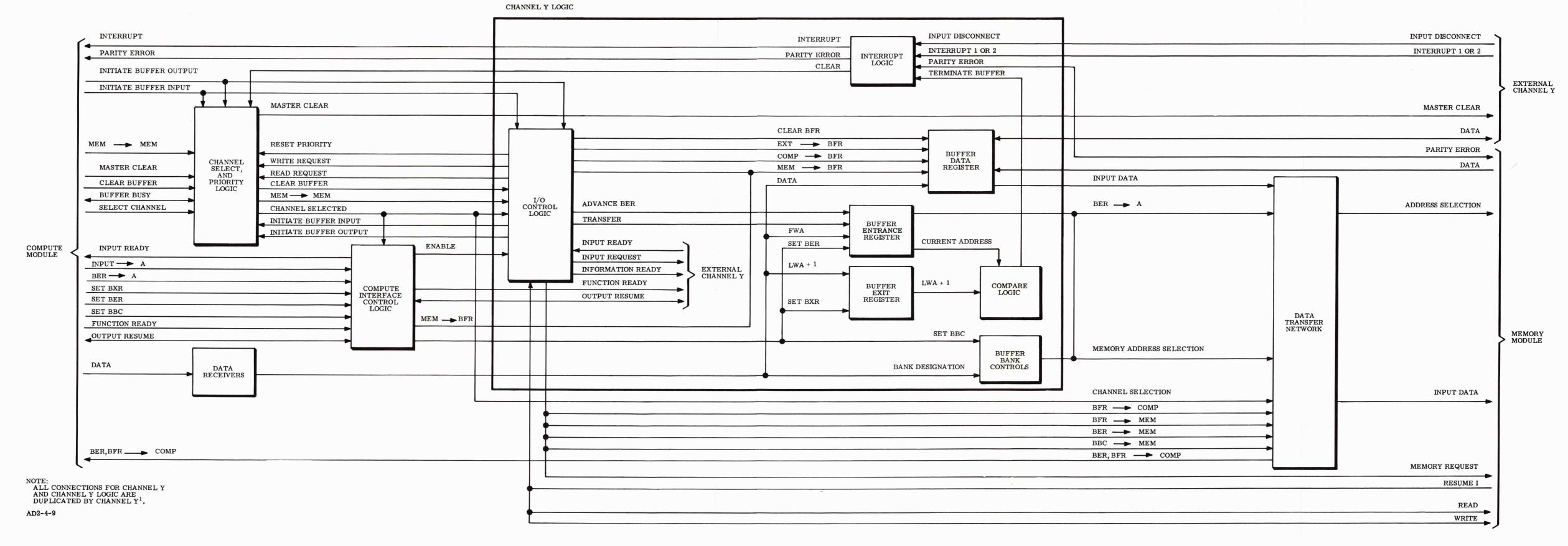

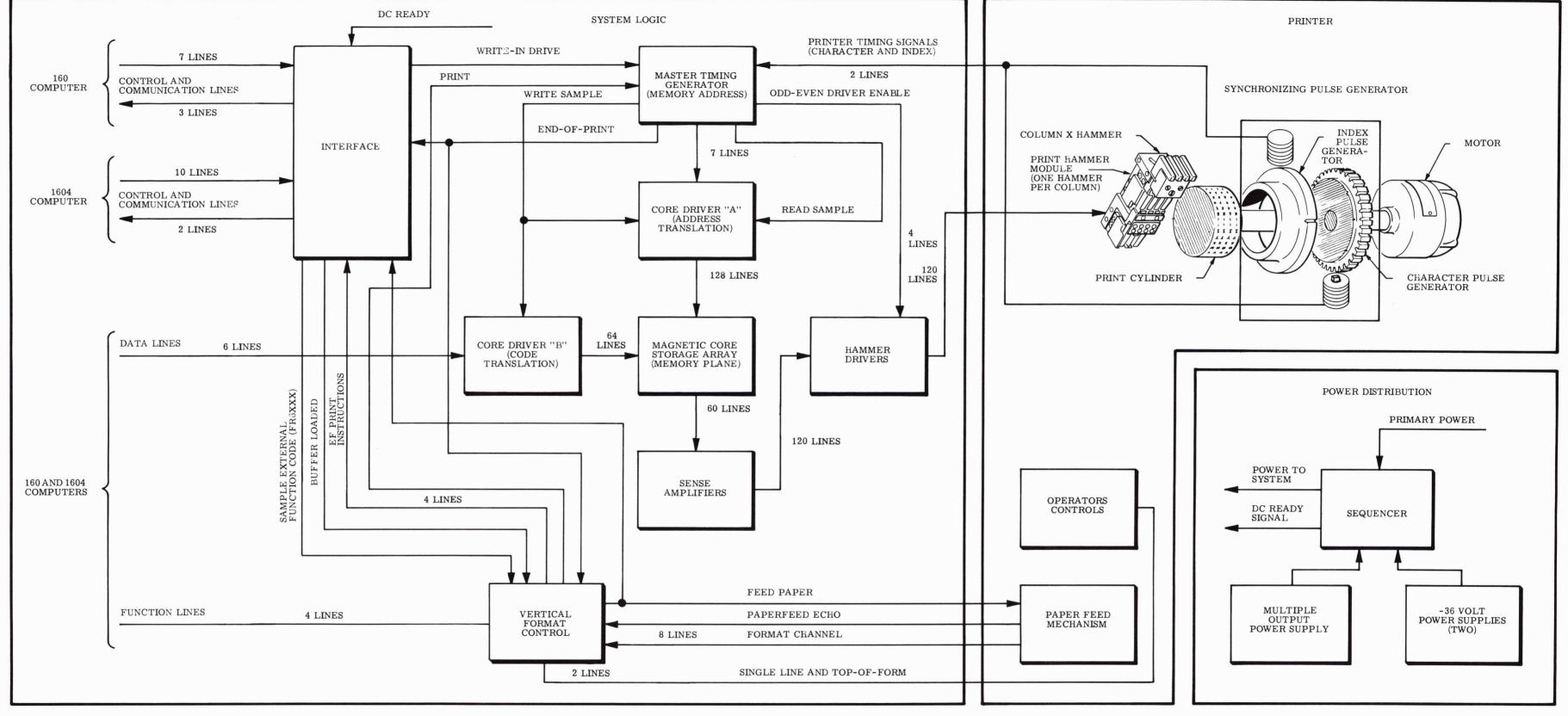

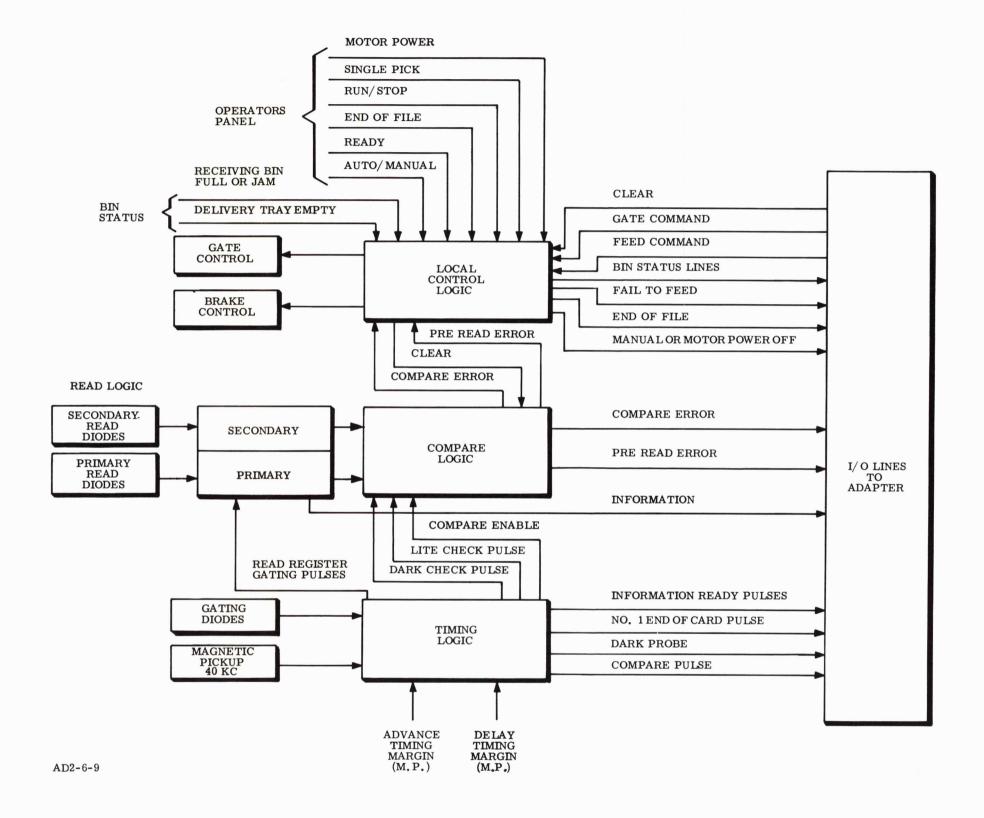

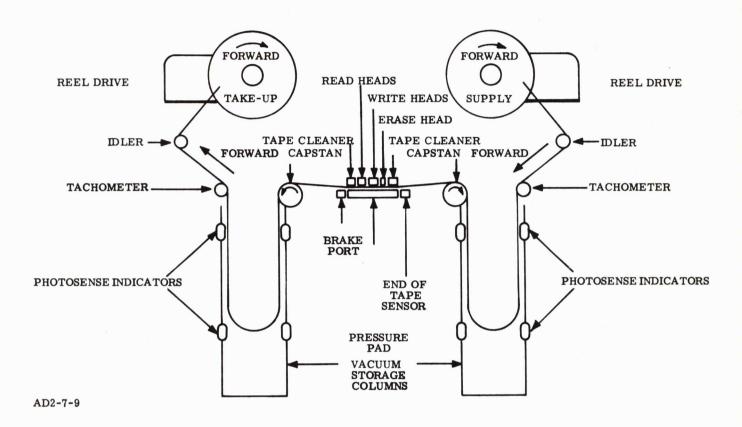

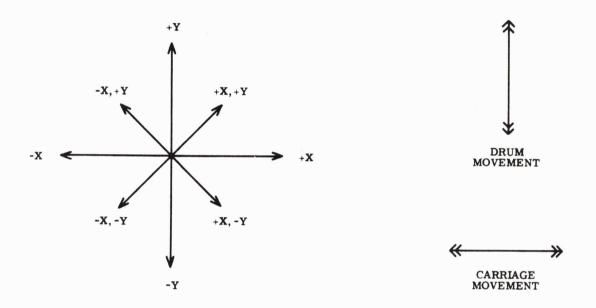

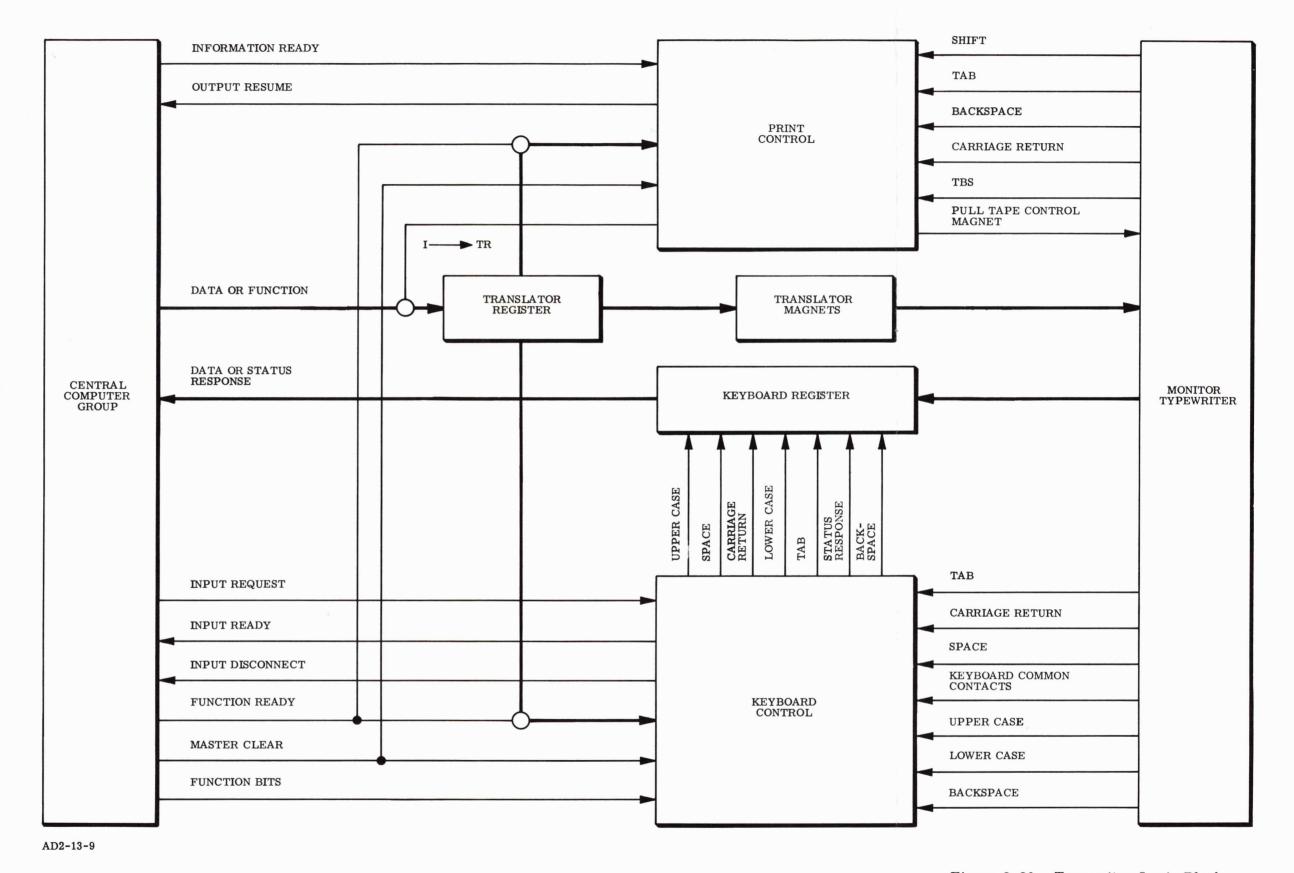

| 2-9Compute Module Simplified Block Diagram2-412-10Memory Module Simplified Block Diagram2-492-11Input/Output Module Block Diagram2-512-12Line Printer Simplified Block Diagram2-592-13Card Reader Logic Block Diagram2-612-14Tape Motion Simplified Diagram2-652-15Tape Transport Logic Block Diagram2-672-16Tape Control Unit Logic Block Diagram2-722-17Card Punch Controller Logic Block Diagram2-752-18X-Y Plotter Simplified Block Diagram2-782-19X-Y Plotter Motion Coordinates2-792-20Typewriter Logic Block Diagram2-81                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2-21 Data Transmission and Verification Converter Block Diagram 2-87 2-22 Data Transmission and Verification Converter Operational Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# LIST OF ILLUSTRATIONS (Cont'd)

| Figure |                                                                             | Page   |

|--------|-----------------------------------------------------------------------------|--------|

|        | SECTION III. DISPLAY AND RECORDING EQUIPMENT                                |        |

| 3-1    | Data Acquisition and Decommutation Equipment Functional                     |        |

|        | Block Diagram                                                               | 3-3    |

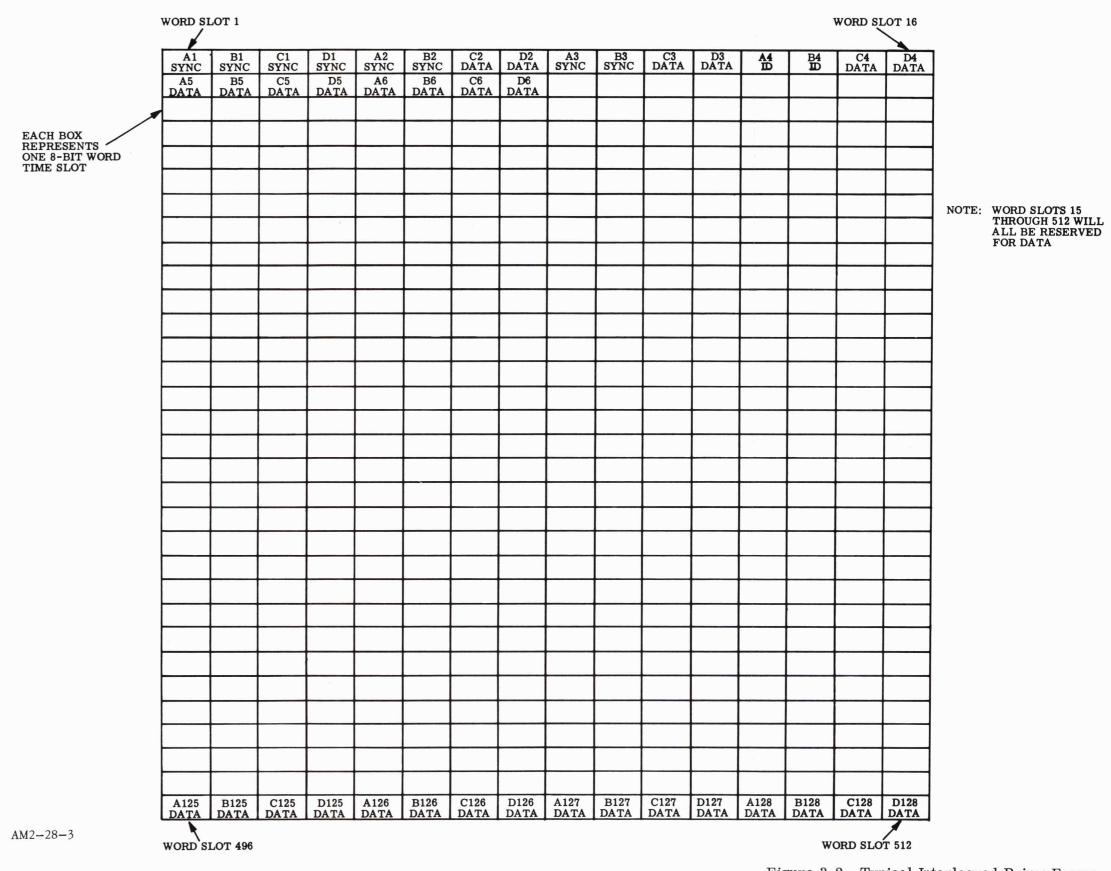

| 3-2    | Typical Interleaved Prime Frame Composition and Word Location               | 3-7    |

| 3-3    | Typical Airborne Prime Frame Composition and Word Location                  | 3-9    |

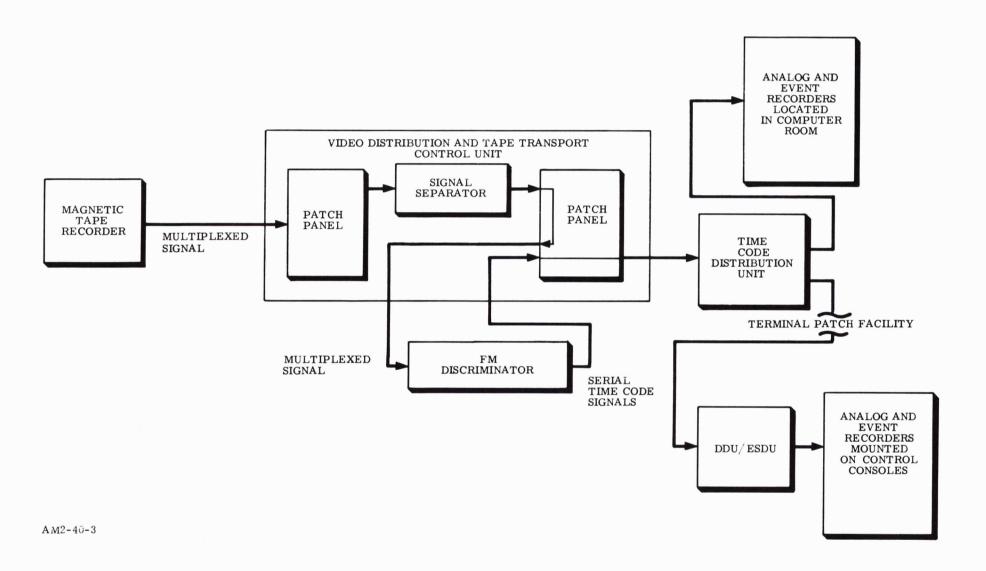

| 3-4    | Video Distribution and Tape Transport Control Unit Functional Block Diagram | 3-11   |

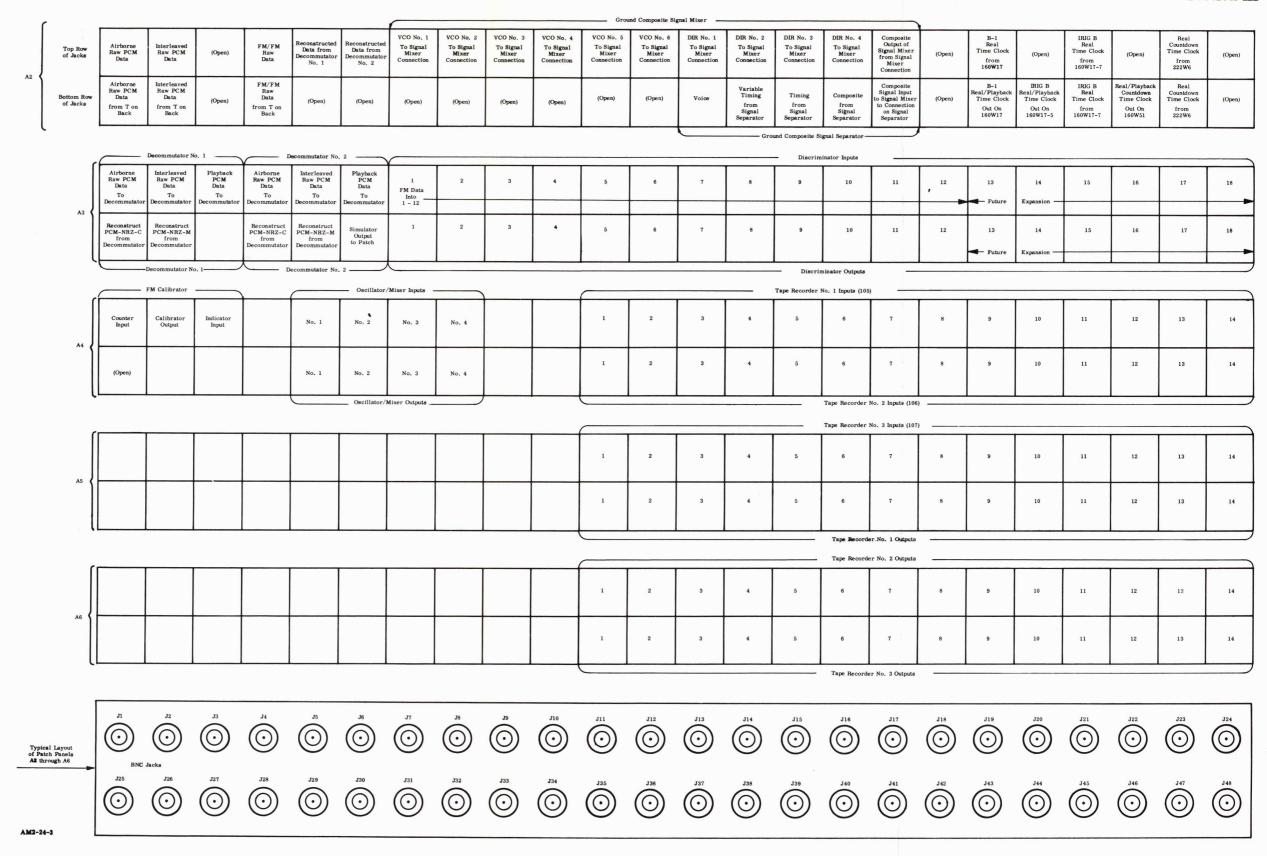

| 3-5    | Patch Panel Layout and Signal Identification                                | 3-13   |

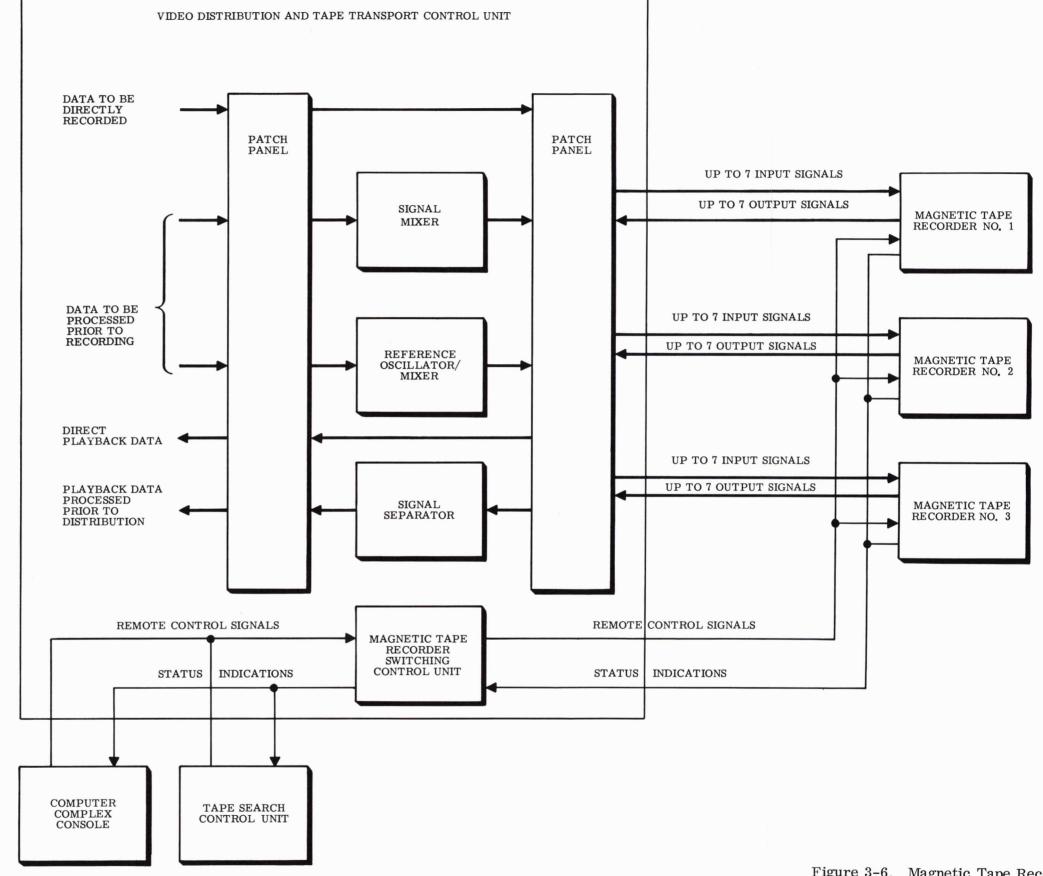

| 3-6    | Magnetic Tape Recorder Input/Output Functional Block Diagram                | 3-15   |

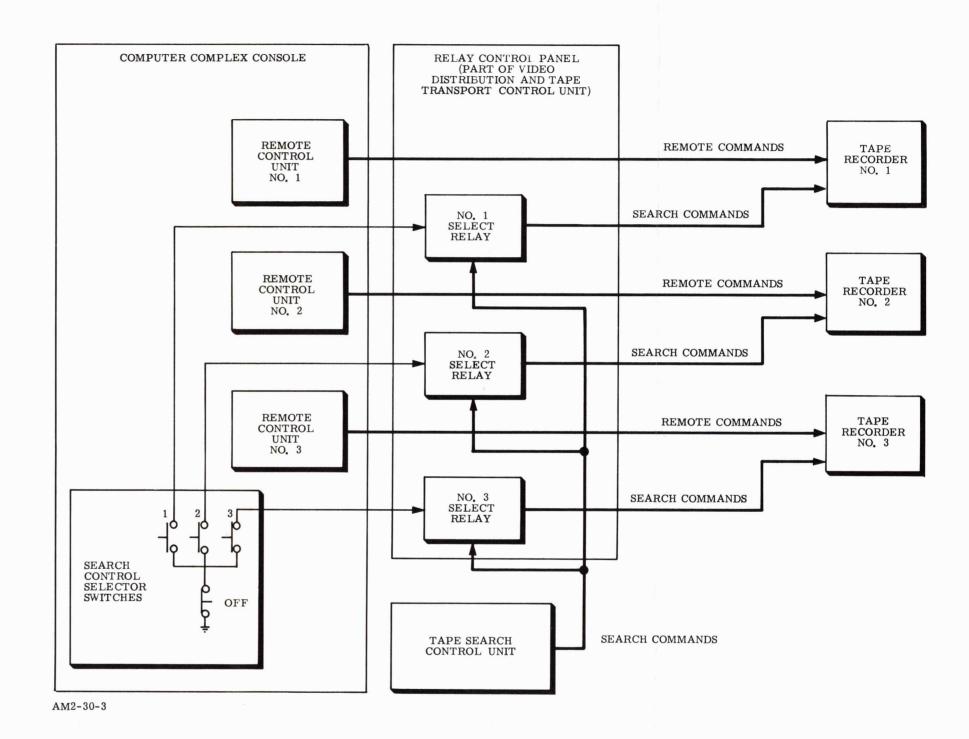

| 3-7    | Search Control Functional Block Diagram                                     | 3-19   |

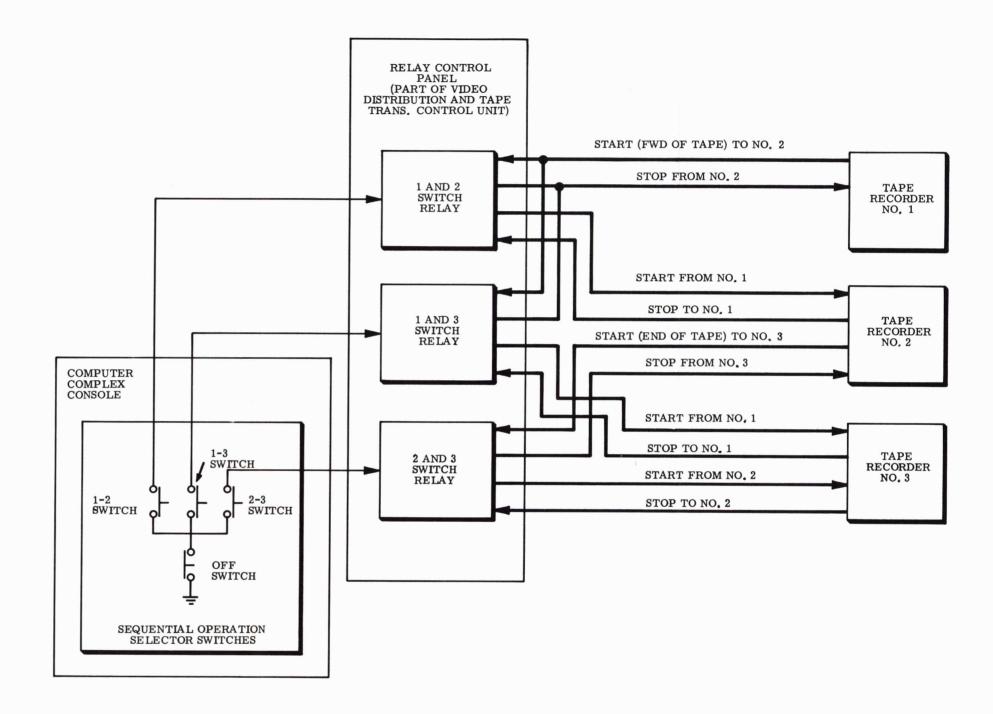

| 3-8    | Sequential Operation Functional Block Diagram                               | 3-21   |

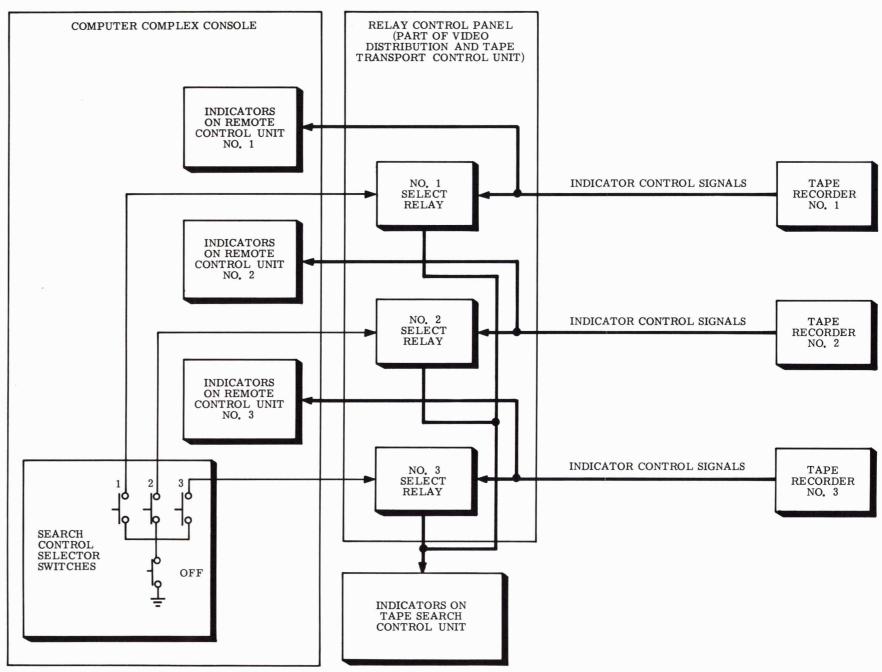

| 3-9    | Status Indication Functional Block Diagram                                  | 3-23   |

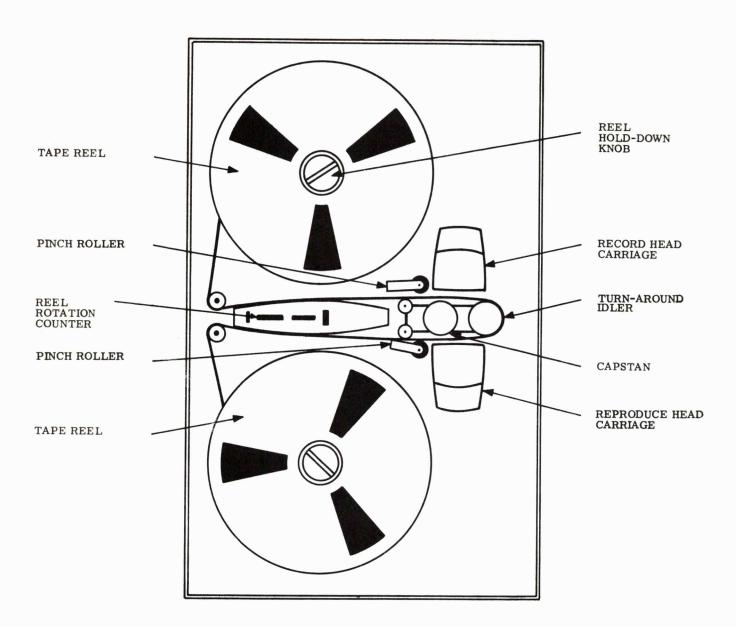

| 3-10   | Wideband Analog Tape Transport                                              | 3-26   |

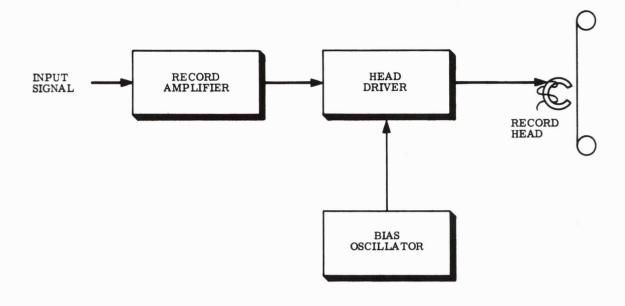

| 3-11   | Direct Record Circuit Block Diagram                                         | 3-29   |

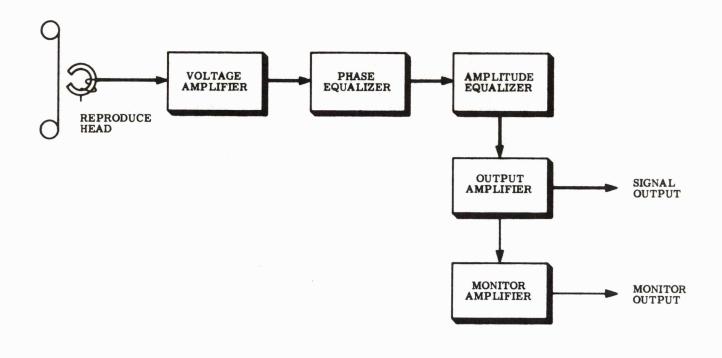

| 3-12   | Direct Reproduce Circuit Block Diagram                                      | 3-30   |

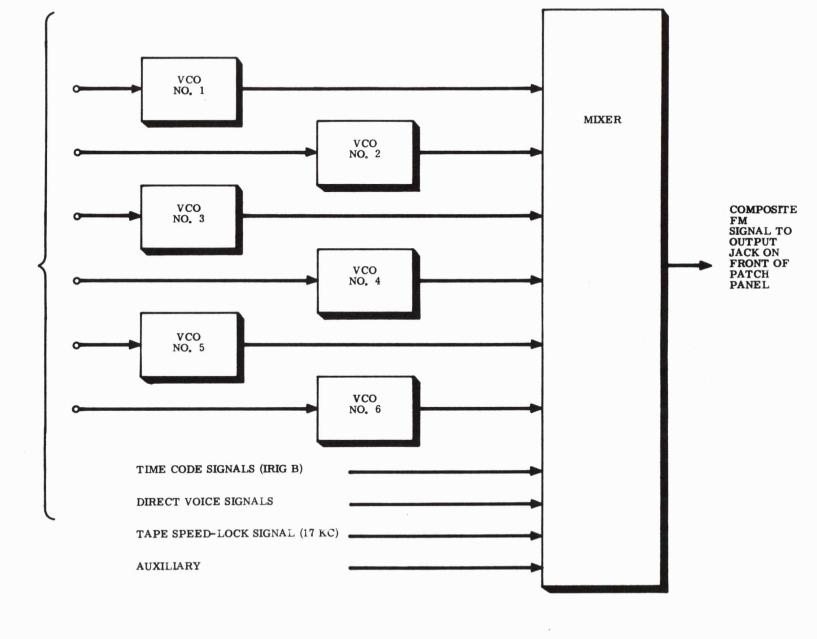

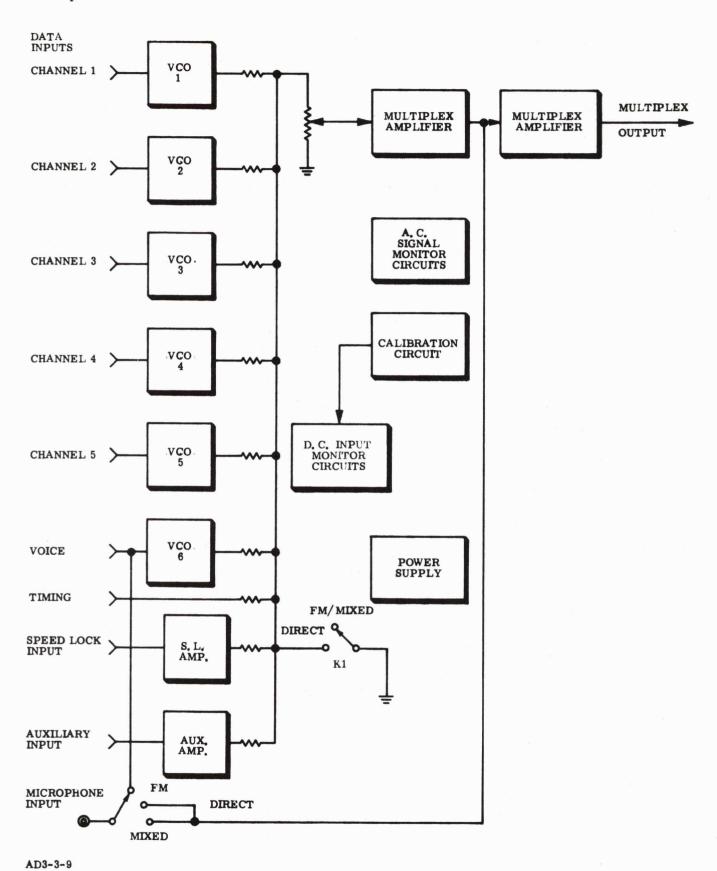

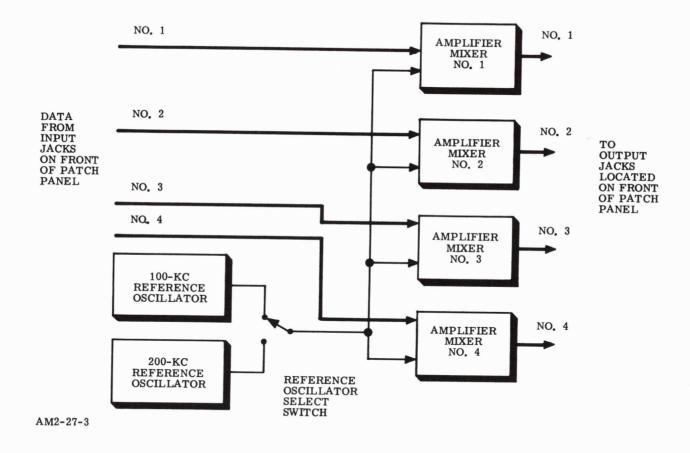

| 3-13   | Signal Mixer Functional Block Diagram                                       | 3-33   |

| 3-14   | Signal Mixer Simplified Block Diagram                                       | 3-35   |

| 3-15   | Reference Mixer/Oscillator Functional Block Diagram                         | 3-37   |

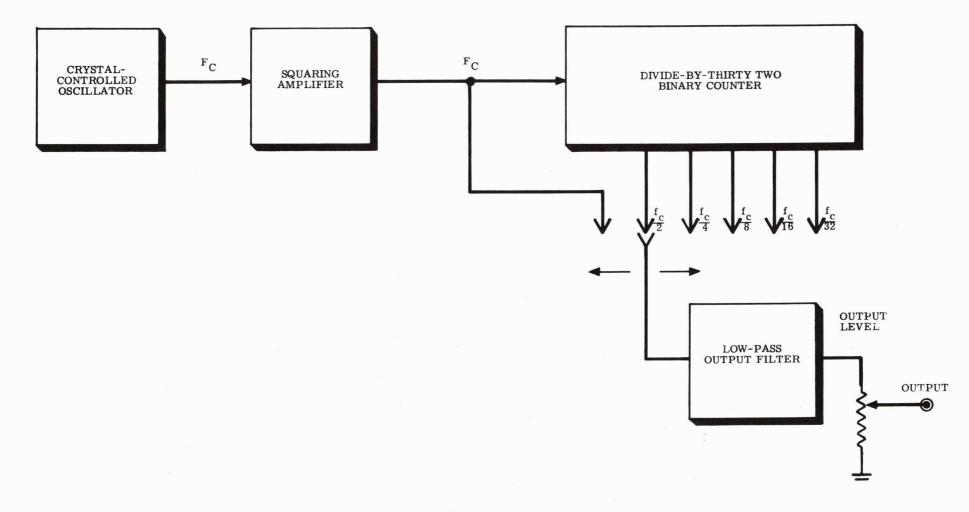

| 3-16   | Reference Oscillator Simplified Block Diagram                               | 3-39   |

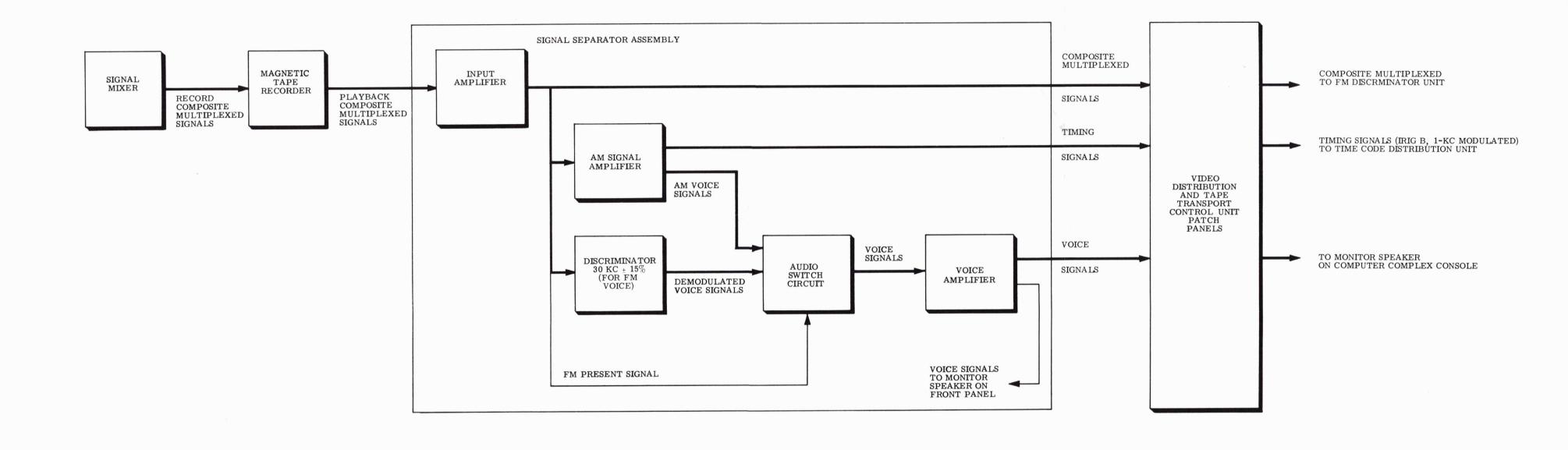

| 3-17   | Signal Separator Functional Block Diagram                                   | 3 - 41 |

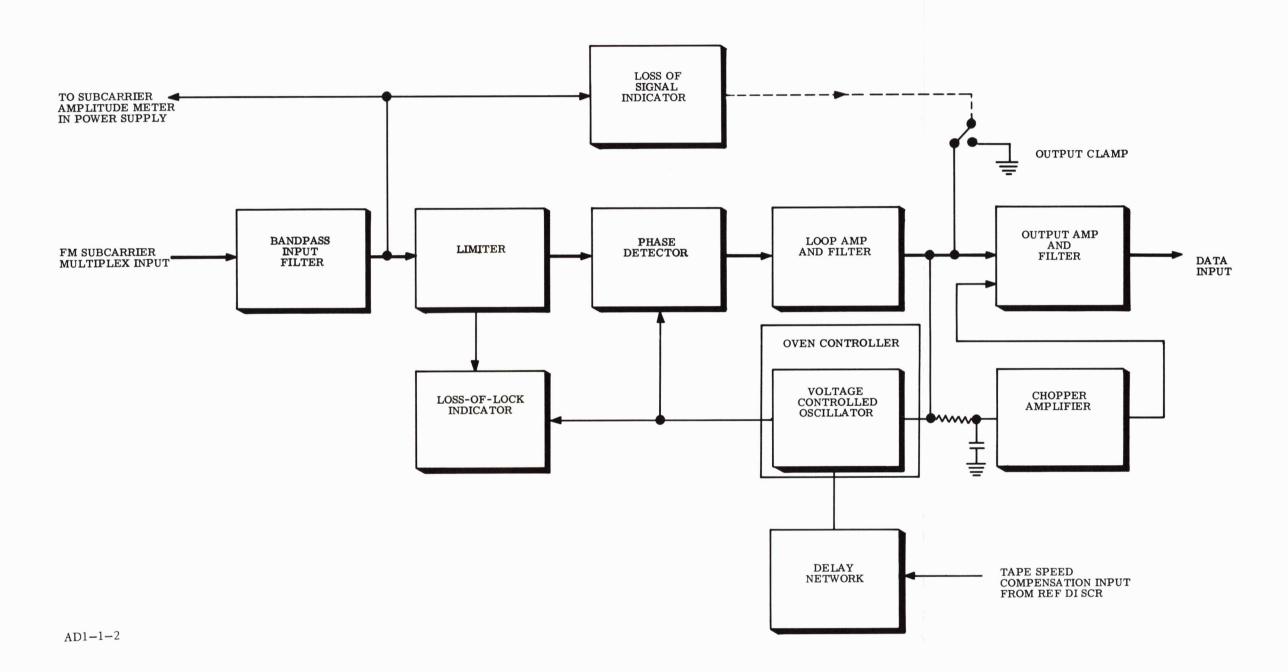

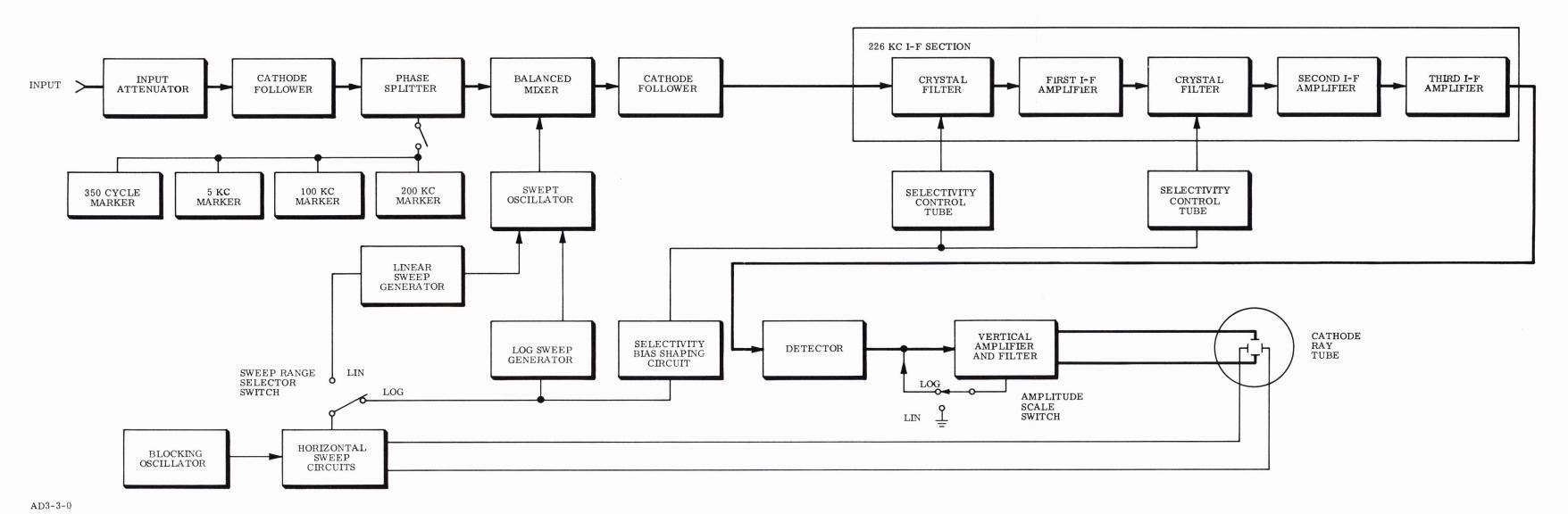

| 3-18   | FM Subcarrier Discriminator Block Diagram                                   | 3-45   |

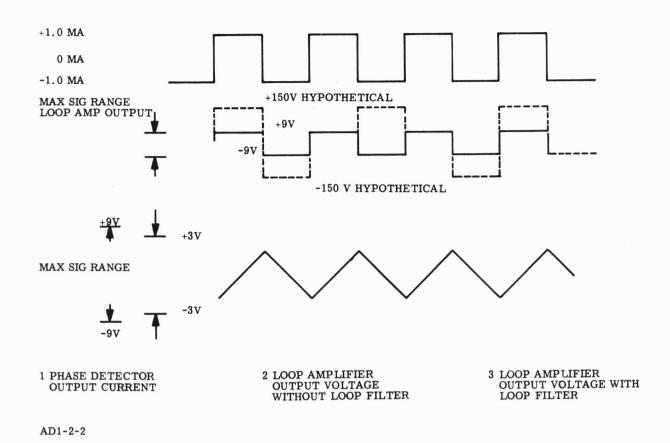

| 3-19   | FM Subcarrier Discriminator Idealized Waveforms                             | 3-49   |

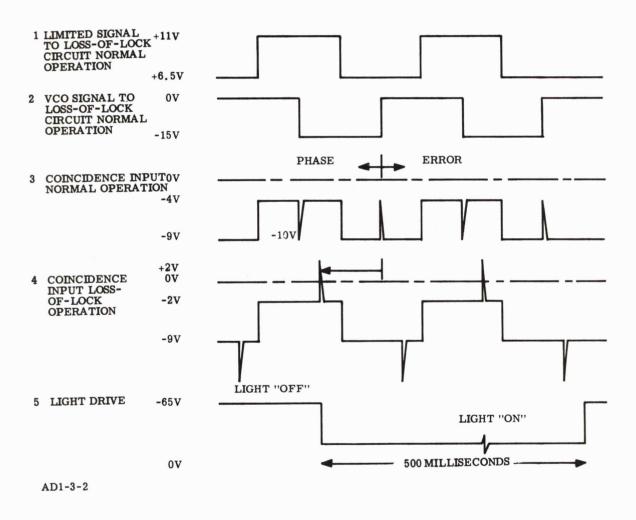

| 3-20   | Idealized Waveforms, FM Subcarrier Discriminator Loss-of-Lock Circuit       | 3-52   |

| 3-21   | FM Telemetry Indicator Simplified Block Diagram                             | 3-55   |

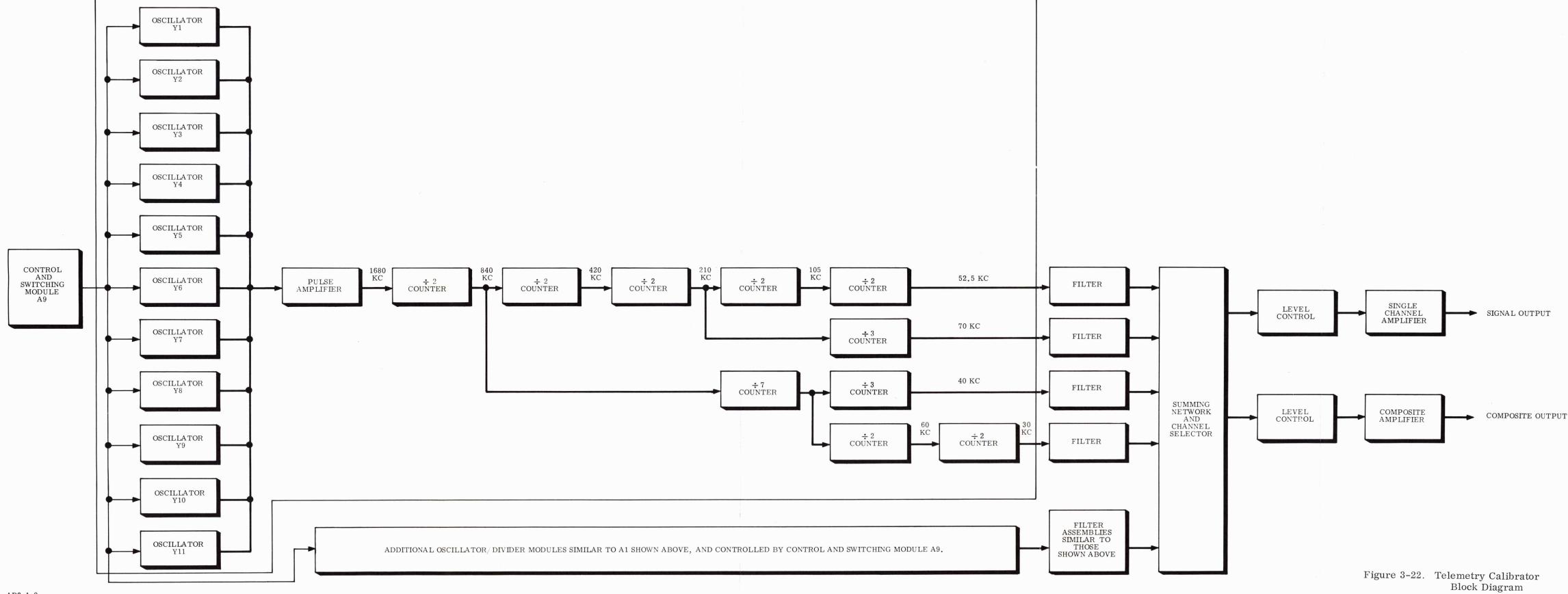

| 3-21   | Telemetry Calibrator Block Diagram                                          | 3-59   |

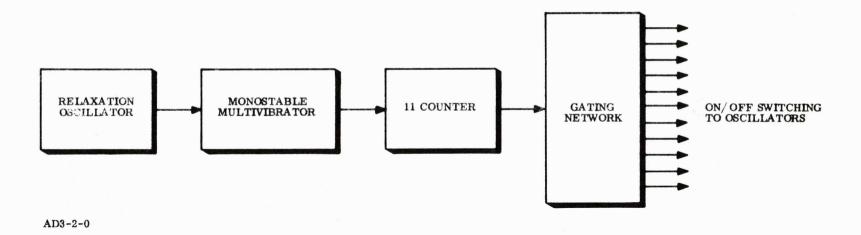

| 3-23   | Switching Module Block Diagram                                              | 3-61   |

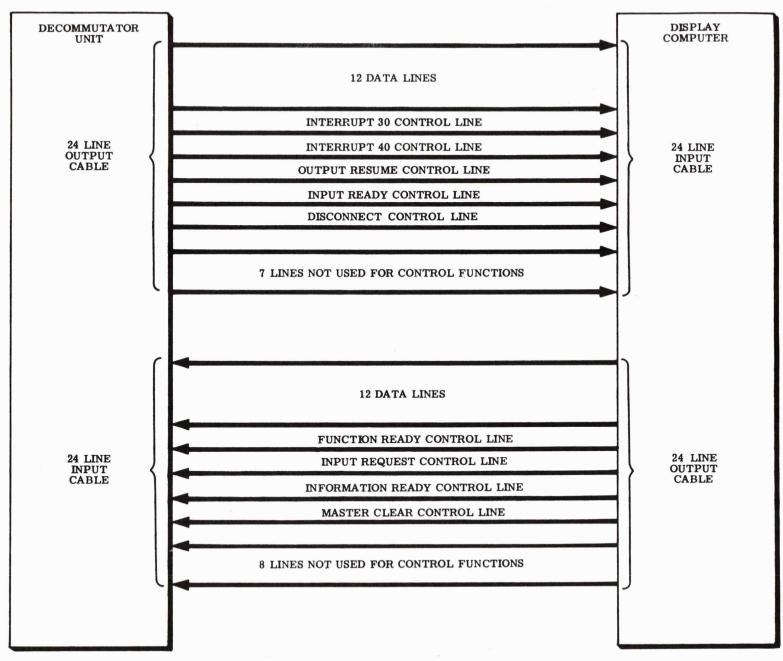

| 3-24   | Decommutator/Computer Connections                                           | 3-63   |

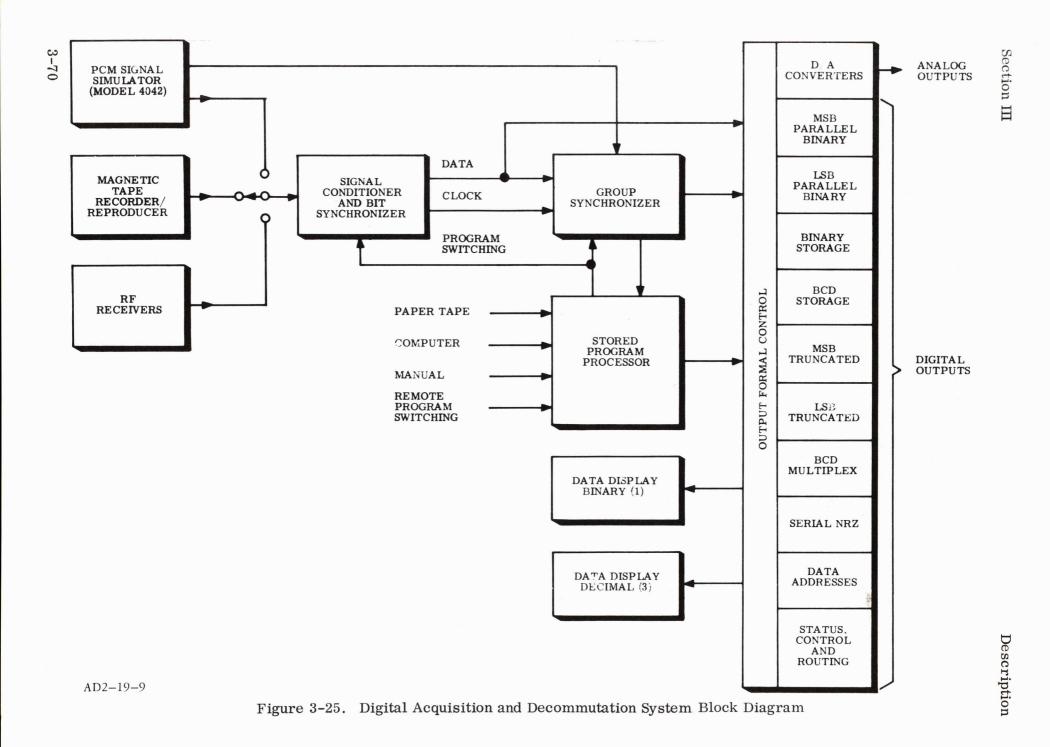

| 3-25   | Digital Acquisition and Decommutation System Block Diagram                  | 3-70   |

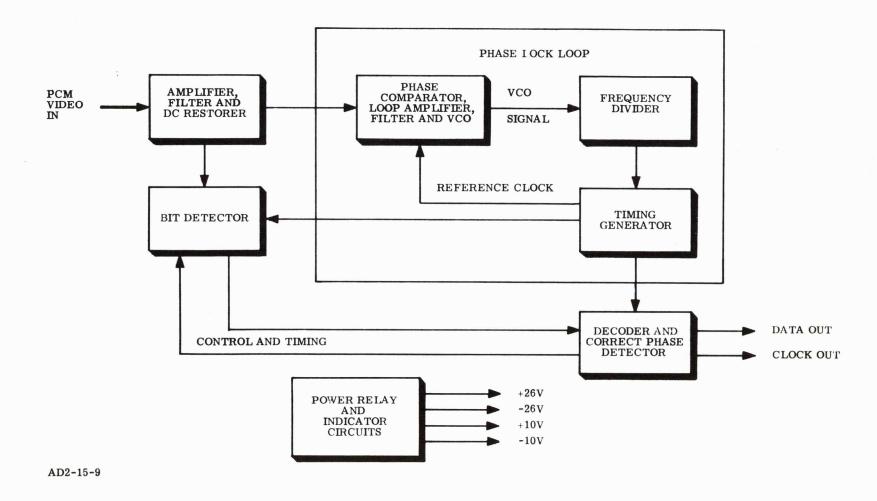

| 3-26   | Signal Conditioner Block Diagram                                            | 3-72   |

| 3-27   | Memory Organization and Coding                                              | 3-73   |

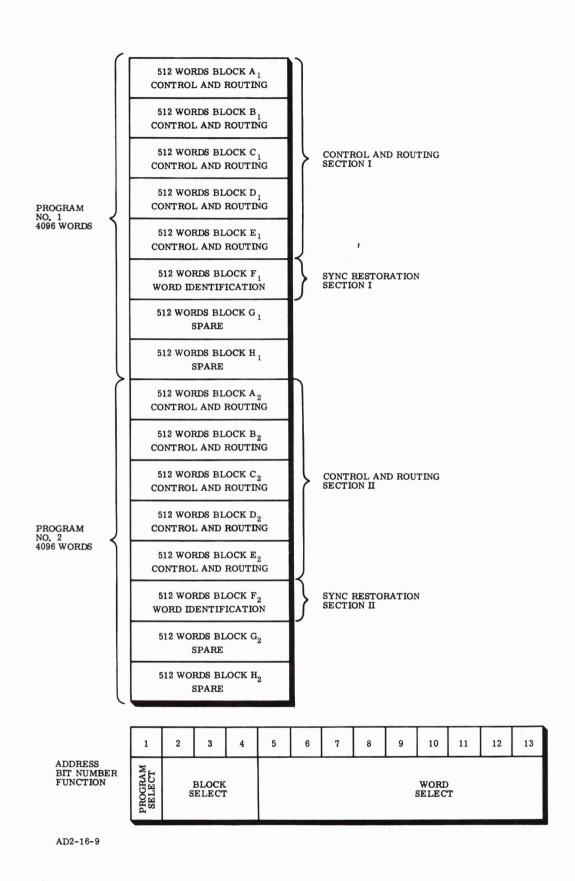

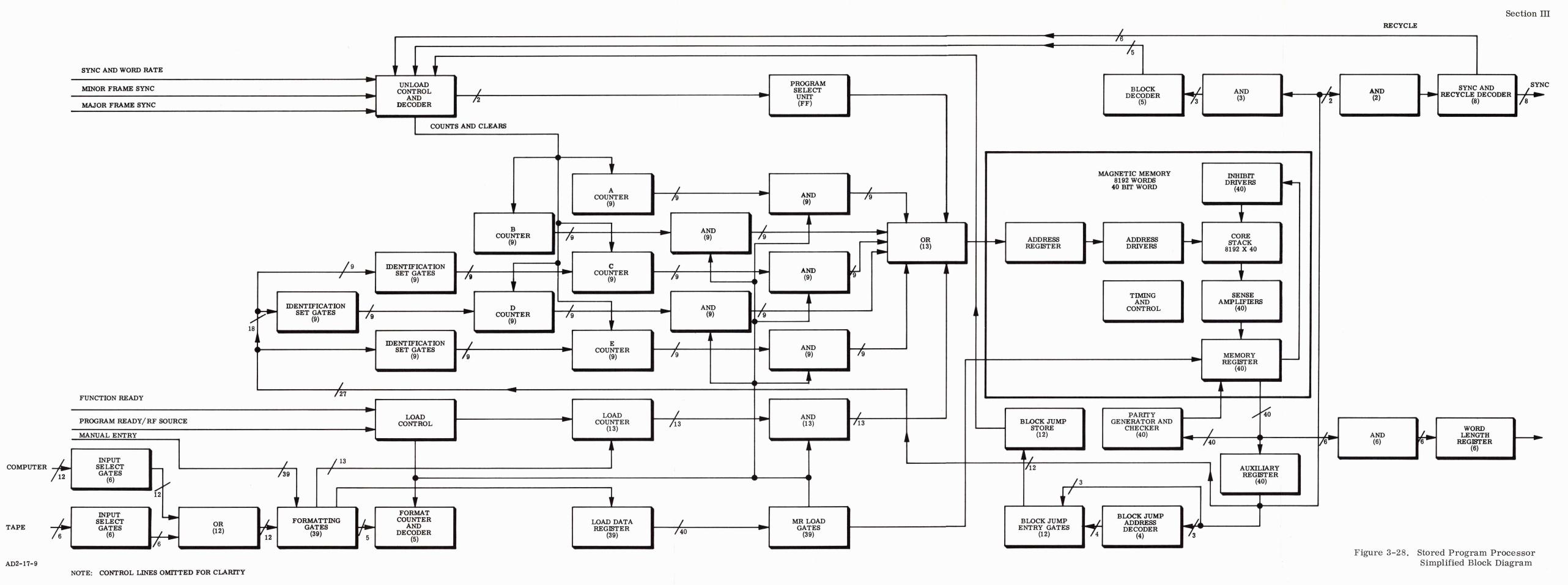

| 3-28   | Stored Program Processor Simplified Block Diagram                           | 3-75   |

| 3-29   | Memory Word Program Control and Routing Instruction Format                  | 3-77   |

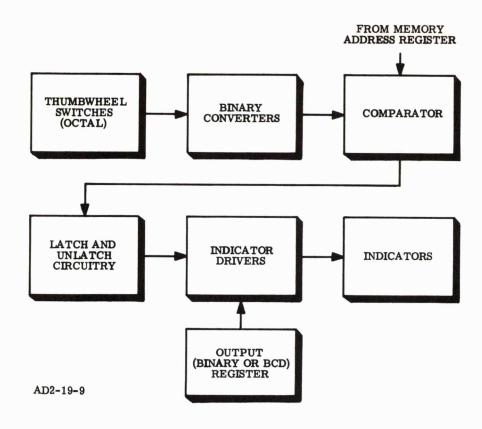

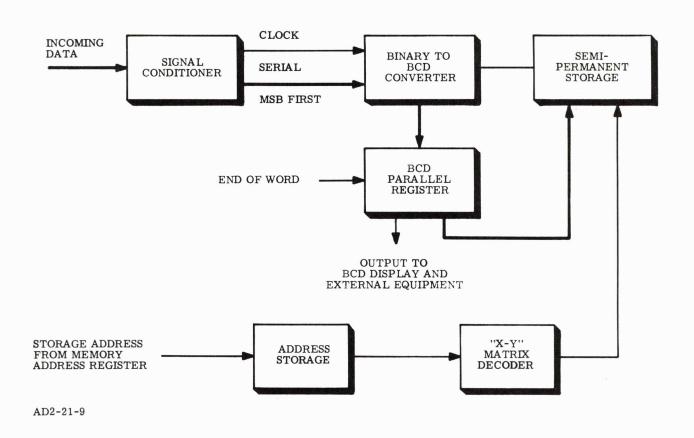

| 3-30   | BCD and Binary Display Simplified Block Diagram                             | 3-80   |

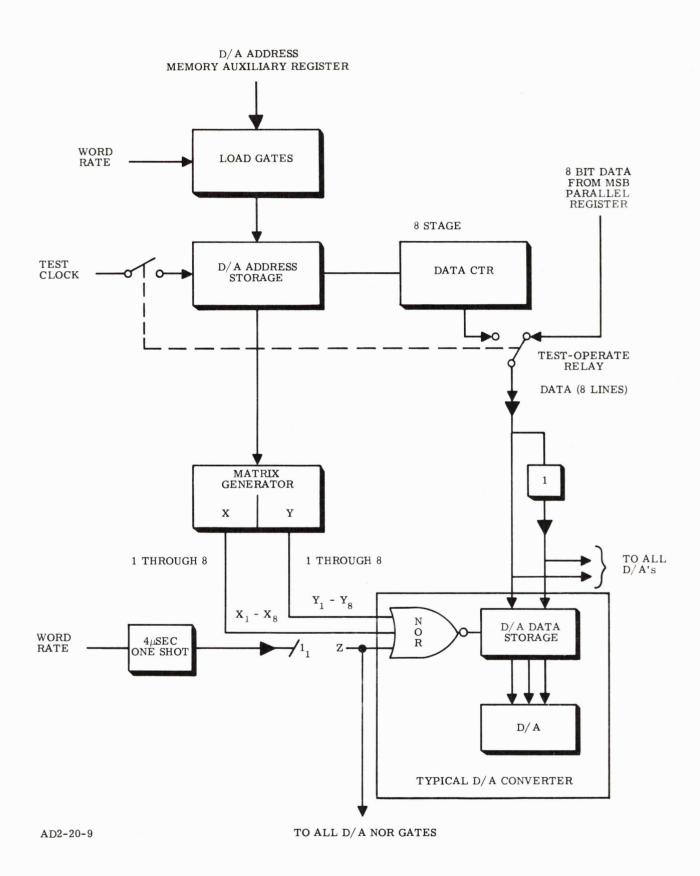

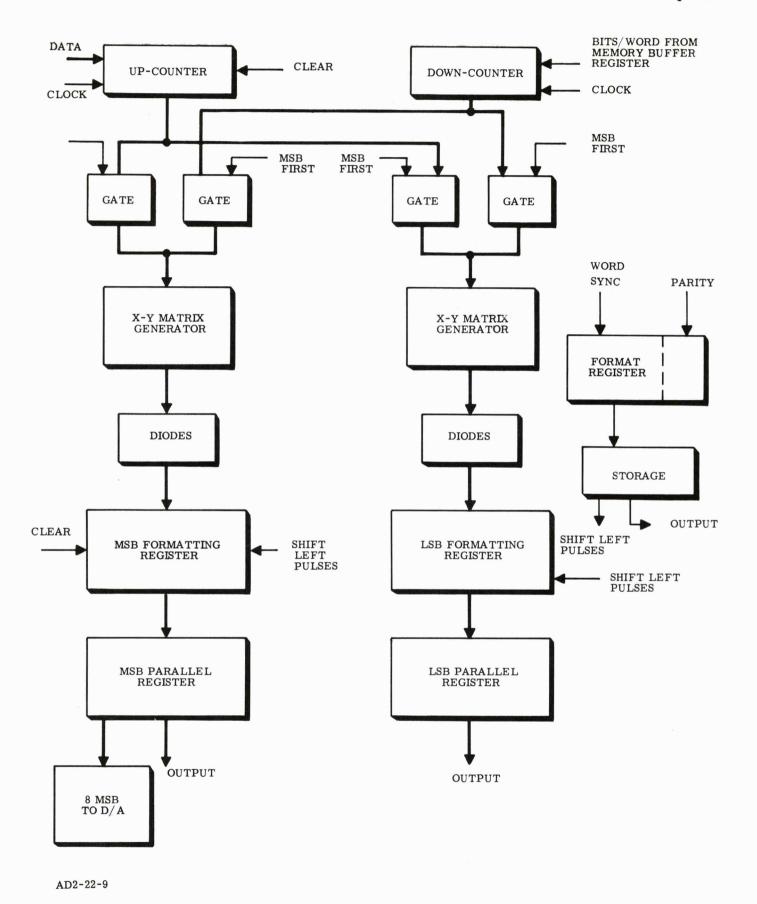

| 3-31   | Digital-to-Analog Conversion Simplified Block Diagram                       | 3-81   |

| 3-32   | Binary-to-BCD Converter Simplified Block Diagram                            | 3-83   |

| 3-33   | MSB and LSB Parallel Registers Simplified Block Diagram                     | 3-84   |

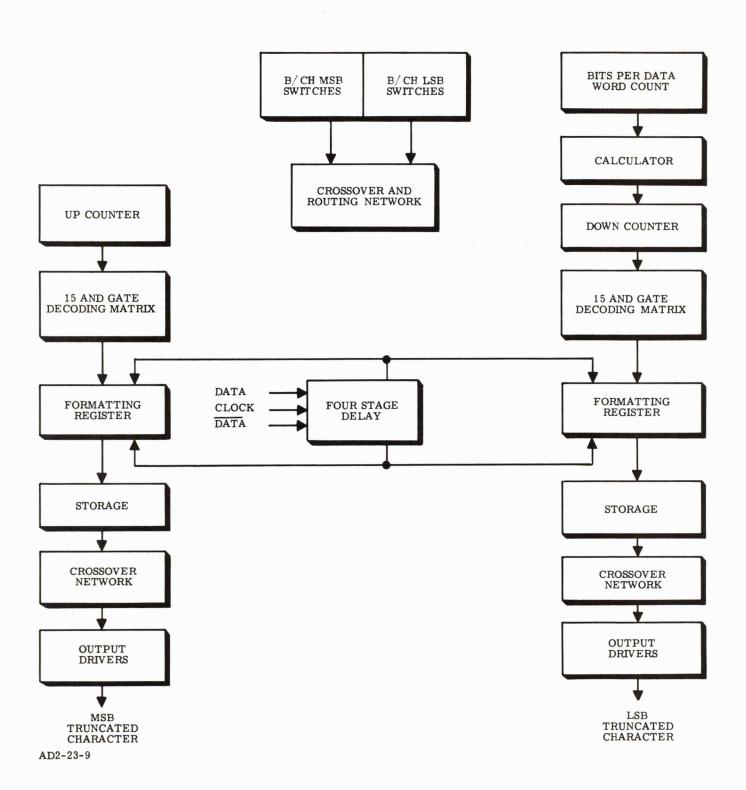

| 3-34   | MSB and LSB Truncated Character Formation Simplified                        |        |

| 200    | Block Diagram                                                               | 3-88   |

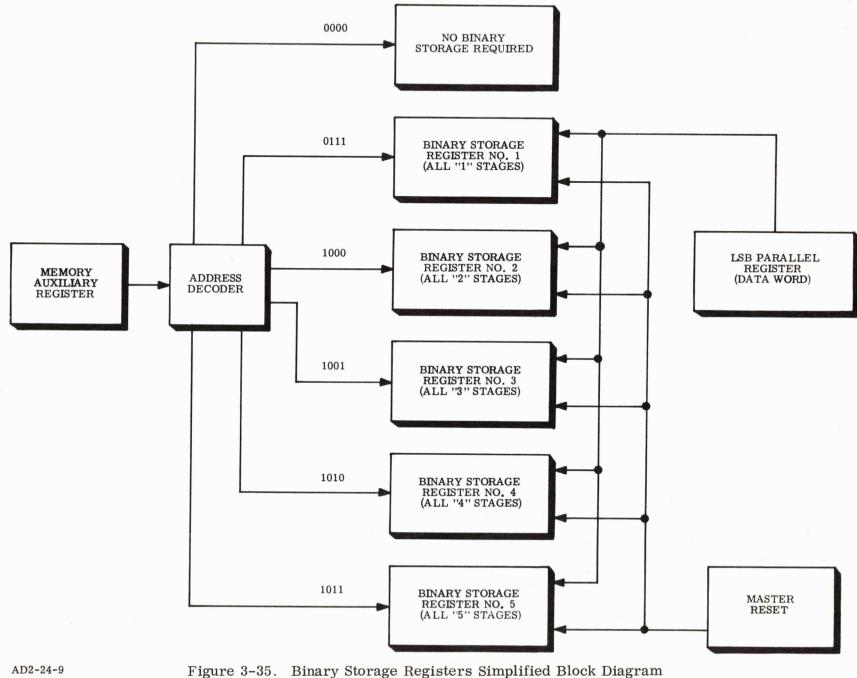

| 3-35   | Binary Storage Registers Simplified Block Diagram                           | 3-91   |

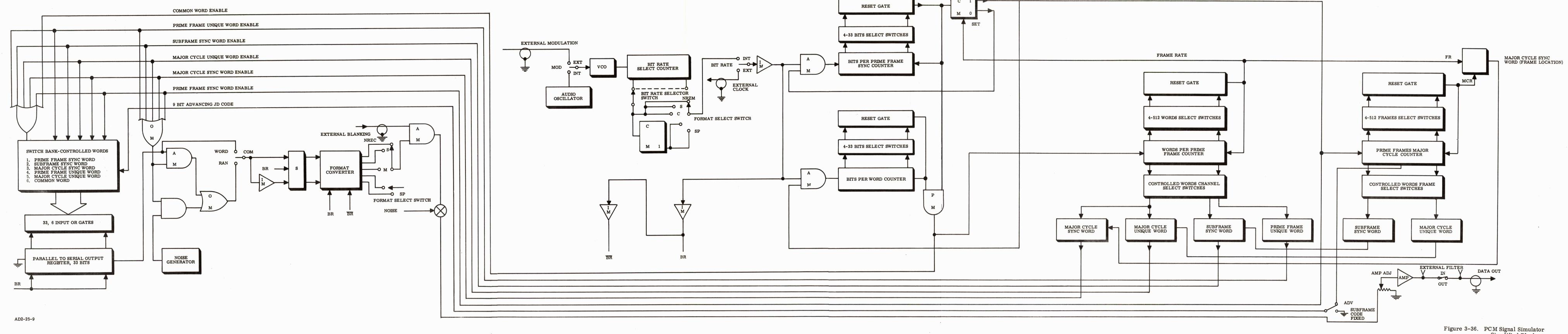

| 3-36   | PCM Signal Simulator Simplified Block Diagram                               | 3-93   |

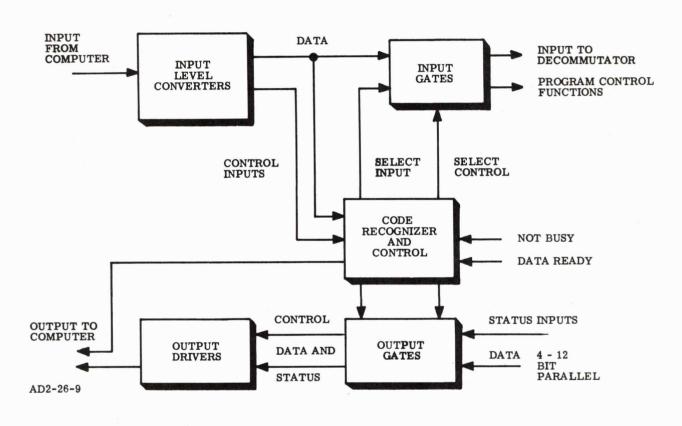

| 3-37   | Decommutator/Computer Interface Simplified Block Diagram                    | 3-95   |

# LIST OF ILLUSTRATIONS (Cont'd)

| Figure |                                                           | Page  |

|--------|-----------------------------------------------------------|-------|

| 3-38   | Control Room Test Data Display and Recording Equipment    |       |

|        | Block Diagram                                             | 3-97  |

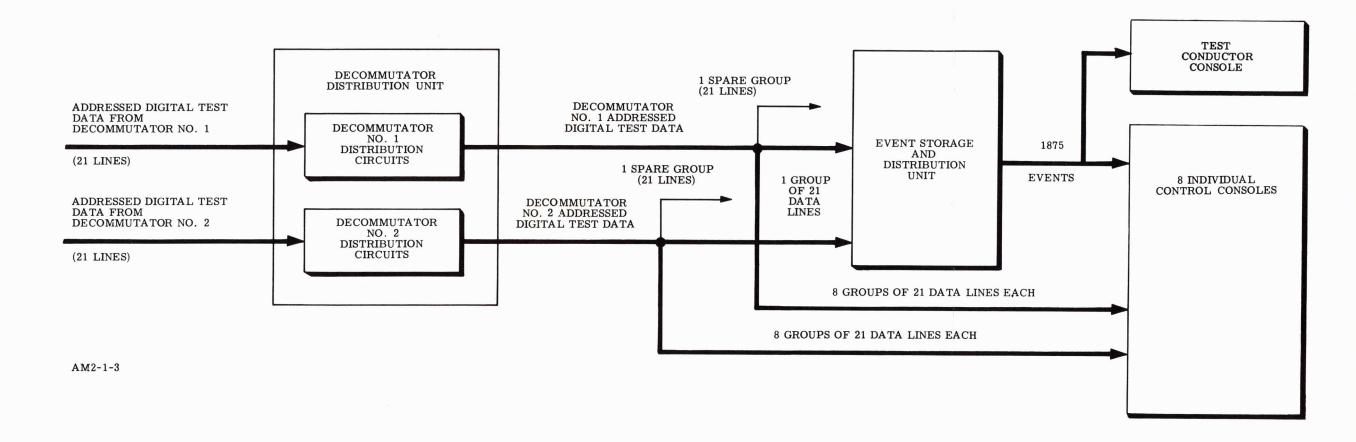

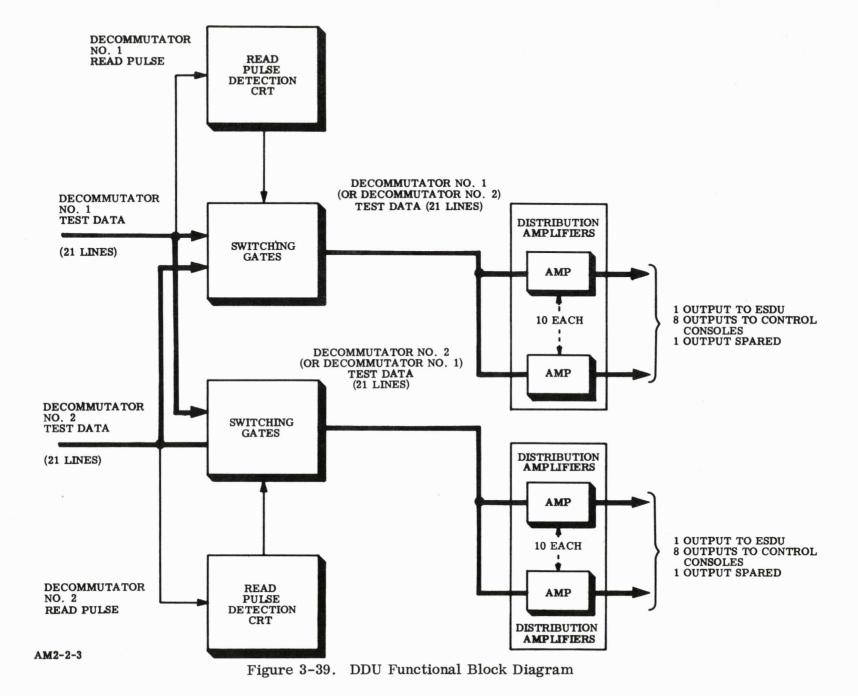

| 3-39   | DDU Functional Block Diagram                              | 3-100 |

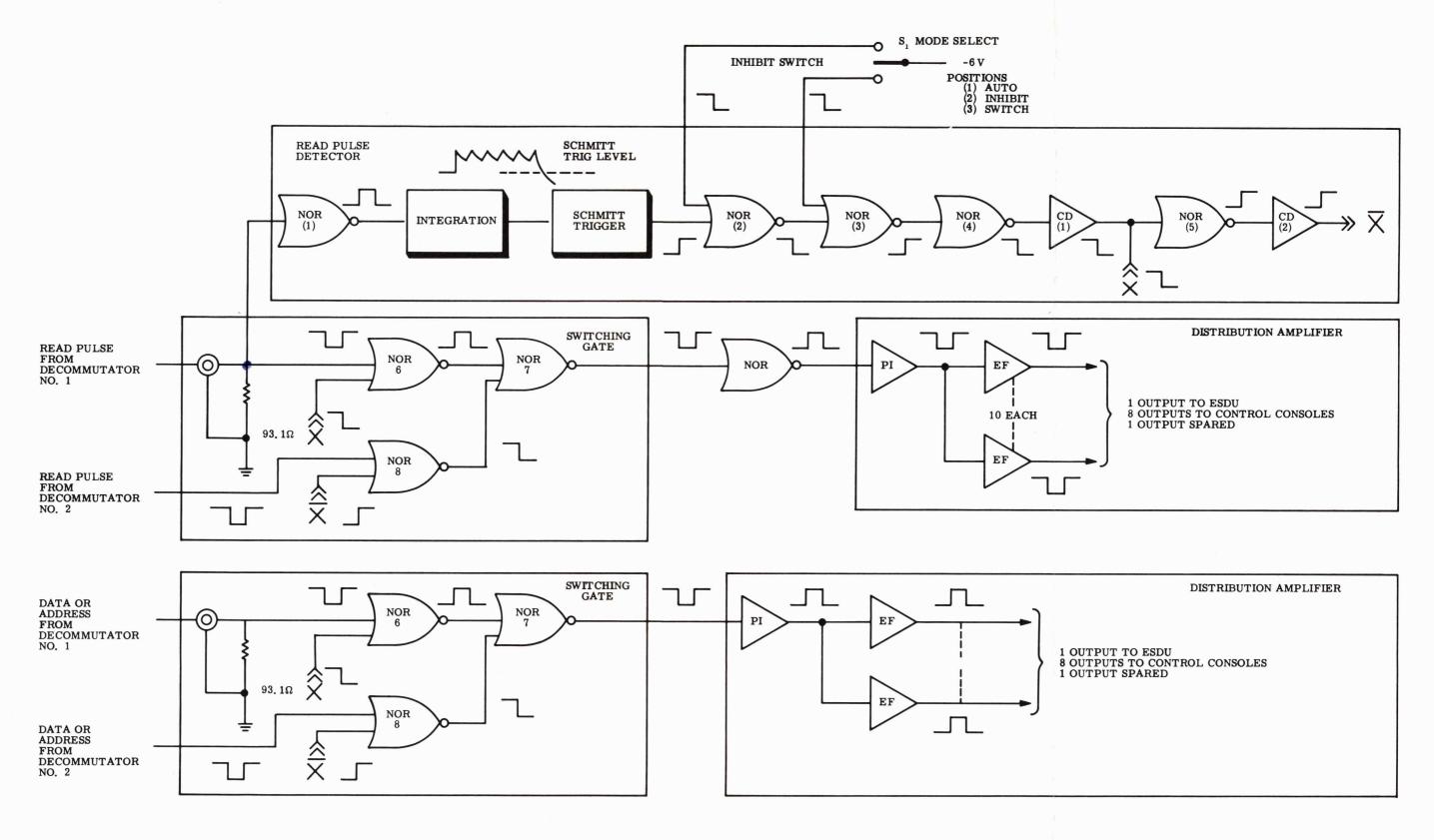

| 3-40   | Typical DDU Circuit                                       |       |

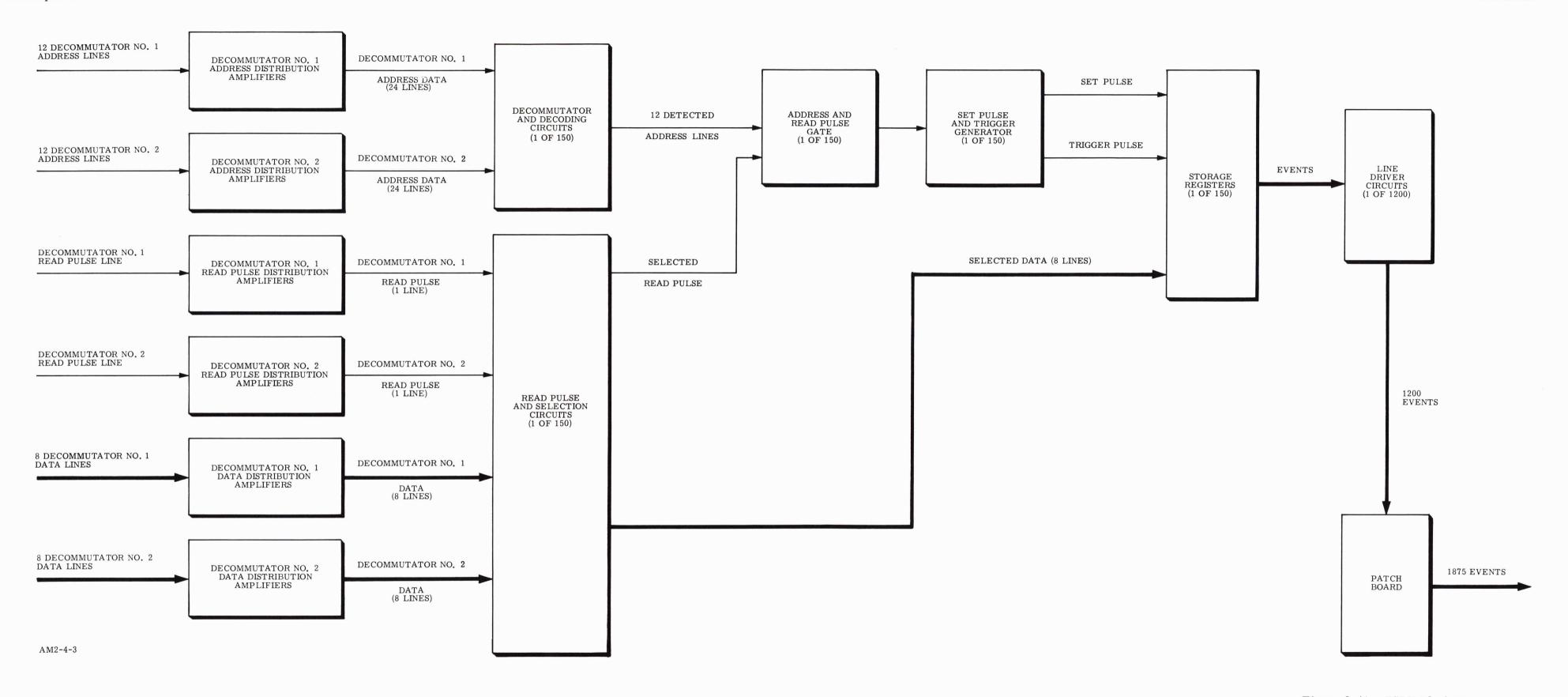

| 3-41   | ESDU Block Diagram                                        |       |

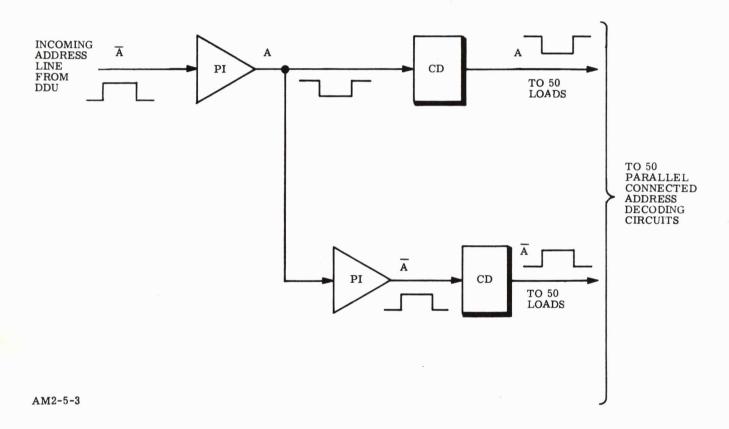

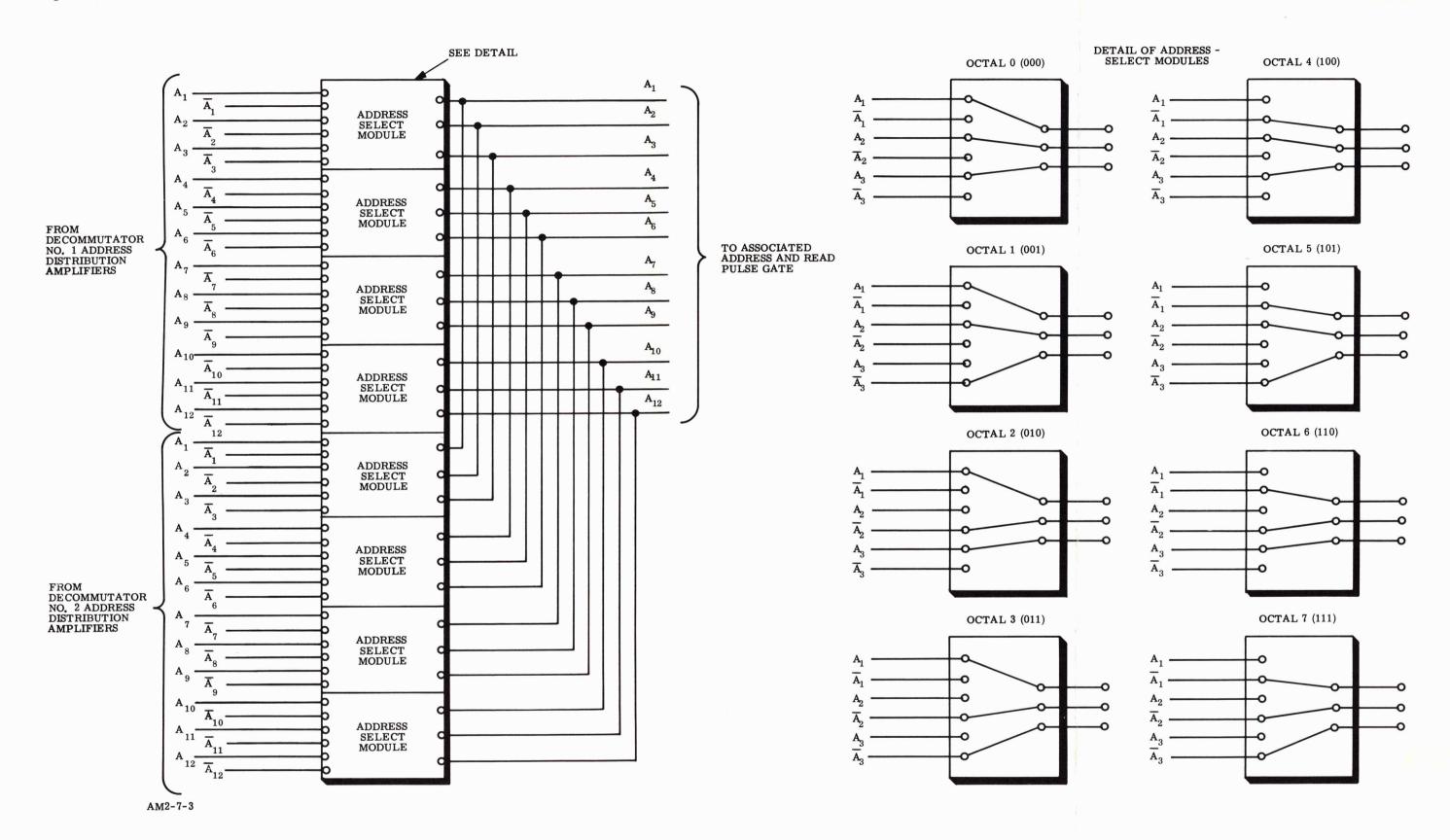

| 3-42   | Typical Address Distribution Amplifier                    |       |

| 3-43   | Typical Address Decoding Circuit                          |       |

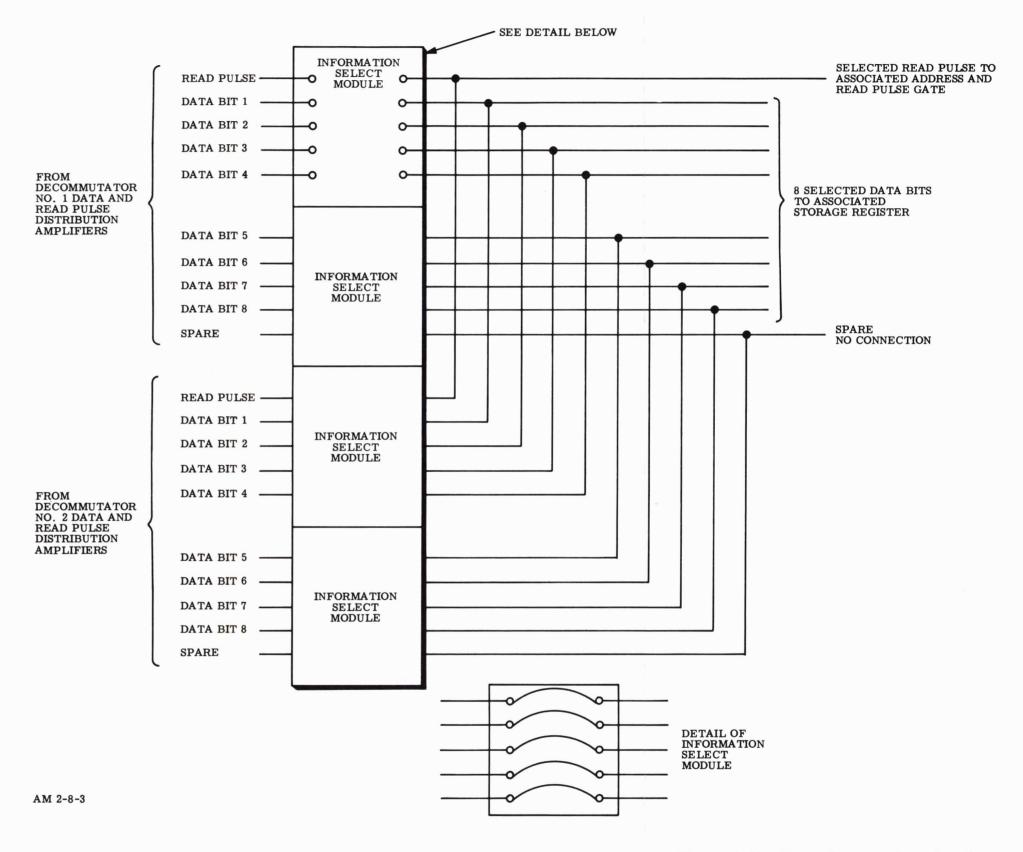

| 3-44   | Typical Data and Read-Pulse Selection Circuit             |       |

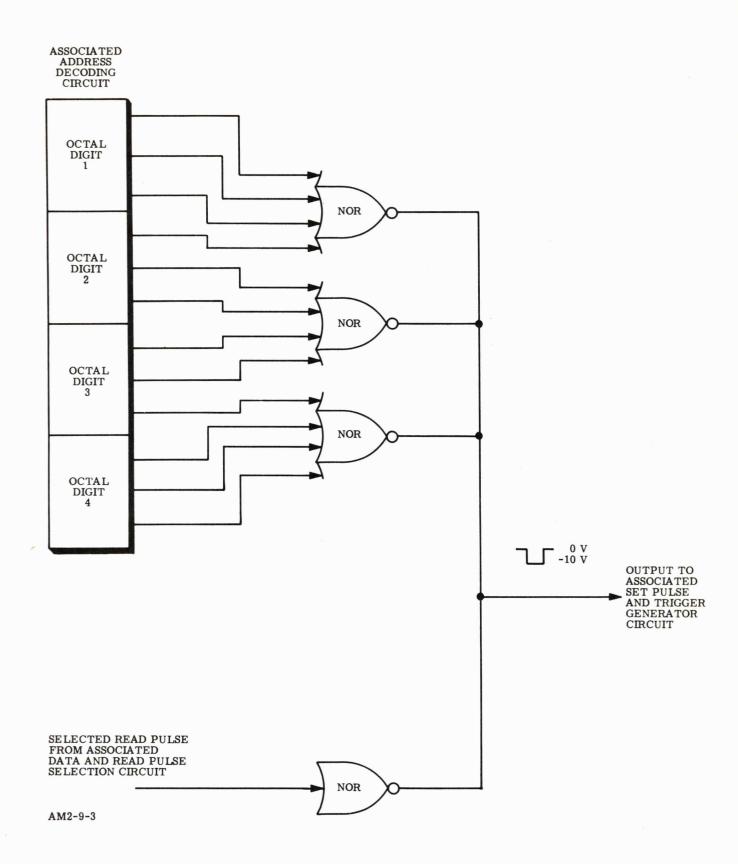

| 3-45   | Typical Address and Read-Pulse Gate                       | 3-117 |

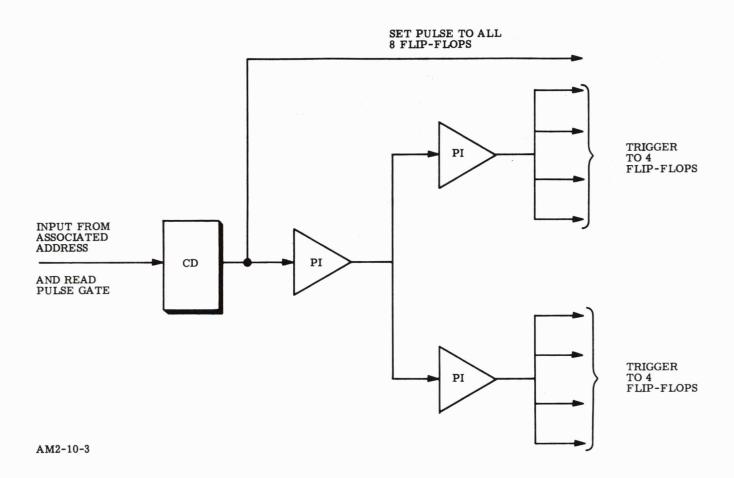

| 3-46   | Typical Set-Pulse and Trigger-Generator Circuit           | 3-118 |

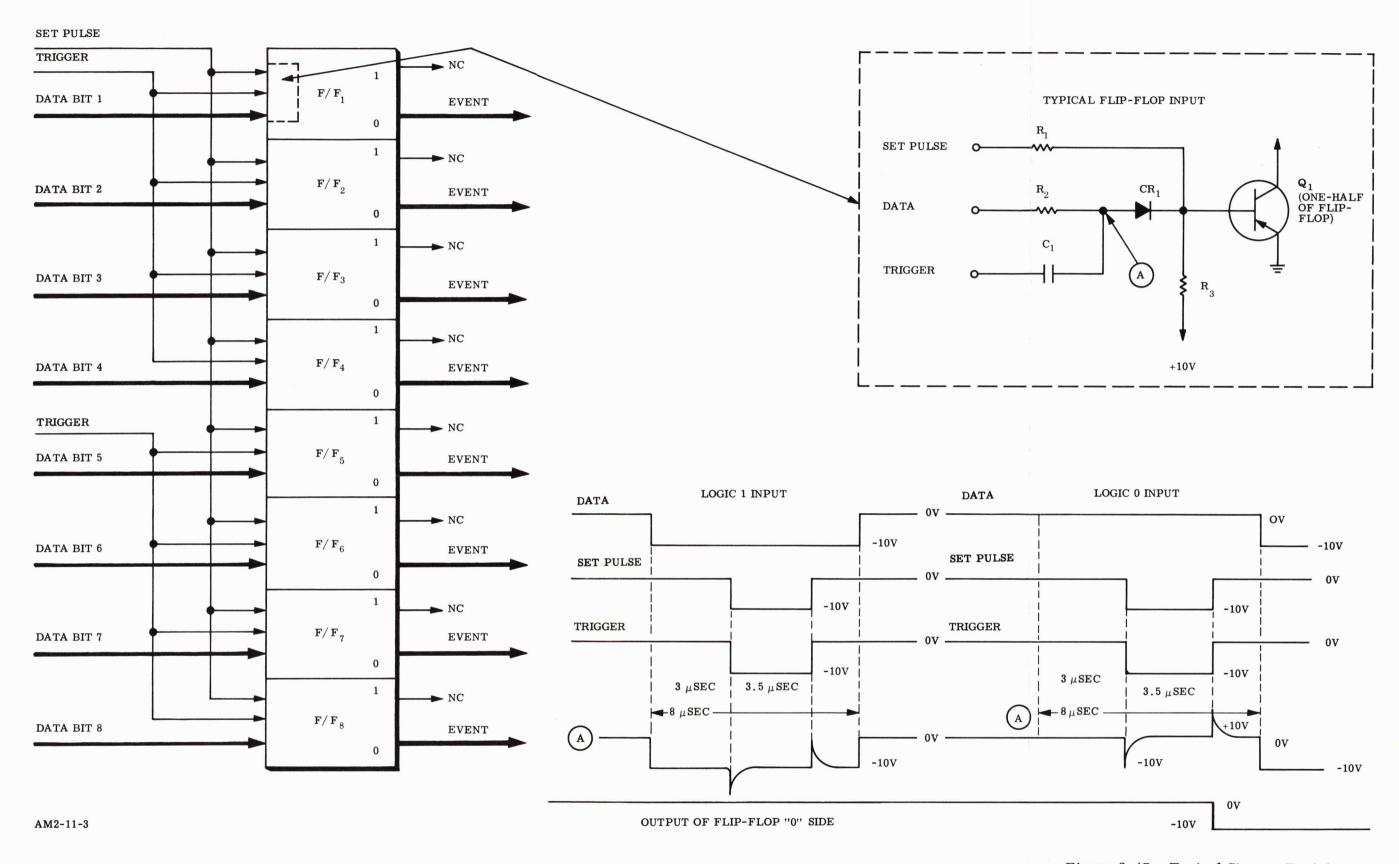

| 3-47   | Typical Storage Register Circuit                          | 3-119 |

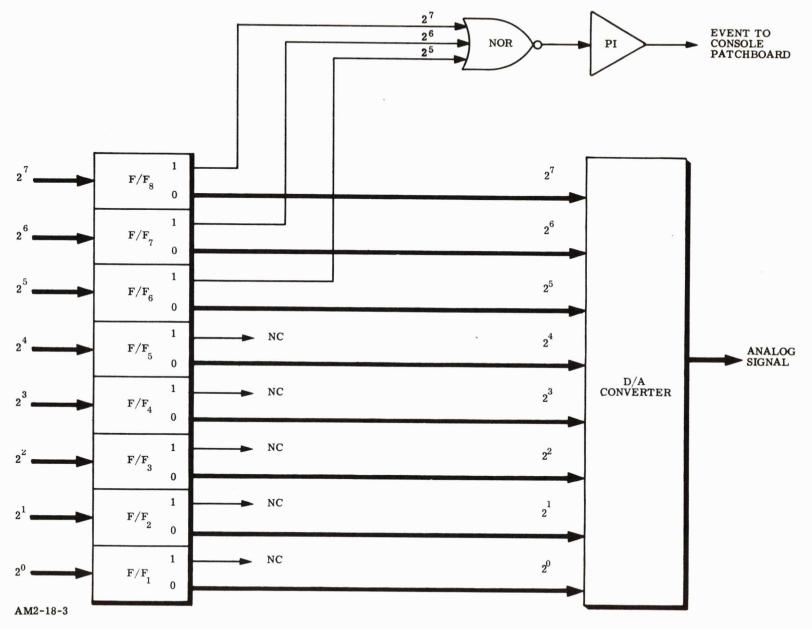

| 3-48   | Typical Control Console Block Diagram                     |       |

| 3-49   | Typical 2 to 1 Address Selection Circuit                  |       |

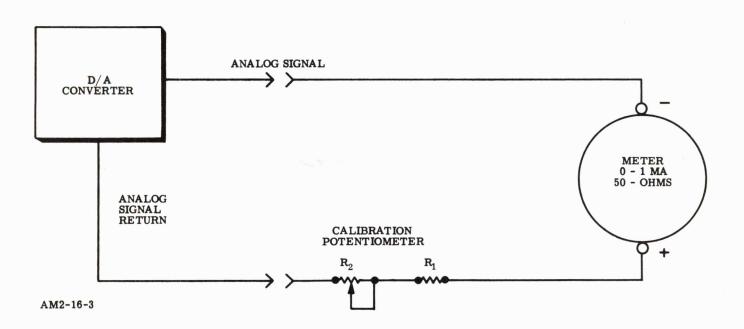

| 3-50   | Typical D/A Converter Circuit                             |       |

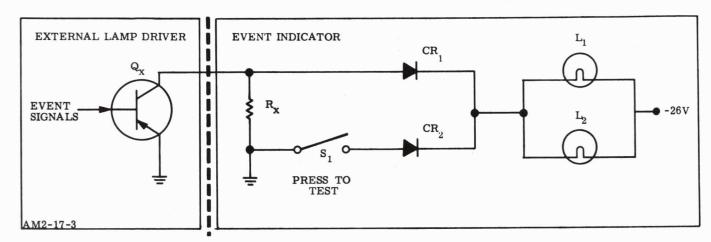

| 3-51   | Typical Lamp Driver and Indicator Circuit                 |       |

| 3-52   | Typical Meter Circuit                                     |       |

| 3-53   | Typical Event Lamp Indicator Circuit                      | 3-135 |

| 3-54   | Typical Converter Circuit                                 |       |

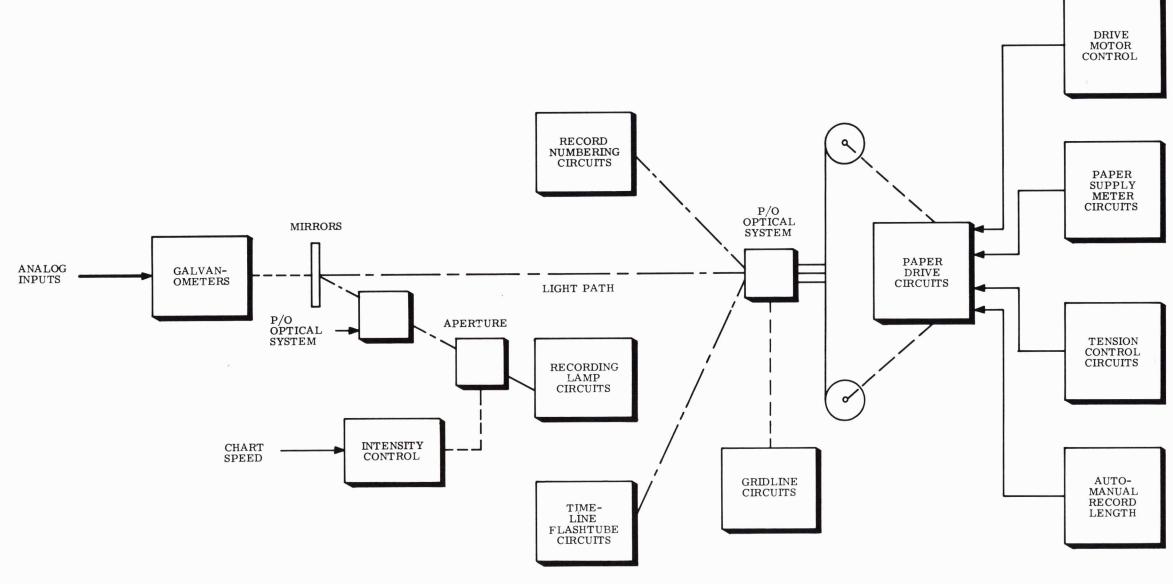

| 3-55   | Eight-Channel Analog Recorder Functional Block Diagram    | 3-138 |

| 3-56   | 32-Channel Event Recorder Functional Block Diagram        |       |

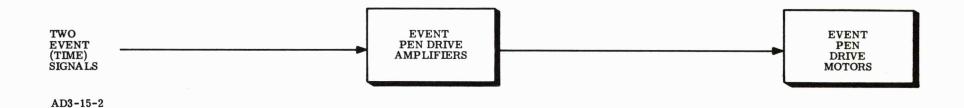

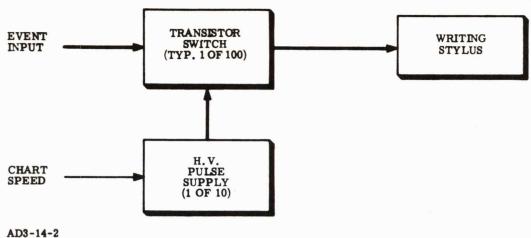

| 3-57   | 100-Channel Event Recorder Functional Block Diagram       |       |

| 3-58   | Computer Room Test Display and Recording Units Functional |       |

|        | Block Diagram                                             |       |

| 3-59   | 36-Channel Oscillographic Recorder Block Diagram          |       |

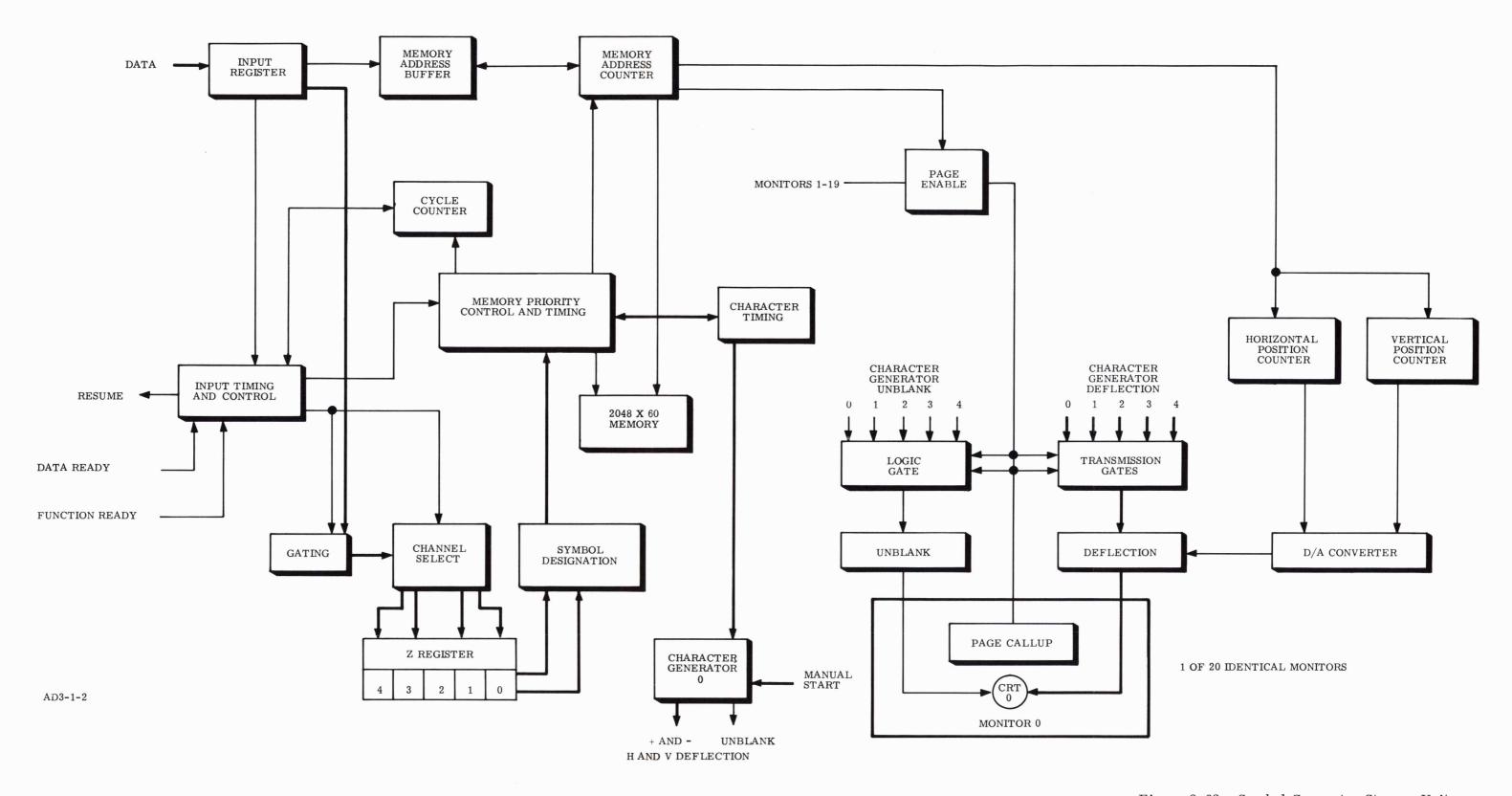

| 3-60   | Alphanumeric Display Units Functional Block Diagram       |       |

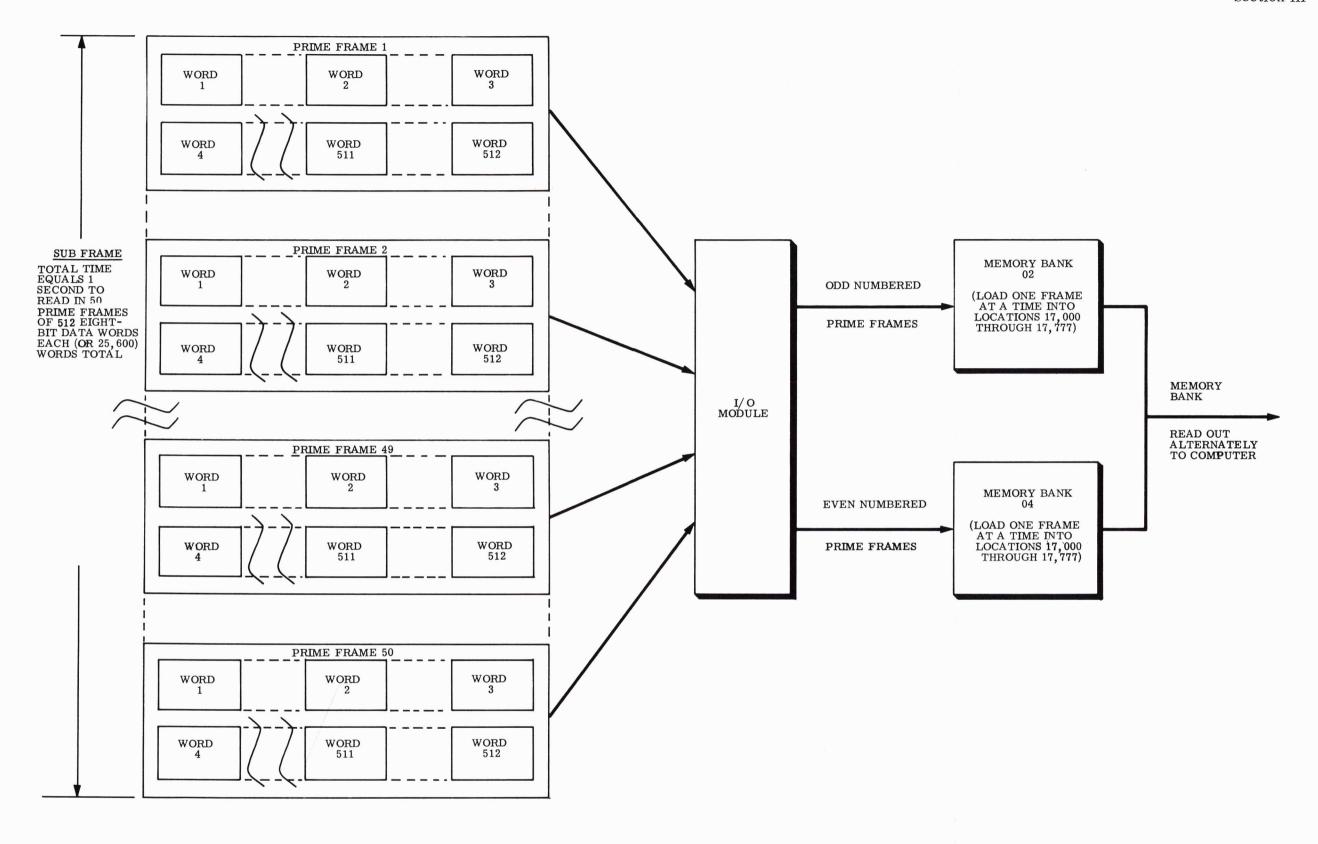

| 3-61   | PCM Data Read-In Functional Block Diagram                 |       |

| 3-62   | DTVC/DCCU Transmission Link Functional Block Diagram      |       |

| 3-63   | Symbol Generator Storage Unit Functional Block Diagram    |       |

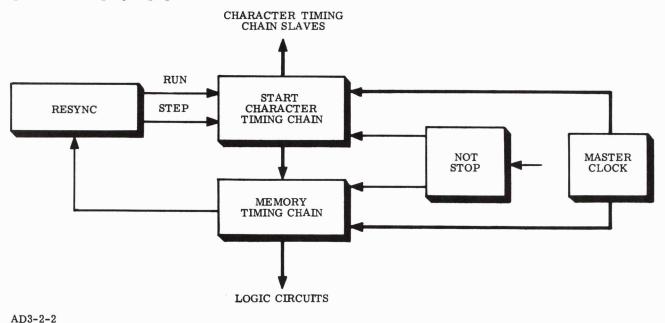

| 3-64   | Display System Timing Block Diagram                       | 3-169 |

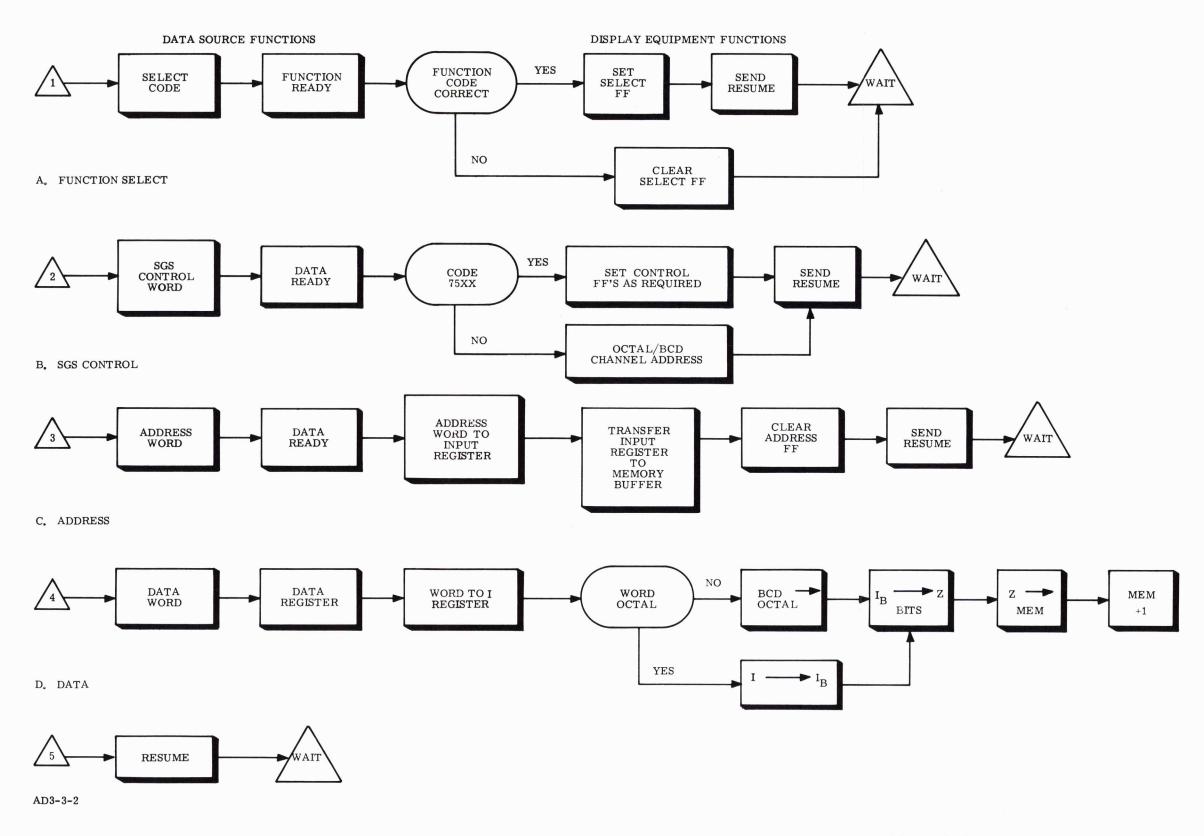

| 3-65   | Input Data Control Functions Flow Chart                   | 3-171 |

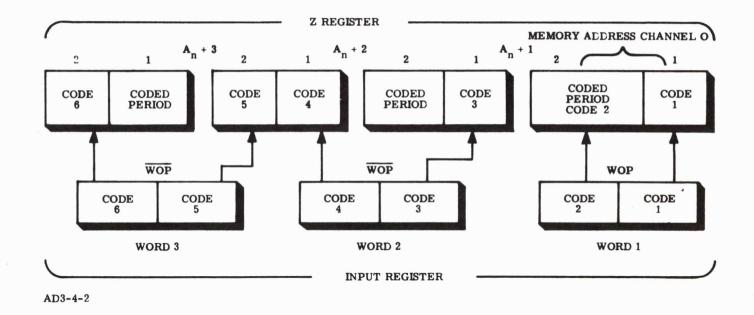

| 3-66   | Input Gating and Input To Z Control Block Diagram         |       |

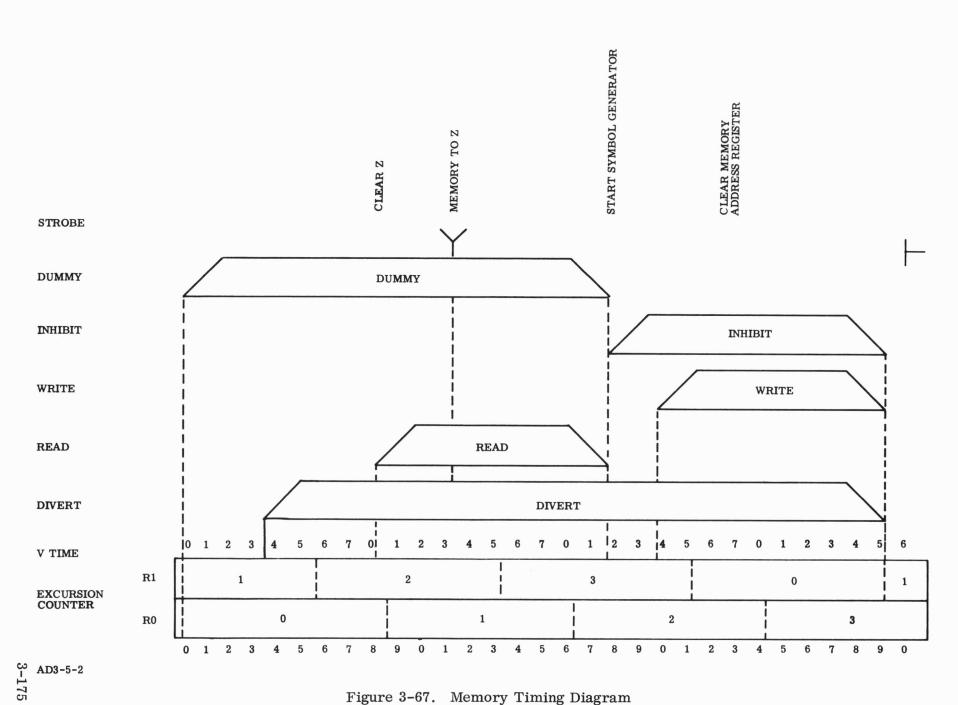

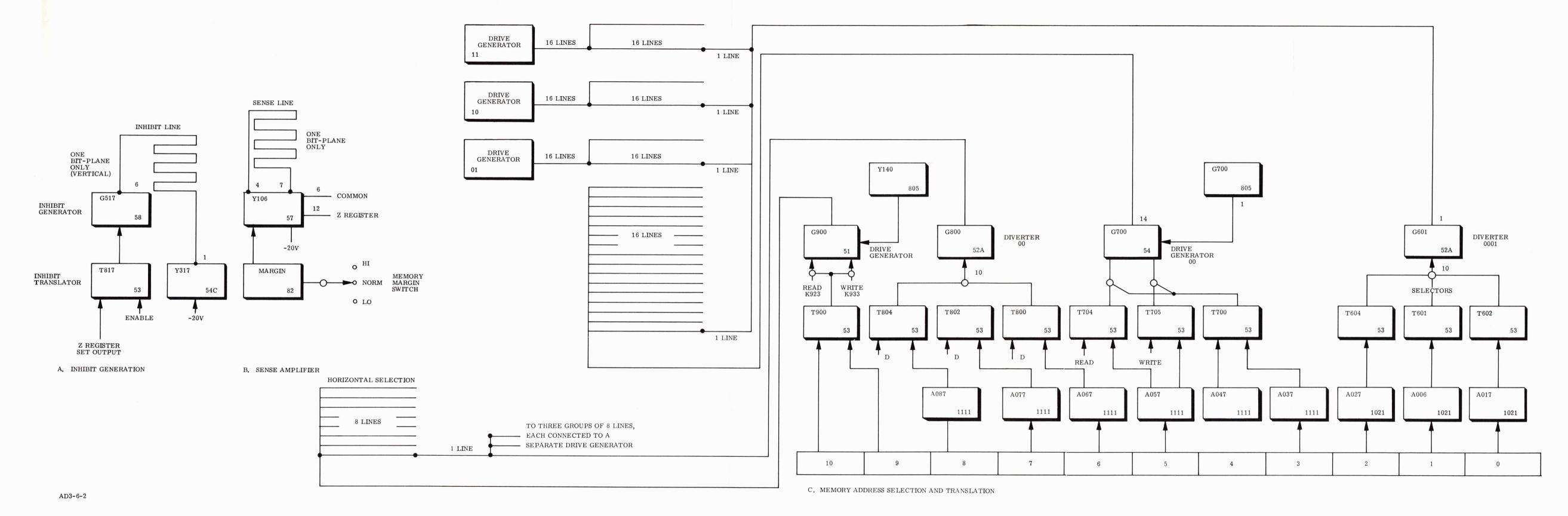

| 3-67   | Memory Timing Diagram                                     | 3-175 |

| 3-68   | Memory Section Simplified Logic Diagram                   | 3-177 |

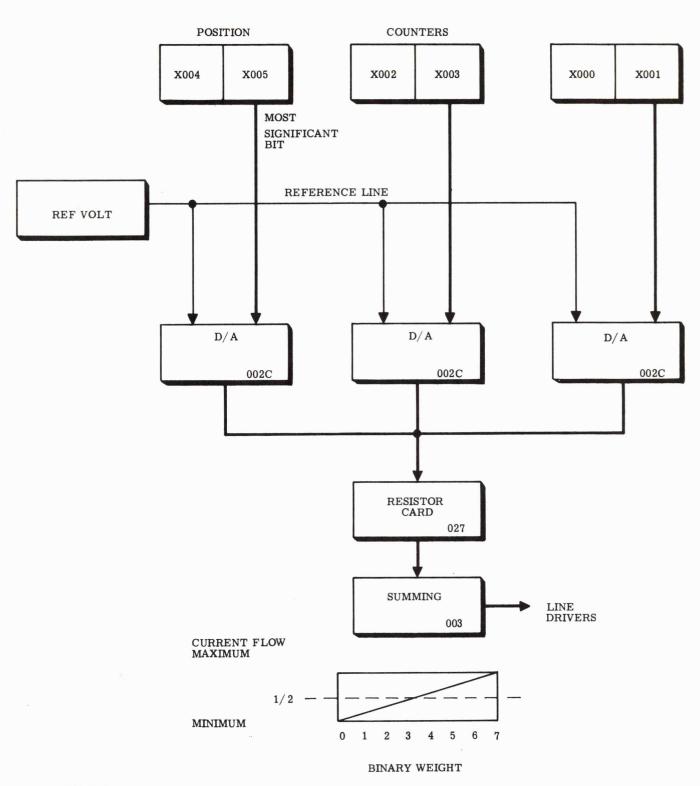

| 3-69   | Typical D/A Conversion Block Diagram                      | 3-180 |

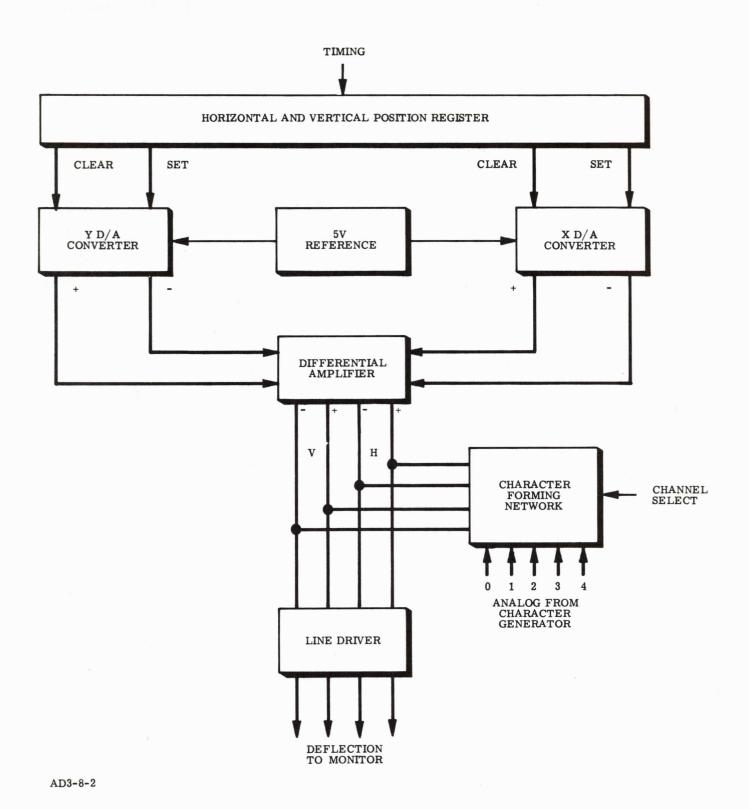

| 3-70   | SGS Deflection System Block Diagram                       |       |

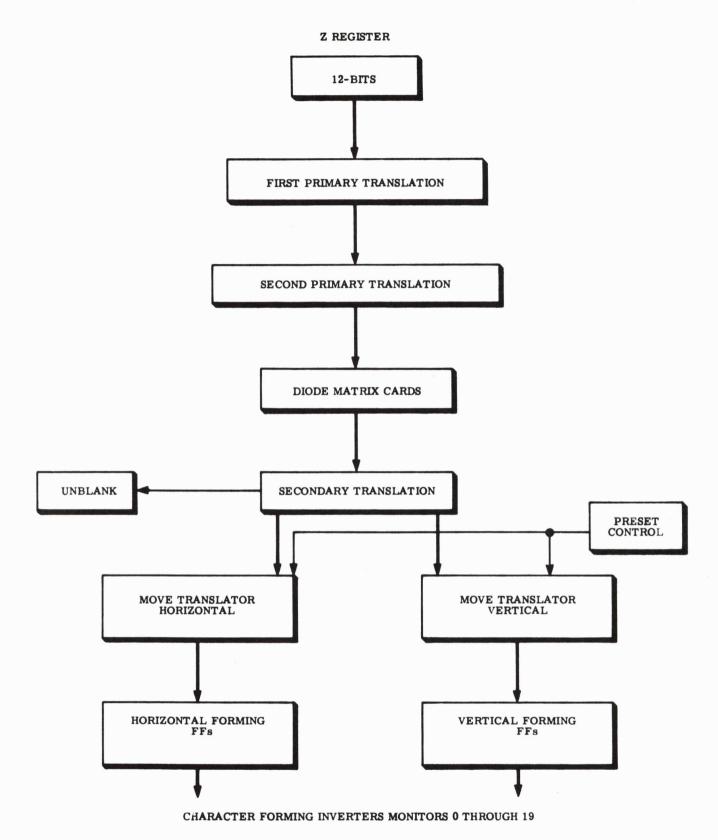

| 3-71   | Diagram of Character Generator Functions                  |       |

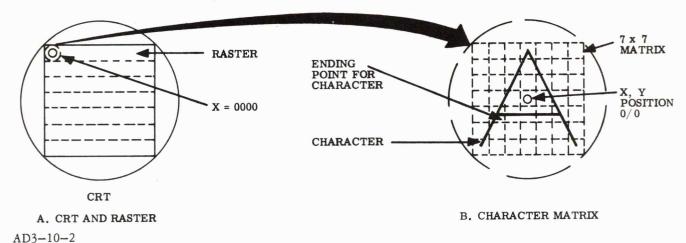

| 3-72   | Character Matrix and CRT Raster                           |       |

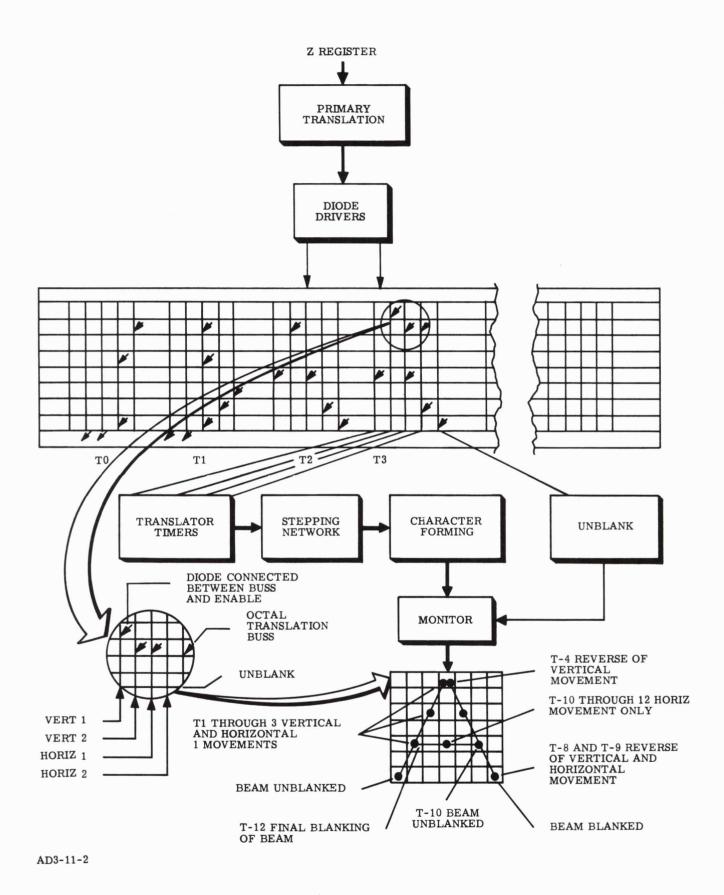

| 3-73   | Diagram of Typical Character Formation                    | 3-185 |

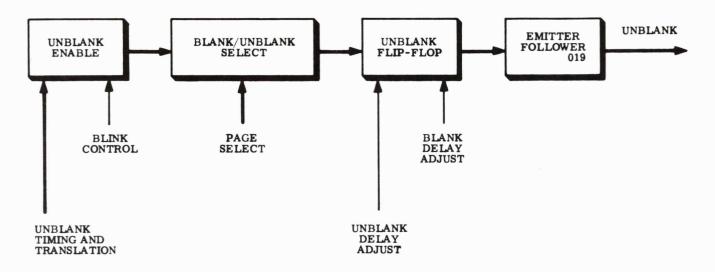

| 3-74   | SGS Unblank System Block Diagram                          |       |

| 3-75   | Monitor Functional Block Diagram                          | 3-188 |

# LIST OF ILLUSTRATIONS (Cont'd)

| Figure |                                                               | Page |

|--------|---------------------------------------------------------------|------|

|        | SECTION IV. SUPPORT EQUIPMENT                                 |      |

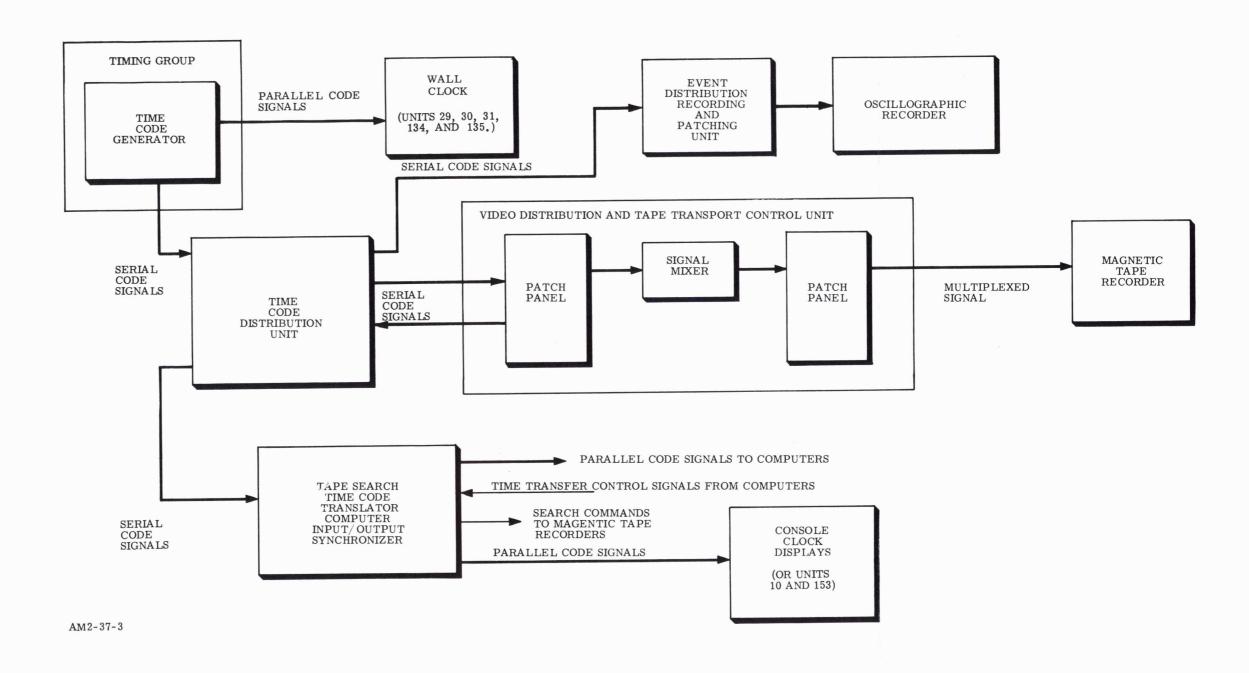

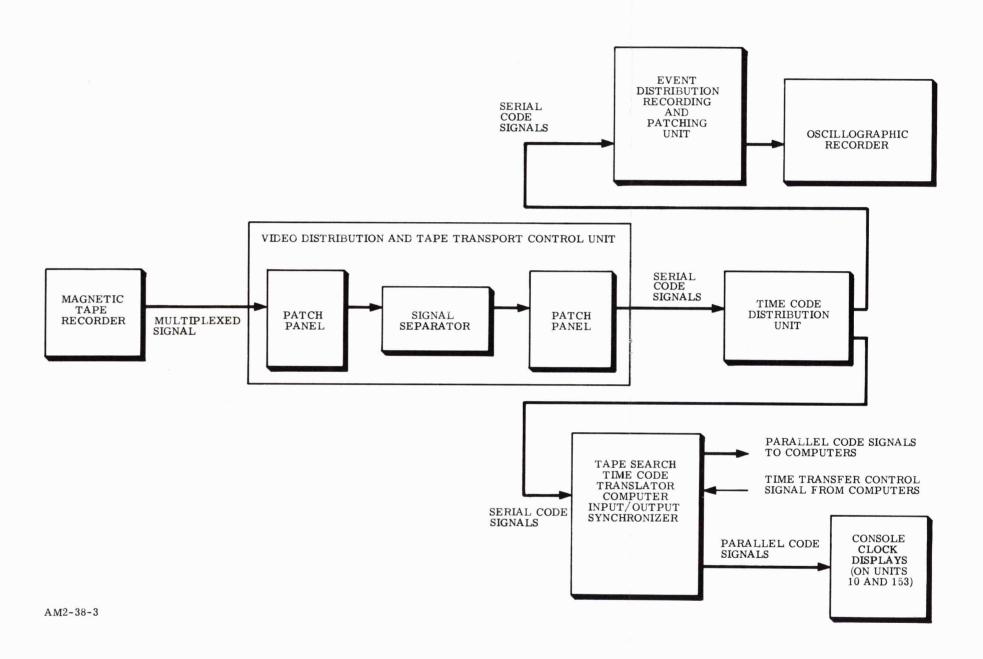

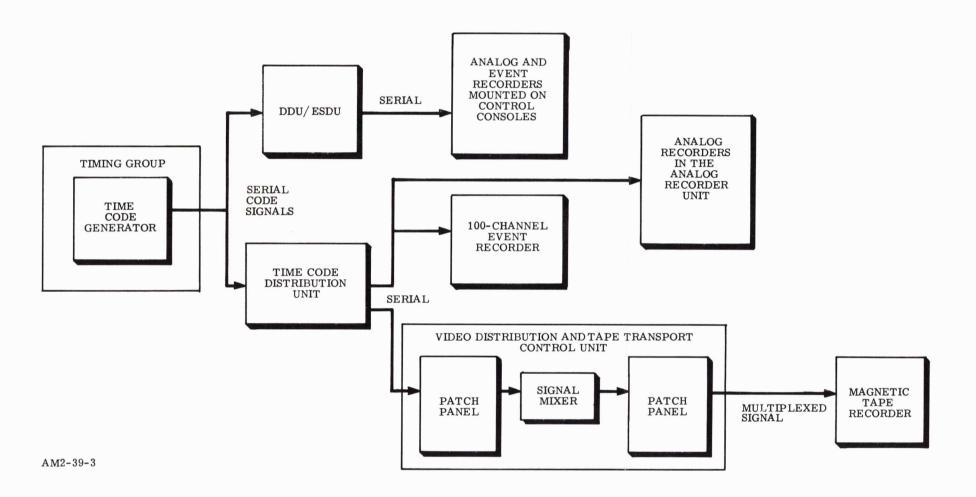

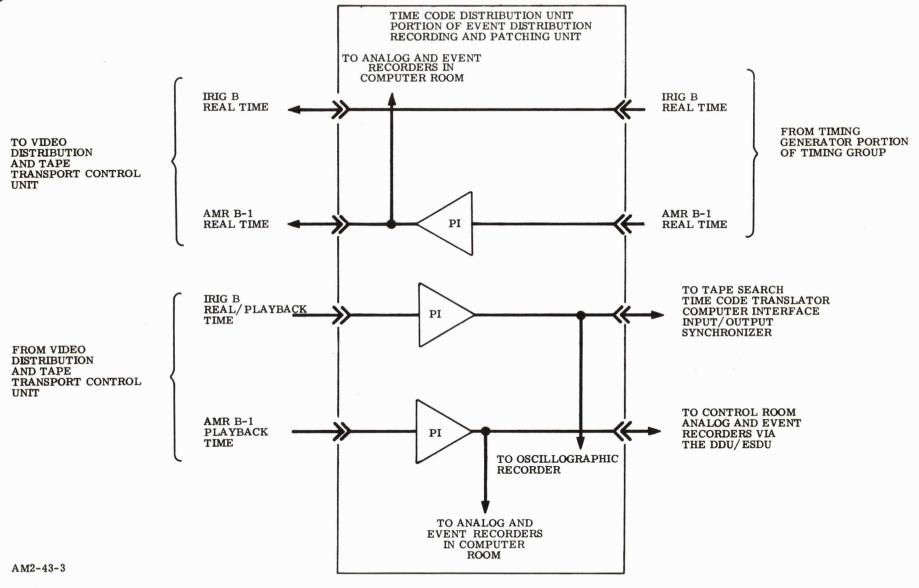

| 4-1    | IRIG B Real Time Distribution Block Diagram                   | 4-5  |

| 4-2    | IRIG B Playback Time Distribution Block Diagram               |      |

| 4-3    | AMR B-1 Real Time Distribution Block Diagram                  |      |

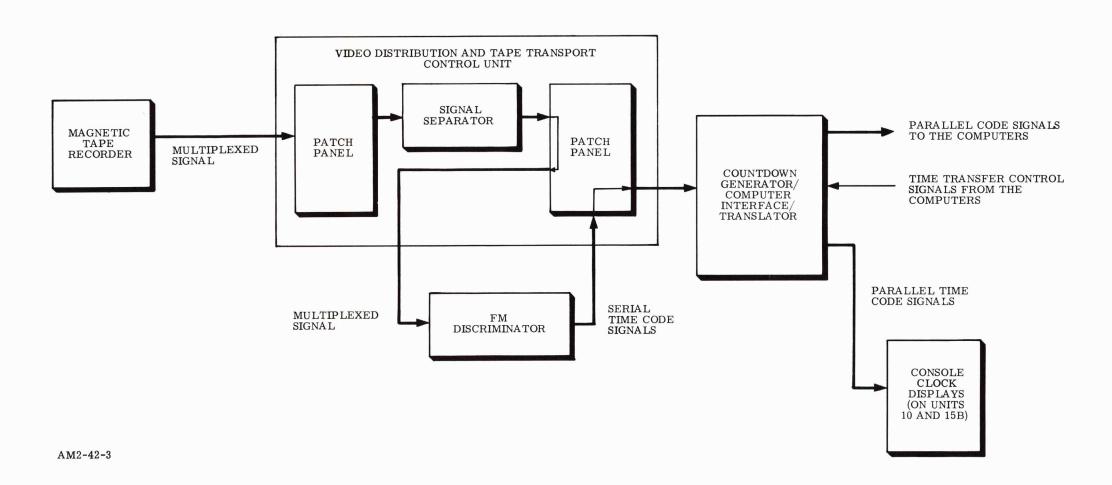

| 4-4    | AMR B-1 Playback Time Distribution Block Diagram              |      |

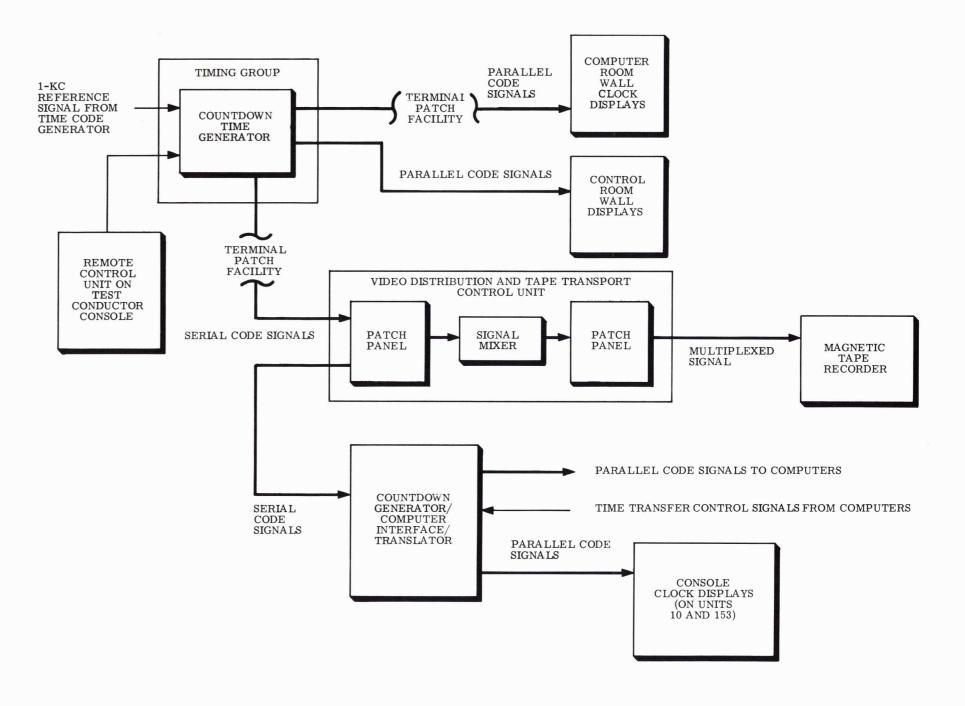

| 4-5    | Countdown Time Distribution Block Diagram                     |      |

| 4-6    | Playback Countdown Time Distribution Block Diagram            |      |

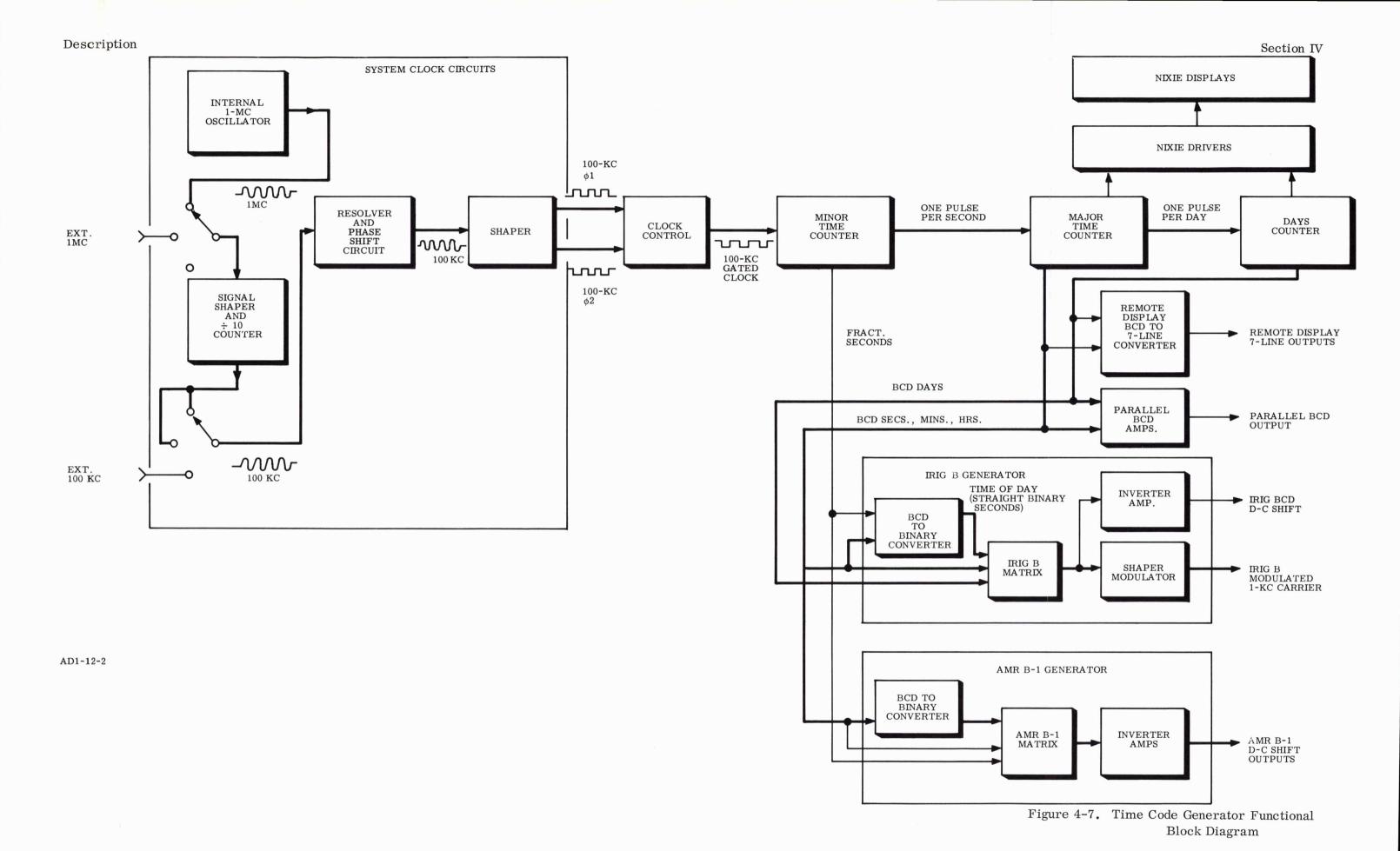

| 4-7    | Time Code Generator Functional Block Diagram                  | 4-19 |

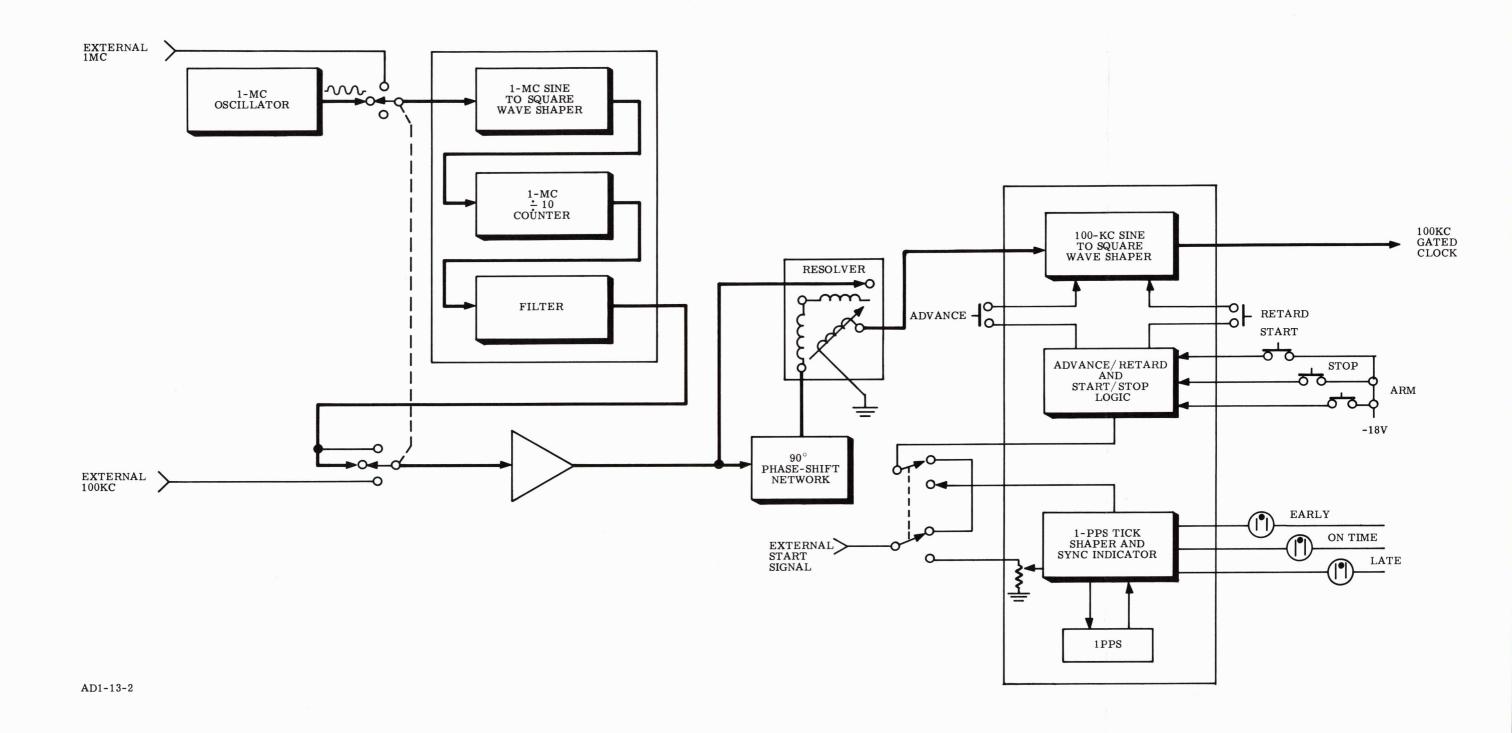

| 4-8    | System Clock Circuits Functional Block Diagram                | 4-23 |

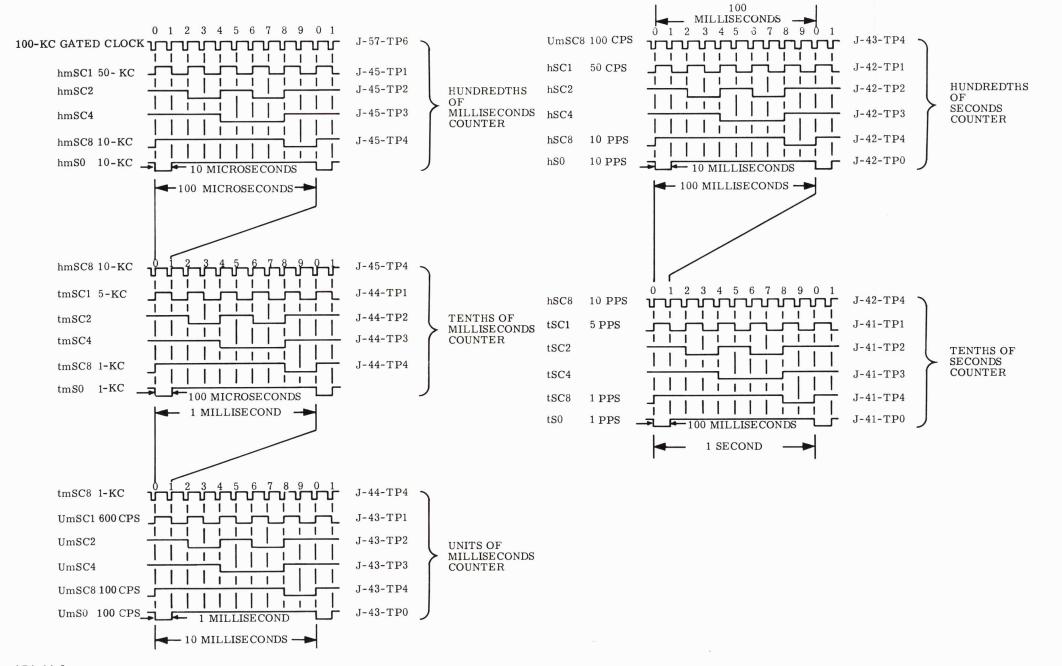

| 4-9    | Major and Minor Counter Timing Diagram                        | 4-27 |

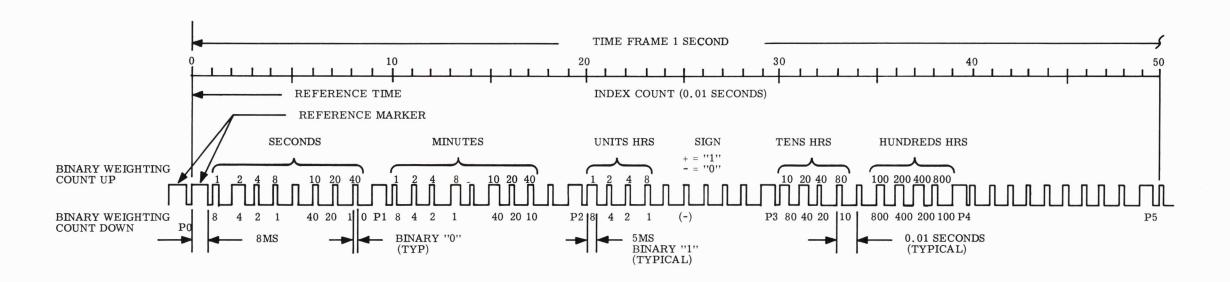

| 4-10   | IRIG B Time Code Format                                       | 4-31 |

| 4-11   | Display Converter Coding                                      | 4-37 |

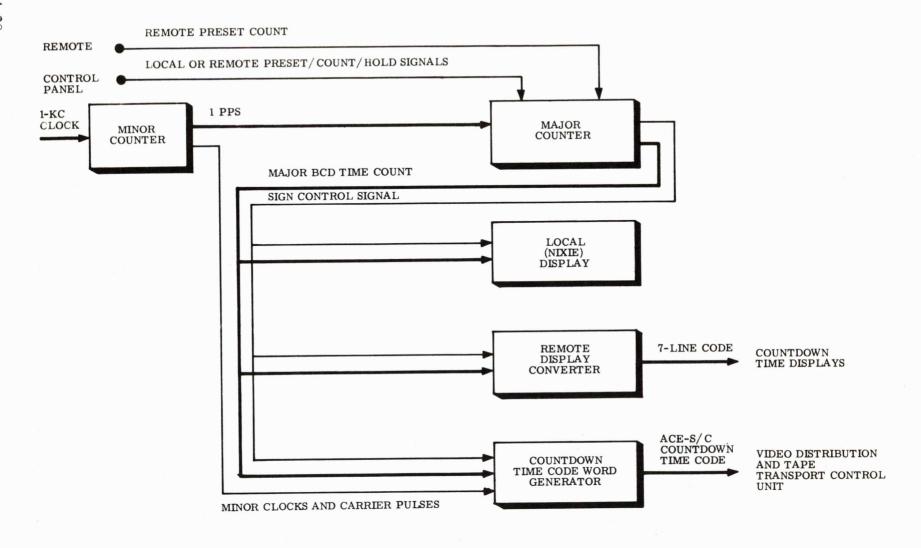

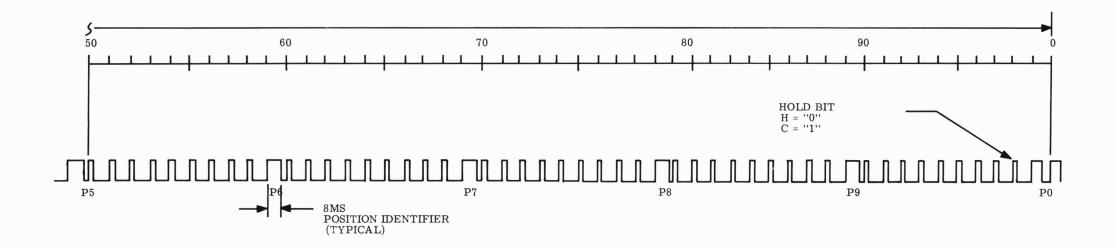

| 4-12   | Countdown Time Code Generator Simplified Block Diagram        | 4-38 |

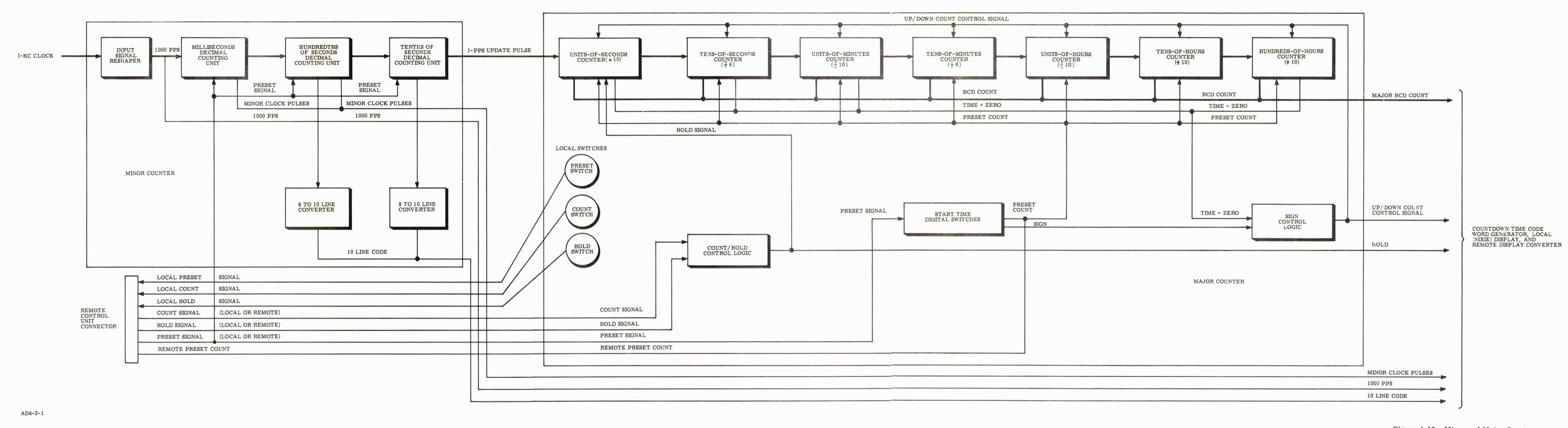

| 4-13   | Minor and Major Counters Block Diagram                        |      |

| 4-14   | ACE-S/C Countdown Time Code Format                            | 4-43 |

| 4-15   | Word Generator and Local and Remote Display Circuit           |      |

|        | Block Diagram                                                 | 4-45 |

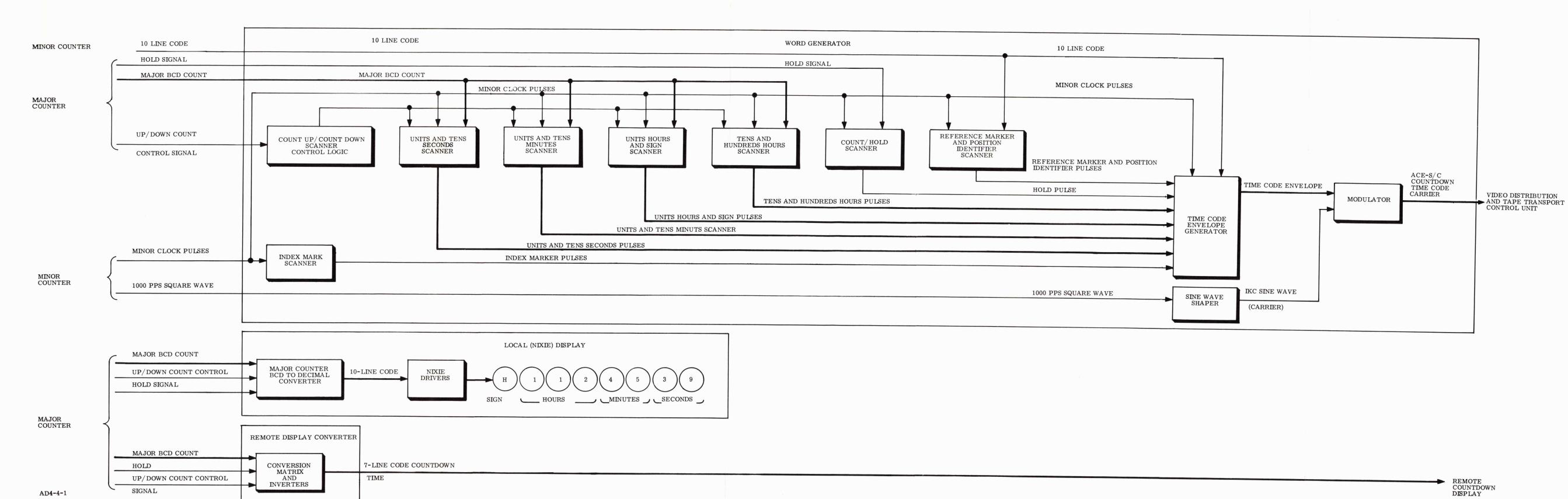

| 4-16   | Tape Search and Time Code Translator Simplified Block Diagram | 4-52 |

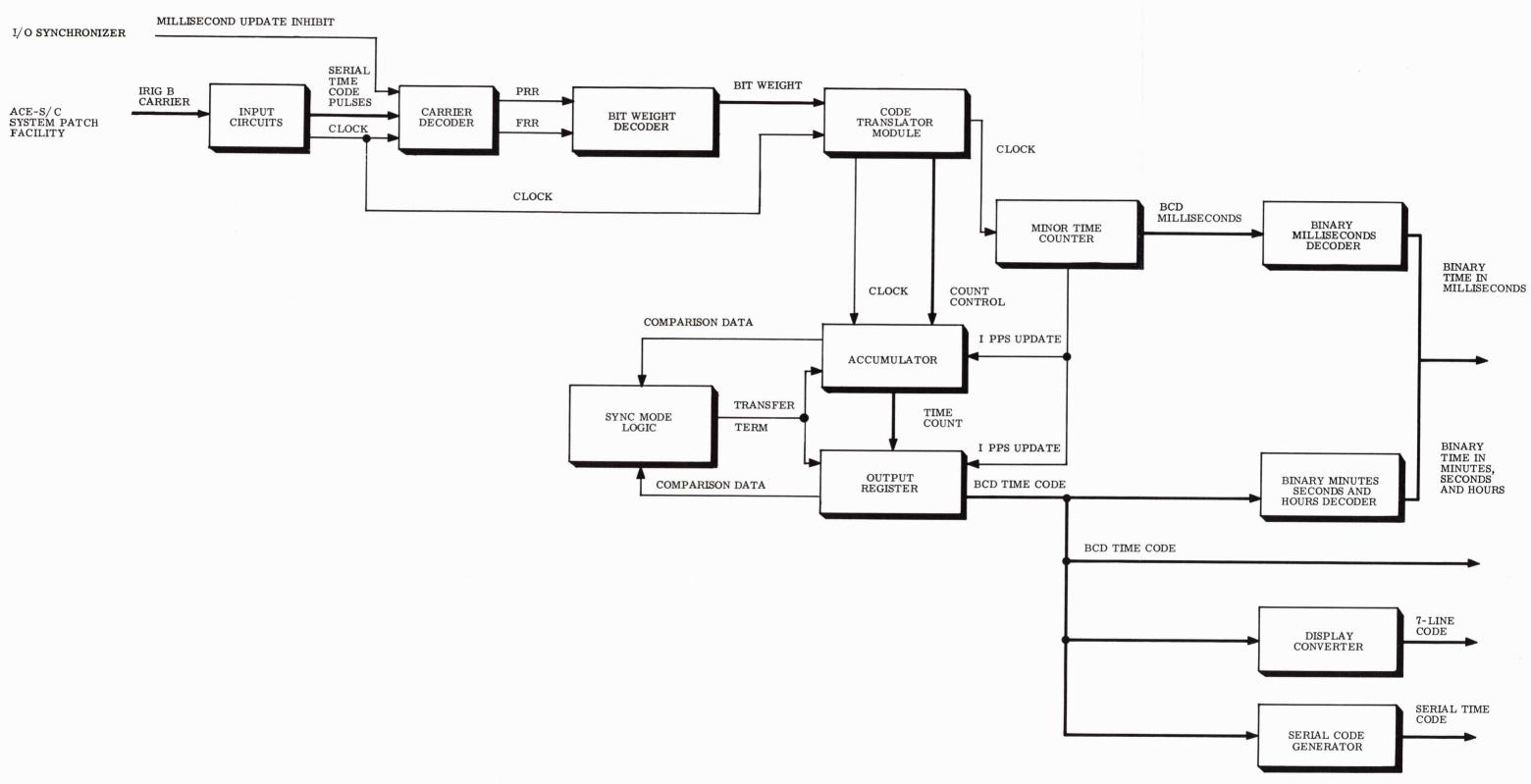

| 4-17   | Time Code Translator Functional Block Diagram                 |      |

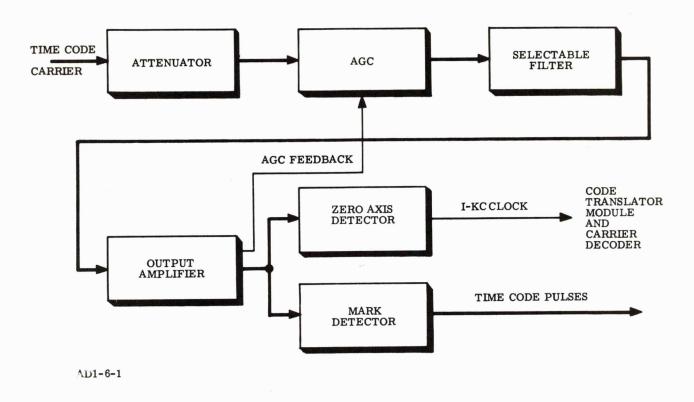

| 4-18   | Input Circuits Functional Block Diagram                       |      |

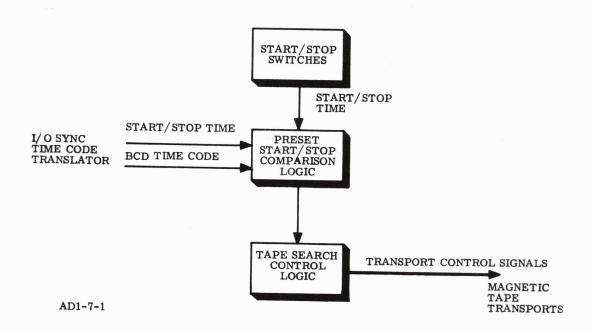

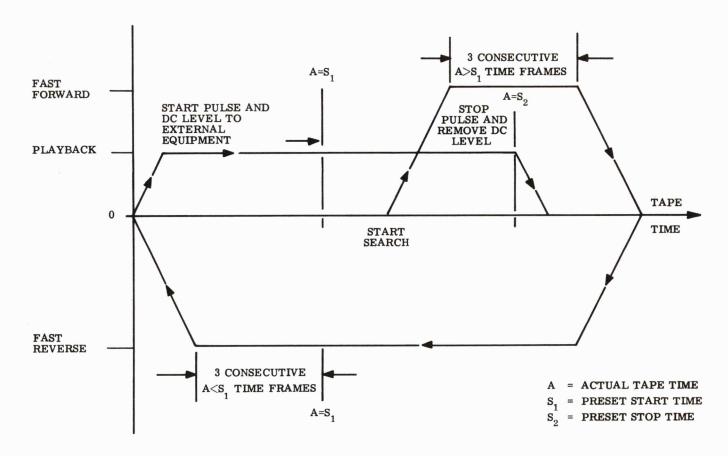

| 4-19   | Tape Search Control Functional Block Diagram                  |      |

| 4-20   | Tape Search Sequence                                          |      |

| 4-21   | Input/Output Synchronizer Block Diagram                       | 4-65 |

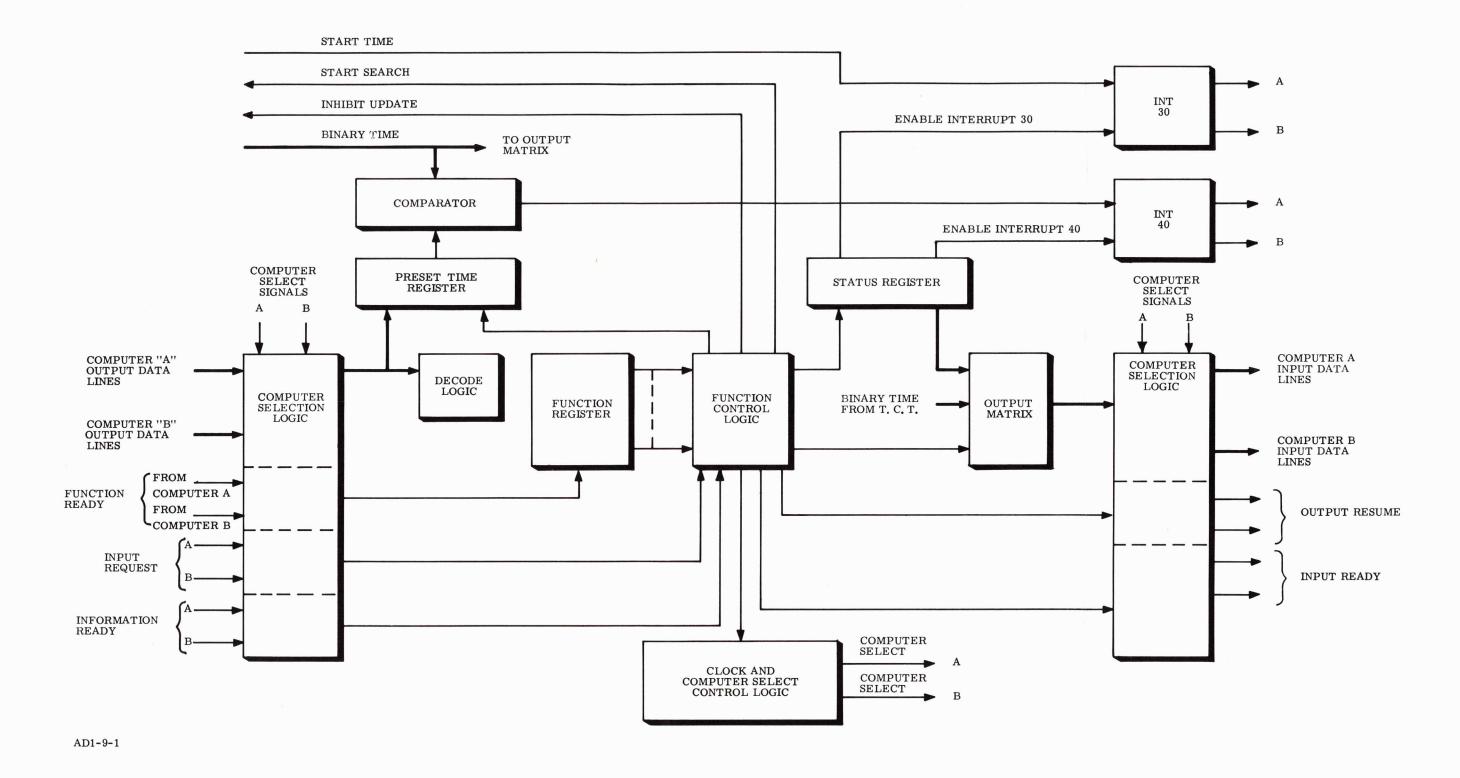

| 4-22   | Range Time Word Formats                                       | 4-67 |

| 4-23   | Time Code Distribution Unit Functional Block Diagram          |      |

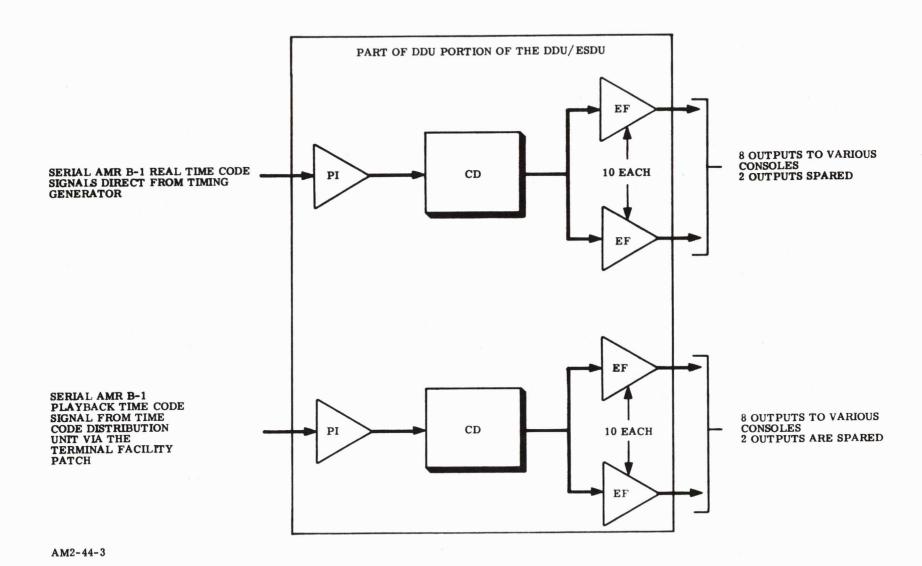

| 4-24   | Distribution of AMR B-1 Time Codes by the DDU                 |      |

| 4-25   | Remote Time Display Indicator Mask Formats                    |      |

| 4-26   | Display Converter Coding                                      |      |

| 4-27   | Status Control and Monitoring System Functional Block Diagram | 4-85 |

### LIST OF TABLES

| Table      |                                                        | Page    |

|------------|--------------------------------------------------------|---------|

|            | SECTION I. GENERAL DESCRIPTION                         |         |

| 1-1        | Quick Reference Table of Major Unit Functions          | . 1–17  |

|            | SECTION II. COMMAND EQUIPMENT                          |         |

| 2-1<br>2-2 | External Function Instructions                         |         |

|            | SECTION III. DISPLAY AND RECORDING EQUIPMENT           |         |

| 3-1        | FM Channel Frequency Assignments                       | . 3-6   |

| 3-2        | Decommutator to Computer Information Transfer Sequence | . 3-64  |

| 3-3        | Computer to Decommutator Information Transfer Sequence |         |

| 3-4        | Decommutator Status Word Bit Weight and Assignment     |         |

| 3-5        | Computer Function Control Words to Decommutator Units  |         |

| 3-6        | Steps in Forming Truncated Characters                  |         |

| 3-7        | Event Distribution                                     | . 3-109 |

| 3-8        | Control Console Component Complement                   | . 3-125 |

| 3-9        | Display Computer Output Word Content                   | . 3-156 |

| 3-10       | External Function Codes Received by DCCU               |         |

| 3-11       | DCCU Status Reply Code                                 | . 3-163 |

#### INTRODUCTION

This manual provides a complete functional and physical description of Acceptance Checkout Equipment - Spacecraft (ACE-S/C) Ground Station No. 1, installed at North American Aviation Company (NAA), Downey, California. The manual is divided into four sections:

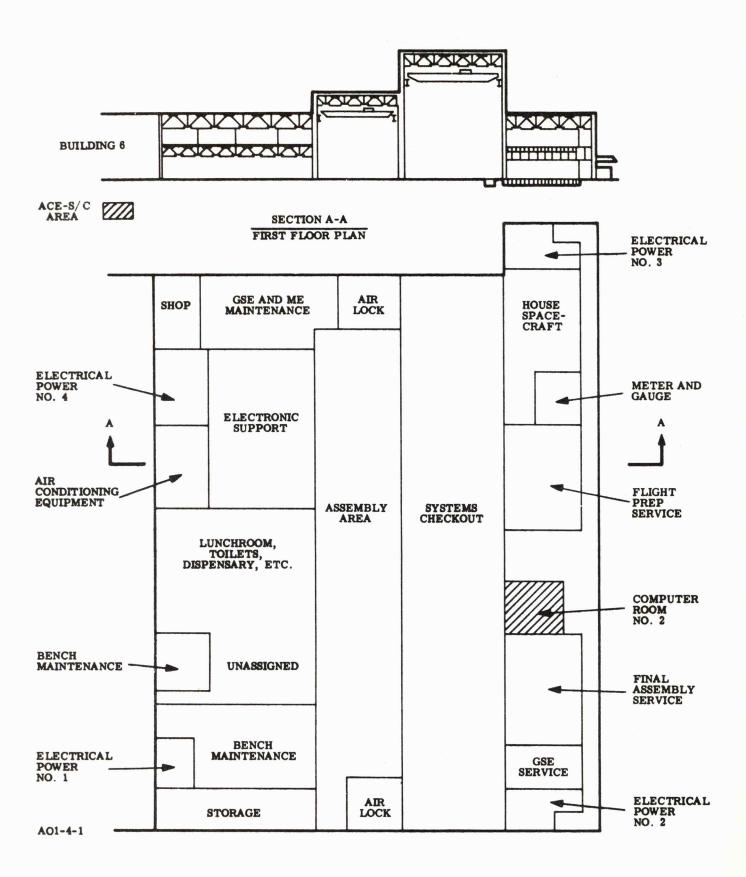

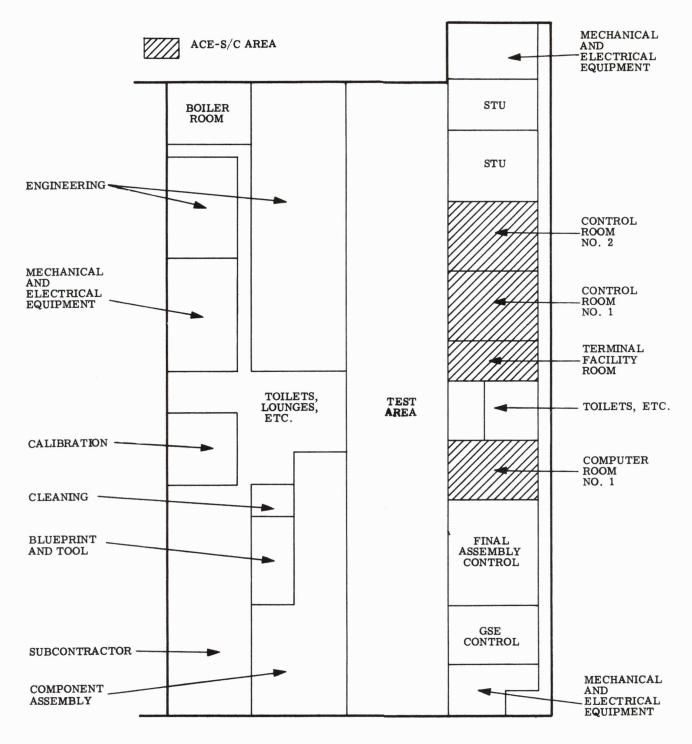

Section I - General Description - This section contains a general functional description of the entire ground station, indicating equipment/station and station/facility relationships. In addition, a detailed physical description of the ACE-S/C installation at NAA is provided to show equipment location and site layout.

Section II - Command Equipment - This section contains a detailed functional description of the Command Equipment portion of the ground station.

Section III - Recording and Display Equipment - This section provides a detailed functional description of the Recording and Display Equipment portion of the ground station.

Section IV - Support Equipment - The Support Equipment category includes units that are not a direct part of the major system functions but are necessary for spacecraft test operations.

#### SECTION I

#### GENERAL DESCRIPTION

#### PART 1

#### FUNCTIONAL DESCRIPTION

#### 1-1. ACCEPTANCE CHECKOUT EQUIPMENT - SPACECRAFT SYSTEM DESCRIPTION.

- 1-2. The Acceptance Checkout Equipment Spacecraft (ACE-S/C) is an advanced, integrated checkout system that provides centralized, programmed control of spacecraft checkout operations. Both independent spacecraft systems testing and integrated system testing are possible. Large quantities of test data can be processed and displayed in real-time, as well as recorded for later analysis, with a relatively small staff of engineering personnel.

- 1-3. Specifically, the ACE-S/C station performs the following functions:

- a. Provides the operator controls and data processing facilities necessary to control spacecraft test stimuli equipment.

- b. Receives, processes, displays, and records spacecraft parameter data derived from the spacecraft ground and flight telemetry systems.

- c. Provides self-check and calibration capability for itself and related equipment.

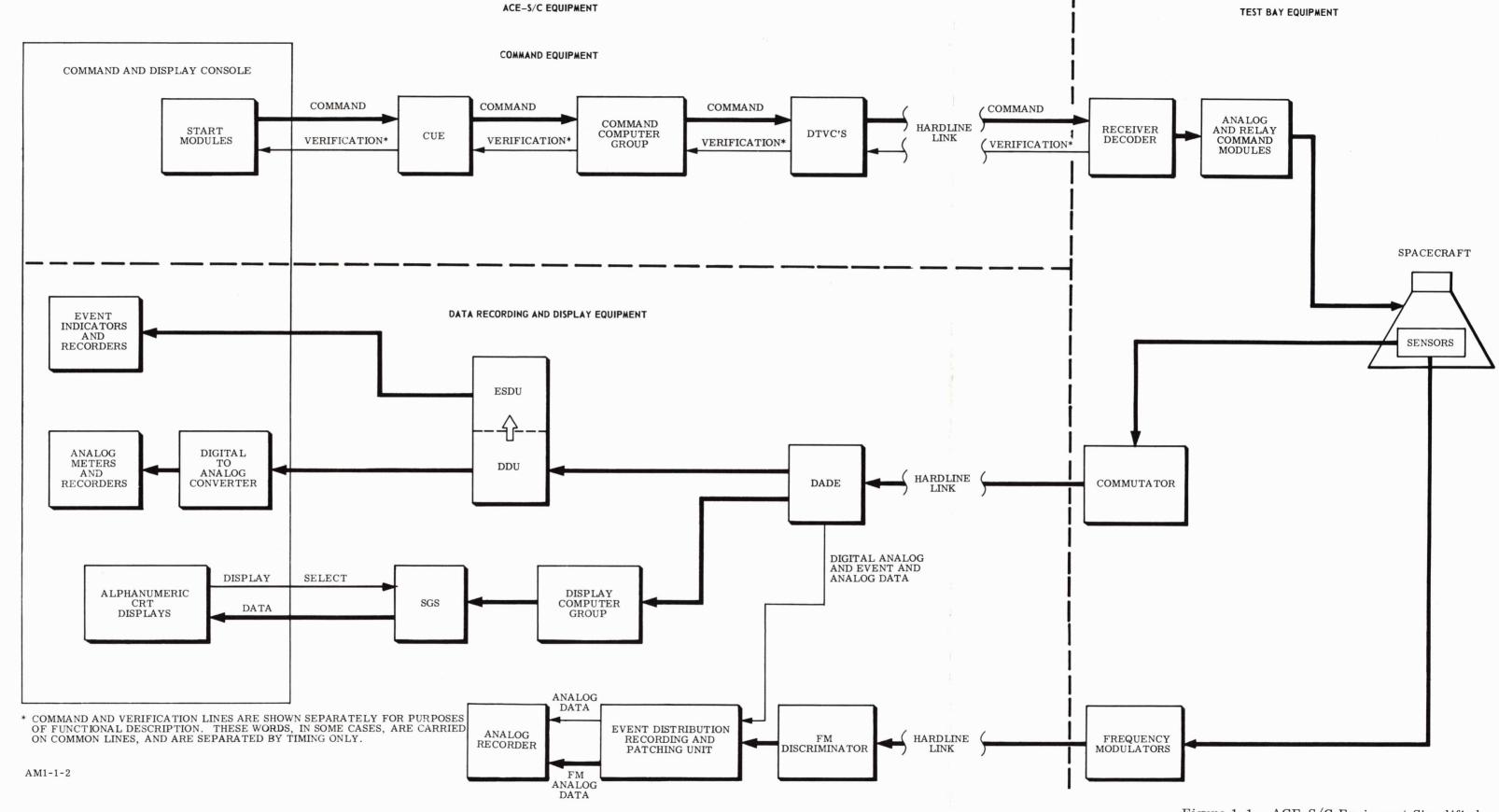

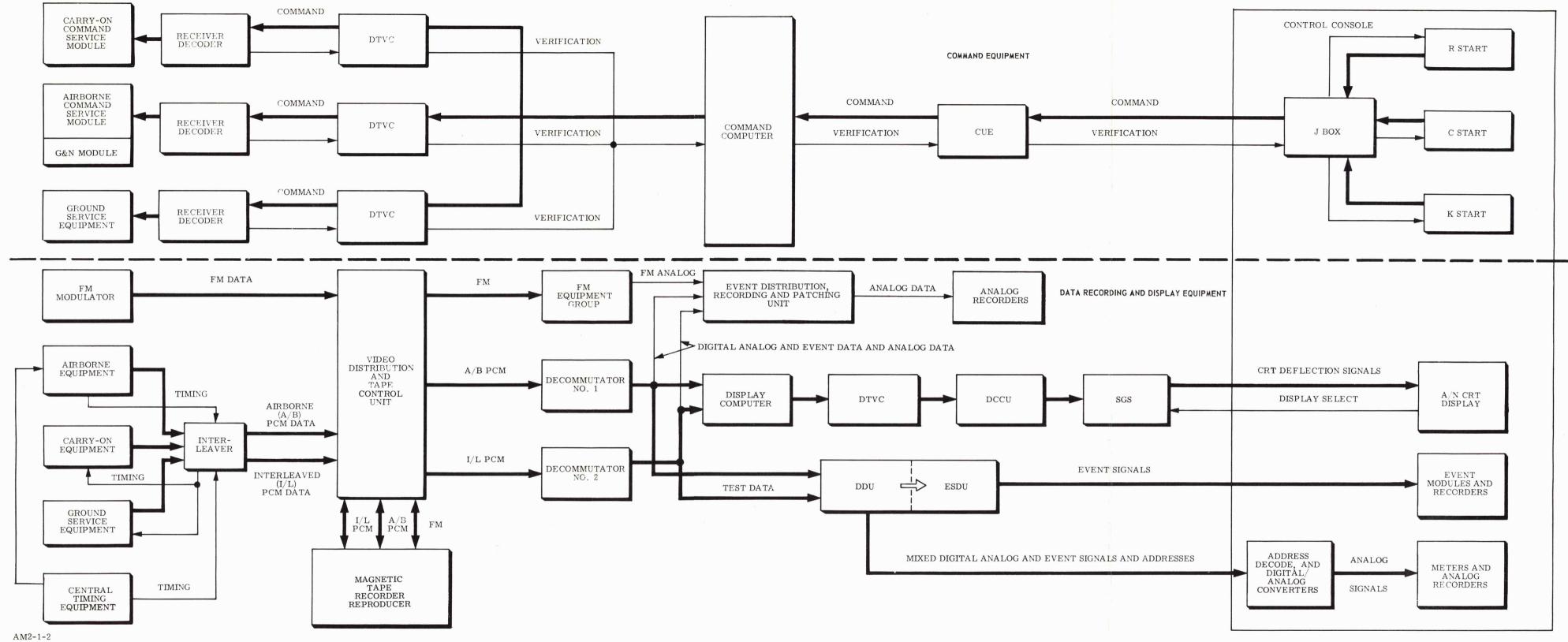

- 1-4. The ground station may be divided into two functional data-chain groupings: the Command Equipment and the Data Recording and Display Equipment. (see figure 1-1.) The Command Equipment is comprised of those units that form the communication path over which all test commands and sequences (in digital word form) are generated and transmitted to the spacecraft. Verification of receipt of these commands is transmitted from the spacecraft test area, back through the command system, to the ACE-S/C station. Test result data from the spacecraft test area is received (again in digital word form) by the Data Recording and Display Equipment which presents these data for evaluation.

- 1-5. COMMAND EQUIPMENT.

- 1-6. Test commands are initiated at various system control consoles by setting switches on units called Selection-To-Activate-Random-Testing (START) modules. The setting of these

switches provides digital command inputs to the command computer. These commands vary from individual event functions (specific relay on-off actions) to the callup of computer subroutines that control sequences of events and/or various analog operations in the spacecraft.

- 1-7. The testing of each functional spacecraft system is controlled from an associated system control console. The following functional systems are tested:

- a. Environmental Control System.

- b. Fuel Cell and Cryogenics.

- c. Power and Sequential System.

- d. Guidance and Navigation System.

- e. Stabilization and Control.

- f. Service Propulsion and Reaction Control System.

- g. Instrumentation.

- h. Communications.

- 1-8. Each system control console operates simultaneously with, and independently of, the other system consoles. Each has a wide variety of test command capability necessary for complete checkout of a particular spacecraft system. In order that the command computer may systematically process each of the many parallel inputs from these consoles, a unit called the Communications Unit Executor (CUE), operating essentially as a commutator, interrogates each START module on all of the system control consoles in sequence. These interrogations occur at a high rate. Therefore, to the individual console operators, there is no perceptible delay in their individual test procedures. When an interrogation determines that a command input exists at a particular START module, the scanning process ceases momentarily while the CUE transfers the digital command to the command computer.

- 1-9. The computer interprets and acts upon the command under program control. Some commands instruct the computer to modify memory while others require some action to occur in the spacecraft. In the latter case, the computer formulates a digital command message for transmission to the spacecraft. The digital command message, which is generated by the computer in a parallel format, is converted into a serial bit stream by a Data Transmission and Verification Converter (DTVC) and transmitted to the spacecraft over a hardline link.

- 1-10. At the spacecraft location, the message is received and stored in registers in a Receiver-Decoder unit. The message is then decoded and applied to analog and relay command modules where the proper stimulus is generated and transmitted to the spacecraft.

- 1-11. Verification of the command message is accomplished by redundant transmission from the DTVC to the Receiver-Decoder. A bit-by-bit comparison is made of the redundant words. In addition, checks are made of each message to determine whether it contains a legal address.

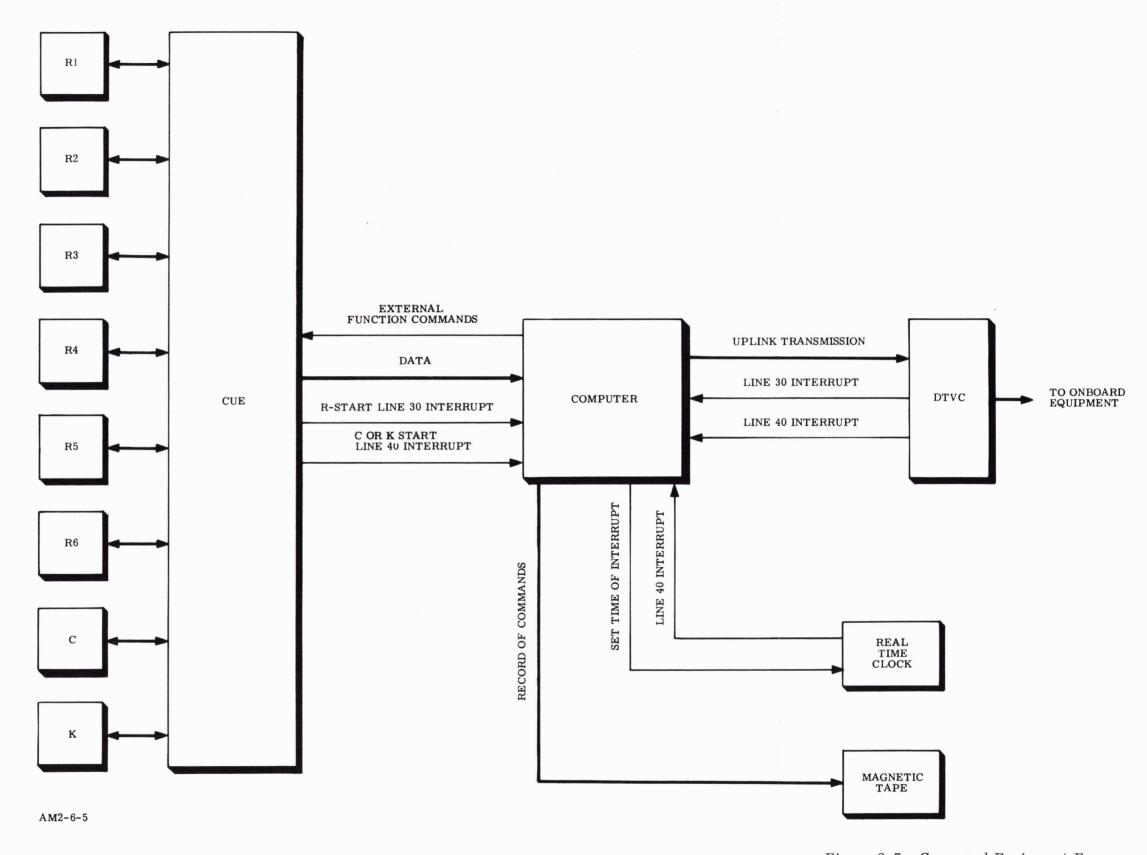

Figure 1-1. ACE-S/C Equipment Simplified Block Diagram

A verification reply message, containing the results of the foregoing checks, is transmitted from the Receiver-Decoder back to the DTVC. The delivery of a command message to the command computer and the verification of proper transmission from the computer to the spacecraft are indicated to the control console operator by appropriate lamps on the START modules.

#### 1-12. DATA RECORDING AND DISPLAY EQUIPMENT.

- 1-13. Spacecraft performance and status data are monitored by sensors coupled to airborne checkout equipment, carry-on ground checkout equipment, and ground service equipment. Most of the measurements are commutated, converted to digital format, interleaved, and transmitted in serial pulse-code-modulated (PCM) form over a hardline link to the data acquisition equipment in the ACE-S/C station. A small portion of the data is frequency-modulated (FM) and transmitted over a separate hardline link.

- 1-14. At the ACE-S/C station, these data are received by the data acquisition equipment. The Digital Acquisition and Decommutation System (DADS) synchronizes on the incoming serial PCM bit stream, decommutates the data, provides an address for each event and analog data word, and presents these words for parallel transmission. The FM data are recorded directly on wideband magnetic tape and an oscillographic recorder. The analog and event words, derived from the PCM data, follow three paths when they leave the decommutator.

- 1-15. One path (addresses are not included) goes to the display computer where selected portions of the data are processed. This processing includes comparison of analog data with predetermined limits, and the conversion of these data into engineering units. A binary word representing the value of the data in engineering units is transferred into a memory in a Symbol Generator and Storage (SGS) unit. The SGS uses these words to generate alphanumeric character display signals (analog) for application to control console CRT displays. These alphanumeric characters appear in "page" form on the console displays. The particular page of data to be displayed at any console is selectable by the operator of that console. When a parameter has been determined by the computer to be out of limits, the intensity of the character representing that parameter will be caused to fluctuate at a low rate (i.e., the character will appear to blink).

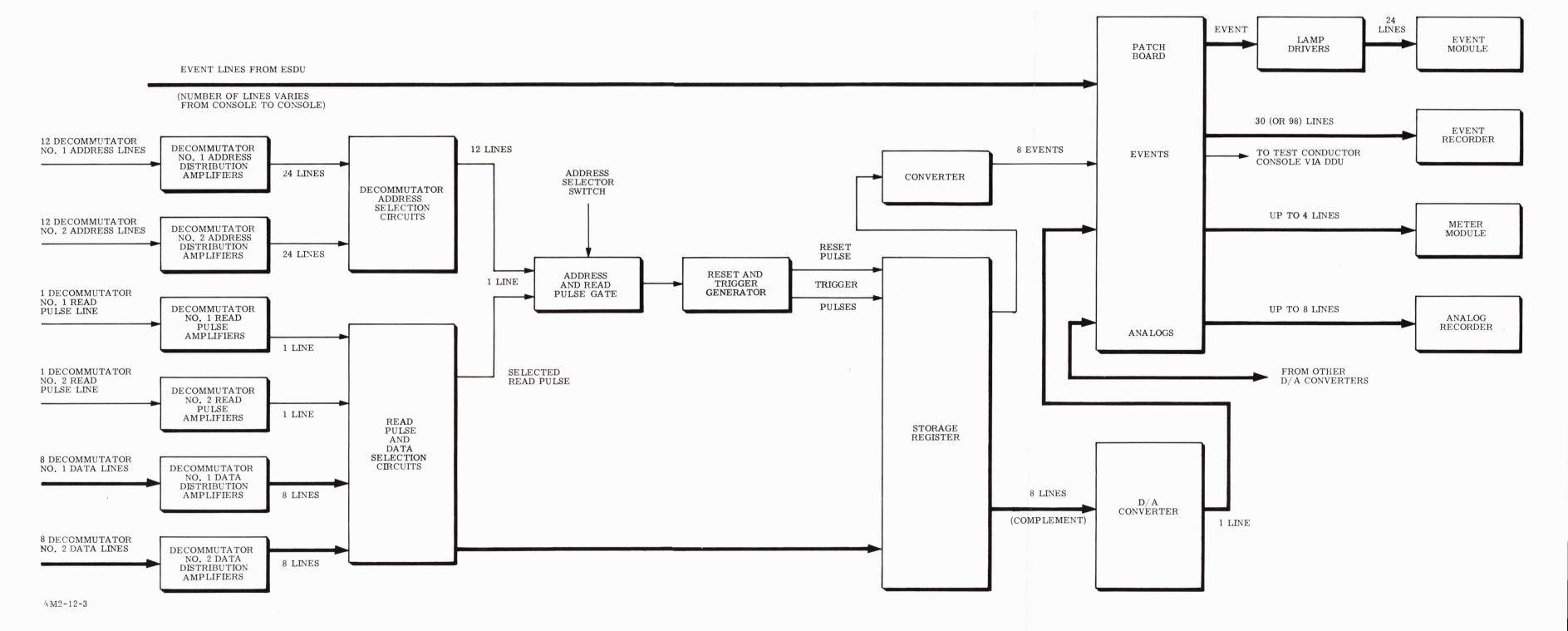

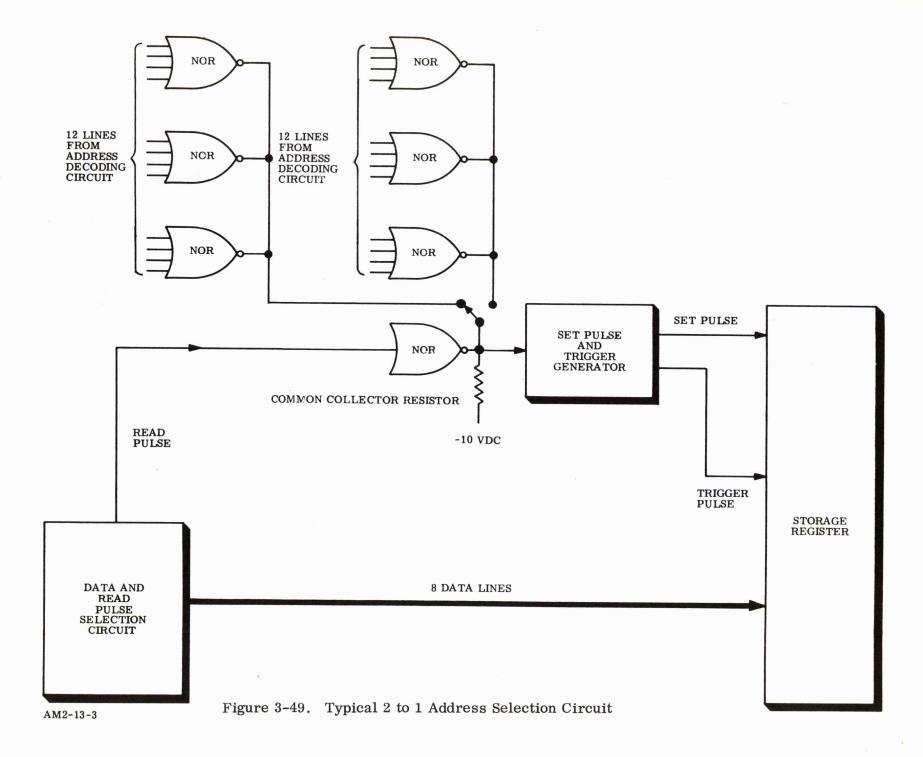

- 1-16. The second data path transfers the digital data to the Decommutator Distribution/

Event Storage and Distribution Unit (DD/ESDU). This unit accepts the data words, and, in

the case of event data, stores each bit (representing an event) in an appropriate location in

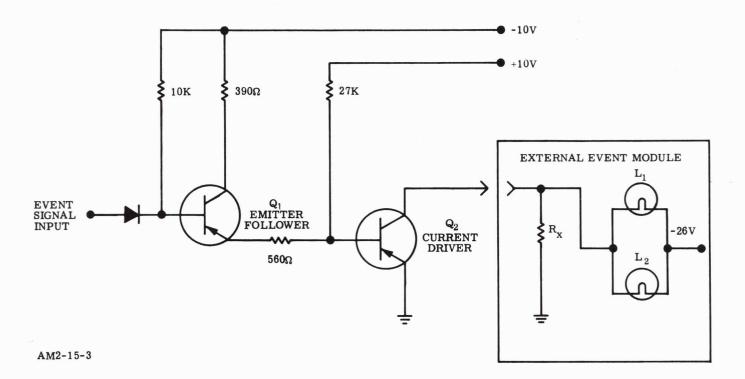

storage registers. The outputs of the storage registers, connected to indicator lamps and/or

event recorders on the control consoles, cause the event lamps and recorders to indicate when

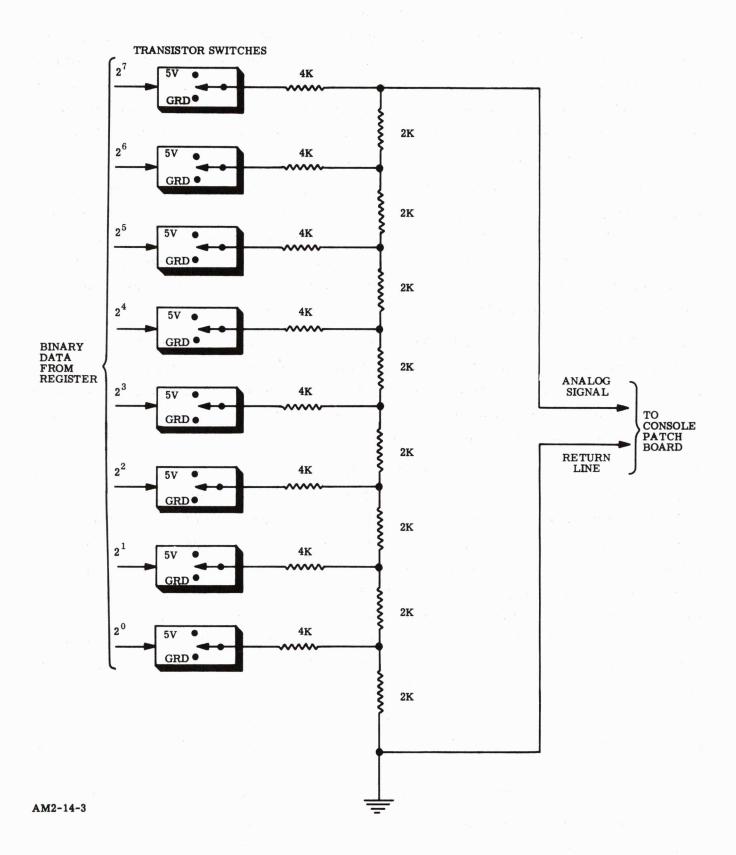

an event has taken place. The analog data words are fed via the decommutator distribution

circuits of the DD/ESDU to all of the control consoles in parallel. When a console recognizes its particular address in these data words, it transfers the data portion of the word to a digital-to-analog (D/A) converter in the console. The output of the D/A converter drives meters or analog recorders located on the console.

1-17. The third data path transfers digital and analog data to the Event Distribution, Recording, and Patching Unit, and then to roll-chart recorders in the computer room. The digital data is processed in a manner similar to the DD/ESDU.

#### 1-18. SUPPORT SYSTEMS.

- 1-19. There are several systems which form an integral portion of the ACE-S/C station, but cannot be categorized as portions of the Command, or Data Recording and Display, Equipment. These include the Timing System and the Status Display System.

- 1-20. TIMING SYSTEM. The timing group provides real-time signals for the use of the two computers and the various recorders. These time signals also drive wall time displays. In addition, the timing group supplies countdown-time signals to the computer wall clock displays.

- 1-21. STATUS DISPLAY SYSTEM. The status display system consists of go-hold switches located on the command and display consoles for reporting the test operation status to the test conductor. The controls on the consoles are connected to a display panel on the test conductor console that displays indications of test countdown hold conditions.

#### 1-22. COMMAND EQUIPMENT DESCRIPTION. (See figure 1-2.)

1-23. All commands are initiated by positioning switches on START modules. These modules are plug-in units, and are located in varying numbers on the system control consoles. There are three distinct types of START modules: R START modules providing for manual control of discrete events and selection of certain computer subroutines; C START modules providing for manual selection of computer subroutines and the parameters required by the subroutines; and a single K START module providing for manual and automatic means of inserting information into the spacecraft Automatic Guidance Computer (AGC).

#### 1-24. R START MODULE.

1-25. The R START (relay selection START) module contains four pushbutton function switches, an execute (XEQ) pushbutton, and appropriate lights to indicate the status of the switches and of the module. The function switches provide the means to select the specific discrete events desired, and the XEQ switch initiates the sequence resulting in their occurrence. Each module controls the occurrence of four discrete events (e.g., individual relay action at the spacecraft) by providing a logical "one" or "zero" from each function switch.

Figure 1-2. ACE-S/C Equipment Block Diagram

The presence or absence of a "one" is established by the on or off condition of the function switch. The R START can also be used to call up certain computer subroutines.

#### 1-26. C START MODULE.

1-27. The C START (computer communication START) module includes ten 12-position switches which provide the means to select a specific command function. Each individual switch position provides a four-bit digital word in binary-coded-decimal form for transmission to the computer. Thus, the command output of the C START is a 40-bit message which instructs the computer to perform specific operations (and also may provide parameters for these operations) and instructs the computer in the disposition of the results. The C START panel also includes status indication of the switches, an XEQ pushbutton to initiate the transmission, and appropriate lights to indicate the module status.

#### 1-28. K START MODULE.

1-29. The K START (keyboard START) module may be operated either manually (using a keyboard) or automatically (using a perforated tape reader). The operator may select the operating mode. The keyboard provides 18 pushbutton switches. Depressing any one of these switches initiates the transmission of a five-bit word to the AGC. The module panel also includes tape reader control switches. These switches provide for automatic sequences of binary words from the tape or manual sequencing including both forward and reverse steps. A visual tape character readout display is provided. Appropriate display lights on the panel indicate the status of the module and of various events within the AGC.

#### 1-30. COMMUNICATIONS UNIT EXECUTOR.

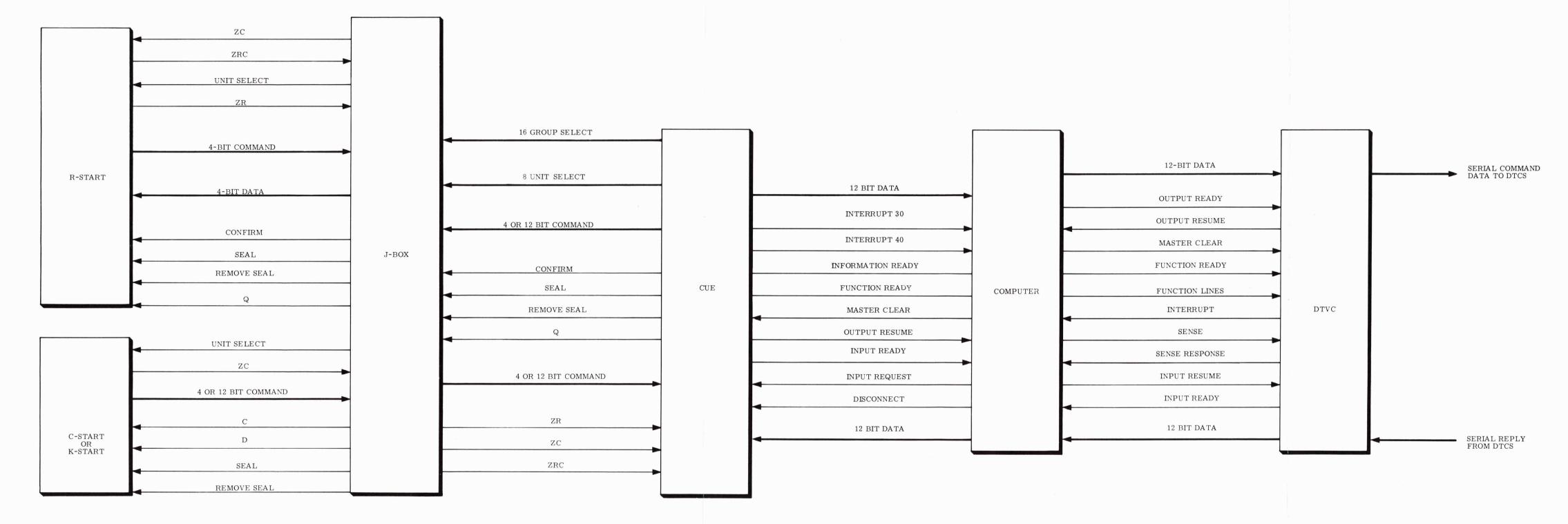

1-31. The primary function of CUE is to control the two-way communication path between the test operators and the command computer. To accomplish this control function, CUE sequentially interrogates all START modules in a repetitive fashion. The depression of an XEQ pushbutton (R START or C START) or a K START keyboard pushbutton results in interruption of CUE when it reaches that point in its cycle. CUE, under control of the computer, transfers the command data out of the START module, assigns an address which relates the data to its specific module, and transmits the data and its address to the computer. (The address assigned at this point is used for identification purposes between the START modules and the computer only.) The transmission to the computer is accomplished in two ways. If the data is from an R START, the data and its address will be transferred as a single 12-bit word in parallel format. If the data is from a C START or K START, the data and its address will be transferred as four consecutive, 12-bit words in parallel format.

1-32. When instructed by the computer, the CUE transmits verification replies to appropriate lights on the START modules. In the event of a failure, and when instructed by the computer, the CUE will display malfunction codes on a maintenance panel enabling the CUE operator to isolate the cause of failure.

#### 1-33. COMMAND COMPUTER.

- 1-34. The command computer receives the addressed data words from the CUE and performs the required processing under program control. Data from an R START or K START are encoded into a 24-bit message which includes the required address for processing at the spacecraft location. Usually, C START data instruct the computer to perform preprogrammed subroutines, the results of which may or may not be transferred out of the computer.

- 1-35. The output of the computer is one or more 24-bit messages presented to a DTVC. Each 24-bit message is transmitted by the computer as two successive 12-bit words in parallel format. The computer selects one of three DTVC's depending on whether the message is intended for airborne, carry-on, or service equipment.

- 1-36. The command computer receives verification replies from the DTVC. If verification of proper message delivery is received, the CUE is instructed to indicate verification on the appropriate START module panel. Should the verification reply indicate malfunction, the computer will retransmit the message a predetermined number of times each time waiting for verification of proper message delivery. Should the final reply still indicate failure, the computer will branch into a malfunction isolation subroutine. This routine will functionally isolate the failure, and the computer will instruct CUE as to the appropriate malfunction code to indicate on the maintenance panel.

#### 1-37. DATA TRANSMISSION AND VERIFICATION CONVERTER.

- 1-38. The DTVC is a two-way communicator and a parallel-to-serial and serial-to-parallel converter. All computer input/output communications are in parallel format but all transmissions to and from the Receiver-Decoder at the spacecraft test area are in serial format.

- 1-39. The output of the uplink computer to the DTVC is a 24-bit message presented as two successive 12-bit words in parallel format. The DTVC converts each 12-bit word to serial format and transmits a 24-bit serial word, the second half of which is identical to the first half. Thus, the output of the DTVC is 48 bits which provide complete redundancy of the 24-bit message from the computer.

- 1-40. The DTVC also receives a 24-bit serial verification reply from the Receiver-Decoder at the spacecraft location. The second half of this 24-bit reply is a repetition of the first half.

The DTVC reads the first 12 bits into a register and then performs a bit-by-bit comparison with the second 12 bits to confirm redundancy.

- 1-41. If the redundancy check fails, the DTVC transmits the first 12-bit word to the computer along with the information that the check failed. If the redundancy check is successful, the DTVC proceeds according to a computer-selected mode of operation. It may decode the verification reply or present the word to the computer. If the reply is decoded by the DTVC, and the reply indicates a legal transmission, this fact is reported to the computer. If the transmission is determined to be illegal, the verification reply word is transmitted to the computer for evaluation.

- 1-42. RECEIVER-DECODER. (This is not a part of the ACE-S/C station.)

- 1-43. The Receiver-Decoder receives the first 24-bit word from the DTVC and assembles the first 12 bits into a 24-position register. It then compares the remaining portion bit-by-bit to check redundancy. The second 24-bit word of the command message is received, and the first 12 bits are assembled into the remaining spaces in the register. A bit-by-bit redundancy check is then performed. If either redundancy check fails, the register is cleared, the Receiver-Decoder is set to receive, and a verification message, coded to indicate transmission error, is transmitted back over the uplink line to the DTVC.

- 1-44. If a successful redundancy check is completed, decoding of the message address is begun. Decoding is accomplished at several levels. At each level, a number of discrete bits are examined to determine which of several alternate routes the remaining message bits are to follow. Decoding begins with the more significant address bits. In each case, the decoded bits are dropped, and only the remaining bits of the word are transmitted to the next lower level.

- 1-45. The Receiver-Decoder performs the first step of address decoding and accordingly selects one of several groups of modular assemblies known as baseplates, or the Guidance and Navigation (G and N) module. If the G and N module is selected, the remaining message bits are sent to this module which transfers the proper data into the spacecraft onboard automatic guidance computer. If one of the baseplate groups is selected, the remaining message bits are sent to all baseplates in this group for further decoding.

- 1-46. A given baseplate group may contain as many as eight baseplates. However, only one of these can accept the message as addressed. The selected baseplate will decode the message further and select one of the modules installed on the baseplate. The selected module will accept the remaining bits for further decoding.

1-47. There are two types of modules mounted on the baseplates - a D/A converter module and a relay module. Any baseplate can contain up to four modules with any combination of the two types, or all four of a single type.

- 1-48. If a D/A converter module is selected, it will decode the remaining bits and provide the indicated positive or negative voltage level as a spacecraft stimulus.

- 1-49. If a relay module is selected, it will decode the message further to select one of four subgroups of relays controlled by the module. Four data bits will be transferred to a buffer memory of the subgroup which exercises control over four relays. A second transmission from the uplink computer provides four duplicate data bits which are compared with those from the first transmission. If the comparison is exact, the first four data bits are shifted from the buffer memory to an execute memory which causes the four relays to react to the data bits, with a "one" causing latch and a "zero" causing unlatch. If the comparison is not exact, the data bits are not shifted to the execute memory, a coded verification reply is sent to indicate the comparison failure, and the Receiver-Decoder is set to receive.

- 1-50. At each level of decoding, from the Receiver-Decoder to the subgroup, the legality of the address is determined. In every case, there are fewer legal addresses than the total which the number of bits would permit. If the decoded portion of the address is found illegal, decoding ceases, the Receiver-Decoder is set to receive, and a coded verification reply is sent to the DTVC to indicate the level of decoding at which the error was detected.

#### 1-51. RECORDING AND DISPLAY EQUIPMENT DESCRIPTION. (See figure 1-2.)

1-52. The recording and display equipment provides for receiving, recording, and displaying the spacecraft performance parameters and other data necessary for complete checkout of the spacecraft. This system is made up of the spacecraft and spacecraft vicinity equipment (not a part of ACE-S/C), Data Acquisition and Decommutation Equipment, Alphanumeric Display Equipment, and Analog and Event Recording and Display Equipment.

#### 1-53. SPACECRAFT AND SPACECRAFT VICINITY EQUIPMENT.

- 1-54. Test data are obtained from sensors in the spacecraft (permanently installed), in the carry-on equipment (which is removed prior to flight), and in the Ground Service Equipment. Data obtained from the permanently installed spacecraft sensors are identical to that which are transmitted by the flight telemetry system and are called airborne (A/B) data.

- 1-55. The majority of data are converted to serial PCM format and transmitted to the ground station over hardlines. Certain data (e.g., the outputs of vibration sensors), which are required in raw form, are frequency modulated and transmitted to the ground station over a separate hardline.

1-56. The flight telemetry system contains the signal conditioning, commutation, encoding, and digital multiplexing equipment necessary to convert the A/B sensor outputs into a serial PCM output at 51.2 kilobits per second. This output is called A/B PCM. The carry-on equipment performs these same functions for the carry-on sensors.

- 1-57. The outputs of the ground service equipment sensors are fed to a unit known as the service equipment adapter, which performs the commutation, encoding, and digital multiplexing required to convert them into a third serial PCM output, called service equipment PCM. The carry-on and ground service equipment PCM data are combined to form a single 51.2-kilobit-per-second signal.

- 1-58. These three PCM outputs (A/B, and combined carry-on and service equipment) are fed to an interleaver which combines the PCM inputs into a single, interleaved (I/L), serial PCM output and transmits this to the ground station over a hardline at a rate of 204.8 kilobits per second. The A/B PCM, in addition to being interleaved with other data, is also transmitted intact (at its original rate of 51.2 kilobits per second) to the ground station over a separate hardline.

- 1-59. All PCM data, analog and event, are presented as eight-bit words. For the analog data, each eight-bit word represents a single analog sample. For the event data, each eight-bit word represents eight discrete events. Interleaving is performed on a word basis.

- 1-60. DATA ACQUISITION AND DECOMMUTATION EQUIPMENT (DADE).

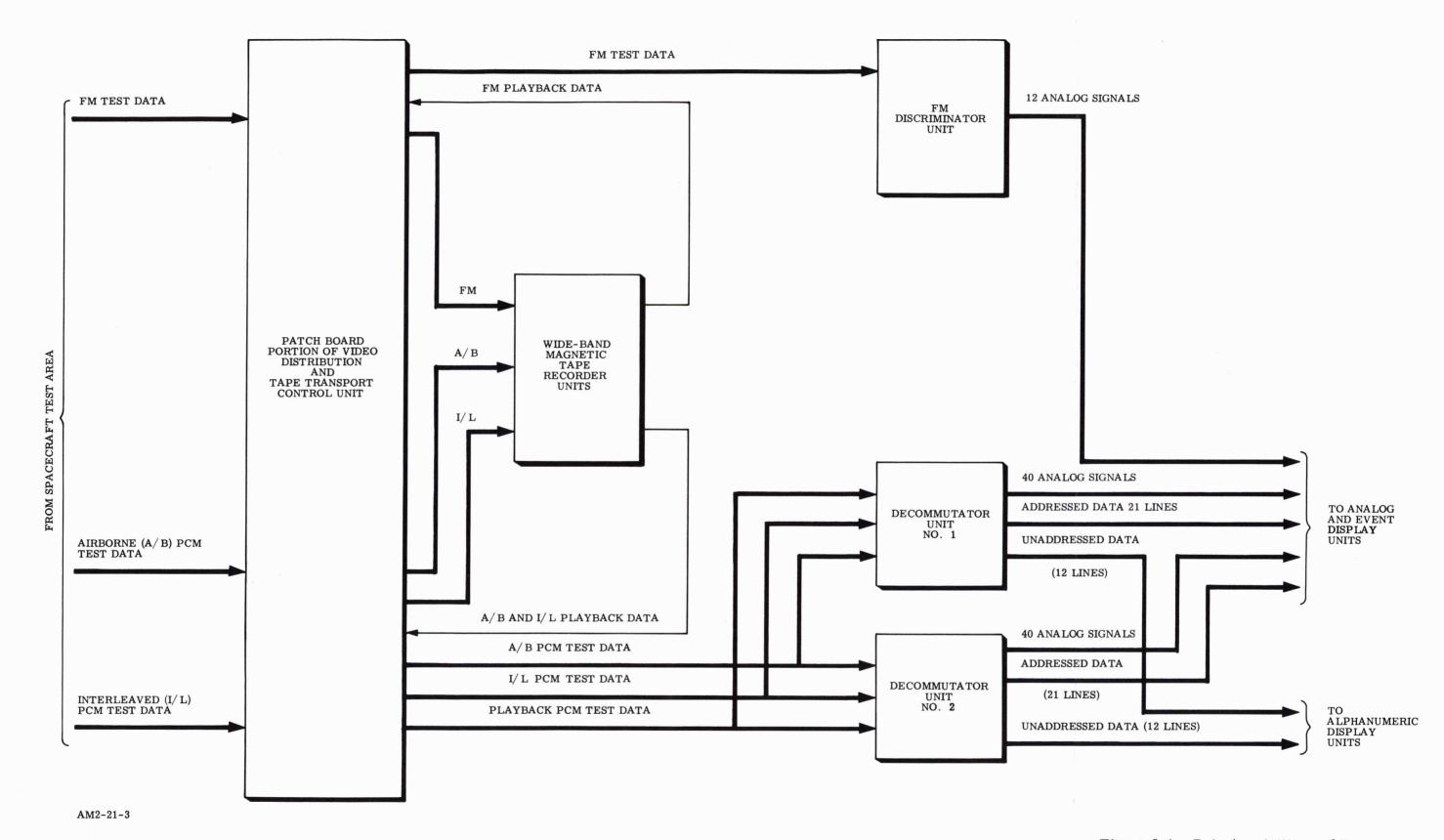

- 1-61. The Data Acquisition and Decommutation Equipment group provides for acquiring, recording, synchronizing, decommutating, and distributing the data transmitted from the spacecraft vicinity. The three data lines (A/B, I/L, and FM) are routed to this equipment group through a terminal patch facility. This equipment group is made up of the Video Distribution and Tape Transport Control Unit and DADS.

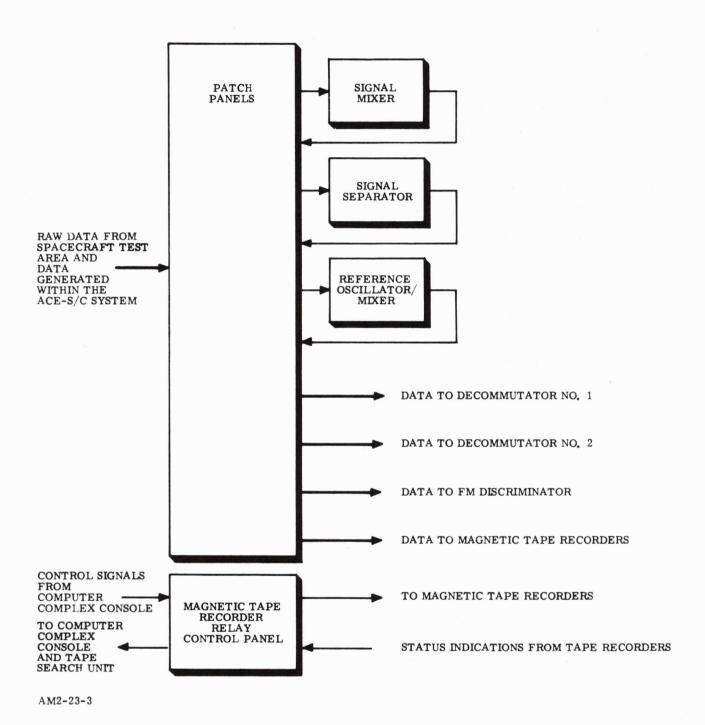

- 1-62. VIDEO DISTRIBUTION AND TAPE TRANSPORT CONTROL UNIT. The three incoming data lines are initially terminated at the Video Distribution and Tape Transport Control Unit which provides patching and switching to route the data to the desired decommutator (PCM), discriminator (FM), and magnetic tape recorder-reproducer (PCM and FM). The data are routed as follows:

- a. All data are routed to wideband magnetic tape recorders.

- b. The FM data may be routed to discriminators and then to an analog recorder.

- c. The A/B PCM data are routed to one of two DADS units.

- d. The interleaved stream of A/B, carry-on, and service equipment data is routed to the other DADS unit.

1-63. DIGITAL ACQUISITION AND DECOMMUTATION SYSTEM. The DADS unit provides the processing necessary to convert the incoming eight-bit serial data words into parallel format and assign addresses to them for distribution within the ground station. At the input to the DADS unit, bit synchronization is achieved, and each pulse is reshaped to assure good bit definition prior to further processing. The serial data bits are read into a shift register and as the data are shifted through the register, frame synchronization is established. Following frame synchronization, subframe synchronization is established. At this point, the location and identity of each data word are known and read out of the register in parallel format and presented at the decommutator output. Simultaneously, in accordance with decommutator programming, the appropriate address for each data word and a read pulse are presented at the decommutator output. The decommutator output (without addresses) is routed to the Alphanumeric Display System via the Decommutator/Computer Interface Unit and Display Computer, and (with addresses) to the Event and Analog Data Display System.

#### 1-64. ALPHANUMERIC DISPLAY SYSTEM.

- 1-65. The Alphanumeric Display System furnishes the primary displays for monitoring analog measurements and certain event occurrences. It provides at a single location the capability of simultaneously viewing 24 lines of data presented in decimal numbers and engineering units on the screen of a CRT. Switching capability on the display module permits the callup of 40 separate data tabulations each of which has a 12-line capacity. Suitable function and page identification are also displayed. This display capability requires data processing, storage, symbols generation, and CRT display.

- 1-66. DATA PROCESSING. Data from the decommutators are routed to the downlink computer through the input/output module. These data are stored in two locations in the memory. While a block of data is being stored in one location, the computer processes data in the other location. The primary operations which the computer must perform in processing the downlink data include the following:

- a. Assemble the data into proper word length and format.

- b. Compare any given word or words to determine whether the data fall within predetermined limits, and flag out-of-limit conditions.

- c. Compute the average of a block of words and retain this average for output display.

- d. Convert data into engineering units, both linear and quadratic functions, using curve techniques.

- e. Convert data and place in proper format for alphanumeric CRT display.

- 1-67. Operating under program control, the computer provides a series of 12-bit coded words which include parameter value and address and associated instructions. These 12-bit words are transmitted in parallel format to the DTVC.

1-68. DATA TRANSMISSION. The DTVC converts each 12-bit word to serial format and transmits it redundantly as a 24-bit serial message to a Digital Communication and Control Unit (DCCU). The DCCU assembles the first 12 bits into a register and then compares the second 12 bits with the first 12 bits to check redundancy. If the redundancy check is successful, the DCCU transmits the 12-bit word in parallel format to an SGS unit. The DCCU has the capability of preventing transmission to the SGS if the redundancy check fails.

- 1-69. SYMBOL GENERATION AND STORAGE. The SGS unit receives the coded words from the DCCU. The 12-bit words are decoded, and the data are stripped out and stored in memory locations according to received instructions and addresses. The entire content of this memory is updated once per second, and it is scanned at a rate sufficient to update all alphanumeric displays at least 30 times per second.

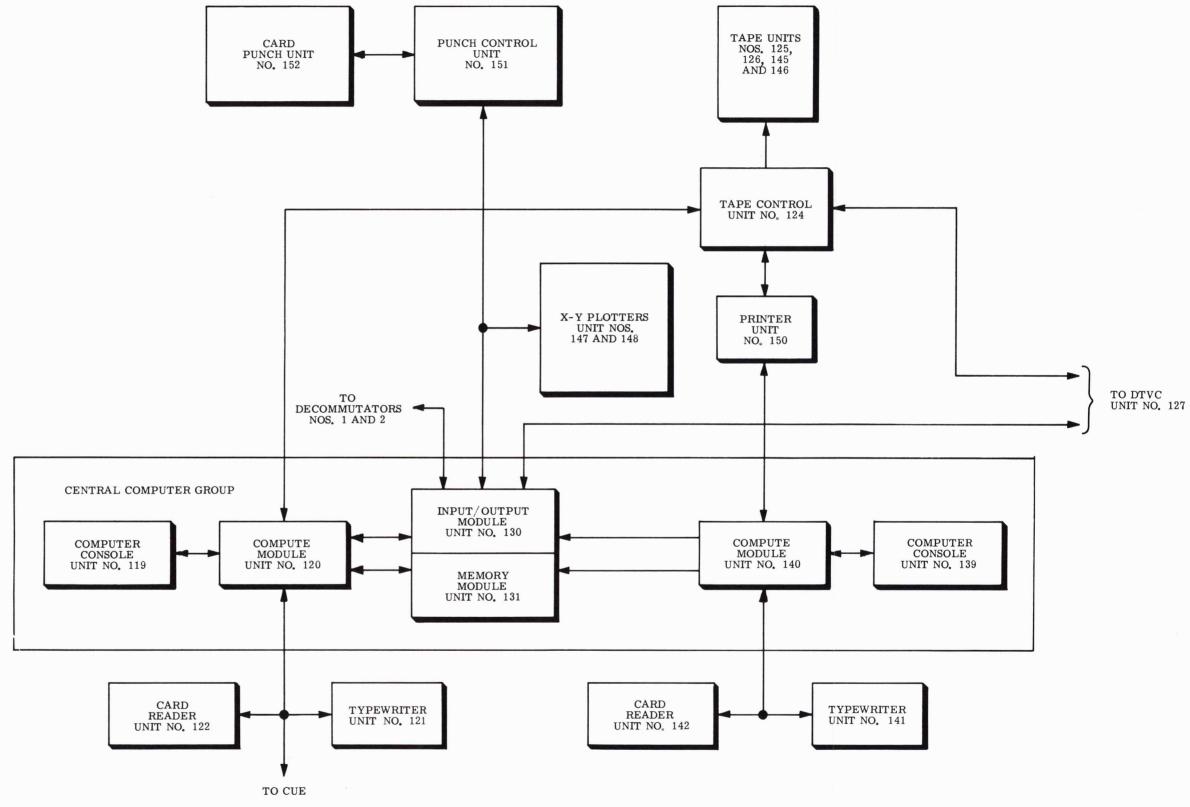

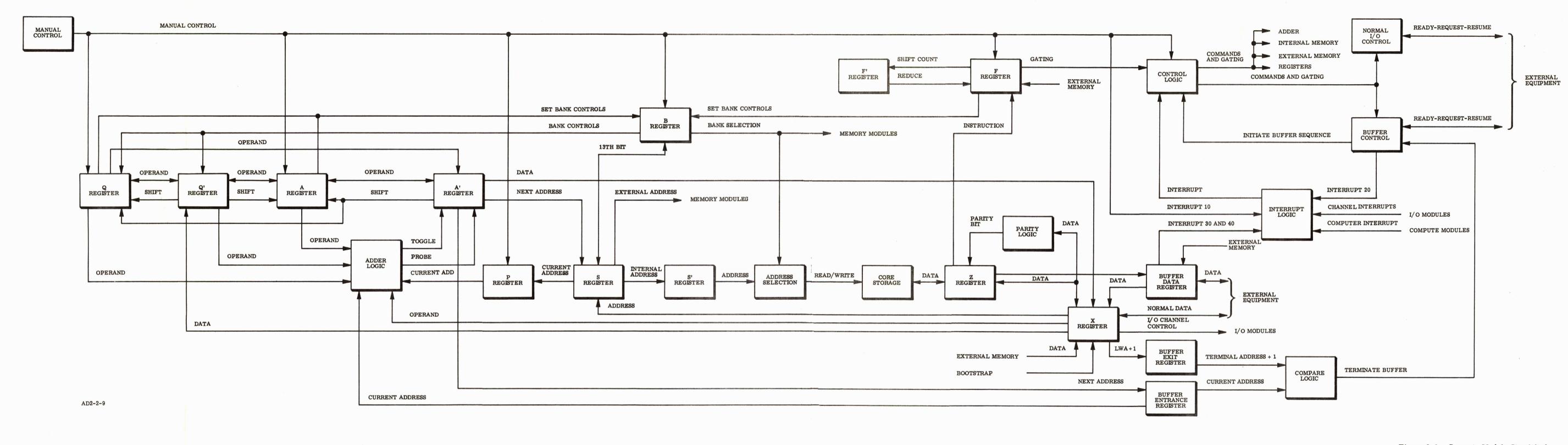

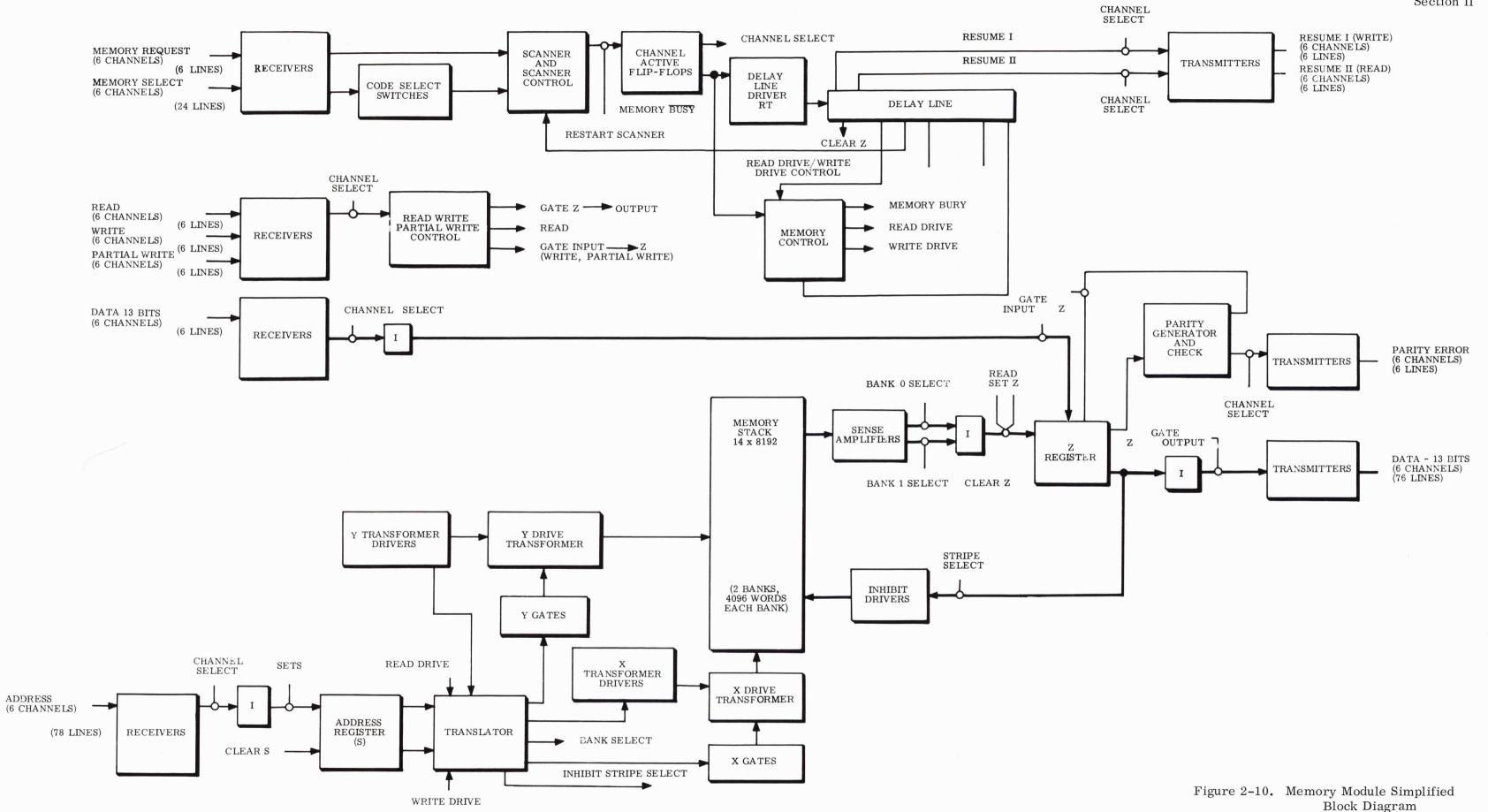

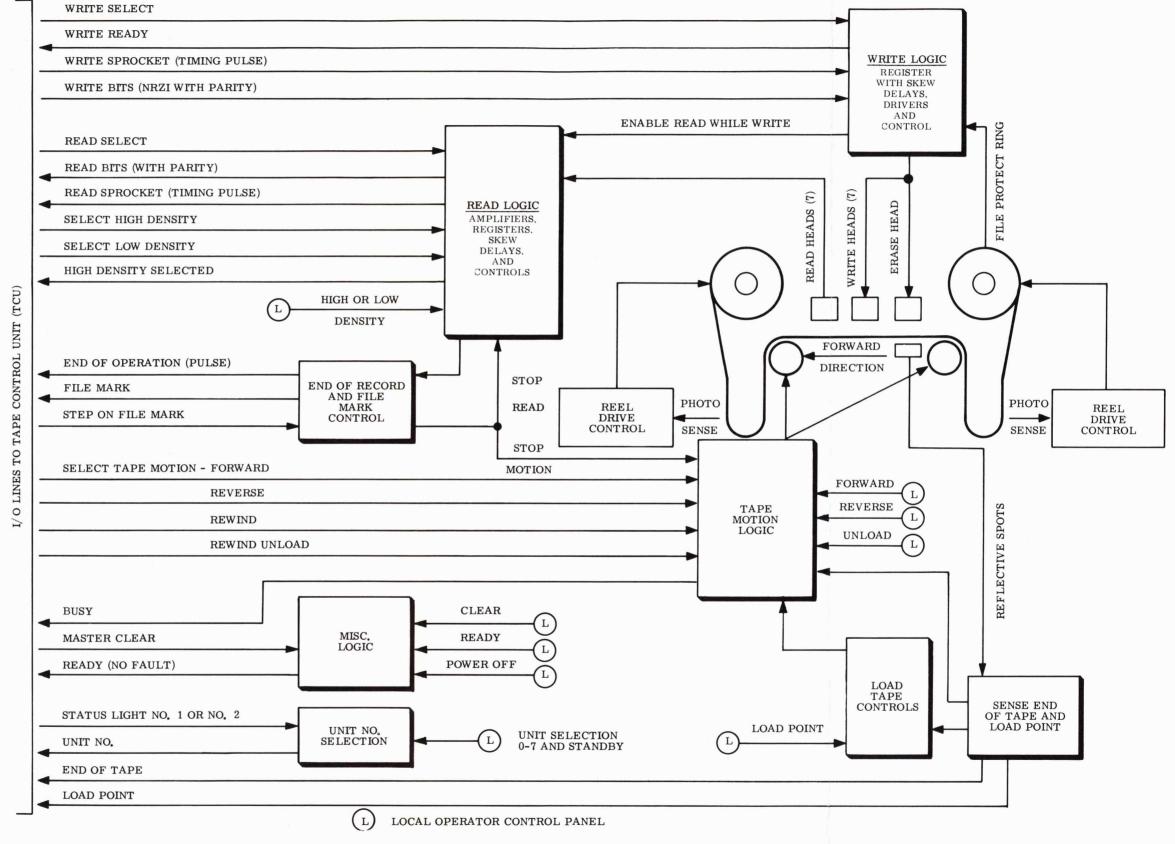

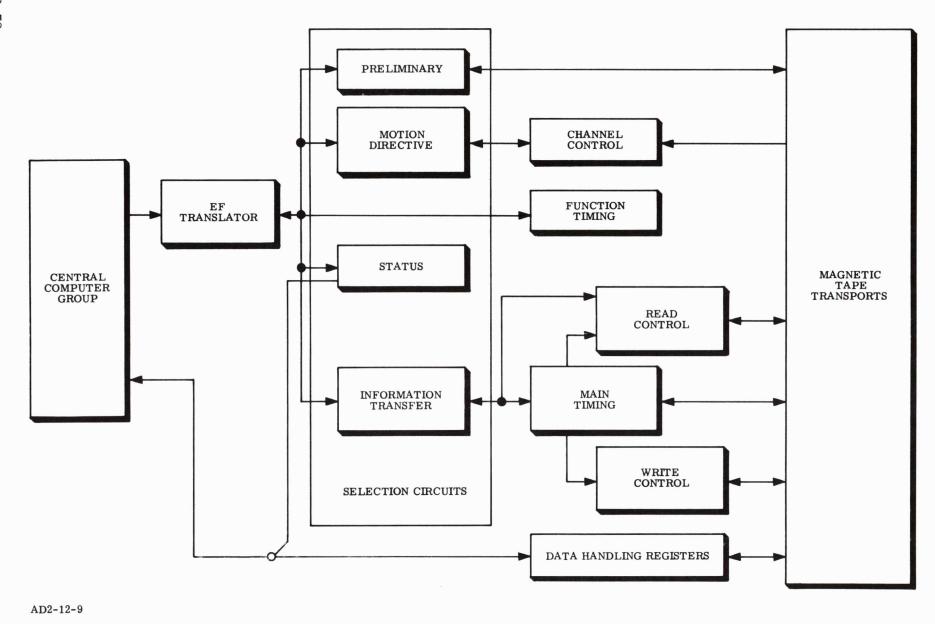

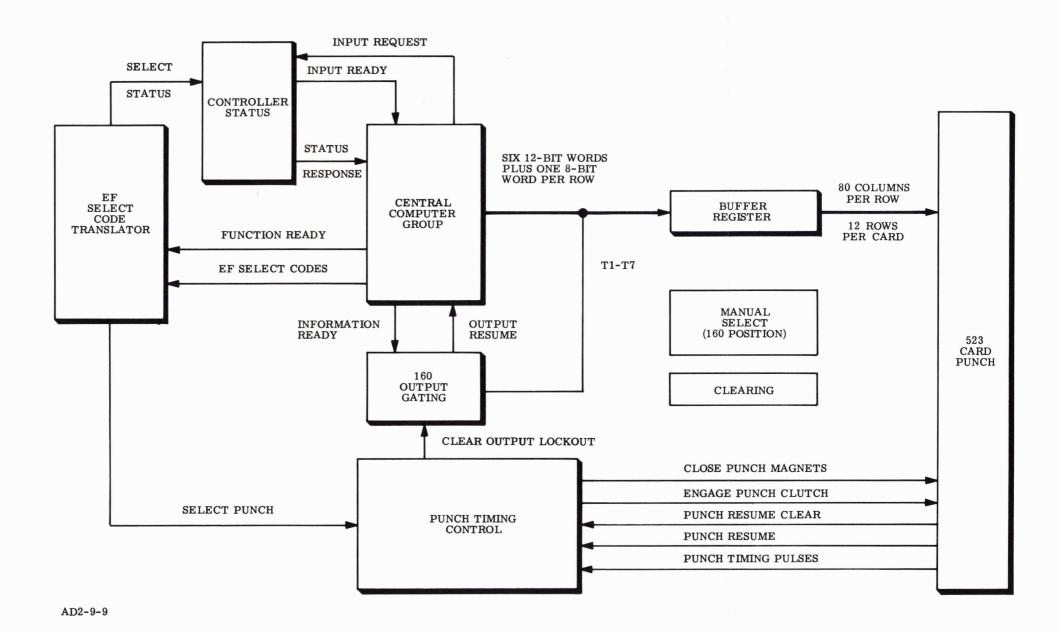

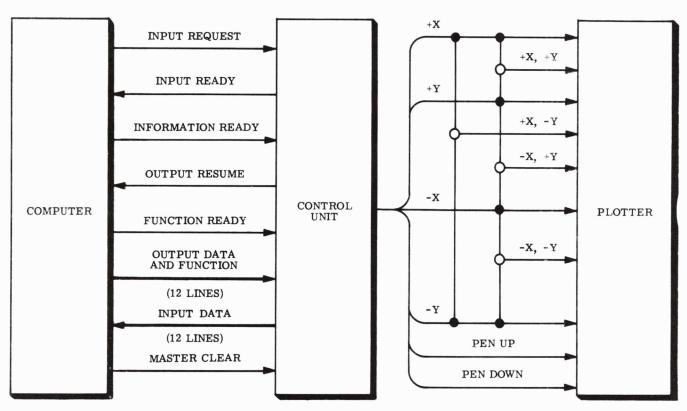

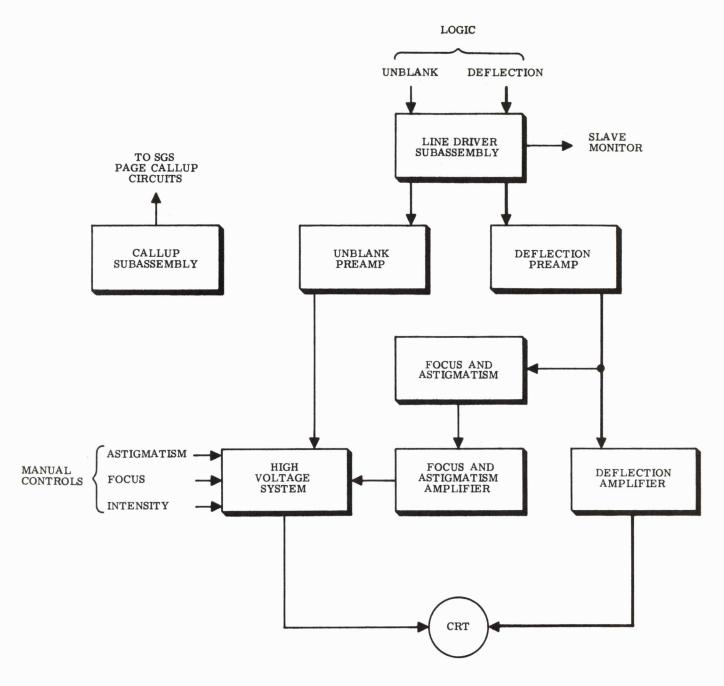

- 1-70. The character repertoire of the SGS allows display of all alphanumeric characters together with a set of special symbols. Also incorporated is the capability to cause characters to blink on the CRT screen when so instructed by the computer. This blinking indicates an out-of-tolerance condition.