APOLLO GUIDANCE COMPUTER

Information Series

**ISSUE 2**

MACHINE INSTRUCTIONS

FR-2-102A

10 March 1963

Changed 2 July 1964

This document contains information affecting the national defense of the United States within the meaning of the Espionage Laws, Title 18, U.S.C., Sections 793 and 794, the transmission or revelation of which in any manner to an unauthorized person is prohibited by law.

#### GROUP 4

Downgraded at 3-year intervals; declassified after 12 years.

FR-2-102A

### CONTENTS

| Paragraph |                                          | Page |

|-----------|------------------------------------------|------|

| 2-1       | INTRODUCTION                             | 2-1  |

| 2-3       | EXECUTION OF MACHINE INSTRUCTIONS        | 2-1  |

| 2-6       | Basic Instructions                       | 2-8  |

| 2-7       | Common Characteristics                   | 2-8  |

| 2-15      | Instruction TCK                          | 2-13 |

| 2-19      | Instruction XCH K                        | 2-15 |

| 2-22      | Instruction CS K                         | 2-18 |

| 2-25      | Instruction TSK                          | 2-18 |

| 2-29      | Instruction MSK K                        | 2-23 |

| 2-33      | Instruction AD K                         | 2-26 |

| 2-36      | Instruction NDX K                        | 2-28 |

| 2-40      | Instruction CCS K                        | 2-32 |

| 2-47      | Extra Code Instructions                  | 2-41 |

| 2-48      | Common Characteristics.                  | 2-41 |

| 2-50      | Instruction SUK                          | 2-41 |

| 2-53      | Instruction MP K                         | 2-42 |

| 2-66      | Instruction DV K                         | 2-58 |

| 2-78      | Special Cases of Regular Instructions    | 2-74 |

| 2-79      | General                                  | 2-74 |

| 2-81      | Special Cases of Basic Instructions      | 2-74 |

| 2-90      | Special Cases of Extra Code Instructions | 2-77 |

| 2-94      | Involuntary Instructions                 | 2-78 |

| 2-95      | General                                  | 2-78 |

| 2-99      | Instruction RPT                          | 2-81 |

| 2-102     | Instruction RSM                          | 2-84 |

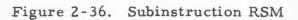

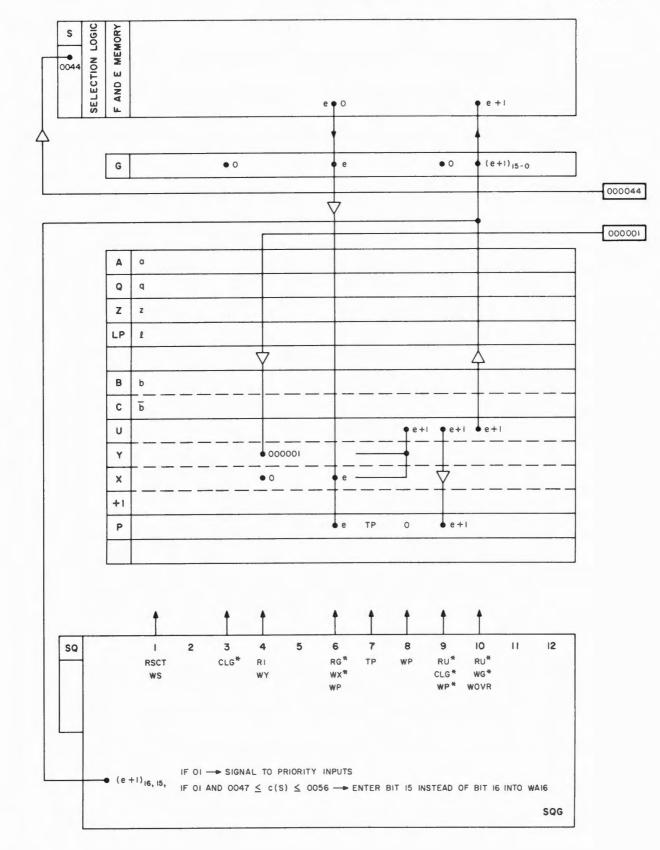

| 2-105     | Instruction PINC                         | 2-84 |

| 2-108     | Instruction MINC                         | 2-86 |

| 2-111     | Instruction SHINC                        | 2-88 |

| 2-115     | Instruction SHANC                        | 2-93 |

FR-2-102A

### CONTENTS (cont)

| Paragraph |                    |    |      |     |  |   |   |   |   |   | Page |

|-----------|--------------------|----|------|-----|--|---|---|---|---|---|------|

| 2-118     | Miscellaneous Inst | ru | ctio | ons |  |   |   |   |   |   | 2-93 |

| 2-119     | General            |    |      |     |  |   |   |   | • | ٠ | 2-93 |

| 2-121     | Instruction GO .   |    |      |     |  | • |   |   |   |   | 2-93 |

| 2-123     | Instruction TCSA   |    |      |     |  |   |   | ٠ |   |   | 2-95 |

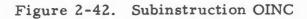

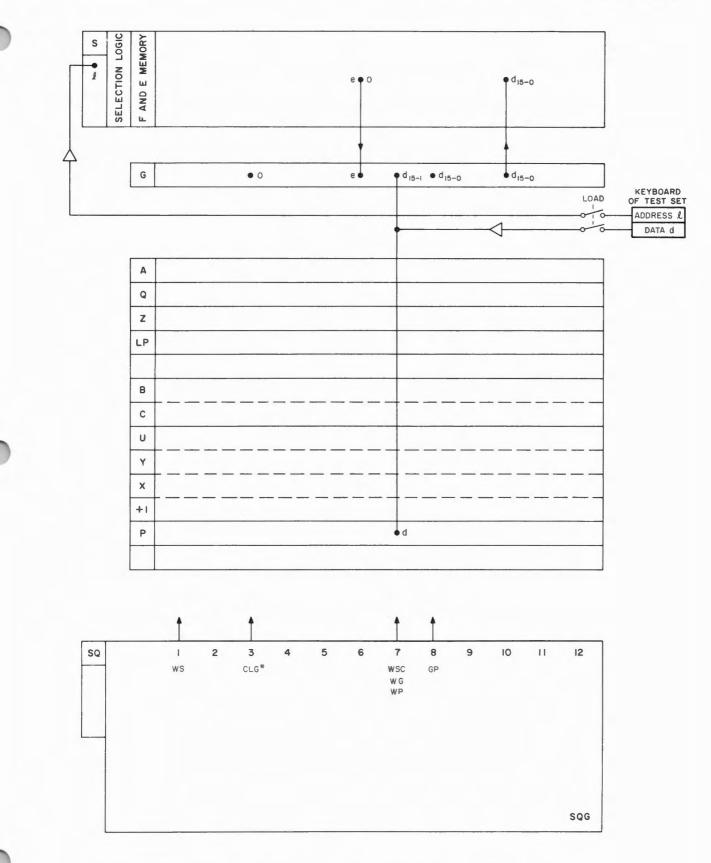

| 2-125     | Instruction OINC   |    |      |     |  |   |   |   |   |   | 2-95 |

| 2-127     | Instruction LINC   |    |      | •   |  |   | • |   |   |   | 2-95 |

### **ILLUSTRATIONS**

| Figure |                                                      |  | Page |

|--------|------------------------------------------------------|--|------|

| 2-1    | Subinstruction STD2 (Example for $z > 0020$ )        |  | 2-7  |

| 2-2    | Subinstruction STD2 (Example for $z = 0001$ )        |  |      |

| 2-3    | Subinstruction TC0                                   |  |      |

| 2-4    | Subinstruction XCH0                                  |  |      |

| 2-5    | Subinstruction CS0                                   |  | 2-19 |

| 2-6    | Subinstruction TS0 (without Overflow or Underflow    |  |      |

|        | in A)                                                |  | 2-21 |

| 2-7    | Subinstruction TS0 (with Overflow or Underflow in A) |  | 2-22 |

| 2-8    | Subinstruction MSK0                                  |  | 2-25 |

| 2-9    | Subinstruction AD0                                   |  |      |

| 2-10   | Subinstruction NDX0                                  |  | 2-29 |

| 2-11   | Subinstruction NDX1                                  |  |      |

| 2-12   | Subinstruction CCS0 (Example e > +0)                 |  | 2-33 |

| 2-13   | Subinstruction CCS0 (Example $e = +0$ )              |  |      |

| 2-14   | Subinstruction CCS0 (Example $e < -0$ )              |  | 2-35 |

| 2-15   | Subinstruction CCS0 (Example e = -0)                 |  | 2-36 |

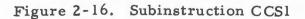

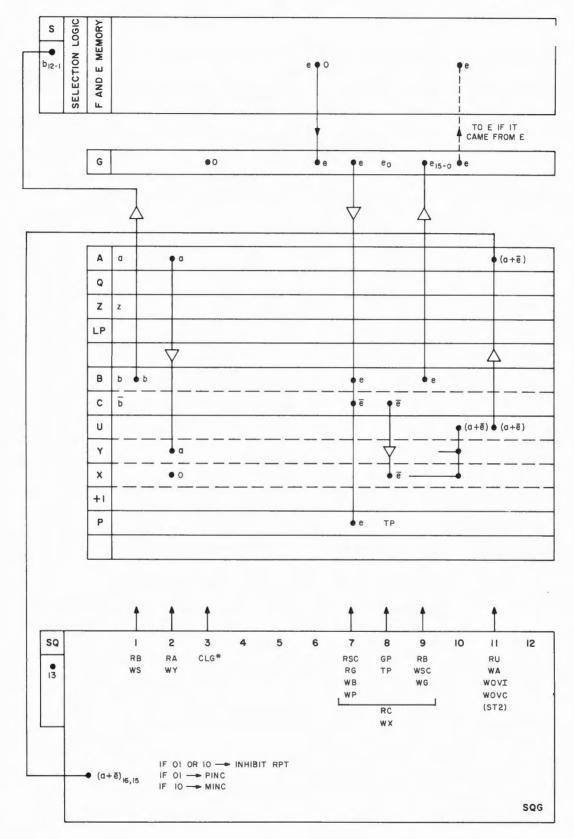

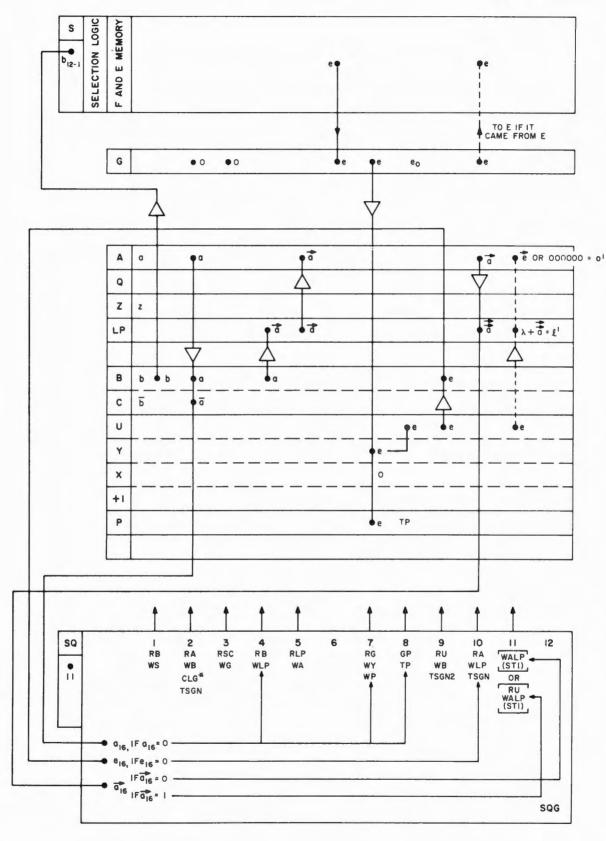

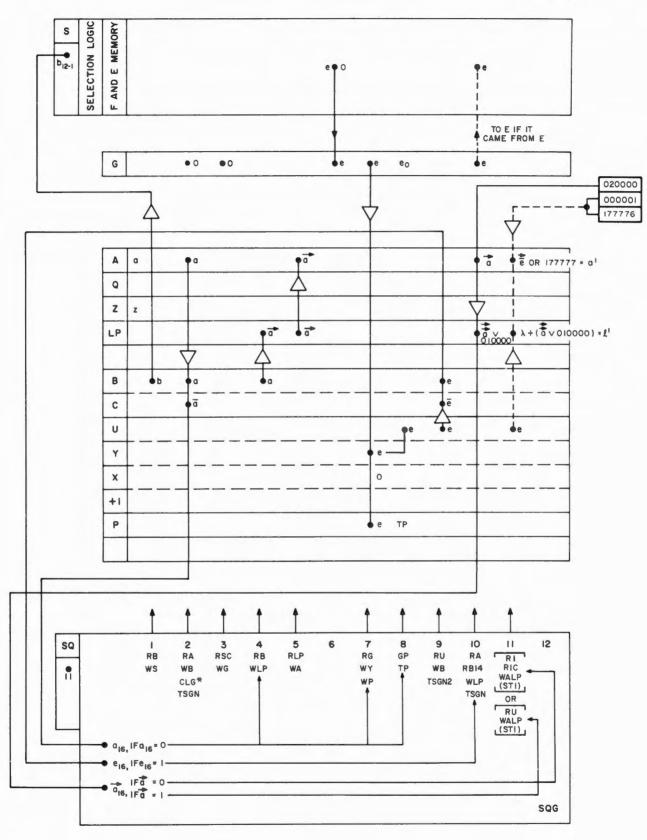

| 2-16   | Subinstruction CCS1                                  |  |      |

| 2-17   | Subinstruction SU0                                   |  |      |

| 2-18   | Multiplication of Two Binary Numbers, Principle      |  |      |

|        | of Operation                                         |  | 2-44 |

| 2-19   | Multiplication of Two Binary Numbers, Method         |  |      |

|        | of Operation                                         |  | 2-46 |

| 2-20   | Subinstruction MP0 (a and e Positive)                |  | 2-48 |

| 2-21   | Subinstruction MP0 (a Positive and e Negative)       |  |      |

| 2-22   | Subinstruction MP0 (a Negative and e Negative)       |  | 2-50 |

| 2-23   | Subinstruction MP0 (a Negative and e Positive)       |  |      |

| 2-24   | Subinstruction MP1                                   |  | 2-52 |

FR-2-102A

### ILLUSTRATIONS (cont)

Figure

| 2-25 | Subinstruction MP3                                 |  | 2-53 |

|------|----------------------------------------------------|--|------|

| 2-26 | Division of Binary Numbers, Principle of Operation |  | 2-60 |

| 2-27 | Division of Binary Numbers, Method of Operation .  |  | 2-63 |

| 2-28 | Subinstruction DVO (a and e Positive)              |  | 2-65 |

| 2-29 | Subinstruction DV0 (a Positive and e Negative)     |  | 2-66 |

| 2-30 | Subinstruction DV0 (a Negative and e Positive)     |  | 2-67 |

| 2-31 | Subinstruction DVO (a and e Negative)              |  | 2-68 |

| 2-32 | Subinstruction DV1 (Incorrect Remainder)           |  | 2-69 |

| 2-33 | Subinstruction DV1 (Correct Remainder)             |  | 2-70 |

| 2-34 | Subinstruction RPT1                                |  | 2-82 |

| 2-35 | Subinstruction RPT3                                |  | 2-83 |

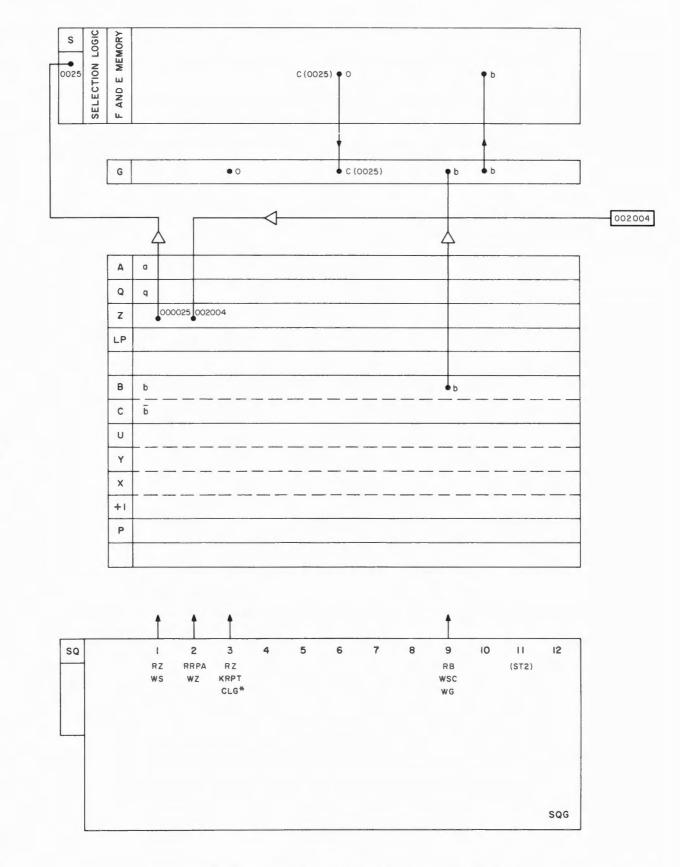

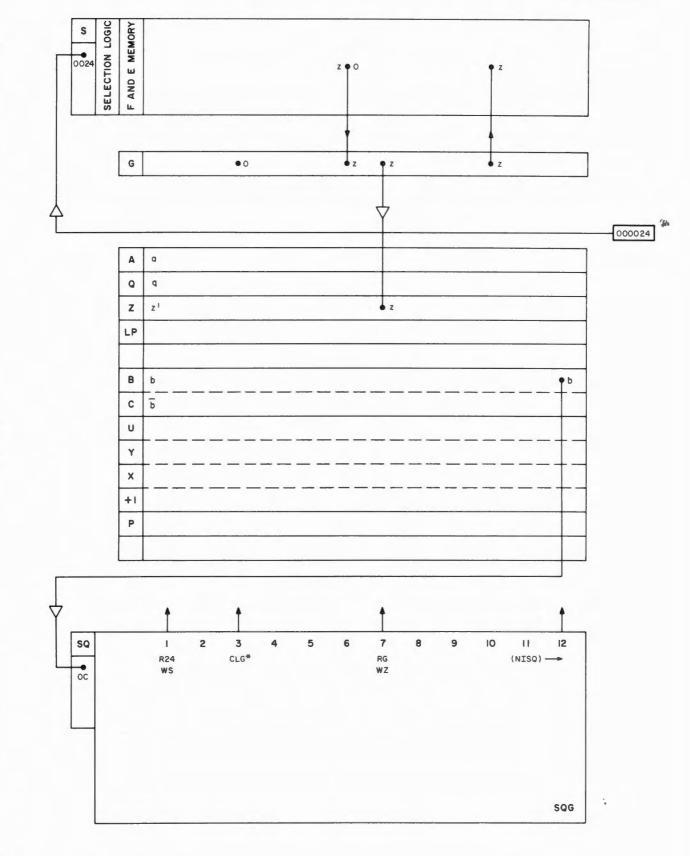

| 2-36 | Subinstruction RSM                                 |  | 2-85 |

| 2-37 | Subinstruction PINC                                |  | 2-87 |

| 2-38 | Subinstruction MINC                                |  | 2-89 |

| 2-39 | Subinstruction SHINC                               |  | 2-91 |

| 2-40 | Completion of an Uplink Word                       |  | 2-92 |

| 2-41 | Subinstruction SHANC                               |  | 2-94 |

| 2-42 | Subinstruction OINC                                |  | 2-96 |

| 2-43 | Subinstruction LINC                                |  | 2-97 |

|      |                                                    |  |      |

#### TABLES

| Table |                                            |  |   |  | Page |

|-------|--------------------------------------------|--|---|--|------|

| 2-1   | Control Pulses                             |  |   |  | 2-2  |

| 2-2   | Control Pulses for all Subinstructions     |  |   |  |      |

| 2-3   | Content of A and Z at End of CCS0 and CCS1 |  | • |  | 2-37 |

| 2-4   | Contents of Registers at End of MP0        |  |   |  | 2-57 |

| 2-5   | Contents of Registers at End of DV0        |  |   |  | 2-73 |

| 2-6   | RPT and GO Transfer Routines               |  |   |  | 2-79 |

Changed 2 July 1964

FR-2-102A

#### 2-1. INTRODUCTION

2-2. This is the second issue of the AGCIS, which is published to inform the technical staff of MIT/IL and Raytheon about the Apollo guidance computer (AGC) subsystem. The various types of instructions provided for the AGC are defined in paragraphs 15-80 through 15-97 of Issue 15. The Machine Instructions are listed in table 15-12. This issue describes the execution of each Machine Instruction. Information pertaining to the Machine Instructions was originally taken from an advanced copy of MIT/IL Report R-393 and later updated.

2-3. A Machine Instruction is defined as a sequence of Actions (paragraph 15-14); each Action as a set of control pulses generated by the Sequence Generator (SG, Issue 5). Table 2-1 lists and defines those control pulses which are directly involved in the execution of a Machine Instruction. Actions are generated at a rate of 1.024 mc, or every 0.977  $\mu$ sec. Twelve Actions make a subinstruction and take one MCT (memory cycle time). One or more subinstructions make one Machine Instruction. Table 2-2 lists the control pulses as generated at the various Actions of all subinstructions. Control pulse WP generated at Action 1 is needed for noise suppression in F memory (paragraph 15-36) and has little to do with the control of information flow.

#### 2-4. EXECUTION OF MACHINE INSTRUCTIONS

2-5. The execution of Machine Instructions is described with the help of instruction flow charts. The format of such a chart, for instance figure 2-1, is similar to the machine organization diagram (figure 15-7). The F memory and the E memory are shown combined. The control registers are shown individually. Buffer-register B is shown with its direct (B) and its complement (C) side. The row marked "+1" symbolizes that circuitry of the Adder which, on command, adds the quantity plus-one to an operand entered into input register X or Y. The basic principle of the Adder operation has been described in paragraphs 15-27 through

Changed 29 May 1964

CONFIDENTIAL

FR-2-102A

#### TABLE 2-1

### CONTROL PULSES

| Pulse   | Purpose                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CI      | Force carry into bit position 1 of Adder                                                                                                                                             |

| CLG*    | Clear (reset) bit position 15 through 0 of G $\triangle$                                                                                                                             |

| CTR     | Decrement Loop Counter and set STAGE 2 at Action 12 if content of Loop Counter goes to zero $2$                                                                                      |

| GP      | Reset bit position 0 of G and enter into it the new parity bit generated by the parity pyramid. If $c(S) = 0014$ , reset bit position 0 of OUT4 and enter generated parity bit there |

| KRPT    | Clear Request Flip-Flop (in Program Interrupt Priority<br>Control) that initiated program interrupt.                                                                                 |

| NISQ    | Transfer contents of $B_{16-13}$ to SQ at Action 12                                                                                                                                  |

| RA      | Read content of A into WA's                                                                                                                                                          |

| RB      | Read content of B (direct side of B) into WA's                                                                                                                                       |

| RC      | Read content of C (complement side of B) into WA's                                                                                                                                   |

| RB14    | Read 020000 into WA's (a ONE into bit position 14)                                                                                                                                   |

| RG, RG* | Read content of G into WA's 1 3                                                                                                                                                      |

| RLP     | Read content of LP into WA's 3                                                                                                                                                       |

| RP2     | Reset bit position 0 of G and enter c(P2) into it                                                                                                                                    |

| RQ      | Read content of Q into WA's                                                                                                                                                          |

| RRPA    | Read address provided by Program Interrupt Priority Control<br>into WA's                                                                                                             |

| RSA     | Read specified address into register S                                                                                                                                               |

| RSB     | Read 100000 into WA's (a ONE into WA16 only)                                                                                                                                         |

| RSC     | Read content of addressed flip-flop register into WA's                                                                                                                               |

| RSCT    | Read address provided by Counter Priority Control into WA's                                                                                                                          |

| RSTRT   | Read STRT address into WA's                                                                                                                                                          |

| RU, RU* | Read content of U into WA's 🔬                                                                                                                                                        |

| RZ      | Read content of Z into WA's                                                                                                                                                          |

| Rl      | Read 000001 into WA's                                                                                                                                                                |

| RIC     | Read 177776 into WA's                                                                                                                                                                |

Changed 13 Dec 1963

FR-2-102A

#### TABLE 2-1

### CONTROL PULSES (continued)

| Pulse | Purpose                                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R2    | Read 000002 into WAs                                                                                                                                                                            |

| R22   | Read 000022 into WAs                                                                                                                                                                            |

| R24   | Read 000024 into WAs                                                                                                                                                                            |

| ST1   | Set STAGE 1 at Action 12                                                                                                                                                                        |

| ST2   | Set STAGE 2 at Action 12                                                                                                                                                                        |

| TMZ   | Test for minus zero. Transfer contents of WAs to SQG and<br>set BR2 if all bits are ONEs. Reset BR2 if all bits are<br>ZEROs 2                                                                  |

| TOV   | Test for overflow or underflow. Transfer contents of WAs 16<br>and 15 to SQG and set BR2 in case of overflow, or set BR1 in<br>case of underflow. Reset BR1 and BR2 for other<br>conditions $2$ |

| TP    | Test Parity. Allow incorrect parity to cause alarm if $c(S) \ge 0030$                                                                                                                           |

| TRSM  | Test for RSM. Transfer $c(S)$ to SQG and set STAGE 2 at<br>Action 12 if $c(S) = 0025$                                                                                                           |

| TSGN  | Test sign. Transfer content of WA16 to SQG and set BR1 if bit 16 is a ONE. Reset BR1 if bit 16 is a ZERO $2$                                                                                    |

| TSGN2 | Test sign. Transfer content of WA16 to SQG and set BR2 if bit 16 is a ONE. Reset BR2 if bit 16 is a ZERO $2$                                                                                    |

| TSGN3 | Test sign. Transfer content of WA16 to SQG and send signal to Program Priority Circuit if bit 16 is a ONE                                                                                       |

| WA    | Reset A and write contents of WAs into A                                                                                                                                                        |

| WALP  | Reset A and bit position 14 of LP and write contents of WAs into them $3$                                                                                                                       |

| WB    | Reset B and write contents of WAs into B                                                                                                                                                        |

| WG    | Reset bit positions 15 through 1 of G and write contents of WAs into G $3$                                                                                                                      |

| WG*   | Write contents of WAs directly (without editing) into bit posi-<br>tions 15 through 1 of register G and the generated parity bit<br>into bit position 0 $(1)$ $(3)$                             |

FR-2-102A

#### TABLE 2-1

### CONTROL PULSES (continued)

| Pulse   | Purpose                                                                                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| WLP     | Reset LP and write contents of WAs into LP 3                                                                                                   |

| WP      | Reset P and write contents of WAs into P                                                                                                       |

| WP*     | Write contents of WAs into P during last $3/4 \ \mu sec$                                                                                       |

| WP2     | Reset P2 and enter into it the new parity bit generated by parity pyramid. If $c(S) = 0014$ , reset position 0 of OUT4 and enter $c(P2)$ there |

| WQ      | Reset Q and write contents of WAs into Q                                                                                                       |

| WS      | Reset S and write contents of WAs 12 through 1 into S                                                                                          |

| WSC     | Reset addressed flip-flop register and write contents of WAs into it                                                                           |

| WX, WX* | Write contents of WAs into X                                                                                                                   |

| WY      | Reset Y, X and CI flip-flop and write contents of WAs into Y $\Delta$                                                                          |

| WY*     | Write contents of WAs into Y                                                                                                                   |

| WZ      | Reset Z and write contents of WAs into Z                                                                                                       |

| WOVI    | Inhibit program interruption at end of current instruction in case of overflow or underflow                                                    |

| wovc    | Increment or decrement OVCTR by executing-next PINC or MINC                                                                                    |

| WOVR    | Deliver counter overflow or underflow to appropriate priority<br>input as selected by the content of register S                                |

| NOTES:  | $\triangle$ * indicates that read or write signal generated by that control pulse is 1 µsec long rather than 0.75 µsec                         |

|         | BR1, BR2, STAGE 1, STAGE 2 and LOOP Counter<br>will be discussed in a later issue when describing the<br>SQG                                   |

|         | 3 For editing operation see table 1-5                                                                                                          |

| Instruction   | Action<br>1 3        | Action<br>2        | Action<br>3    | Action<br>4    | Action<br>5           | Action<br>6  | Action<br>7           | Action<br>8              | Action<br>9     | Action<br>10                  | Action<br>11                                        | Action<br>12 | Figure Num<br>(Page Num) |

|---------------|----------------------|--------------------|----------------|----------------|-----------------------|--------------|-----------------------|--------------------------|-----------------|-------------------------------|-----------------------------------------------------|--------------|--------------------------|

| STD2          | RZ<br>WS<br>WY<br>CI | NO<br>ACTION       | CLC*           | RU<br>WZ       | NO<br>ACTION          | NO<br>ACTION | RSC<br>RG<br>WB<br>WP | GP<br>TP                 | RB<br>WSC<br>WG | NO<br>ACTION                  | (NISQ)                                              |              | 2-1<br>2-2               |

|               | WP                   |                    |                |                |                       |              |                       |                          |                 |                               |                                                     |              | (2-7)<br>(2-11           |

| TCO           | RB<br>WS             | NO<br>ACTION       | CLG*           | RA<br>WOVI     | NO<br>ACTION          | NO<br>ACTION | RG<br>RSC             | GP<br>TP                 | RB<br>WSC       | RU<br>₩Z                      | (NISQ)                                              | >            | 2-3                      |

| CODE 0 🛆      | WY<br>CI<br>WP       |                    |                |                |                       |              | WB<br>WP              | RZ<br>WQ                 | WG              |                               |                                                     |              | (2-14                    |

| хсно          | RB<br>WS             | RA                 | CLG*           | WP2            | NO<br>ACTION          | NO<br>ACTION | RSC<br>RG             | GP<br>TP                 | RA<br>WSC       | RB<br>WA                      | (ST2)                                               |              | 2-4                      |

| CODE 3 🛕      | WP                   | WP A               |                |                | ACTION                | Rentin       | WB<br>WP              |                          | WG<br>RP2       | WOWI                          |                                                     |              | (2-17                    |

| CS0           | RB                   | NO                 | CLG≄           | NO             | NO                    | NO           | RSC                   | GP                       | RB              | RC                            | (ST2)                                               |              | 2-5                      |

| CODE 4 🛆      | WS<br>WP             | ACTION             |                | ACTION         | ACTION                | ACTION       | RG<br>WB<br>WP        | TP                       | WSC<br>WG       | WA<br>WOVI                    |                                                     |              |                          |

| TSO           | RB                   | RA                 | CLC*           | NO             | NO                    | NO           | NO                    | GP                       | RB              | RA                            | (ST2)                                               |              | (2-19                    |

|               | WS<br>WP             | WB<br>WP           |                | ACTION         | ACTION                | ACTION       | ACTION                |                          | WSC<br>WG       | WOVI                          |                                                     |              | (2-2)                    |

| CODE 5 🛆      |                      | TOV                |                | RZ<br>WY<br>CI | R1 R1C<br>or<br>WA WA |              | RU<br>WZ              | 1                        |                 |                               | ·                                                   |              | 2-7                      |

| MSKO          | RB<br>WS<br>WP       | RA<br>WB           | CLG≎           | RC<br>WY       | NO<br>ACTION          | NO<br>ACTION | RSC<br>RG<br>WB       | RU<br>RC<br>WA           | NO<br>ACTION    | RA<br>WB                      | RC<br>WA<br>WOVI                                    |              | 2-8                      |

| CODE 7 🛆      |                      |                    |                |                | · ·                   |              | WP                    | GP<br>TP                 |                 |                               | (ST2)                                               |              | (2-25                    |

| ADO           | RB<br>WS<br>WP       | RA<br>WY           | CLG\$          | NO<br>ACTION   | NO<br>ACTION          | NO<br>ACTION | RSC<br>RC<br>WB       | CP<br>TP                 | RB<br>WSC<br>WG | NO<br>ACTION                  | RU<br>WA<br>WOVI                                    |              | 2-9                      |

| CODE 6        |                      |                    |                |                |                       |              | WP                    | RB<br>WX                 |                 |                               | WOVC<br>(ST2)                                       |              | (2-2                     |

| NDX0          | RB<br>WS             | NO<br>ACTION       | CLG*           | RA<br>WOVI     | NO<br>ACTION          | NO<br>ACTION | RSC<br>RG             | GP<br>TP                 | RB<br>WSC       | TRSM                          | (ST1)                                               |              | 2-1                      |

| CODE 2 🛆      | WP                   |                    |                | *011           | Renow                 | ACTION       | WB<br>WP              | 11                       | WG              |                               |                                                     |              | (2.2)                    |

| NDX1          | RZ                   | NO                 | CLG*           | RU             | NO                    | RB           | RSC                   | GP                       | RB              | NO                            | RU                                                  |              | 2-1                      |

|               | WS<br>WY<br>CI<br>WP | ACTION             |                | wz             | ACTION                | WY           | RC<br>WB<br>WP        | TP<br>RB<br>WX           | ₩SC<br>₩G       | ACTION                        | WB<br>WOVI<br>(NISQ)                                | •            |                          |

| CCS0          | RB                   | RZ                 | CLG*           | NO             | NO                    | RSC          |                       | 1                        | RB              | RC RIC                        | RU                                                  |              | 2-12                     |

|               | WS<br>WP             | WY                 |                | ACTION         | ACTION                | RG ···<br>WB |                       | GP RI<br>TP WX           | WSC<br>WG       | WA WA                         | (ST1)<br>WZ                                         |              |                          |

|               |                      |                    |                |                |                       | WP<br>TSGN   | RC<br>TMZ             | GP<br>TP                 |                 |                               |                                                     |              | (2-33)                   |

|               |                      |                    |                |                |                       |              | RB<br>TMZ             | R2 R1<br>WX R2<br>GP WX  |                 | RB RIC<br>WA WA               |                                                     |              | 2-14                     |

| CODE 1        |                      |                    |                |                |                       |              |                       | TP GP<br>TP              |                 |                               |                                                     |              | (2-35)                   |

| CCSI          | RZ<br>WS             | NO<br>ACTION       | CLG*           | RU<br>WZ       | RA<br>WY              | NO<br>ACTION | RSC                   | RU<br>WB                 | NO<br>ACTION    | RC<br>WA                      | RG<br>RSC                                           |              | 2-1                      |

| CODE 1        | WY<br>CI<br>WP       |                    |                |                | CI                    |              | WB<br>WP              | GP<br>TP                 |                 | WOVI                          | WB<br>(NISQ)                                        |              |                          |

| 6110          |                      |                    |                |                |                       | -            |                       |                          |                 |                               |                                                     |              | (2-38                    |

| SUO<br>CODE 6 | RB<br>WS<br>WP       | RA<br>WY           | CLG*           | NO<br>ACTION   | NO<br>ACTION          | NO<br>ACTION | RSC<br>RG<br>WB<br>WP | GP<br>TP<br>RC<br>WX     | RB<br>WSC<br>WG | NO<br>ACTION                  | RU<br>WA<br>WOVI<br>WOVC<br>(ST2)                   |              | 2-1                      |

| MP0           | RB                   | RA                 | RSC            | RB             | RLP                   | NO           | RG                    | CP                       | RU              | RA RA                         | WALP                                                |              | 2-20                     |

|               | ₩S<br>₩P             | WB<br>CLG≄<br>TSGN | WG             | WLP<br>RC      | WA                    | ACTION       | WY<br>WP<br>RG<br>WB  | TP<br>RC<br>WY<br>GP     | WB<br>TSGN2     | WLP RB 14<br>TSGN WLP<br>TSGN | (STI)   RI<br>or   RIC<br>RU   WALP<br>WALP   (STI) |              | (2-48)                   |

|               | A Indicator Incl     | ruction Code - not | Subinstruction | WLP            | 3 WP at Ac            | tion 1 for   | WP                    | TP<br>WP suppressed if H |                 |                               | (ST1)                                               |              | (2-50)                   |

(

# CONFIDENTIAL

### FR-2-102A

### TABLE 2-5

Control Pulses for all Subinstructions

C

2

1

### Control Pulses for all Subinstructions

| Instruction                  | Action A                    | Action<br>2        | Action<br>3              | Action<br>4  | Action<br>5    | Action<br>6              | Action<br>7           | Action<br>8              | Action<br>9           | Action<br>10       | Action<br>11                     | Action<br>12 | Figure Num<br>(Page Numb |

|------------------------------|-----------------------------|--------------------|--------------------------|--------------|----------------|--------------------------|-----------------------|--------------------------|-----------------------|--------------------|----------------------------------|--------------|--------------------------|

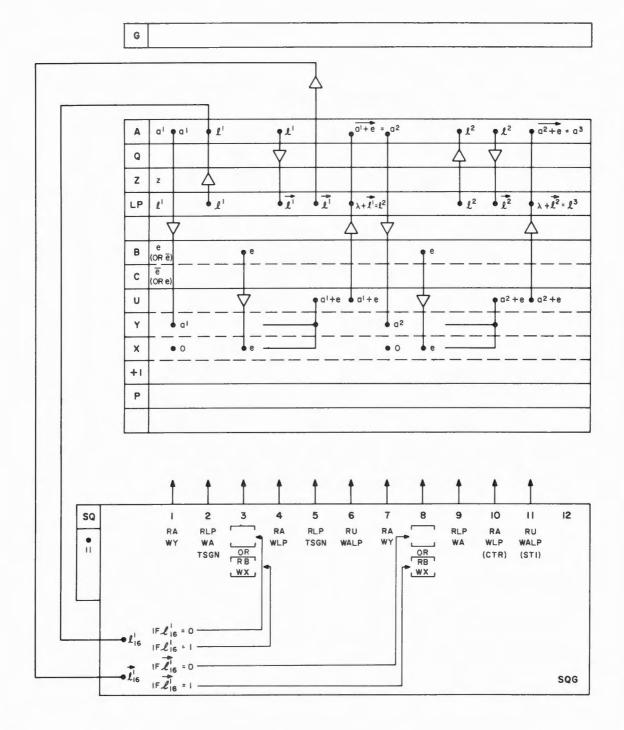

|                              | RA<br>WY<br>No WP           | RLP<br>WA<br>TSGN  | NO<br>ACTION<br>or<br>RB | RA<br>WLP    | RLP<br>(TSGN)  | RU<br>WALP               | RA<br>WY              | NO<br>ACTION<br>or<br>RB | RLP<br>WA             | RA<br>WLP<br>(CTR) | RU<br>WALP<br>(ST1)              |              | 2-24                     |

| A                            |                             |                    | WX                       |              |                |                          |                       | wx                       |                       |                    |                                  |              | (2-52)                   |

|                              | RZ<br>WS<br>WY<br>CI<br>WP  | RLP<br>TSGN        | CLG≄                     | RU<br>WZ     | RA<br>WY       | NO<br>ACTION<br>or<br>RB | RG<br>RSC<br>WB<br>WP | RLP<br>WA<br>GP<br>TP    | RB<br>WSC<br>WG       | . RA<br>WLP        | RU<br>WALP<br>(NISQ)             |              | (2-25                    |

| DV0                          | RB                          | RA                 | RSC                      | RC           | RI             | WX<br>R <b>A</b>         | RG                    | RB                       | RLP   NO<br>R2 ACTION | RB RC              | Rİ                               |              | 2-28 2-                  |

| CODE 5 🛆                     | WS<br>WP                    | WB<br>CLG*<br>TSGN | WG                       | WA<br>       | WLP<br>        | wo                       | WG<br>WP<br>(TSGN)    | WA<br>GP<br>TP           | WB                    | WLP WA             | WB<br>(ST1)                      |              | 2-30 2                   |

| ▲                            |                             |                    |                          | ACTION       | WLP            |                          |                       |                          | 1                     |                    |                                  |              | (2-67) (2-               |

| DVI                          | R22<br>WS<br>WP             | RQ<br>WG           | RG<br>R5B<br>WQ<br>WY    | RA<br>WX     | RLP<br>(TSGN2) | NO<br>ACTION             | RU<br>(TSGN)          | NO<br>ACTION             | RB<br>RSB<br>WG<br>RB | RG<br>WB<br>(TSGN) | (ST1)<br>or<br>RC<br>WA<br>(ST1) |              | $\frac{2-32}{(2-69)}$    |

| ▲                            |                             |                    |                          |              |                |                          |                       | WQ                       | ₩G                    |                    | (ST2) (ST2)                      |              | (2-70)                   |

| RPTI                         | R24<br>WY<br>WS<br>CI<br>WP | NO<br>ACTION       | CLG*                     | NO<br>ACTION | NO<br>ACTION   | NO<br>ACTION             | NO<br>ACTION          | NO<br>ACTION             | RZ<br>WG              | RU<br>WZ           | (ST1)<br>(ST2)                   |              | 2-34                     |

|                              |                             |                    |                          |              |                |                          |                       |                          |                       | NO                 | (67.3)                           |              | (2-82)                   |

| RPT3                         | RZ<br>WS<br>WP              | RRP <b>A</b><br>WZ | RZ<br>CLG*<br>KRPT       | NO<br>ACTION | NO<br>ACTION   | NO<br>ACTION             | NO<br>ACTION          | NO<br>ACTION             | RB<br>WSC<br>WG       | NO<br>ACTION       | (ST2)                            |              |                          |

|                              |                             |                    |                          |              |                |                          |                       |                          |                       |                    |                                  |              | (2-83)                   |

| RSM<br>(NDX1 of<br>NDX 0025) | R24<br>WS<br>WP             | NO<br>ACTION       | CTC+                     | NO<br>ACTION | NO<br>ACTION   | NO<br>ACTION             | RG<br>WZ              | NO<br>ACTION             | NO<br>ACTION          | NO<br>ACTION       | (NISQ)                           |              | 2-36                     |

| PINC                         | RSCT                        | NO                 | CLG*                     | RI 🔬         | NO             | RG*                      | TP                    | WP                       | RU*                   | RU*                | NO                               |              | (2-85)                   |

| FINC                         | WS<br>WP                    | ACTION             | 020                      | WY           | ACTION         | WX*<br>WP<br>CI          |                       |                          | CLG+<br>WP+           | WG*<br>WOVR        | ACTION                           |              |                          |

|                              |                             |                    |                          |              |                |                          |                       |                          |                       |                    |                                  |              | (2-87)                   |

| MINC                         | RSCT<br>WS<br>WP            | NO<br>ACTION       | CLG*                     | RIC<br>WY    | NO<br>ACTION   | RG*<br>WX*<br>WP<br>CI   | TP                    | WP                       | RU*<br>CLG*<br>WP*    | RU*<br>₩G≉<br>₩OVR | NO<br>ACTION                     |              | 2-38                     |

|                              |                             |                    |                          |              |                |                          |                       |                          |                       |                    |                                  |              | (2-89)                   |

| SHINC                        | RSCT<br>WS<br>WP            | NO<br>ACTION       | CLG*                     | WY           | NO<br>ACTION   | RG*<br>WY*<br>WX*<br>WP  | TP                    | WP                       | RU*<br>CLG*<br>WP*    | RU≑<br>₩G≠<br>₩OVR | NO<br>ACTION                     |              | 2-39                     |

|                              |                             |                    |                          |              |                | TSGN3                    |                       |                          |                       |                    |                                  |              | (2-91)                   |

| SHANC                        | RSCT<br>WS<br>WP            | NO<br>ACTION       | CLG≠                     | WY           | NO<br>ACTION   | RG*<br>WY*<br>WX*<br>WP  | TP<br>CI              | WP                       | RU*<br>CLG*<br>WP*    | RU≑<br>WG≑<br>WOVR | NO<br>ACTION                     |              | 2-41                     |

|                              |                             |                    |                          |              |                | TSGN3                    |                       |                          |                       | <u> </u>           |                                  |              | (2-94)                   |

| OINC                         | WS<br>WP                    | NO<br>ACTION       | CLG≄                     | NO<br>ACTION | NO<br>ACTION   | NO<br>ACTION             | RSC<br>RG             | NO<br>ACTION             | NO<br>ACTION          | NO<br>ACTION       | NO<br>ACTION                     |              | 2-42                     |

|                              |                             |                    |                          |              |                |                          |                       | 1                        |                       |                    |                                  |              | (2-96                    |

| LINC                         | ₩S<br>₩P                    | NO<br>ACTION       | CLG≑                     | NO<br>ACTION | NO<br>ACTION   | NO<br>ACTION             | WSC<br>WG<br>WP       | GP                       | NO<br>ACTION          | NO<br>ACTION       | NO<br>ACTION                     |              | 2-43                     |

|                              |                             |                    |                          |              |                |                          |                       |                          |                       |                    |                                  |              | (2-97                    |

Control pulse symbols followed by \* indicate that the pulse takes 1 µsec rather than 0.75 µsec (also indicated with S).

Changed 29 May 1964

# CONFIDENTIAL

#### FR-2-102A

### TABLE 2-5 (cont)

Rl supplessed at Action 4 and CI generated at Action 6 if register 0047, 50, 51, 52 or 53 is addressed.

FR-2-102A

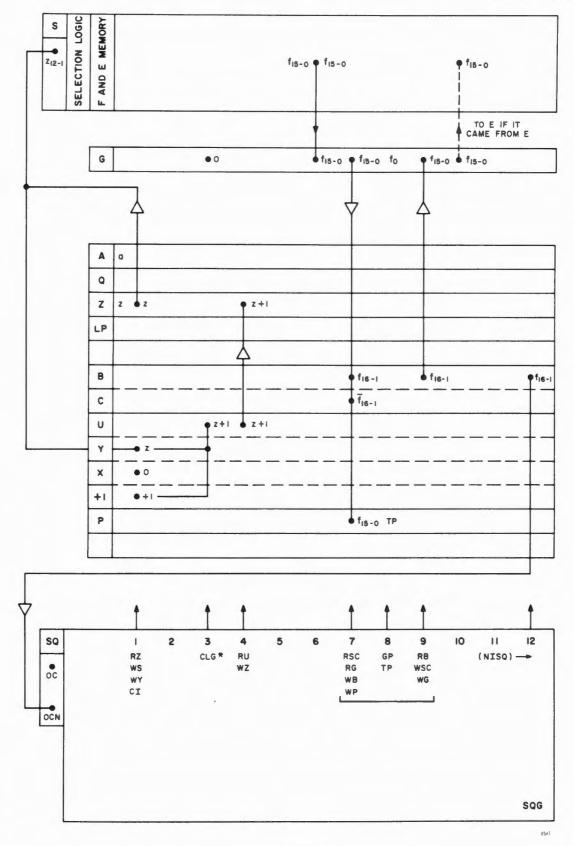

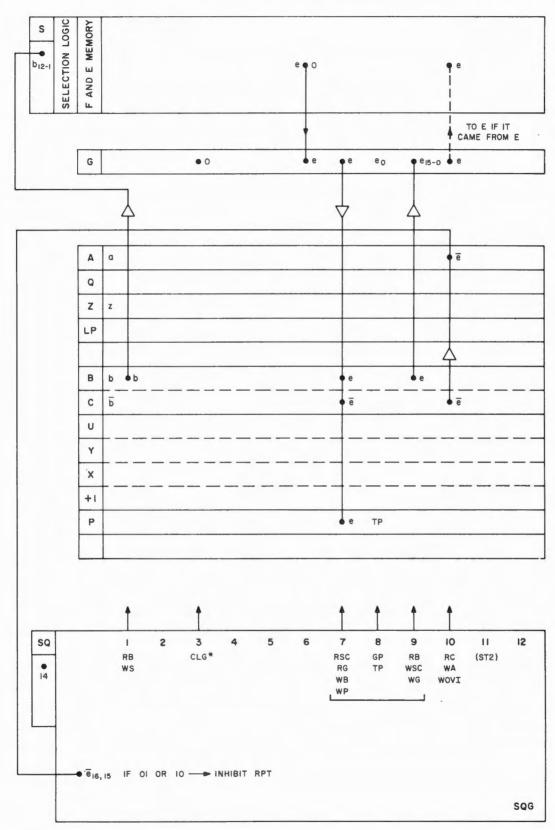

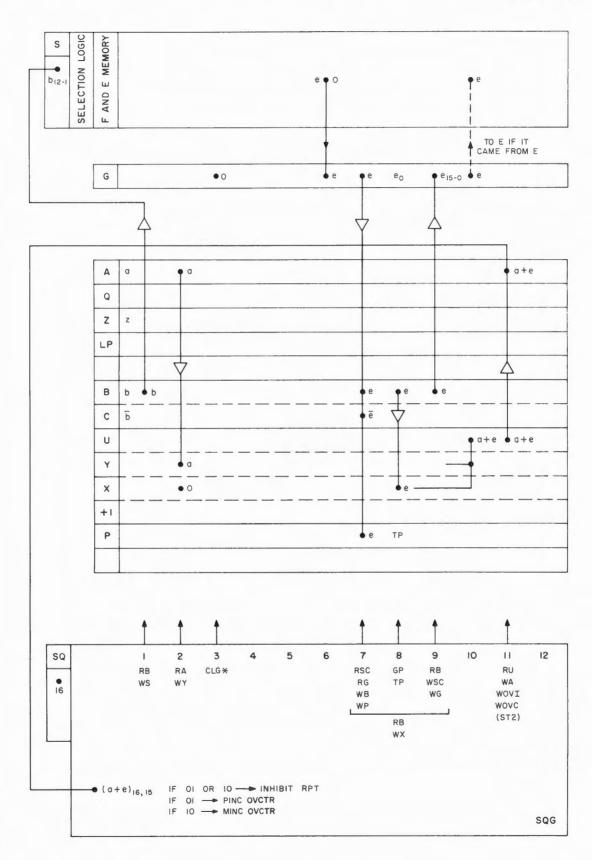

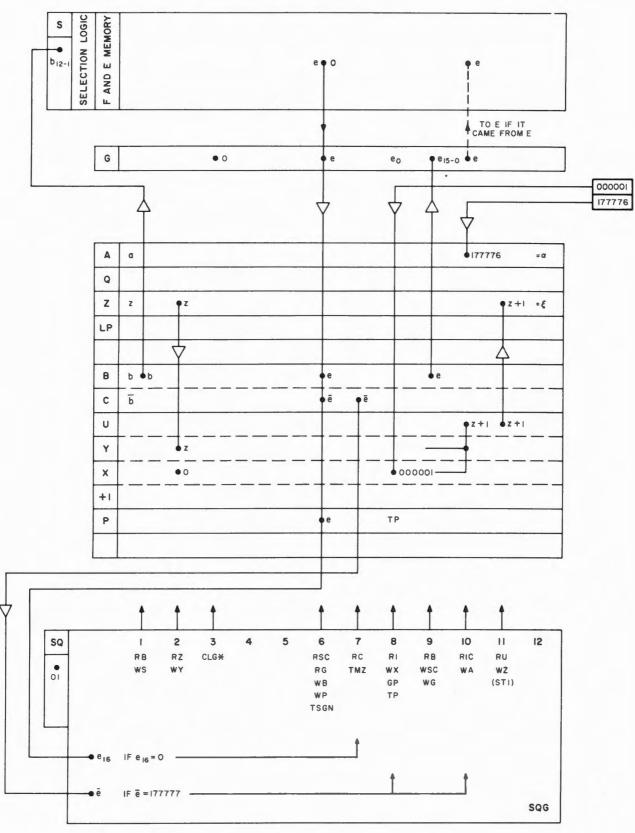

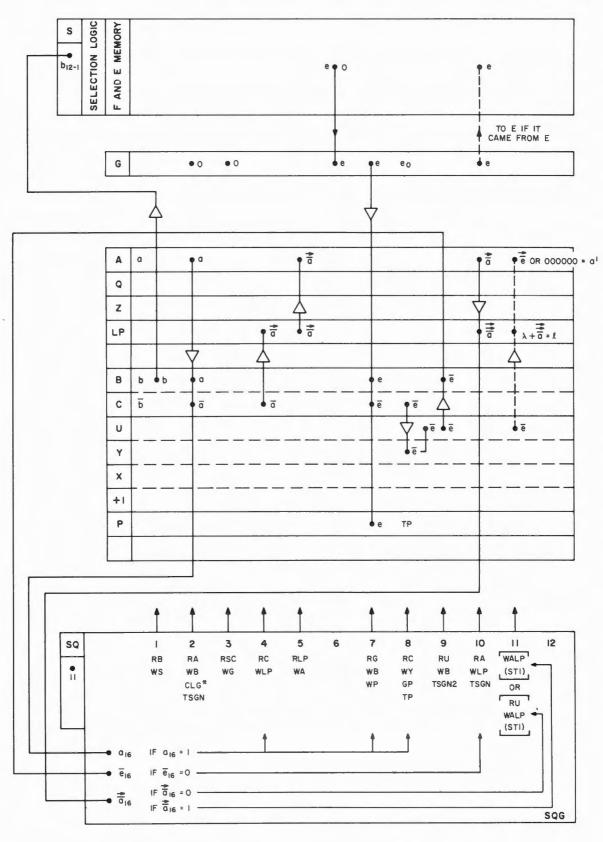

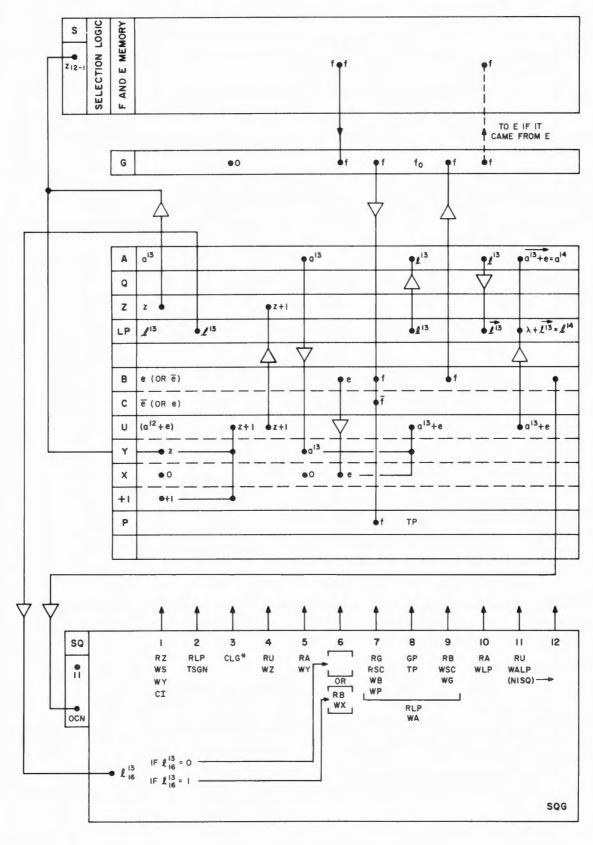

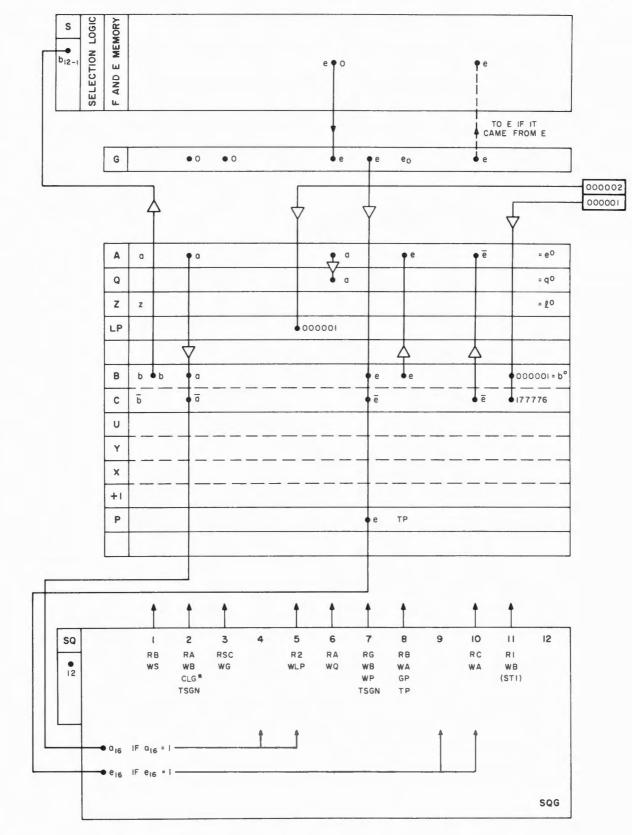

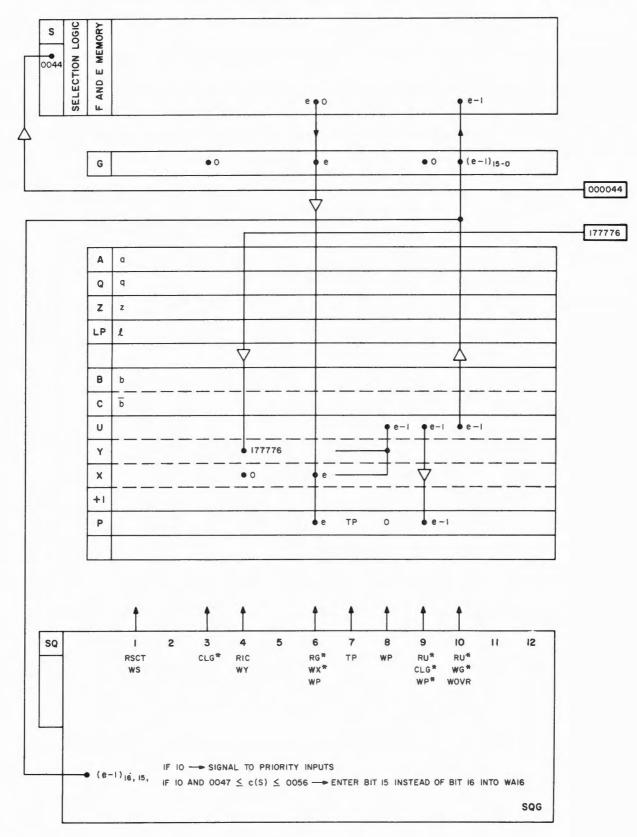

Figure 2-1. Subinstruction STD2 (Example for  $z \ge 0020$ )

Changed 29 May 1964

# CONFIDENTIAL

FR-2-102A

2 - 8

15-33. The write amplifiers (WA's) of figure 15-7 are symbolized in figure 2-1 by triangles placed into the flow lines. Registers are always signified by capital letters, their contents by small letters. Furthermore,  $\overline{a}$  means complement of a. Control pulse symbols in parentheses indicate signals internal to the SQG. In the text, c(A) means content of A, b(A) means previous (before) content of (A),  $\overline{c}$ (A) indicates the complemented c(A), and  $c^{e}$ (A) indicates the edited c(A). Basic instructions and Extra Code Instructions, which belong in the category of Regular Instructions, are described first. Paragraphs 2-6 through 2-77 deal with normal cases, i. e. instructions of which the relevant address K refers to a location in the F or E memory. (Special attention is required for any address K which refers to an editing location.) Instructions with address K referring to registers A, Q, Z, and LP (special cases) are discussed in paragraphs 2-78 through 2-93 together with some other special cases of NDX K instructions.

#### 2-6. BASIC INSTRUCTIONS

#### 2-7. COMMON CHARACTERISTICS

2-8. A program portion written in basic machine language consists of a series of Basic Instructions and it is the responsibility of each instruction to make sure that its execution will be followed by the execution of another (the proper) instruction. The relevant address (figure 15-12) of each Basic Instruction (table 15-12) is normally used to specify the location of data to be worked with. In order to specify the sequence in which Basic Instructions are to be executed, the instructions are simply stored at locations in numerical order. By incrementing (by one) the address of an instruction presently executed, the location of the instruction to be executed next is defined. The address of the instruction to be executed next (the "next" address) is stored in register Z, the program counter. During the execution of an instruction, this address code in register Z is incremented (by one) in order to represent the proper address of the "next" instruction at the start of the subsequent instruction. In case the normal sequence of instruction is inter-

CONFIDENTIAL

Changed 29 May 1964

FR-2-102A

rupted, the "next" address is stored in register Q for later use. Another duty of a Basic Instruction is to enter the entire code of the subsequent instruction (the instruction to be executed next) into register B so that it will be available during its execution. Finally, each Basic Instruction (in fact, all Regular Instructions) must enter the order code of the subsequent instruction into the SQ register in order to initiate its execution. (Involuntary Instructions cannot be written into a program and are free of the duties mentioned above.)

2-9. Most Basic Instructions consist of two subinstructions. Normally the first subinstruction carries out the specific task of the instruction, such as, adding data, transferring information, etc. The second subinstruction performs the common duties required of the instruction. Usually the second subinstruction is STD2 (Standard Subinstruction Two). Instruction flow chart figure 2-1 illustrates the execution of STD2 for  $z \ge 0020$ . In the box representing the sequence generator (SQG), four control pulses (RZ, WS, WY, and CI) are listed in the first column, indicating that these four pulses are generated at Action 1. The control pulses generated at each Action are listed in table 2-2. Pulse RZ reads the contents of register Z, i.e. the "next" address (z), into the write amplifiers. Note that if L is the location of the instruction being executed, then z = c(Z) = (L + 1). Pulse WS resets (clears) the S register then writes the "next" address into it. Pulse WY clears input registers X and Y of the Adder, and writes c(Z) into Y. Control pulse CI forces a carry into the Adder, thereby causing a one to be added to z. The sum (z + 1), i.e., the address "after the next" or the "second next" address, appears in output gates U with 3  $\mu$ sec. Now, (z + 1) = (L + 2). Control pulse CLG\*, at Action 3, resets register G as symbolized by the 0. At Action 4, pulse RU reads quantity (z + 1) to the write amplifiers, and pulse WZ clears Z and writes (z + 1) into it.

2-10. The content of register S (z, entered at Action 1) causes the selection logic to gate the proper location for readout and write-in. If the address stored in S is equal to or larger than 0020 (all data are normally given in octal numbers),

Changed 29 May 1964

CONFIDENTIAL

FR-2-102A

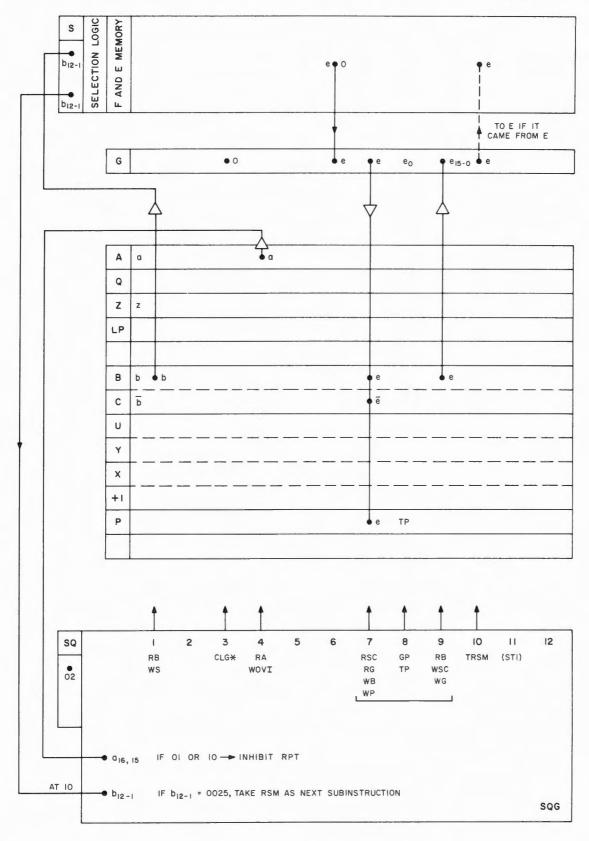

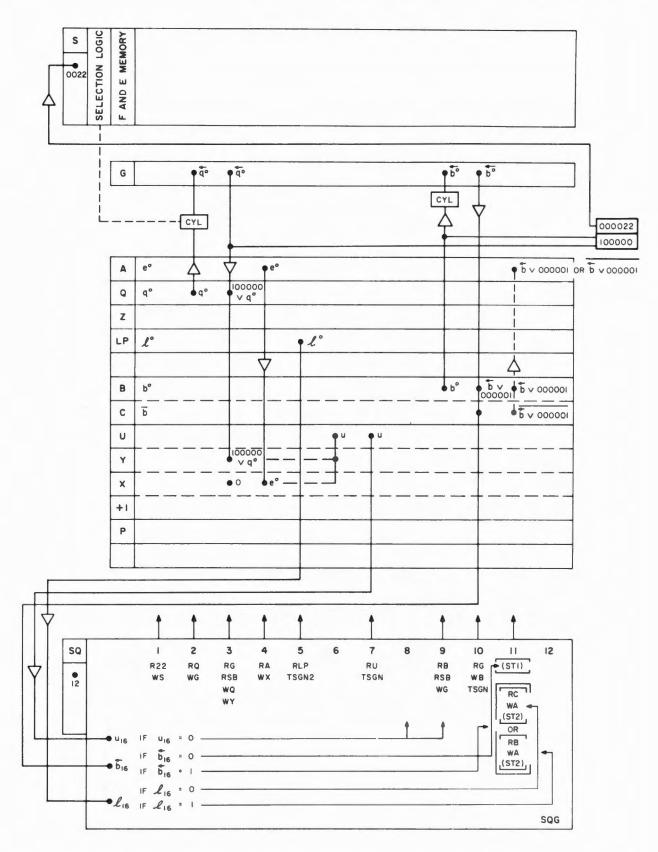

the corresponding location in the F or E memory will deposit its content (f or e) into register G during Action 6. If the address refers to a location in the E memory  $(0020 \le z \le 1777)$ , the z drivers of the E memory are energized during Actions 10 through 12 and any content of G is written into the addressed location in the E memory. If the address stored in S is equal to or smaller than 0017, a flip-flop register is addressed for readout or write-in, as shown in figure 2-2 for the case of z = 0001.

2-11. Actions 7, 8, and 9, as shown in figures 2-1 and 2-2, are common to most subinstructions. This group of control pulses is referred to as the standard memory inquiry cycle (STMIC) and is symbolized by the bracket underneath. Control pulses RG, WB, and WP transfer data to be worked with or the subsequent instruction f from G to B and P. The complement of f appears at the C side of buffer-register B. Control pulse RSC has no effect unless a flip-flop register is addressed. Pulse GP gates the new parity bit (generated by the parity pyramid) for the word stored at register P into bit position 0 of G, as symbolized by f in G. Pulse TP (test parity) causes an alarm in case the parity of the word in register P is incorrect. The parity test is symbolized by TP in register P. (The operation of the Parity Block is described in paragraphs 15-34 through 15-36. In Issue 2 it is always assumed that the parity is correct and no consequences on incorrect parity are discussed. Control pulses RB and WG transfer the content of B into bit positions 1 through 15 of G. Pulse WSC has no effect since a flip-flop register has not been addressed.

2-12. It is worthwhile to remember that whenever a word is transferred from register G to any other flip-flop register except P, bit 15 of G is entered into bit positions 16 and 15 of the other register, as shown in table 1-6. Whenever a word is transferred from a flip-flop register to register G, bit 16 from the flip-flop register moves into bit position 15 of G and bit 15 of the flip-flop register gets lost. The parity bit location in position 0 of register G can only be transferred into position 0 of register P. Any new parity bit is fed directly into bit position 0

Changed 29 May 1964

CONFIDENTIAL

FR-2-102A

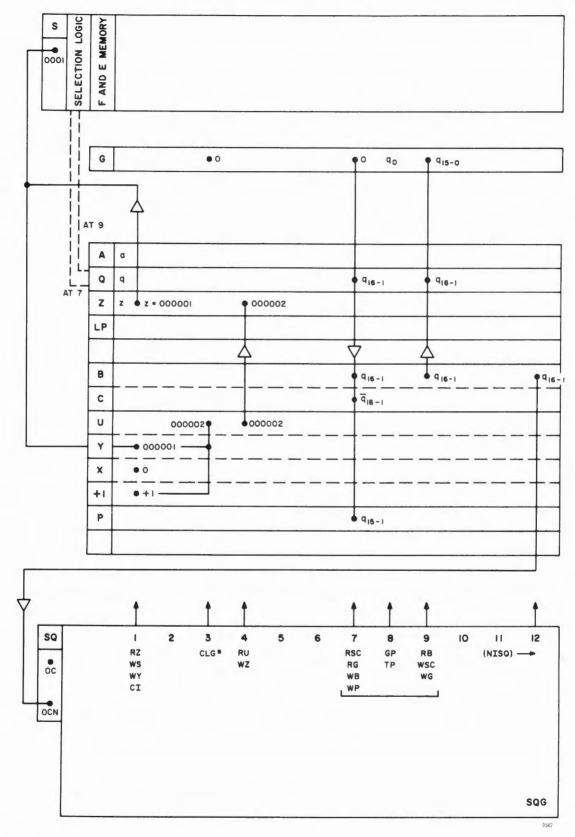

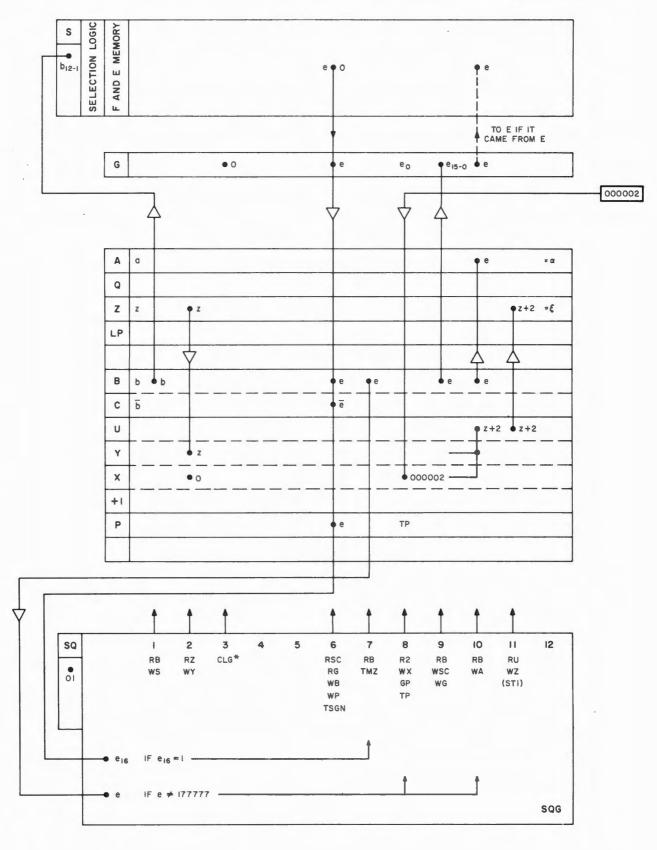

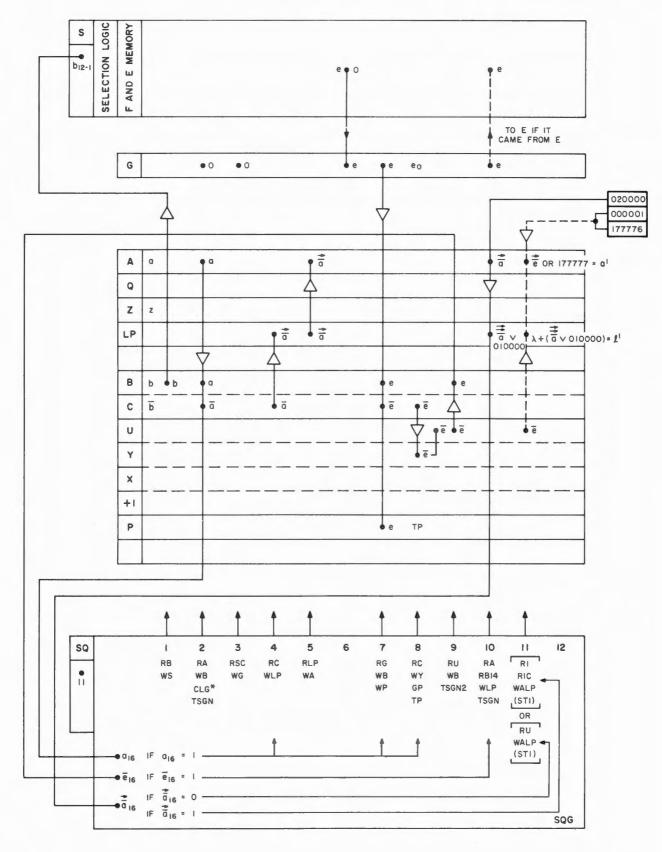

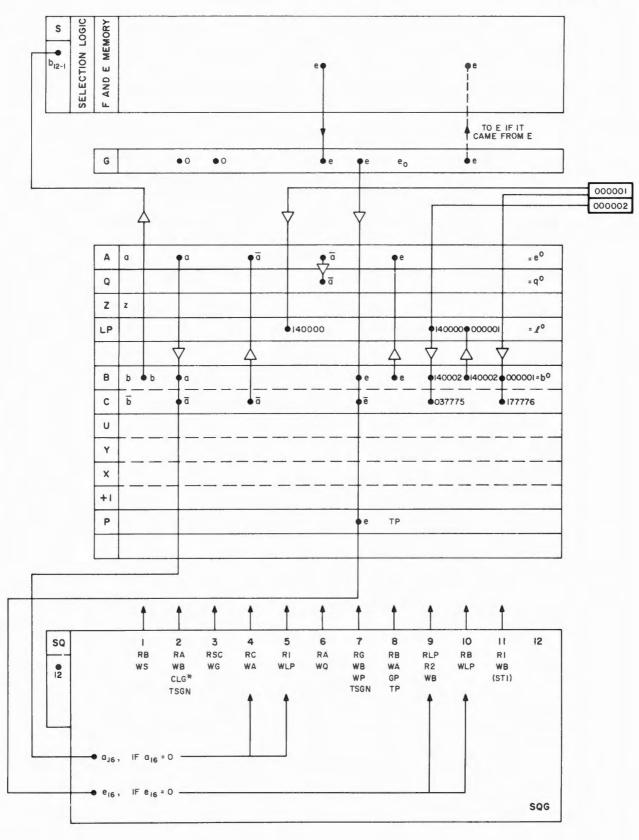

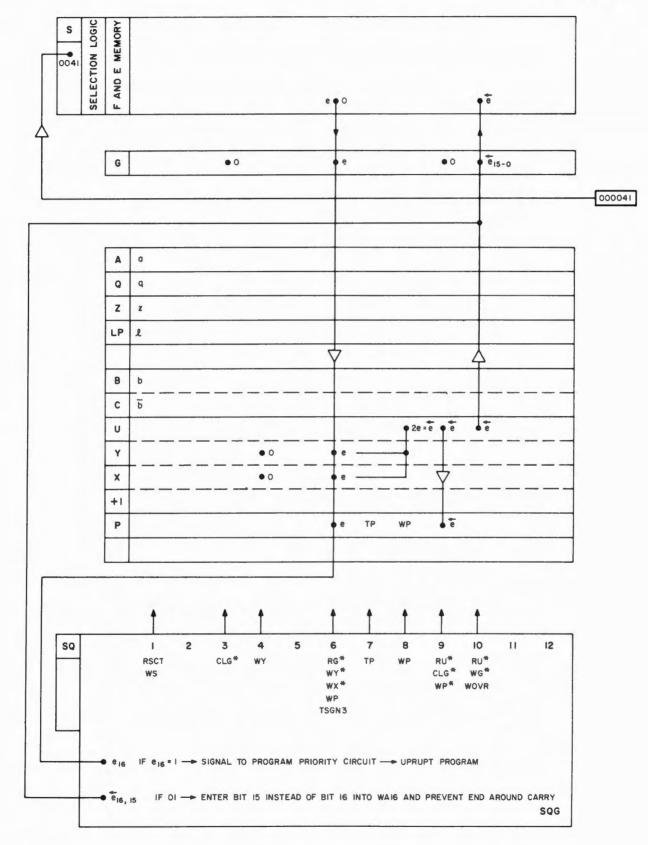

Figure 2-2. Subinstruction STD2 (Example for z = 0001)

FR-2-102A

of G. For example, the word 32614 stored in the F or E memory becomes 032614 when transferred into the accumulator (A), and word 62614 becomes 162614.

2-13. Control pulse NISQ generated at Action 11 causes the SQG to transfer (at Action 12, as indicated by an arrow) the order code OCN of the instruction to be executed next from bit positions 16 through 13 of B to SQ. If the transfer of data or of the subsequent instruction (paragraph 2-11) is not established by means of STD2 (i.e., if STD2 is not the second subinstruction), control pulse NISQ must be contained in another concluding subinstruction.

2-14. Figure 2-2 is very similar to figure 2-1 except that the addressed register er is Q, a flip-flop register, instead of a location in the F or E memory. Control pulse RG at Action 7 has no real effect since register G is cleared at Action 3 and not loaded from the F or E memory thereafter. Since the address stored in S (0001) is lower than 0020, the selection logic signals the SQG to gate the proper flip-flop register for readout and write-in during Actions 7 and 9. This is indicated by dotted lines leading from the selection logic to register Q. Pulse RSC goes to all addressable flip-flop registers but is only able to read out the one which is addressed simultaneously. Control pulse WSC also goes to all addressable flipflop registers, but only that register which is addressed at the same time is enabled to accept data. Since  $c(S) \leq 0027$ , control pulse TP is prevented from causing an alarm as stated in paragraph 15-35.

Changed 29 May 1964

CONFIDENTIAL

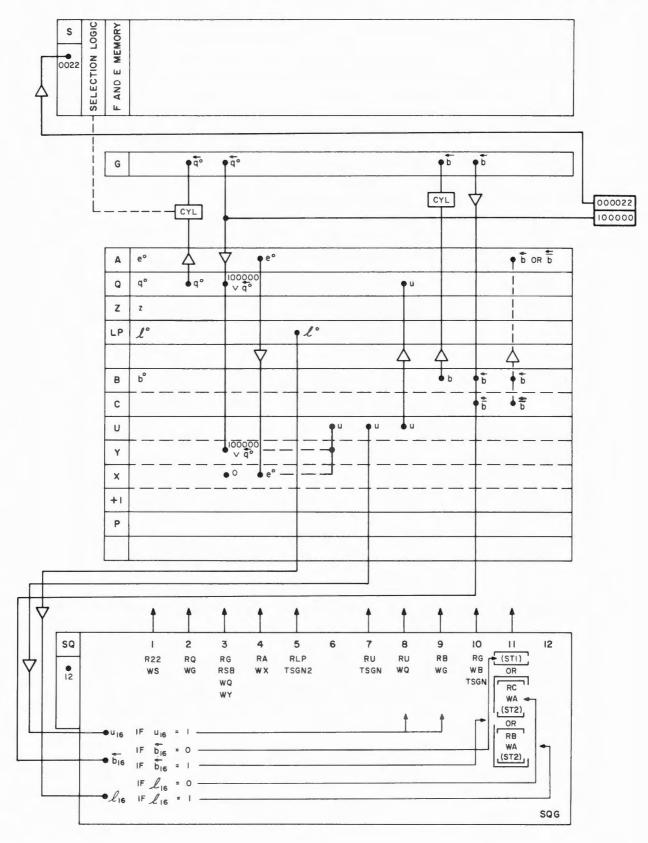

#### 2-15. INSTRUCTION TC K (Transfer Control to K, Order Code 0)

2-16. TC K means: transfer program control to the instruction stored at location K. The entire operation TC K (for  $0020 \le K$ ) can be formulated as follows:

- (1) Execute next the instruction located at K instead of at z = (L + 1).

- (2) Set c(Z) = (TC K) + 1 = b(B) + 1.

- (3) Set c(Q) = z = b(Z), z = L + 1.

- (4) Restore c(K) = b(K), if 0024 ≤ K ≤ 1777.

If 0020 ≤ K ≤ 0023, then c(K) = b<sup>e</sup>(K); b<sup>e</sup> means before content edited, i.e. cycled or shifted.

The TC K instruction consists of only one subinstruction, TCO.

2-17. Figure 2-3 illustrates the execution of TC 6145 as an example. Assuming that the present instruction is located at address 2670 of the F memory, the command TC 6145 means that the instruction f located at 6145 shall be executed next instead of the instruction located at z = 2671, the "next" instruction of the present sequence of instructions. Instruction f might be the first instruction of another program, of a subroutine, etc. The address (z) of the "next" instruction is transferred from register Z to Q in order to be available in case a return to the original sequence of instructions is requested. The instruction TC Q transfers control to Q. After the execution of TC 6145, register Q contains 002671, which in fact is the instruction TC z, or TC 2671 in the case of the example, since the order code stored in bit positions 16 through 13 consists of four ZERO's.

2-18. The entire code of instruction TC 6145 (06145) was entered into register B during the execution of the previous instruction, and B now contains b = 006145. The order code 00 was entered into register SQ at Action 12 of the previous instruction. In so doing, the SQG was set to execute a TC instruction. At Action 1 the relevant address 6145 contained in bit positions 12 through 1 of B is transferred to S and the selection logic gates a location with

Changed 29 May 1964

FR-2-102A

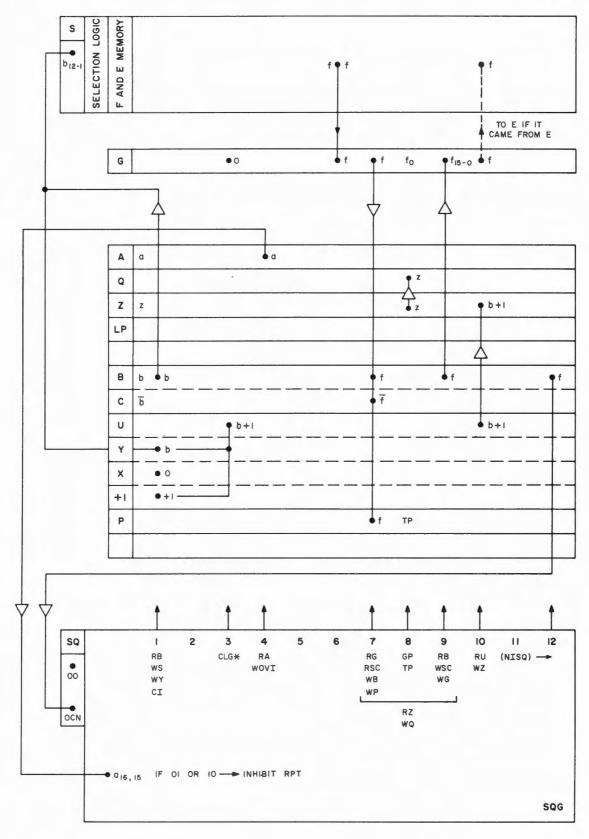

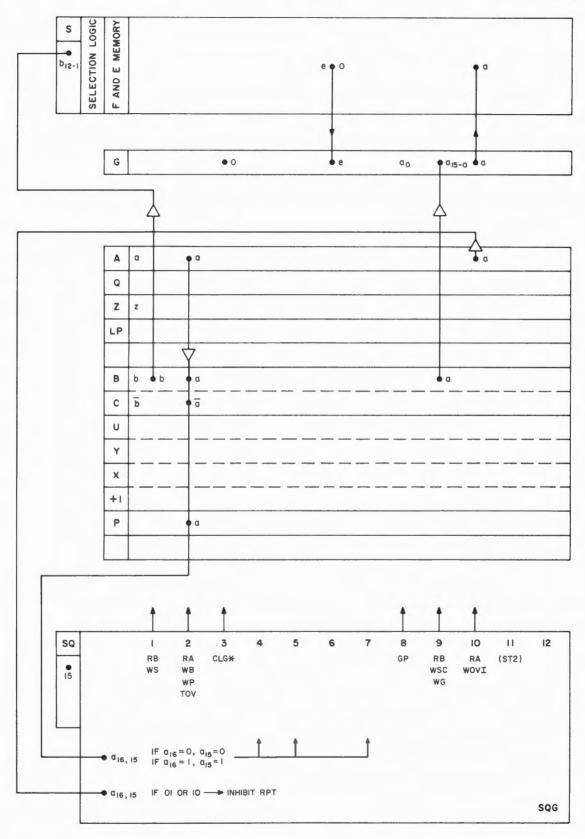

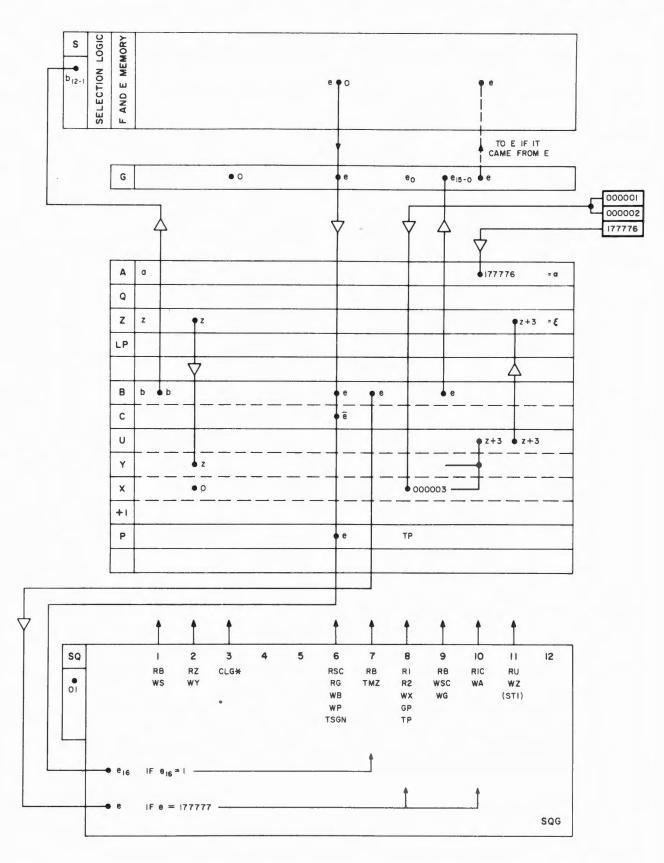

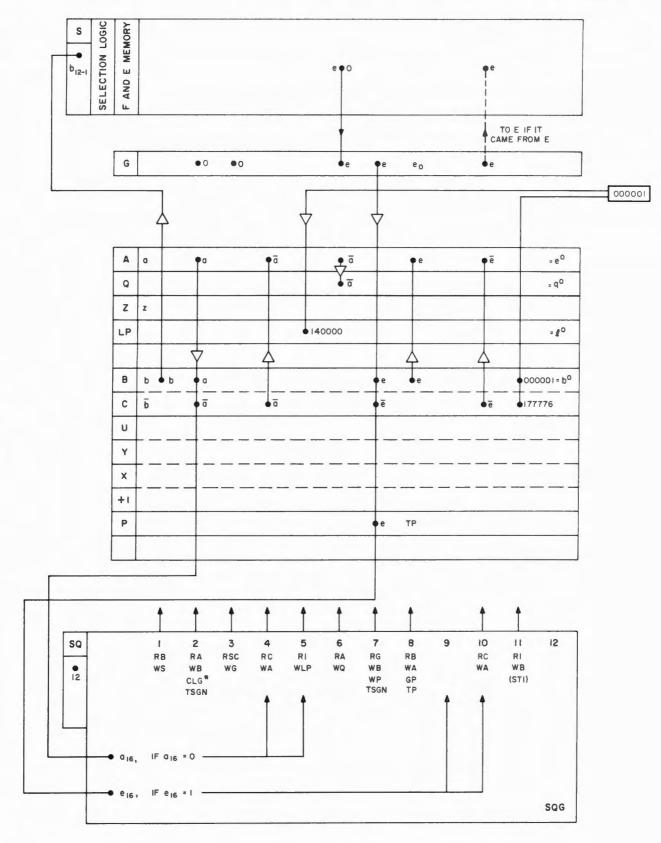

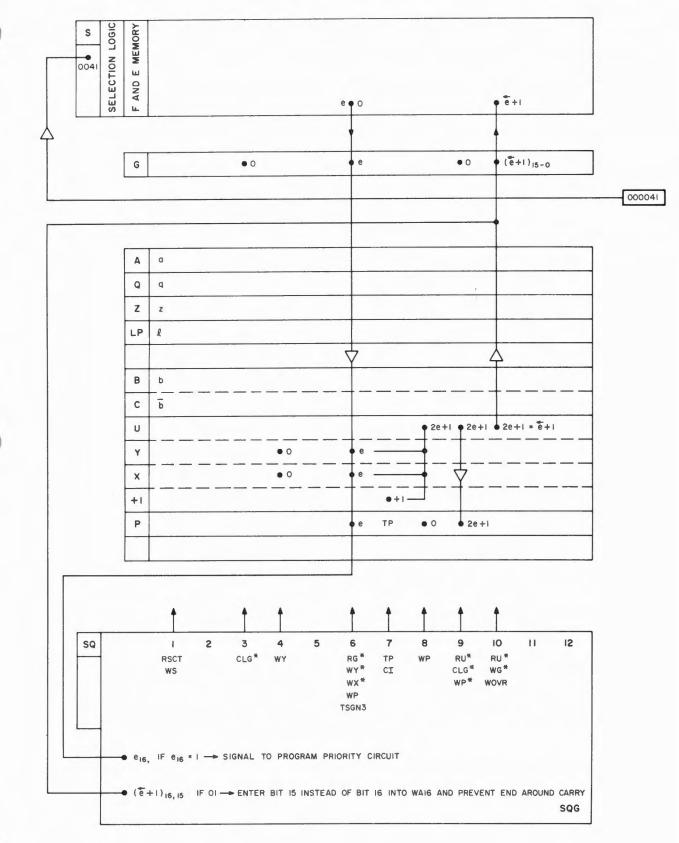

Figure 2-3. Subinstruction TC0

FR-2-102A

address 6145 for readout and write-in. The content of register BNK determines which location with address 6145 is selected. At the same time, the entire content of B is fed into Y, and X is cleared. Control pulse CI forces a one into the Adder, causing a one to be added to b. The sum (b + 1) = 006146is available at U within 3 µsec. At Action 3, register G is cleared. At Action 4, bits 16 and 15 contained in A are transferred to the SQG for test of overflow or underflow. Assuming that both bits are ZEROs, or that both bits are ONEs, control pulse WOVI has no consequence. In case the two bits are not equal, interrupt at the end of the current instruction is inhibited in order to save the overflow bit. The overflow bit would be lost in the process of transferring the content of A to location 0024 as requested by a program interruption. Actions 7, 8, and 9 of instruction TC K are very similar to the STMIC with the exception that control pulses RZ and WQ are added. The purpose of RZ and WQ is to transfer "next" address z = 2671 from Z to Q. Instruction f located at address 6145 is transferred from the F memory into register G at Action 6, and from G into B and P at Action 7. At Action 8, the parity of word f is tested, an alarm caused in case of incorrect parity, and a new parity bit  $(f_0)$  for quantity f is generated and entered into G. At Action 9, instruction f is returned to G. At Action 10, (b + 1) = 006146 is entered into Z and becomes the "next" address 6146. At Action 12, order code OC of instruction f is entered into register SQ to initiate the execution of instruction f. (If K refers to a flip-flop register, the STMIC has an effect similar to that shown in figure 2-2.)

2-19. INSTRUCTION XCH K (Exchange Data with Location K, Order Code 3)

2-20. XCH K means: exchange data contained in the accumulator (A) with data stored at location K. If K represents a location in F memory, then XCH transfers data from K to A but data in K remains undisturbed. Therefore, optional code CAF (Clear and Add F) may be used. The entire operation XCH K (for  $0020 \ge K$ ) can be formulated as follows:

# CONFIDENTIAL

FR-2-102A

(1) Set c(A) = b(K) and c(K) = b(A) if 0024 ≤ K ≤ 1777.

If 2000 ≤ K, set c(A) = b(K) only.

If 0020 ≤ K ≤ 0023, then c(K) = b<sup>e</sup>(A).

Remember that bit 15 (overflow bit) of A gets lost and that bit 16 (sign bit) of A moves into bit position 15 of K. Bit 16 of K moves into positions 16 and 15 of A.

(2) Execute-next the instruction located at z = (L + 1).

The XCH K instruction consists of two subinstructions; XCH0 and STD2.

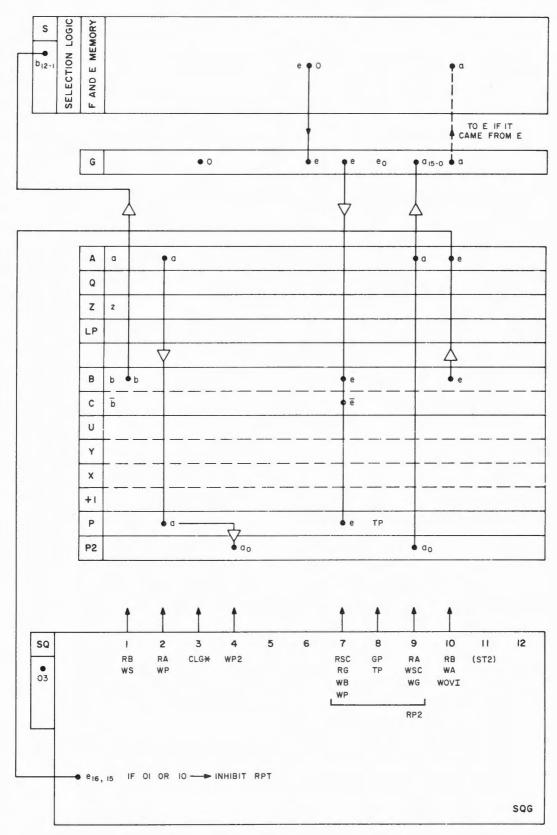

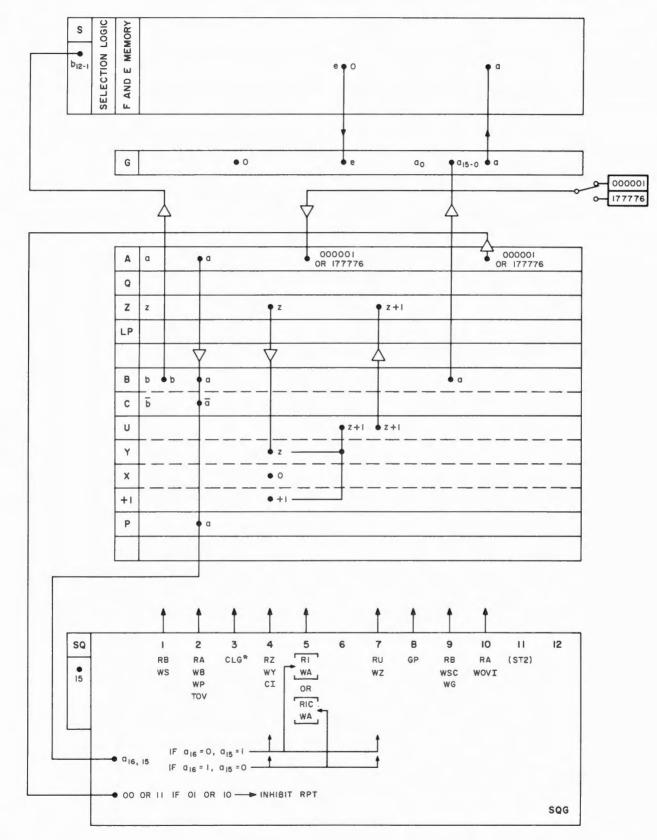

2 - 21.Figure 2-4 illustrates the execution of XCH 1063. The quantity (a) stored in A is to be exchanged with the quantity (e) stored at location 1063. During the execution of the previous instruction, the entire code of instruction XCH 1063 (31063) was entered into B (B now contains b = 031063), and order code 03 was entered into register SQ. At Action 1, the address contained in B is transferred to S and the selection logic gates location 1063 for readout and write-in. At Action 2, quantity a is read into P, and at Action 4, parity bit  $a_0$ , generated for quantity a, is entered into P2 for temporary storage. At Action 3, register G is cleared. Actions 7, 8, and 9 of subinstruction XCH0 are very similar to the STMIC with the exception that control pulse RP2 is added. Word e is transferred from location 1063 to G at Action 6, and from G into B and P at Action 7. At Action 8, the parity of word e is tested, an alarm caused in case of incorrect parity, and a new parity bit (e,) for quantity e is generated and entered into G. At Action 9, quantity a and parity bit a<sub>o</sub> are entered into G and written into location 1063 at Action 10. Also at Action 10, the quantity e is transferred from B to A, and bits 16 and 15 into the SQG for test of overflow or underflow. Since quantity e was taken from the E memory, normally no overflow or underflow in A is possible at that time. Control pulse ST2 causes the SQG to execute-next subinstruction STD2 in order to increment the program counter (Z) and to initiate the execution of the next instruction. (If K refers to a flip-flop register, Action 7 has an effect similar to that of Action 7 of figure 2-2. At Action 9, quantity a is written into the addressed flip-flop register, but ao is written into G.)

Changed 11 April 1963

CONFIDENTIAL

CONFIDENTIAL

FR-2-102A

Figure 2-4. Subinstruction XCH0

2-22. INSTRUCTION CS K (Clear A and Subtract Data in K, Order Code 4)

2-23. CS K means: clear the accumulator (A) and enter into it the complemented value of the quantity stored at location K. The entire operation CS K (for  $0020 \le K$ ) can be formulated as follows:

- (1) Set  $c(A) = \overline{b}(K)$ .

- (2) Restore c(K) = b(K) if  $0024 \le K \le 1777$ . If  $0020 \le K \le 0023$ , then  $c(K) = b^{e}(K)$ .

- (3) Execute-next the instruction located at z = (L + 1).

The CS K instruction consists of two subinstructions; CS0 and STD2.

Figure 2-5 illustrates the execution of CS 1021. Quantity e located 2-24. at 1021 is to be complemented and entered into A. During the execution of the previous instruction, the entire code of instruction CS 1021 (41021) was entered into B (B now contains b = 141021), and order code 14 was entered into register SQ. At Action 1, the address contained in B is transferred to S and the selection logic gates location 1021 for readout and write-in. At Action 3, register G is cleared, as usual. During the STMIC (Actions 7 to 9), data e is entered into B and P, and restored in G as usual. At Action 10, quantity e is entered into A by means of control pulses RC and WA. Control pulse WOVI transfers bits 16 and 15 of e into the SQG for test of overflow or underflow. Since quantity e was taken from the F or E memory, normally no overflow or underflow in A is possible at that time, therefore, WOVI is of no further consequence. Control pulse ST2 causes the SQG to execute-next subinstruction STD2, in order to increment the program counter (Z) and to initiate the execution of the next instruction. (If K refers to a flip-flop register, the STMIC has an effect similar to that shown in figure 2-2.)

2-25. INSTRUCTION TS K (Transfer Data to K, Order Code 5)

2-26.

TS K means: transfer the content of the accumulator (A) to location

CONFIDENTIAL

FR-2-102A

Figure 2-5. Subinstruction CS0

K. If K represents a location in the F memory, then TS K is equivalent to NOOP (No Operation). If A contains no overflow or underflow, execute-next the instruction at z = (L + 1). If A contains overflow or underflow, executenext the instruction at (L + 2), and enter the value plus-one or minus-one respectively into A. The "skip on overflow" feature is used chiefly in multiprecision operations. The entire operation TS K (for  $0020 \le K$ ) can be formulated as follows:

- (1) Set c(K) = b(A) for 0024 ≤ K ≤ 1777.

If 0020 ≤ K ≤ 0023, then c(K) = b<sup>e</sup>(A).

Remember that bit 15 of b(A) gets lost, and that bit 16 of b(A) moves into position 15 of c(K).

- (2a) If 000000 ≤ b(A) ≤ 037777, or

if 177777 ≥ b(A) ≥ 140000, then

keep c(A) = b(A) and execute-next the instruction located at

z = (L + 1).

- (2b) If 040000 ≤ b(A) ≤ 077777, then set c(A) = 000001 and execute-next the instruction located at (L + 2). Set c(Z) = b(Z) + 1.

- (2c) If 137777 ≥ b(A) ≥ 100000, then set c(A) = 177776 and execute-next the instruction located at (L + 2).

Set c(Z) = b(Z) + 1.

The TS K instruction consists of two subinstructions; TS0 and STD2.

2-27. Figures 2-6 and 2-7 illustrate the execution of TS 0611; figure 2-6 shows the execution without overflow, and figure 2-7 shows the execution with overflow. The quantity (a) stored in A is to be transferred to location 0611 in the E memory where the quantity e is presently located. During the execution of the previous instruction, the entire code of instruction TS 0611 (50611) was entered into register B (B now contains b = 150611), and order code 15 was

CONFIDENTIAL

FR-2-102A

CONFIDENTIAL

FR-2-102A

FR-2-102A

entered into register SQ. At Action 1, the address contained in B is transferred to S and the selection logic gates location 0611 for readout and write-in. At Action 2, the entire content of A is entered into B and P. Bits 16 and 15 are brought into the SQG for test of overflow or underflow by means of control pulse TOV. At Action 3, register G is cleared. If there was not any overflow or underflow detected at Action 2, no control pulses are generated during Actions 4 through 7, as shown in figure 2-6. The parity bit, generated by the parity pyramid for data a, is entered into G at Action 8, and quantity a is entered into G at Action 9. At Action 10, bits 16 and 15 of quantity a are transferred into the SQG for test of overflow or underflow, as usual. Since no overflow or underflow is present in A of figure 2-6, Action 10 is of no further consequence. Control pulse ST2, at Action 11, causes the SQG to execute-next the subinstruction STD2 in order to increment the program counter (Z) and to initiate the execution of the next instruction. (If K refers to a flipflop register, Action 9 has an effect similar to that of Action 9 of figure 2-2.)

2-28. If overflow or underflow was detected at Action 2, several control pulses are generated at Actions 4 through 7, as shown in figure 2-7. At Action 4, address z is entered into the Adder, incremented by one, and returned to Z at Action 7. In case of overflow in A, the word 000001 is written into A; in case of underflow, the word 17776. At Action 10, bits 16 and 15 of quantity 000001 or 177776 are entered into the SQG for the usual test of overflow or underflow, but Action 10 is again of no further consequence.

2-29. INSTRUCTION MSK K (Mask with Data from K, Order Code 7)

2-30. MSK K means: mask the content of location K with the content of the accumulator (A), i.e. perform an operation which has the same effect as applying the Boolean AND operation for each bit position of locations A and K. This is accomplished by applying  $\overline{c(A)}$  OR  $\overline{c(K)}$  instead of c(A) AND c(K) for each bit position. The entire operation MSK K (for  $0020 \le K$ ) can be formulated

FR-2-102A

as follows:

- (1) Set c(A) = b(A) AND c(K).

- (2) Restore c(K) = b(K) if  $0020 \le K \le 1777$ .

- (3) Execute-next the instruction located at z = (L + 1).

The MSK K instruction consists of two subinstructions; MSK0 and STD2.

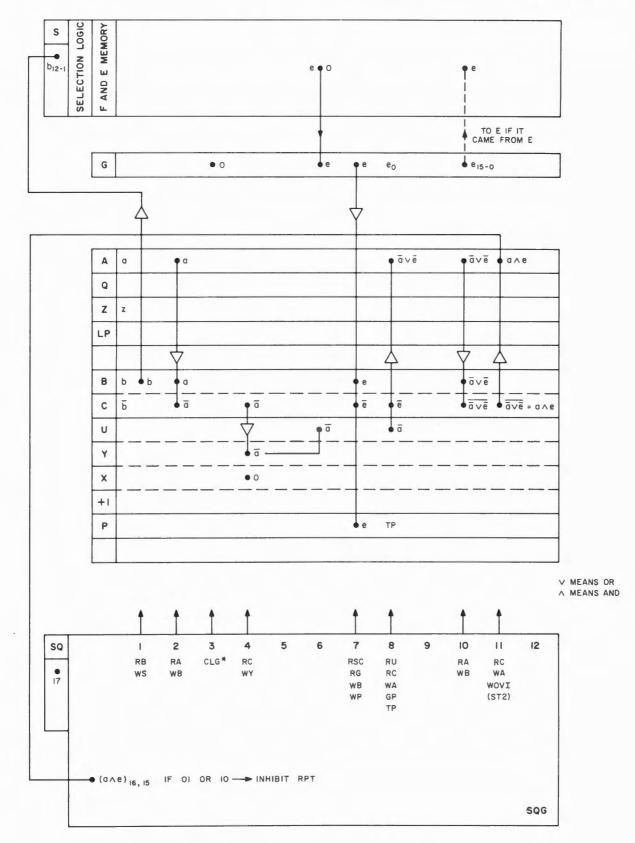

2-31. Figure 2-8 illustrates the execution of MSK 0700. The quantity e = 36000, located at K, is to be masked with the quantity a = 025252, contained in A. During the execution of the previous instruction, the entire code of instruction MSK 0700 (70700) was entered into B (B now contains b = 170700), and order code 17 was entered into register SQ. At Action 1, the address contained in B is transferred to S and the selection logic gates location 0700 for readout and write-in. At Action 2, quantity a is transferred to B and a is available at C. Register G is cleared at Action 3. At Action 4, the complemented quantity a is entered into Y for temporary storage in U. At Actions 7 and 8, quantity e is transferred to B and P, a new parity bit for quantity e is entered into G, and an alarm caused in case of incorrect parity. Furthermore, quantities a and e are read simultaneously and written into A, resulting in (a OR e). At Action 10, the quantity (a OR e) is complemented once more and becomes (a AND e) which is returned to A at Action 11. Control pulse WOVI inhibits program interruption at the end of the current instruction in case of overflow or underflow in A, as usual. Control pulse ST2 causes the SQG to execute-next subinstruction STD2 in order to increment the program counter (Z) and to initiate the execution of the next instruction. (If K refers to a flipflop register, Action 7 of MSK0 has an effect similar to that of Action 7 of figure 2-2.)

2-32. By omitting the control pulses usually generated at Action 9, Instruction MSK does not change the content of register G after Action 7. Most other instructions change the content of G, if an editing operation (shift or cycle) is performed.

CONFIDENTIAL

FR-2-102A

Figure 2-8. Subinstruction MSK0

2-33. INSTRUCTION AD K (Add Data from K and Count on Overflow or Underflow, Order Code 6)

2-34. AD K means: add the quantity located at K to the quantity contained in the accumulator (A). In case of overflow or underflow, increment or decrement the overflow counter (OVCTR). The method of addition applied is discussed in paragraph 15-30 through 15-33. The entire operation AD K (for  $0020 \leq K$ ) can be formulated as follows:

- (1) Set c(A) = b(A) + c(K).

- (2a) In case of overflow, set c(OVCTR) = b(OVCTR) + 1 by executing PINC.

- (2b) In case of underflow, set c(OVCTR) = b(OVCTR) 1 by executing MINC.

- (3) Restore c(K) = b(K) if  $0024 \le K \le 1777$ . If  $0020 \le K \le 0023$ , then  $c(K) = b^{e}(K)$ .

- (4) Execute-next the instruction located at z = (L + 1).

The AD K instruction consists of two subinstructions; AD0 and STD2. In case of overflow or underflow, it takes 3 MCTs to perform an addition.

2-35. Figure 2-9 illustrates the execution of AD 1043. Quantity e located at 1043 is to be added to the quantity (a) in A. During the execution of the previous instruction, the entire code of instruction AD 1043 (61043) was entered into B (B now contains b = 161043), and order code 16 was entered into register SQ. At Action 1, the address contained in B is transferred to S and the selection logic gates location 1043 for readout and write-in. At Action 2, quantity a is entered into Y. At Action 3, register G is cleared, as usual. The STMIC (included in Actions 7 to 9) deals with data a. The additional pulses, RB and WX, at Actions 7 to 9 transfer quantity e into X, and the arithmetic sum (a + e) is available at U within 3  $\mu$ sec. At Action 11, control pulses RU and WA transfer the sum to A. Pulse WOVI enters bits 16 and 15 of (a + e) into the SQG for test of overflow or underflow. In case of overflow or underflow, a program interruption at the end of the current instruction is inhibited.

Changed 29 May 1964

CONFIDENTIAL

CONFIDENTIAL

FR-2-102A

Figure 2-9. Subinstruction AD0

CHANGED 21 Aug 1963

FR-2-102A

If overflow occurs, control pulse WOVC is sent to the Counter Priority Control. About 10  $\mu$  sec later the Counter Priority Control causes the SQG to initiate instruction PINC, in order to increment the OVCTR by one. Incrementing the OVCTR is executed at the end of subinstruction STD2. If underflow occurs, WOVC causes decrementing (MINC) the OVCTR by one. Control pulse ST2 causes the SQG to execute next subinstruction STD2 in order to increment the program counter (Z) and to initiate the execution of the next instruction. (If K refers to a flip-flop register, the STMIC has an effect similar to that shown in figure 2-2.)

2-36. INSTRUCTION NDX K (Index Next Instruction, Order Code 2)

2-37. NDX K means: use as the next instruction the arithmetic sum of the instruction located at the next address z = (L + 1) plus the quantity located at K. K may be any address except 0025. In case K = 0025, this is instruction RESUME. When no overflow or underflow of the four-bit order code occurs during addition, the new instruction remains a Basic Instruction. When underflow occurs, the new instruction is an Extra Code Instruction. The entire operation NDX K (for  $0020 \le K$ , except K = 0025) can be formulated as follows:

- (1) Set c(B) = c(z) + c(K), z = (L + 1).

- (2) Restore c(K) = b(K), if  $0024 \le K \le 1777$ . If  $0020 \le K \le 0023$ , then  $c(K) = b^{e}(K)$ .

- (3) After the execution of the instruction put into B, execute next the instruction located at (L + 2), L being the location of the NDX instruction. If the instructions at (L + 1) and K are TC instructions (and if no overflow or underflow occurs during addition), the instruction to be executed next is not located at (L + 2) but at address c(L + 1) + c(K).

The NDX K instruction consists of two subinstructions: NDX0 and NDX1.

2-38. Figures 2-10 and 2-11 illustrate the execution of NDX 1174, this instruction being located at address 6534. Instruction AD 2103 is located at address z = 6535. Location K = 1174 contains the quantity e = 00011. The

Changed 13 Dec 1963

CONFIDENTIAL

FR-2-102A

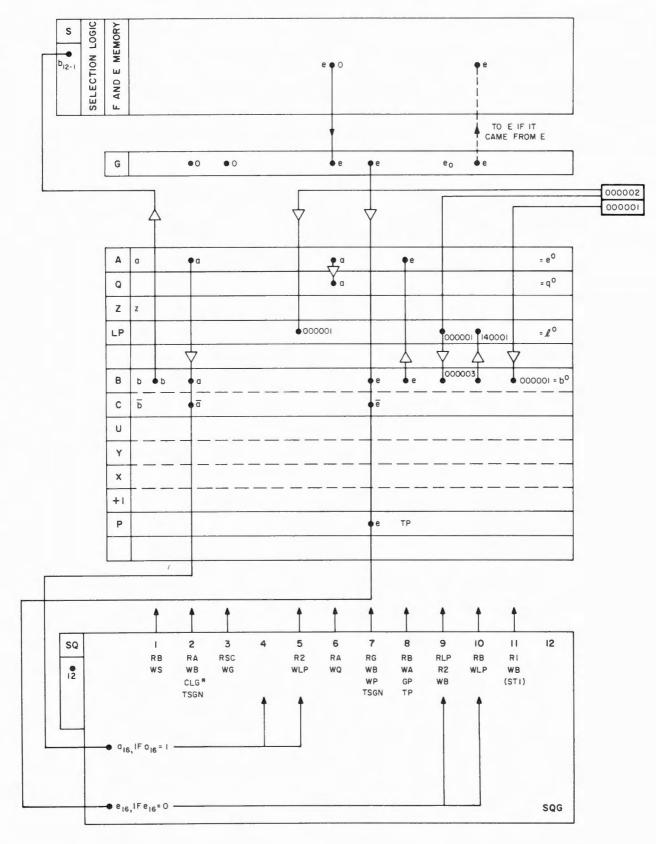

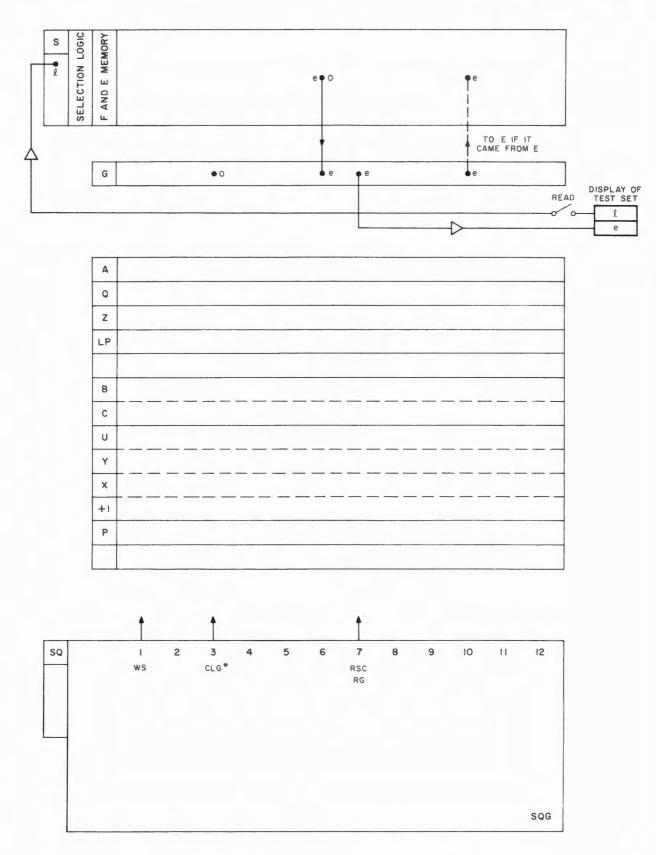

Figure 2-10. Subinstruction NDX0

CONFIDENTIAL

FR-2-102A

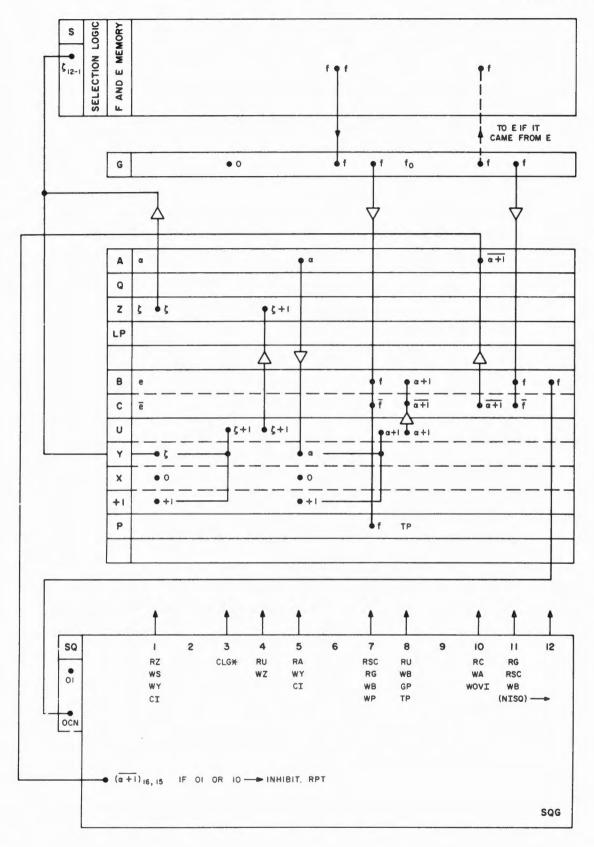

Figure 2-11. Subinstruction NDXI

Changed 13 Dec 1963

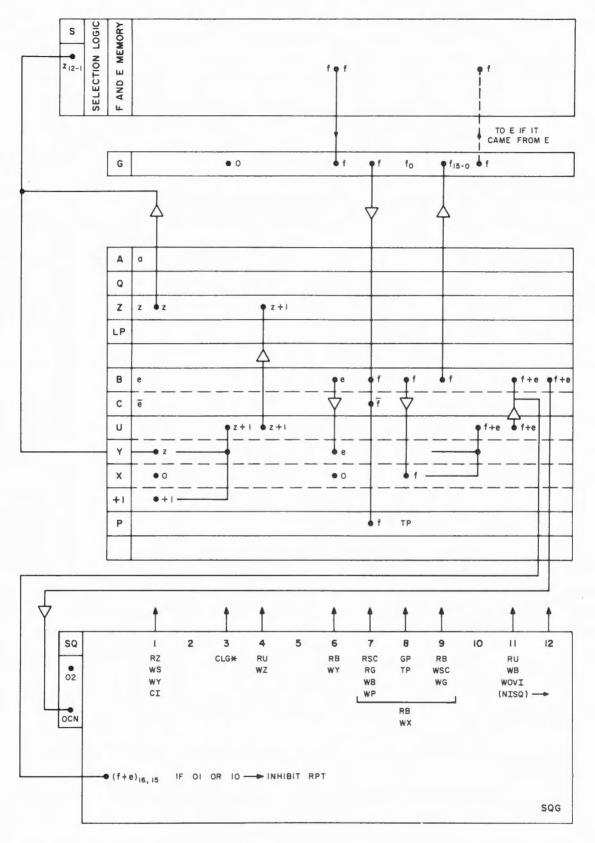

instruction AD 2103 is to be indexed to AD 2114. During the execution of the previous instruction, the entire code of instruction NDX 1174 (21174) was entered into B (B now contains b = 021174), and order code 02 was entered into register SQ. At Action 1 of NDX0, the address contained in B is transferred to S and the selection logic gates location 1174 for readout and write-in. Register G is cleared at Action 3. At Action 4, a program interruption at the end of the current instruction is inhibited if there is any overflow or underflow in the accumulator. The STMIC (Actions 7 to 9) brings data e into B and P, generates a new parity bit ( $e_0$ ), causes an alarm in case of incorrect parity, and restores word e in G. At Action 10, pulse TRSM tests whether the address contained in S is or is not 0025. Control pulse ST1, generated at Action 11, causes the SQG to execute-next subinstruction NDX1, if the address is not 0025, or subinstruction RSM, if the address is 0025. Subinstruction RSM will be discussed with the Involuntary Instructions. (If K refers to a flip-flop register, the STMIC has an effect similar to that shown in figure 2-2.)

2-39. At the start of NDX1, register Z still contains z but register B contains data e. The order code 02 is still stored in the SQ register. At Action 1, the address contained in Z is transferred to S and Y. The selection logic gates a location with address 6535 for readout, and the Adder increments z by one. The content of register BNK determines which location with address 6535 is selected. At Action 3, register G is cleared, and (z + 1) is transferred to Z at Action 4. At Action 6, quantity e is entered into Y from B. Actions 7, 8, and 9 of NDX1 are very similar to the STMIC with the exception that control pulses RB and WX are added. The instruction f = AD 2103 is entered into B (b becomes 162103) and P, an alarm caused in case of incorrect parity, a new parity bit for word f is generated, and word f is returned to G. At Action 8, instruction f is entered into X, and the new instruction (f + e) = 162114 = AD 2114is available at U within 3  $\mu$ sec. At Action 11, the new instruction is entered into B, and its order code OCN is brought into SQ at Action 12 to initiate the execution of the new instruction. Control pulse WOVI inhibits program

FR-2-102A

interruption if there is any overflow or underflow in the sum (f + e). For Extra Code Instructions, (f + e) is the quantity with underflow.

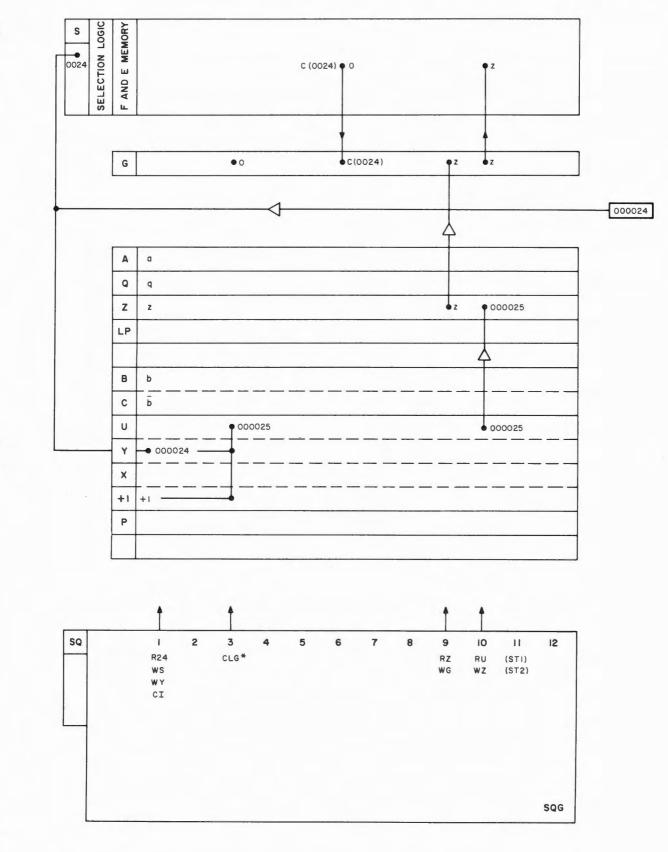

2-40. INSTRUCTION CCS K (Count, Compare, and Skip with Data at K, Order Code 1)

2-41. CCS K means: examine the data located at K. If c(K) > +0, take as the subsequent instruction the one located at z = (L + 1). If c(K) = +0, take the subsequent instruction from (L + 2). If c(K) < -0, take from (L + 3). If c(K) = -0, take from (L + 4). K may be any address, except an address referring to F Memory. The entire operation CCS K (for  $0020 \le K < 2000$ ) can be formulated as follows:

- (1a) If 00000 < c(K) < 37777, set c(A) = c(K) 00001 and executenext the instruction located at z = (L + 1).

- (1b) If c(K) = 00000, set c(A) = 000000 and execute-next the instruction located at (L + 2).

- (1c) If 40000 < c(K) < 77777, set c(A) = c(K) 00001 = |c(K)| 00001 and execute-next the instruction located at (L + 3).

- (1d) If c(K) = 77777, set c(A) = 000000 and execute-next the instruction located at (L + 4).

- (2) Restore c(K) = b(K) if  $0024 \le K \le 1777$ . If  $0020 \le K \le 0023$ , then  $c(K) = b^{e}(K)$ .

The CCS K instruction consists of two subinstructions; CCS0 and CCS1.

2-42. Figures 2-12 through 2-16 and table 2-3 illustrate the execution of CCS 1051 being located at 6040. Content e of location 1051 is to be examined, and dependent on the result, the instruction to be executed next is to be taken from location 6041, 6042, 6043, or 6044. During the execution of the previous instruction, the entire code of instruction CCS 1051 (11051) was entered into B (B now contains b = 011051), and order code 01 was entered into register SQ. At Action 1 of CCS0, the address contained in B is transferred to S and

Changed 29 May 1964

CONFIDENTIAL

2-32

CONFIDENTIAL

FR-2-102A

Figure 2-12. Subinstruction CCS0 (Example e > +0)

FR-2-102A

Figure 2-13. Subinstruction CCS0 (Example e = +0)

Changed 25 Sept 1963

FR-2-102A

Figure 2-14. Subinstruction CCS0 (Example e < -0)

FR 2-102A

Figure 2-15. Subinstruction CCS0 (Example e = -0)

Changed 13 Dec 1963

FR-2-102A

#### TABLE 2-3

#### CONTENT OF A AND Z AT END OF CCS0 AND CCS1

| INITIAL<br>CONDITION<br>c(K)≈ e |        | ζ<br>(CONTENT OF Z<br>AT END OF CCSO) |       |       |

|---------------------------------|--------|---------------------------------------|-------|-------|

| e>+0                            | ē      | Z                                     | z + I | e – I |

| e = +0                          | 177776 | z + 1                                 | z + 2 | +0    |

| e < - 0                         | e      | z + 2                                 | z + 3 | ē — I |

| e = -0                          | 177776 | z + 3                                 | z + 4 | +0    |

FR-2-102A

FR-2-102A

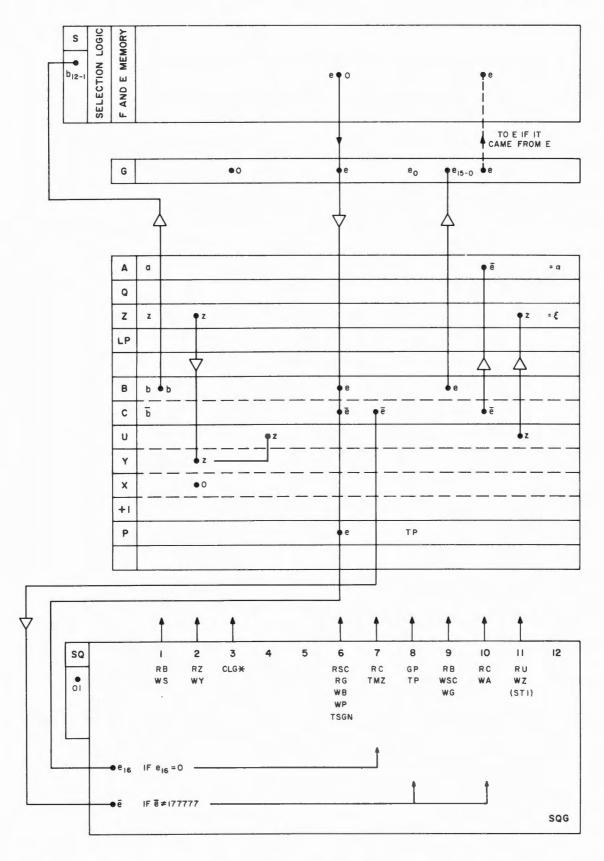

the selection logic gates location 1051 for readout and write-in. At Action 2, the "next" address (z) is entered into Y and kept in U, and G is cleared at Action 3. At Action 6, control pulses RG, WB, and WP transfer the content of G to B and P. Remember that P now contains exactly the same word as G. The word in B contains the sign bit of G in bit positions 16 and 15, but does not contain the parity bit. Control pulse RSC has no effect unless a flip-flop register has been gated for readout. Control pulse TSGN enters the sign bit of e into the SQG. If  $e_{16} = 0$ , control pulses RC and TMZ are generated at Action 7 as shown in figures 2-12 and 2-13, transferring the entire word e into the SQG. If  $e \neq 177777$  (e is not minus zero, i.e., e not zero), then Actions 8 and 10 are generated as shown in figure 2-12. At Action 8, an alarm is caused in case of incorrect parity, and a new parity bit for word e is entered into G. At Action 9, word e is brought back to G, as usual. At Action 10, e is transferred to A, and z is returned to Z. Control pulse ST1 causes the SQG to execute-next subinstruction CCS1. (If K refers to a flip-flop register, Actions 6 and 9 have an effect similar to that of Actions 7 and 9 of figure 2-2.)

2-43. If (at Action 7) e = 177777 (e is minus zero, i.e., e is zero), then Actions 8 and 10 are generated as shown in figure 2-13. The additional pulses Rl and WX write the value plus-one into X. The value plus-one is added to z and the sum appears at U 3 µsec later. At Action 10, the quantity minus-one is written into A. At Action 11, the quantity (z + 1) is transferred from U to Z, and subinstruction CCS1 follows after Action 12.

2-44. Returning to Action 6, if  $e_{16} = 1$ , control pulses RB and TMZ are generated at Action 7, as shown in figures 2-14 and 2-15, transferring the word e into the SQG. If  $e \neq 177777$  (e is not minus zero), then Actions 8 and 10 are generated as shown in figure 2-14. The additional pulses R2 and WX write the value plus-two into X. The value plus-two is added to z and the sum appears at U 3 µsec later. At Action 10, word e is transferred to A. At

Action 11, the quantity (z + 2) is transferred from U to Z and subinstruction CCS1 follows after Action 12.