# UNCLASSIFIED

270

#### APOLLO GUIDANCE COMPUTER

Contral to Pelus The

Information Series

ISSUE 30 BLOCK II APOLLO GUIDANCE COMPUTER SUBSYSTEM FR-2-130

# RAYTHEON COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

APOLLO GUIDANCE COMPUTER Information Series ISSUE 30 BLOCK II APOLLO GUIDANCE COMPUTER SUBSYSTEM FR-2-130 31 August 1965

FR-2-130

### CONTENTS

| Paragraph | Pa                                                 | ge  |

|-----------|----------------------------------------------------|-----|

| 30-1      | INTRODUCTION                                       | · 1 |

| 30-9      | BLOCK II AGC SUBSYSTEM                             | .3  |

| 30-16     | COMPUTER OPERATIONS                                | -13 |

| 30-18     | Timer                                              | 13  |

| 30-22     | Sequence Generator                                 | .13 |

| 30-29     | Central Processor                                  | 17  |

| 30-33     | CP Register Manipulations                          | .17 |

| 30-42     | Adder                                              | 21  |

| 30-48     | Parity Block                                       |     |

| 30-51     | Memories                                           |     |

| 30-54     | Addressing                                         |     |

| 30-65     | E Location Assignments and Counter Operations. 30- |     |

| 30-67     | Input-Output Control                               |     |

| 30-75     | Output Channels                                    |     |

| 30-83     | Input Channels                                     |     |

| 30-89     | Special Circuits                                   |     |

| 30-90     | CDU Drive Control                                  |     |

| 30-95     | Gyro Drive Control                                 |     |

| 30-100    | EMS and Thrust Drive Control                       |     |

| 30-105    | Radar Control                                      |     |

| 30-110    | BMAG/RHC Control of the CM                         |     |

| 30-113    |                                                    | 71A |

| 30-116    |                                                    | 71A |

| 30-120    |                                                    | 71D |

| 30-123    |                                                    | 71F |

| 30-126    |                                                    | 71H |

| 30-128    |                                                    | 71L |

| 30-130    |                                                    | 71L |

| 30-136    |                                                    | 71M |

| 30-140    | Alarm Control                                      |     |

| 30-141A   | Digital Fault Detections                           |     |

| 30-141B   | Parity Fail                                        |     |

| 30-141D   | Rupt Lock                                          | _   |

|           |                                                    |     |

(cont)

FR-2-130

# CONTENTS (cont)

Paragraph

| aragraph |                           |    |     |      |     |  |   |  | Page  |

|----------|---------------------------|----|-----|------|-----|--|---|--|-------|

| 30-141F  | TC Trap                   |    |     |      |     |  |   |  | 30-73 |

| 30-141H  | Watchman                  |    |     |      |     |  |   |  |       |

| 30-141K  | Counter Fail              |    |     |      |     |  |   |  | 30-73 |

| 30-141 M | PIPA Fail                 |    |     |      |     |  |   |  | 30-74 |

| 30-141P  | Analog Fault Detections   |    |     |      |     |  |   |  | 30-74 |

| 30-141Q  | Voltage Fail              |    |     |      |     |  |   |  | 30-74 |

| 30-141 T | Oscillator Fail           |    |     |      |     |  |   |  | 30-74 |

| 30-141W  | Scaler Fail               |    |     |      |     |  |   |  | 30-75 |

| 30-141Z  | Warning Integrator        |    |     |      |     |  |   |  | 30-75 |

| 30-141AC | Associated Signals        |    |     |      |     |  |   |  | 30-76 |

| 30-141AD | Light Test                |    |     |      |     |  |   |  | 30-76 |

| 30-141AG | Alarm Reset               |    |     |      |     |  |   |  | 30-76 |

| 30-141AJ | Standby Control           |    |     |      |     |  |   |  | 30-77 |

| 30-142   | Display and Keyboards .   |    |     |      |     |  |   |  | 30-77 |

| 30-148   | INSTRUCTIONS              |    |     |      |     |  |   |  | 30-81 |

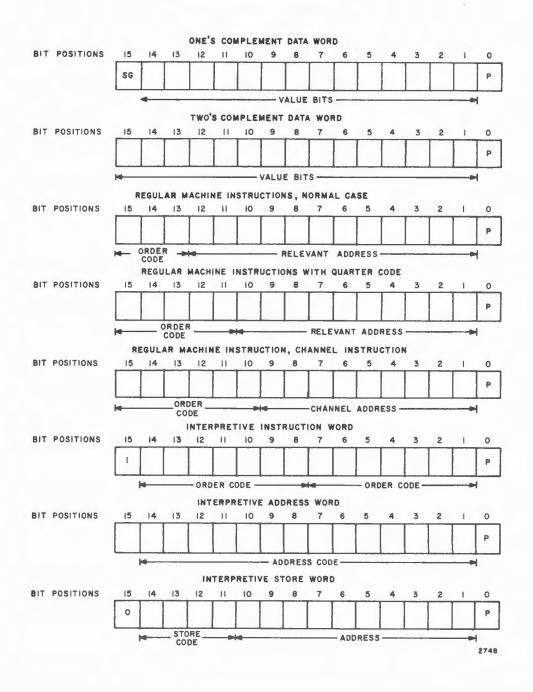

| 30-149   | Word Formats and Instruct |    |     |      |     |  |   |  | 30-81 |

| 30-156   | Machine Instructions      |    |     |      |     |  |   |  | 30-83 |

| 30-158   | Regular Instructions .    |    |     |      |     |  |   |  | 30-83 |

| 30-167   | Sequence Changing Inst    |    |     |      |     |  |   |  | 30-86 |

| 30-170   | Fetching and Storing Ir   | st | ruc | tio  | ns  |  |   |  | 30-87 |

| 30-174   | Modifying Instructions    |    |     |      |     |  |   |  | 30-88 |

| 30-176   | Arithmetic and Logic I    | ns | tru | ctio | ons |  |   |  | 30-88 |

| 30-179   | Channel Instructions      |    |     |      |     |  |   |  | 30-88 |

| 30-181   | Special Instructions      |    |     |      |     |  |   |  | 30-89 |

| 30-183   | Involuntary Instructions  |    |     |      |     |  |   |  | 30-89 |

| 30-186   | Peripheral Instructions   |    |     |      |     |  | • |  | 30-90 |

|          |                           |    |     |      |     |  |   |  |       |

### ILLUSTRATIONS

| Figure |                                              | Page            |

|--------|----------------------------------------------|-----------------|

| 30-1   | Block II AGC.                                | 30-4            |

| 30-2   | Tray A                                       | 30-8            |

| 30-3   | Tray B                                       | 30-9            |

| 30-4   | Block II DSKY                                | 30-10           |

| 30-5   | Flat Package, Schematic Diagram              | 30-12           |

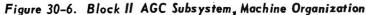

| 30-6   | Block II AGC Subsystem, Machine Organization | 30-16           |

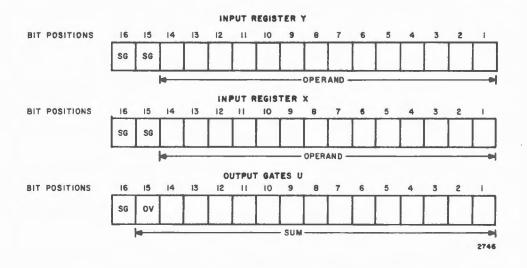

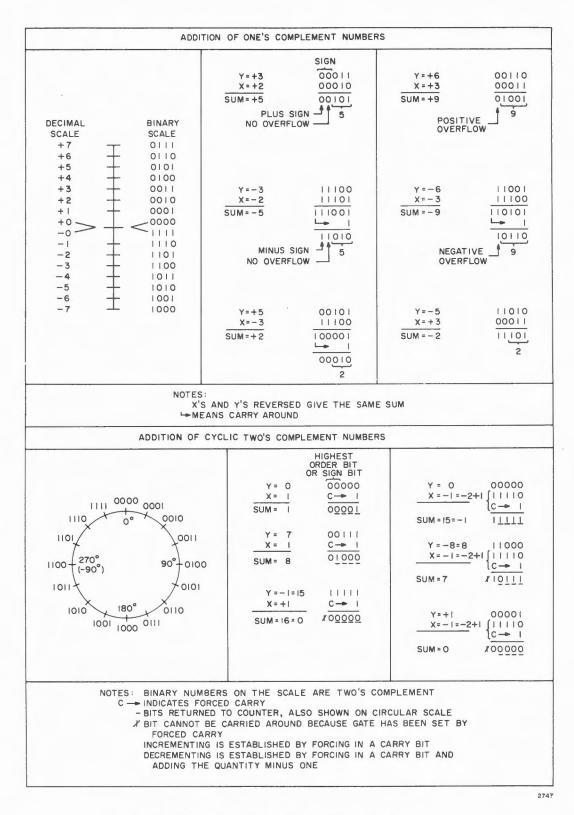

| 30-7   | Adder Input Registers and Output Gates       | 30-22           |

| 30-8   | Summation of Two Binary Numbers              | 30-24           |

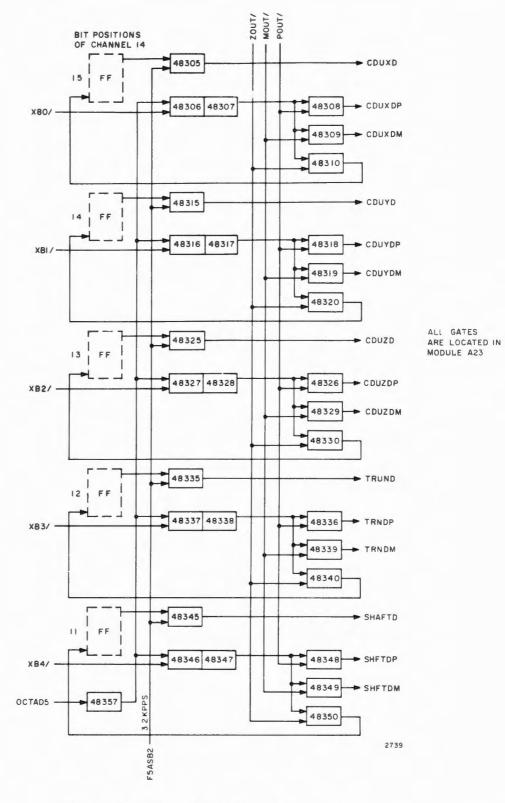

| 30-8A  | CDU Drive Control.                           | 30-61           |

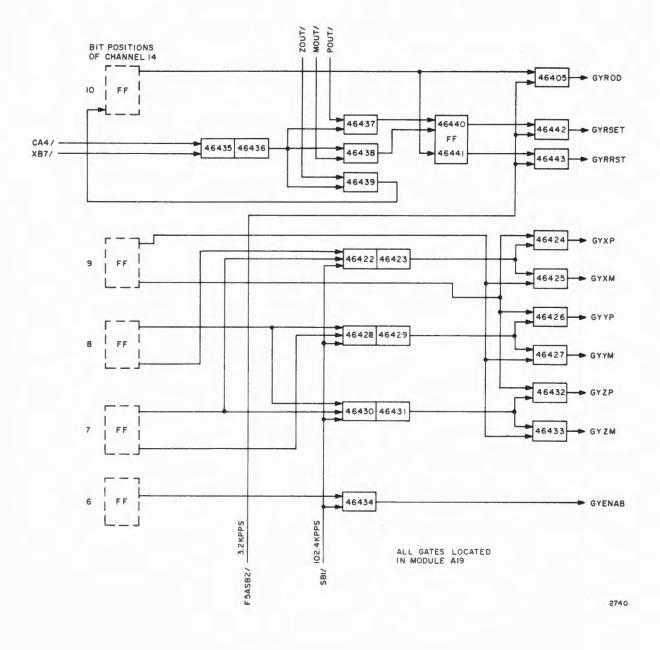

| 30-8B  | Gyro Drive Control                           | 30-64           |

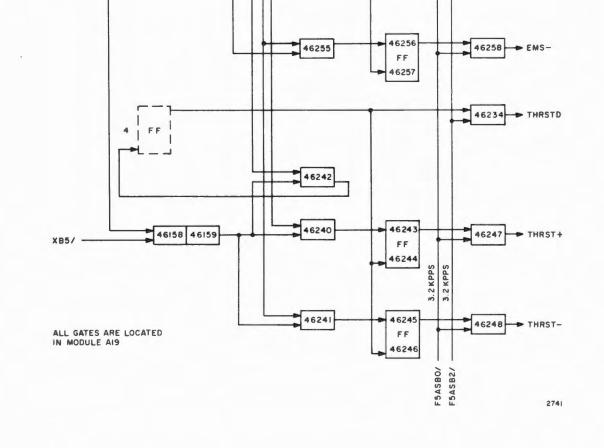

| 30-8C  | EMS and Thrust Drive Control                 | 30-66           |

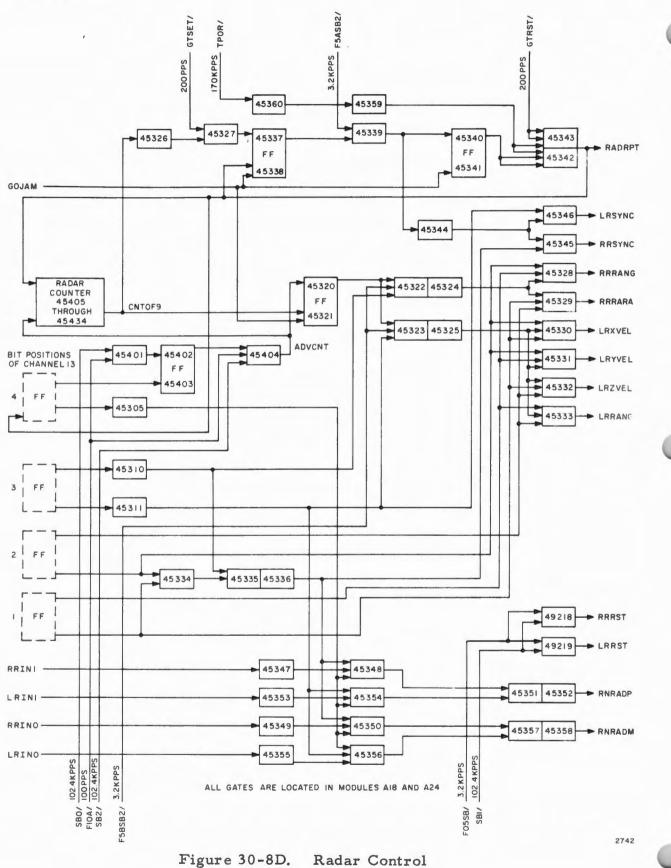

| 30-8D  | Radar Control                                | 30-68           |

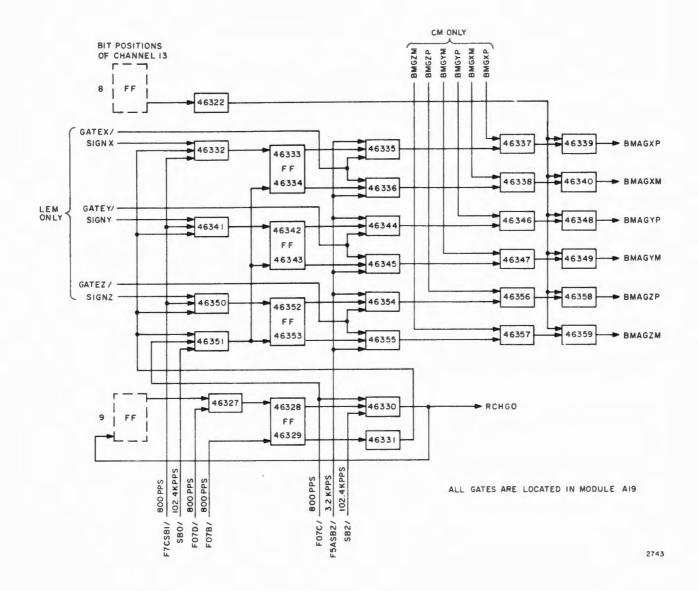

| 30-8E  | BMAG/RHC Control                             | 30-71           |

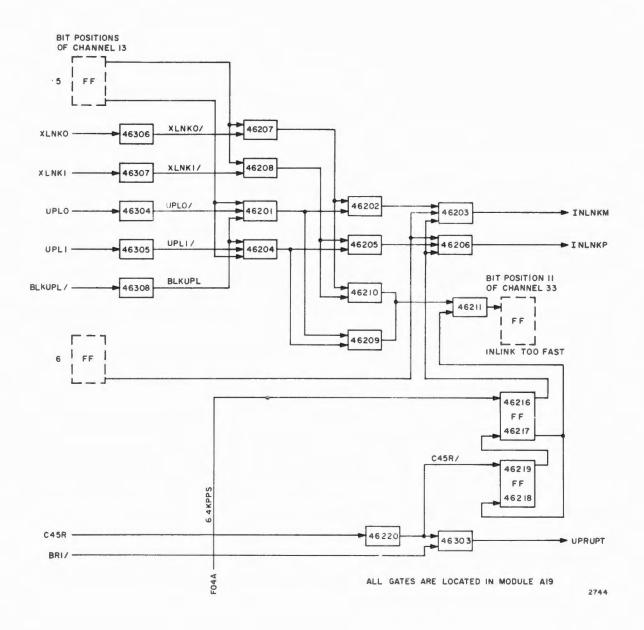

| 30-8F  | Inlink Control.                              | 30-71C          |

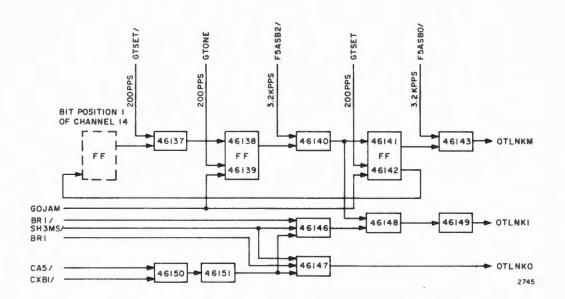

| 30-8G  | Outlink Control                              | 30-71E          |

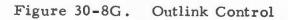

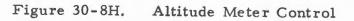

| 30-8H  | Altitude Meter Control                       | 30-71G          |

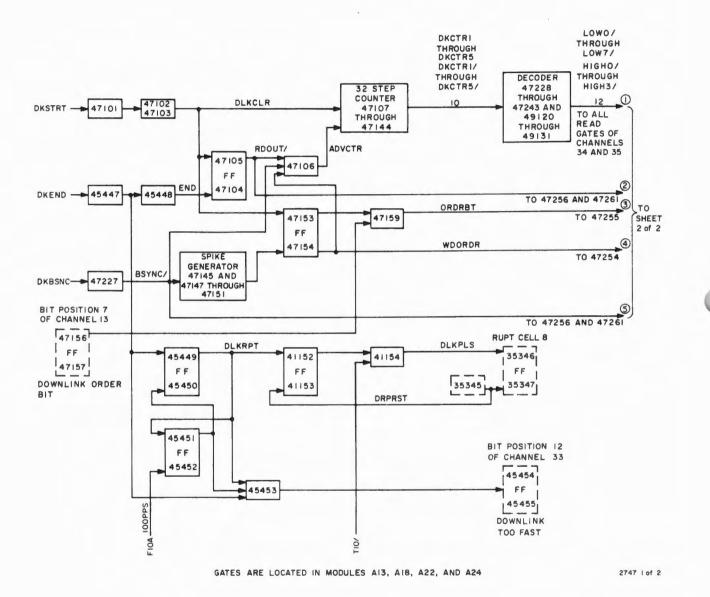

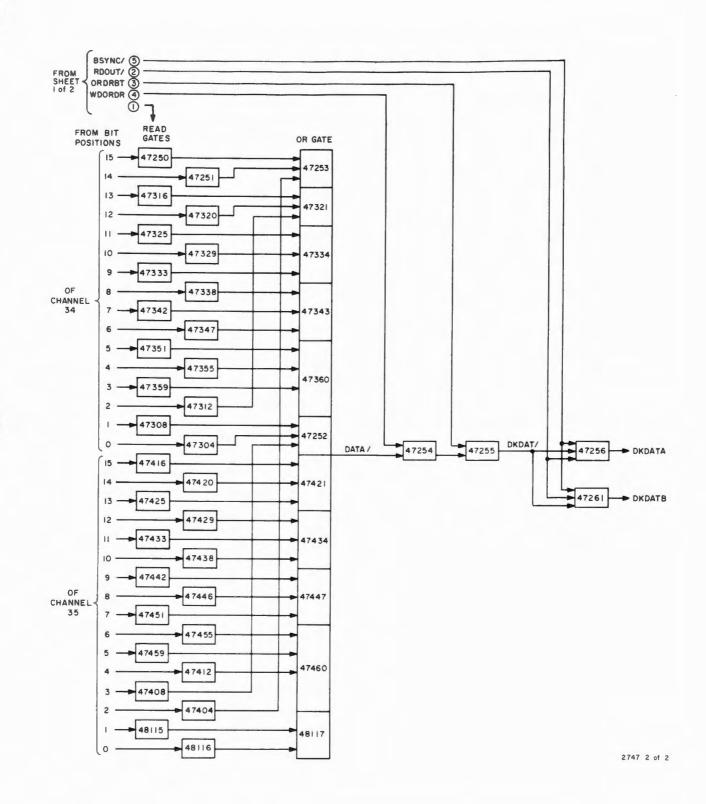

| 30-8J  | Downlink Converter.                          | 30 <b>-</b> 71I |

| 30-9   | Word Formats                                 | 30-82           |

|        |                                              |                 |

### TABLES

| Table |                                               | Page            |

|-------|-----------------------------------------------|-----------------|

| 30-0  | Modules and Drawing Numbers                   | 30 <b>-</b> 12B |

| 30-1  | Information Flow Between CP Register Bit      |                 |

|       | Positions and Write Amplifiers                | 30-18           |

| 30-2  | E Addressing                                  | 30-27           |

| 30-3  | F Addressing                                  | 30-28           |

| 30-4  | E Location Assignments and Counter Operations | 30-35           |

| 30-5  | Input-Output Channels                         | 30-48           |

| 30-5A | Output Channel 12                             | 30-50           |

| 30-5B | Output Channel 13                             | 30-51           |

| 30-5C | Output Channel 14                             | 30-52           |

| 30-5D | Input Channel 30                              | 30-53           |

| 30-5E | Input Channel 31                              | 30-54           |

| 30-5F | Input Channel 32                              | 30-56           |

FR-2-130

# TABLES (cont)

| Table |                                  |  |   |  | Page   |

|-------|----------------------------------|--|---|--|--------|

| 30-5G | Input Channel 33                 |  | • |  | 30-57  |

| 30-5H | Output Channels 05 and 06        |  |   |  | 30-58  |

| 30-5J | Input Channel 16                 |  |   |  | 30-59  |

| 30-6  | Interrupt Motions                |  |   |  | 30-71N |

| 30-7  | Counter Priority Control Inputs. |  |   |  | 30-71Q |

| 30-8  | Machine Instruction Types        |  |   |  | 30-83  |

| 30-9  | Order Code Structure             |  |   |  | 30-85  |

| 30-10 | Machine Instructions             |  |   |  | 30-91  |

### APPENDICES

| Appendix |                                            | Page  |

|----------|--------------------------------------------|-------|

| 30Å      | Command Module AGC Subsystem Input and     |       |

|          | Output Signals                             | 30A-1 |

| 30B      | Lunar Excursion Module AGC Subsystem Input |       |

|          | and Output Signals                         | 30B-1 |

| 30C      | Test Connector Signals                     | 30C-1 |

#### **30–1. INTRODUCTION**

30-2. This is the thirtieth issue of the AGCIS published to inform the technical staff at MIT/IL and Raytheon about the Apollo guidance computer (AGC) subsystems. The various types of computer subsystems are listed in paragraph 1-5 of Issue 1. This issue is an over-all description of the Block II AGC subsystems used in the Command Modules (CM's) and the Lunar Excursion Modules (LEM's). Other issues will describe in more detail the various sections and programs of the Block II AGC subsystems.

30-3. A Block II AGC subsystem used in a CM consists of one Apollo guidance computer (AGC) and two identical Display and Keyboards (DSKY's). One DSKY is mounted in the Navigation Panel of the CM, the other in the Main Panel. A Block II AGC subsystem used in a LEM consists of one AGC and only one DSKY. The CM and LEM Computers are identical except for the programs wired in and some input and output signals. An AGC, including its own power supply, occupies a volume of about 1 cu ft. and weighs approximately 60 lbs. Each DSKY occupies about 1/5 cu ft. and weights approximately 17 lbs.

30-4. An AGC subsystem is a control computer (real time computer) with many features of a general purpose computer. The AGC's are parallel digital computers which operate with 16-bit words and single address instructions. The clock rate of an AGC is 1.024 Mc (oscillator frequency of 2.048 Mc and word transfer time of approximately 1  $\mu$ sec). They employ a ONE's complement number system with overflow bit and fixed binary point. Each Block II AGC contains an Erasable Memory (ferrite core array) capable of storing 2048 words of 16-bits each, and a Fixed Memory (Mo-perm core ropes) capable of storing 36,864 words of 16-bits each. The words stored in the two memories include one parity bit for error detection. All Block II logic is built from only one type of solid state integrated NOR gates contained in flat packages.

30-5. Input signals to the AGC subsystem can be parallel binary information (DC signals), incremental data (pulses counted), or serial binary data. Output signals can also be parallel binary information (DC signals or pulse trains), controlled pulse bursts (computed number of drive pulses), or timing pulses (continuous pulse trains).

30-6. Provision is made to have the AGC's operating either in the standby or the normal mode of operation to save power. When an AGC is in the standby mode, only the Timer is operating to monitor time information. When in the normal mode of operation, the whole subsystem operates. 30-7. Most modern computers, large business machines in particular, are designed such that various programs can be inserted and executed. The AGC differs from these computers since programs are wired in and can be changed only by replacing the Fixed Memory (either completely or in part) into which the program is wired. Therefore, an AGC program should be defined as the entire content of the Fixed Memory. An AGC program consists of various program sections (sub-programs).

30-8. An AGC program section can be written in regular machine language, in interpretive language, or in both. The regular machine language can be expressed with 38 different Regular Instructions, including some double precision operations. More than 100 different Interpretive Instructions, including double precision, triple precision, vector double precision, and matrix operations, are provided for the interpretive language. Program portions written in regular language operate faster than portions written in interpretive language because interpretive portions require extra time to interpret instructions. Portions written in interpretive language require less space for program storage than portions written in basic language because of the subroutine character of Interpretive Instructions. Furthermore, the interpretive language considerably simplifies the programming of complicated mathematical operations. The interpretive language is used mainly in program sections dealing with astronautical computations. Many of the control operations that the computer must perform are written in regular language; the interpretive language is used to simplify multiprecision and vector operations. Thus, the AGC is a fast computer when operating in the regular machine language, and a powerful machine when operating in the interpretive mode.

#### 30-9. THE BLOCK II AGC SUBSYSTEM

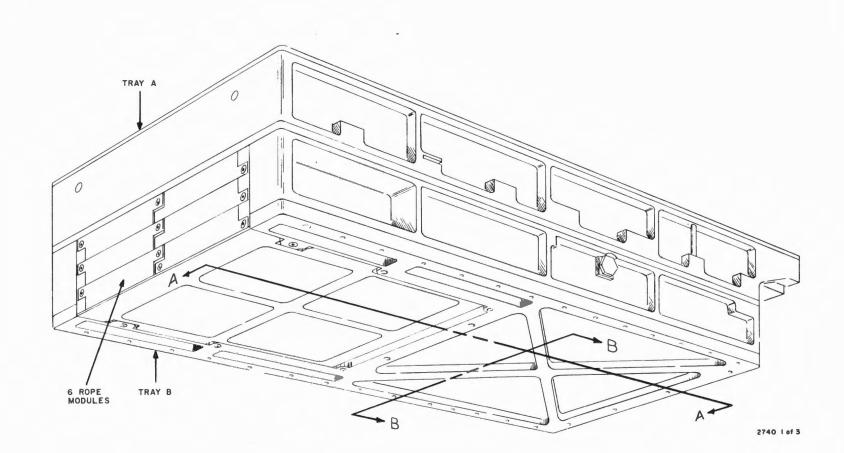

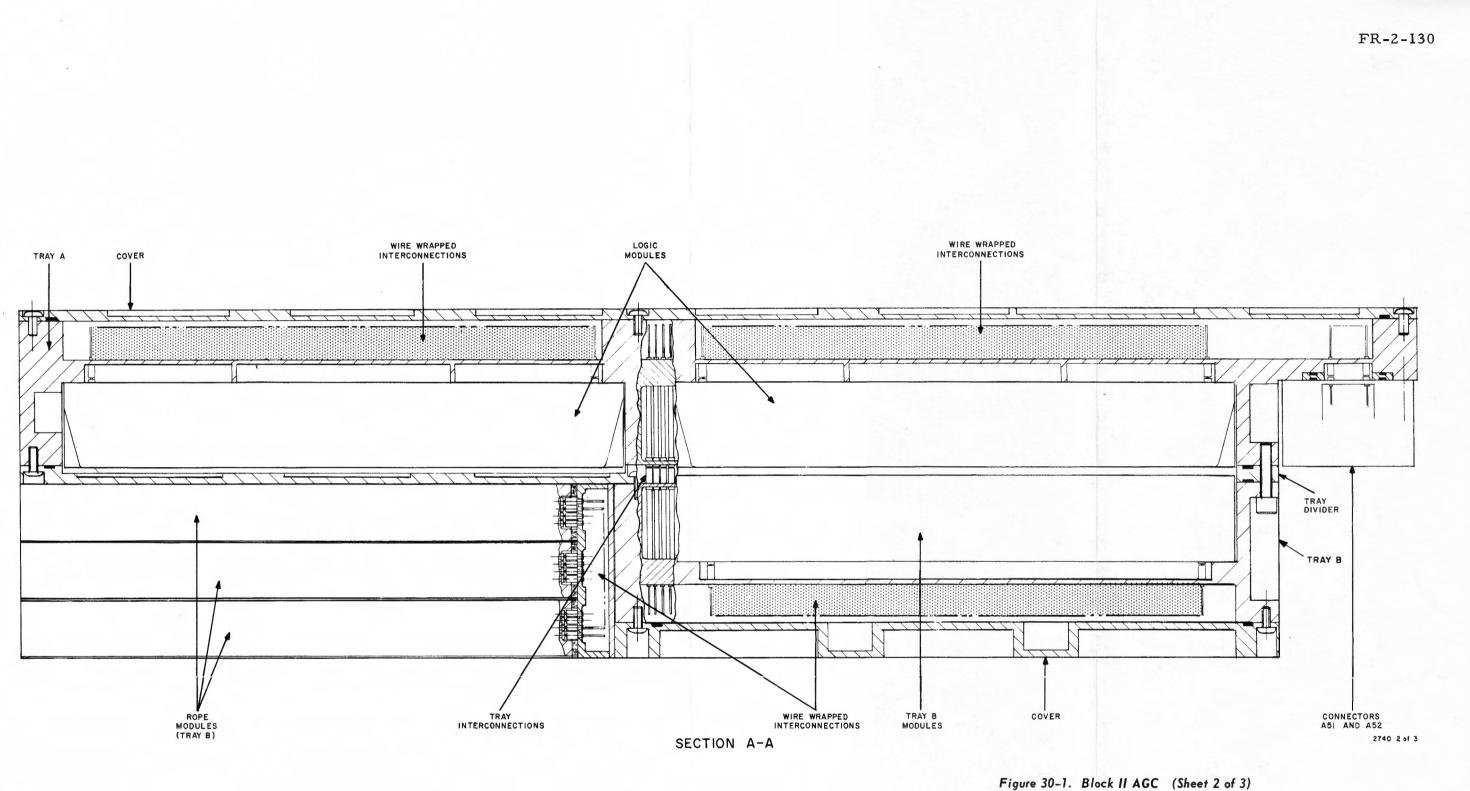

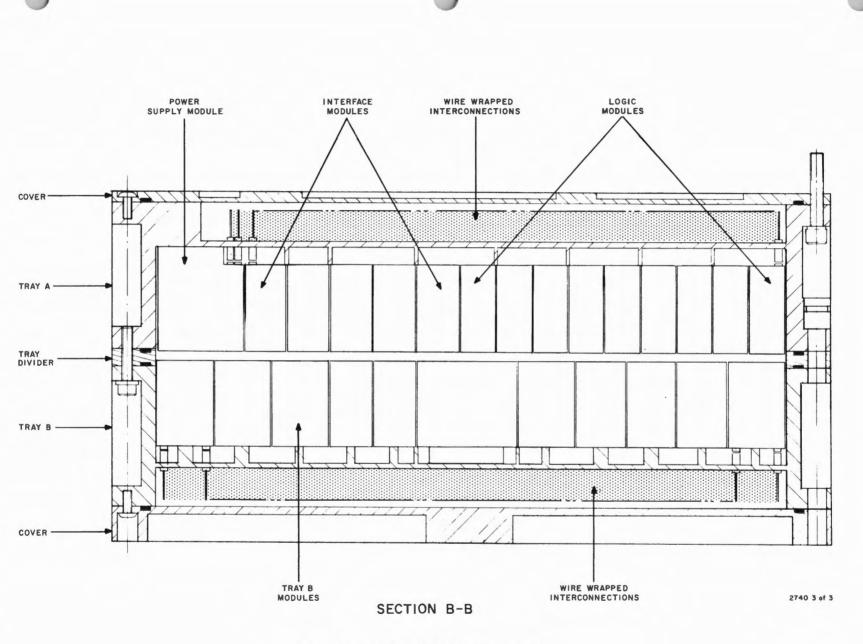

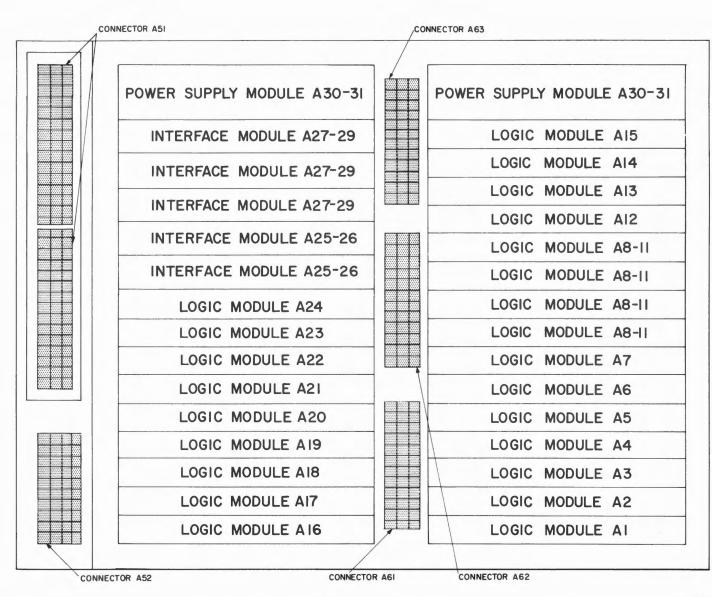

30-10. A Block II AGC subsystem used in a CM consists of one Apollo guidance computer (AGC) and two identical Display and Keyboards (DSKY's). A Block II AGC subsystem used in a LEM consists of one AGC and only one DSKY. The AGC, which occupies a volume of about 1 cu ft., consists of one Tray A and one Tray B (figure 30-1). Tray A contains 24 logic modules, 5 interface modules, and 2 power supply modules (figure 30-2). A logic module may contain up to 120 flat packs and measures approximately  $9 \ 3/4 \times 1 \ 1/2 \times 5/8$  inches. All other modules also measure  $9 \ 3/4 \times 1 \ 1/2$  inches but vary in width in multiples of 1/8 inch. Tray B contains the oscillator module, the alarm module, the erasable memory module, 6 core rope modules, and 8 modules which contain all the drivers and amplifiers for Erasable (E) and Fixed (F) Memory (figure 30-3). All modules, except the core rope modules, are plugged into receptacles mounted in the bottom of the trays. The core rope modules are plugged in from the front.

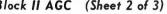

30-11. The two trays are joined such that the wirewrapped interconnections in the tray bottoms are on the outside (figure 30-1). Both trays are covered on the outside. The AGC is mounted with the logic tray side to a cold plate. The core rope modules can be interchanged without removing the cover of Tray B.

30-12. A 360 pin connector (A51) in figure 30-2 provides all the necessary connections between the AGC and the DSKY's, the G & N system, and the space craft (S/C), i.e., the CM or the LEM. A 144 pin connector (A52) is provided for connecting the AGC to the Computer Test Set (CTS), the Program Analyzer Console (PAC), or any other applicable test equipment.

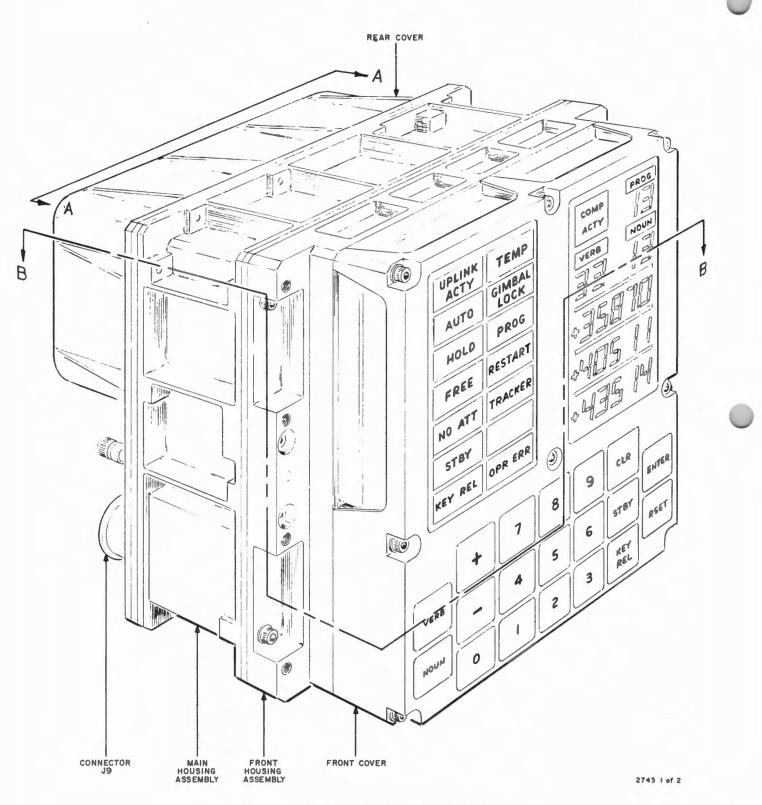

30-13. A Block II DSKY consists of the main and front housing assembly with covers (figure 30-4). A 91 pin connector (J9) provides all the necessary connections to the AGC, the G & N system, and the CM or the LEM.

30-14. All signals fed into the AGC and the two DSKY's of a CM, and all the signals provided by these three units are described in Appendix A. All signals of the LEM AGC and DSKY are described in Appendix B.

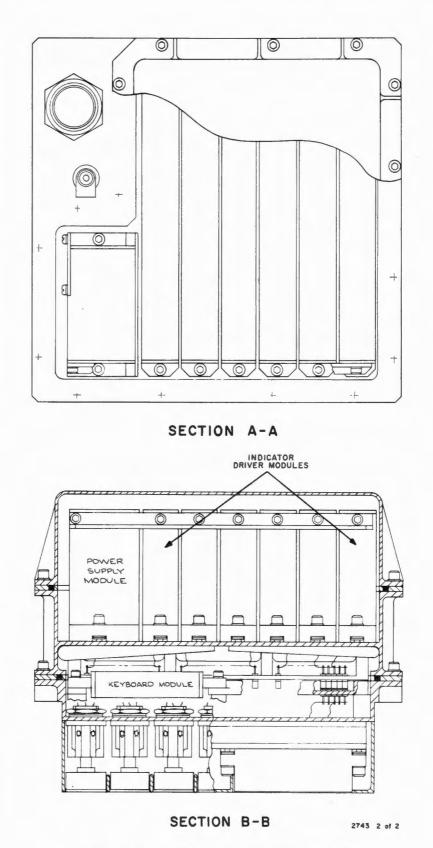

30-15. All Block II logic is built from flat packages each of which contains two solid state silicon integrated NOR gates with three inputs (figure 30-5). If one or more inputs of a NOR gate are connected to a positive potential of approximately 1.5 volts, the output potential of the NOR gate is about 0.2 volt.

Figure 30-1. Block II AGC (Sheet 1 of 3)

0

Figure 30-1. Block II AGC (Sheet 3 of 3)

30-7

FR-2-130

30-8

Figure 30-2. Tray A

2741

2742

Figure 30-3. Tray B

FR-2-130

Figure 30-4. Block II DSKY (Sheet 1 of 2)

FR-2-130

Figure 30-4. Block II DSKY (Sheet 2 of 2)

FR-2-130

Figure 30-5. Flat Package, Schematic Diagram

If all inputs of a NOR gate are connected to a positive potential of about 0.2 volt or less, the output potential is approximately 1.5 volts. Thus, a logical ONE is represented by a positive potential of approximately 1.5 volts and a logical ZERO by a positive potential of about 0.2 volt. Since each NOR gate inverts voltage levels, a logical ZERO can represent either a data ZERO or a data ONE depending on the operational location of a gate, and a logical ONE can represent a data ONE or a data ZERO. The reference point is the input to the Write Amplifiers where a data ONE is represented by a logical ONE (positive potential of approximately 1.5 volts) and a data ZERO by a logical ZERO (positive potential of about 0.2 volt). At the outputs of the Write Amplifiers, a logical ONE (positive potential of approximately 1.5 volts) represents a data ZERO, and a logical ZERO (positive potential of approximately 0.2 volt) represents a data ONE.

30-15A. Table 30-0 lists all modules of the AGC, the numbers of NASA drawings showing the logic of these modules, and the numbers of the gates contained in the modules.

### TABLE 30-0

### MODULES AND DRAWING NUMBERS

| Module    | Drawing Number | Gate Numbers  |

|-----------|----------------|---------------|

| Al        | 2005059        | 38101 - 38491 |

| A2        | 2005060        | 37101 - 37459 |

| A3        | 2005051        | 30001 - 30457 |

| A4        | 2005062        | 36101 - 36460 |

| A5        | 2005061        | 39101 - 39461 |

| A6        | 2005063        | 40101 - 40441 |

| A7        | 2005052        | 33101 - 33459 |

| A8        | 2005055        | 51101 - 51463 |

| A9        | 2005056        | 52101 - 52463 |

| A10       | 2005057        | 53101 - 53463 |

| All       | 2005058        | 54101 - 54463 |

| A12       | 2005053        | 34101 - 34467 |

| A1 3      | 2005069        | 41101 - 41244 |

| A14       | 2005064        | 42101 - 42457 |

| A15       | 2005065        | 35101 - 35460 |

| A16       | 2005066        | 43101 - 43460 |

| A17       | 2005067        | 44101 - 44464 |

| A18       | 2005068        | 45101 - 45456 |

| A19       | 2005070        | 46101 - 46461 |

| A20       | 2005054        | 31101 - 31459 |

| A21       | 2005054        | 32001 - 32658 |

| A22       | 2005050        | 47101 - 47460 |

| A23       | 2005072        | 48101 - 48458 |

| A24       | 2005072        |               |

|           | 2005021        | 49101 - 49443 |

| A25-A26   | 2005021        | -             |

| A27-A29   |                | -             |

| A30 - A31 | 2005010        |               |

| B7        | 2005003        | -             |

| B8        | 2005008        | -             |

| B9-B10    | 2005004        | -             |

| B11       | 2005005        | -             |

| B12       | 2005006        | -             |

| B13-B14   | 2005002        | -             |

| B15       | 2005009        | -             |

| B16-B17   | 2005000        | -             |

| DSKY      | 2005900        | -             |

| DSKY      | 2005950        | -             |

| D1 - D6   | 2005902        | -             |

| D8        | 2005903        | -             |

| Buffer    | 2014123        | -             |

30-12A/30-12B

#### **30-16. COMPUTER OPERATIONS**

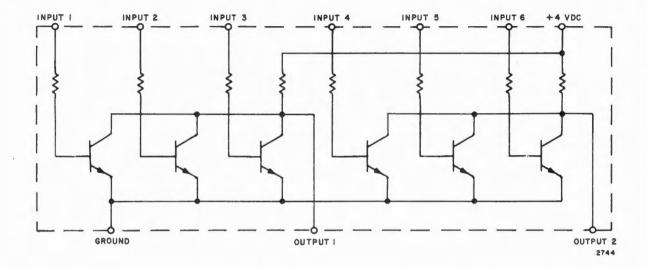

30-17. The organization of the AGC subsystem is illustrated in figure 30-6. The AGC subsystem can be divided into the following major sections:

- a. Timer

- b. Sequence Generator (SQG)

- c. Central Processor (CP)

- d. Erasable (E) Memory

- e. Fixed (F) Memory

- f. Standby Control

- g. Alarm Control

- h. Power Supply

- i. Interface (including RHC Converter)

- j. Display and Keyboards (DSKY's)

#### 30-18. TIMER

30-19. The Timer consists of the Clock, the Scalers, and the Time Pulse Generator. The Clock is driven by a 2.048 Mc oscillator. For classified information, refer to Issue 1, paragraph 1-40.

30-20. The Clock provides various signals of 1.024 Mpps, 512 kpps, and 102.4 kpps. Some of these signals are used for driving the Time Pulse Generator, and for timing and gating various logic areas of the AGC. Two 102.4 kpps signals are fed into the 33 stage Scaler, each stage of which divides by two. Stage 10, for instance, supplies 100 pps (one pulse every 10 msec) and the last stage generates a pulse about every 23.3 hours. The last 28 stages of the Scaler can be read out like two 14-bit input channels (registers of the Input-Output Control), thus making time information available to the computer. If the AGC is in the standby mode, only the Clock and the Scaler are operating. When the mode is switched from standby to normal operation, time information is transferred under program control from the Scaler to time counters T2 and T1.

30-21. The Time Pulse Generator generates one time pulse every 0.977  $\mu$ sec and a sequence of twelve time pulses (T01 through T12) every 11.7  $\mu$ sec, which is referred to as one Memory Cycle Time (MCT). The time pulses control the Sequence Generator and other sections of the AGC.

#### 30-22. SEQUENCE GENERATOR

30-23. The Sequence Generator (SQG) generates a set of control pulses, if required, for the subinstruction being executed whenever a time pulse (T01 through T12) is received. Each such set of control pulses is called an

Action. The control pulses control various registers and gates in the Central Processor (CP), the Input-Output Control, and other sections of the AGC. All Machine Instructions (Regular, Involuntary, and Peripheral or Test Instructions) are composed of one, two, or more subinstructions, each sub-instruction consisting of 12 Actions (one MCT).

30-24. The execution of a Regular Instruction (Basic, Extra Code, Channel, or Special Instruction) is initiated by entering its order code into register SQ. When stored in memory, Extra Code and Channel Instructions use the same order codes as the Basic Instructions. However, Extra Code and Channel Instructions are preceded by Special Instruction EXTEND which enters a ONE into bit position EXT of register SQ. When a program is executed, one Regular Instruction after another is transferred from memory into the CP and the order code is entered into register SQ, together with the EXT bit which is entered into bit position SQ-EXT of register SQ.

30-25. Involuntary Instructions (Interrupting Instructions and Counter Instructions) are executed at the request of the Priority Control. Instruction RUPT commands the SQG to interrupt the execution of the program section currently being executed in favor of a programmed operation of higher priority. Instruction RUPT is executed upon request from the Interrupt Priority Control which also supplies the address of the priority program. Instruction RESUME, a Special (Regular) Instruction, orders the SQG to resume the execution of the interrupted program. Instruction GO commands the SQG to restart program execution. This instruction is executed at the occurrence of certain errors.

30-26. Counter Instructions cause the SQG to change the content of a specified counter. They are executed upon request from the Counter Priority Control which also supplies the proper counter address. The Counter Instructions are executed between the execution of Regular Instructions, and each delays the program execution by one MCT.

30-27. Peripheral Instructions are executed under the control of the Computer Test Set (CTS) or the Program Analyzer Console (PAC) during the testing of the AGC on the ground.

30-28. The control pulses generated by the SQG can be grouped in five categories:

- a. Read pulses read content of a register to WA's (for instance, RA reads content of register A to the WA's; content of A is not changed)

- b. Write pulses clear register and write into it information from WA's (for instance, WA writes into A from the WA's)

(cont)

FR-2-130

30-15/30-16

- c. Direct read-write copy content of one register directly (not via WA's) into another register (for instance, A2X copies c(A) into X)

- d. Test pulses test content of certain bit positions and set branch flip-flops accordingly (for instance, TOV tests for overflow)

- e. Special pulses enter certain information into the WA's or into a register, or set certain flip-flops, etc.

All control pulses are defined in Issue 32, table 32-4.

#### 30-29. CENTRAL PROCESSOR

30-30. The Central Processor (CP) consists of various registers, the Adder, the Write Amplifiers (WA's), and the Parity Block. All CP registers are NOR gate flip-flop registers which can be read nondestructively.

30-31. All CP registers are shown in figure 30-6. Registers A, L, Q, Z, and B consist of 16-bit positions (flip-flops) each, which are numbered 16 through 1 from left to right. Register FBANK consists of 5-bit positions numbered 16 and 14 through 11. Register EBANK consists of 3-bit positions numbered 11 through 9. Register S consists of 12-bit positions numbered 12 through 1. Register SQ consists of 7-bit positions, one named SQ-EXT and the remainder numbered 16 and 14 through 10. Registers X and Y of the Adder each also consist of 16-bit positions numbered 16 through 1. The 16 output gates (U) of the Adder, and the WA's are also numbered 16 through 1. All registers mentioned so far may contain instructions, addresses, a code, etc., or a number, but do not contain a parity bit. Whenever a number is contained, the lowest order bit is stored in bit position 1, the highest order bit in bit position 14, and the sign bit (a ZERO for a plus sign and a ONE for a minus sign) is stored in bit position 16. Bit position 15 is used for storing any overflow bit (OV).

30-32. Register G, which serves as a buffer between the CP and the memories, consists of 16-bit positions which are numbered 16 through 1. Any parity bit which is received from memory is transferred to the Parity Block but to no CP register. The 16 inputs to the Parity Block are numbered 16 and 14 through 0. No provision is made to enter an overflow bit into the Parity Block.

#### 30-33. CP REGISTER MANIPULATIONS

30-34. Registers A, L, Q, FBANK, EBANK, and Z are addressable; registers B, S, SQ, Y, X, and G are not addressable. A register is addressable when it can be selected for write-in or read-out by entering the proper address into register S.

# TABLE 30-1 INFORMATION FLOW BETWEEN CP REGISTER BIT POSITIONS AND WRITE AMPLIFIERS

|                  |               | Register                          |           |                  | Rea | d and | Wri | ite L | ines | of W | rite | Am | plifie | ers ( | WA' | s) |   |    |    |    |

|------------------|---------------|-----------------------------------|-----------|------------------|-----|-------|-----|-------|------|------|------|----|--------|-------|-----|----|---|----|----|----|

| Octal<br>Address | Ini-<br>tials | Name                              |           | Control<br>Pulse | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

| 0000             | A             | Accumulator                       |           | WA, WSC          | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

|                  |               |                                   |           | WALS /1          | 14  | 13    | 12  | 11    | 10   | 9    | 8    | 7  | 6      | 5     | 4   | 3  | 2 | 1  | -  | -  |

|                  |               |                                   |           | RA, RSC          | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

| 0001             | L             | Low Order Accumu-                 |           | WL, WSC          | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

|                  |               | lator                             |           | WALS A           | -   | -     | -   | -     | -    | -    | -    | -  | -      | -     | -   | -  | - | -  | 14 | 13 |

|                  |               |                                   |           | RL, RSC          | 16  |       | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

| 0002             | Q             | Return Address Registe            | r         | WQ, WSC          | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

|                  |               | 0                                 |           | RQ, RSC          | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

| 0003             | EBANK         | E Memory Bank Selecto             | r         | WSC              | -   | -     | -   | -     | -    | 11   | 10   | 9  | -      | -     | -   | -  | - | -  | -  | -  |

|                  |               |                                   |           | RSC              | -   | -     | -   | -     | -    | 11   | 10   | 9  | -      | -     | -   | -  | - | -  | -  | -  |

| 0004             | FBANK         | F Memory Bank Selecto             | r         | WSC              | 16  | -     | 14  | 13    | 12   | 11   | -    | -  | -      | -     | -   | -  | - | -  | -  | -  |

|                  |               |                                   |           | RSC              | 16  | -     | 14  | 13    | 12   | 11   | -    | -  | -      | -     | -   | -  | - | -  | -  | -  |

| 0005             | Z             | Program Counter                   |           | WZ, WSC          | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

|                  |               |                                   |           | RZ, RSC          | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

| 0006             | BBANK         | Both registers EBANK<br>and FBANK | EBANK     | WSC              | -   | -     | -   | -     | -    | -    | -    | -  | -      | -     | -   | -  | - | 11 | 10 | 9  |

|                  |               | and F DANK                        | EDANK     | RSC              | -   | -     | -   | -     | -    | -    | -    | -  | -      | -     | -   | -  | - | 11 | 10 | 9  |

|                  |               |                                   | FBANK     | WSC              | 16  | -     | 14  | 13    | 12   | 11   | -    | -  | -      | -     | -   | -  | - | -  | -  | -  |

|                  |               |                                   | - Diritin | RSC              | 16  | -     | 14  | 13    | 12   | 11   | -    | -  | -      | -     | -   | -  | - | -  | -  |    |

| 0007             | ZERO          | ZERO (non-existing reg            | ister)    | RSC              | 16  | 15    | 14  | 13    | 12   | 11   | 10   | 9  | 8      | 7     | 6   | 5  | 4 | 3  | 2  | 1  |

MALS also enters content of bit position 16 of G into bit positions 16 and 15 of A if bit position 1 of G contains a ZERO or enters content of output gate 16 of U into bit positions 16 and 15 if bit position 1 of G contains a ONE.

### TABLE 30-1

### INFORMATION FLOW BETWEEN CP REGISTER BIT POSITIONS AND WRITE AMPLIFIERS (cont)

|                  |               | Register   |                      |                   |                  | Read  | and | Wri | te Li | ines | of W | rite | Amp | lifie | rs (1 | WA's | ) |   |   |   |    |

|------------------|---------------|------------|----------------------|-------------------|------------------|-------|-----|-----|-------|------|------|------|-----|-------|-------|------|---|---|---|---|----|

| Octal<br>Address | Ini-<br>tials |            | Name                 |                   | Control<br>Pulse | 16    | 15  | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

| none             | В             | Buffer Re  | gister with          |                   | WB               | 16    | 15  | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

|                  | С             | direct out | put B and com        | n-                | RB, RC           | 16    | 15  | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

|                  |               | plement o  | utput C              |                   | RL10BB           | -     | -   | -   | -     | -    | -    | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

| none             | S             | Address F  | Register             |                   | WS               | -     | -   | -   | -     | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

| none             | SQ            | Sequence   | Register             |                   | WSQ              | 16    | -   | 14  | 13    | 12   | 11   | 10   | -   | -     | -     | -    | - | - | - | - | -  |

| none             | Y             | Adder wit  | h input regist       | ers               | WY               | 16    | 15  | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

|                  | x             |            | nd output gate       |                   | WY12             | -     | -   | -   | -     | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

|                  | U             |            |                      |                   | WYD /2           | 1 16  | -   | 15  | 14    | 13   | 12   | 11   | 10  | 9     | 8     | 7    | 6 | 5 | 4 | 3 | 2  |

|                  |               |            |                      |                   | RU               | 16    | 15  | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

|                  |               |            |                      |                   | RUS              | 15    |     | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

| none             | G             | Memory E   | Buffer Registe       | r                 | RG               | 16    | 15  | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

|                  |               | Function   | c(S)                 | Control<br>Signal |                  |       |     |     |       |      |      |      |     |       |       |      |   |   |   |   |    |

|                  |               | Direct     | Any Other<br>Address | WG1G,<br>WG5G     | WG               | 16    | 15  | 14  | 13    | 12   | 11   | 10   | 9   | 8     | 7     | 6    | 5 | 4 | 3 | 2 | 1  |

|                  |               | CYR        | 0020                 | WG2G,<br>WG4G     | WG               | 14    | -   | 13  | 12    | 11   | 10   | 9    | 8   | 7     | 6     | 5    | 4 | 3 | 2 | 1 | 16 |

|                  |               | SR         | 0021                 | WG2G,<br>WG5G     | WG               | 16 14 | -   | 13  | 12    | 11   | 10   | 9    | 8   | 7     | 6     | 5    | 4 | 3 | 2 | 1 | -  |

|                  |               | CYL        | 0022                 | WG3G,<br>WG6G     | WG               | 1     | -   | 16  | 14    | 13   | 12   | 11   | 10  | 9     | 8     | 7    | 6 | 5 | 4 | 3 | 2  |

|                  |               | EDOP       | 0023                 | WG3G,<br>WG5G     | WG               | -     | -   | 7   | 6     | 5    | 4    | 3    | 2   | 1     | -     | -    | - | - | - | - | -  |

$\triangle$  There are exceptions where content of WA 16 is not entered into bit position 1 of Y.

Table 30-1 lists those control pulses in addition to control pulses WSC and RSC. Control pulses WSC and RSC are applied to all addressable registers for write-in or read-out, but only that register, the register of which is contained in register S, is written into or read out.

30-35. A word can be transferred from one CP register to another either via the WA's or directly. Read and Write control pulses (paragraph 30-28) occur simultaneously and gate the read gates of the transmitting and the write gates of the receiving register at the same time and thus allow a word to flow from one register to another via the WA's. (Refer to table 30-1). The flow of information to and from the WA's occurs on two different sets of lines, the read and write lines. When one read pulse and two or three write control pulses occur simultaneously, the same information is entered into two or three registers. Direct read-write pulses transfer information directly from one register to only one other register.

30-36. Information contained in the WA's is written into the corresponding bit position of register A if control pulse WA is applied; information contained in register A is read out to the corresponding WA's if control pulse RA is applied. When control pulse WALS is applied (during a multiplication), the information contained in the WA's is shifted two places to the right while writing into register A whereby the last two bits are shifted into register L. When control pulse WL is applied, information contained in the WA's is written into the corresponding bit positions of register L. Information contained in register L is read into the corresponding WA's by means of control pulse RL except for the content of bit position 16 which is read into WA16 and WA15. Refer to table 30-1.

30-37. Registers Q and Z are written into and read out straight, i.e., from and into the corresponding WA's. Registers FBANK and EBANK are written into and read out straight if address 0003 or 0004 is contained in register S. If register S contains 0006, the content of the WA's is written into or read out straight from register FBANK but shifted eight places as it is written into or read out of register EBANK. Register B is always written into and read out straight; however, the content of register B (by means of control pulse RB) or its complement (by means of RC) can be read into the WA's. Control pulse RL10BB reads only the content of bit positions 10 through 1 into the corresponding WA's.

30-38. Registers S and SQ are written into from the corresponding WA's. Bit position SQ-EXT accepts the EXT bit (paragraph 30-24). 30-39. Both registers Y and X of the Adder are cleared whenever control pulse WY, WY12, or WYD is generated. Control pulse WY writes the content of WA's 16 through 1 into register Y; control pulse WY12 writes only the content of WA's 12 through 1 into register Y. Control pulse WYD cycles the content of the WA's one place to the left as it is written into register Y, thereby doubling the content of the WA's. Information is transferred directly (not via WA's) from register A to register X whenever control pulse A2X is applied. Control pulse RU reads the sum contained in the Adder into the corresponding WA's. Control pulse RUS, which is used in connection with inlink and TWO's complement operations, reads the content of output gate 15 into WA's 16 and 15.

30-40. Register G is able to exchange information (except the parity bit) with E or F Memory on one side, and with the CP registers on the other side. Words stored in E or F Memory consist of 16 bits numbered 15 through 0 where bit number 0 is the parity bit. If a memory location contains a number, bit position 15 stores the sign bit and bit position 1 the lowest order bit. When a word is transferred from E or F Memory to register G, bit number 15 is entered into bit positions 16 and 15 of register G while bits 14 through 1 are entered into the corresponding bit positions of register G. Entering a sign bit into bit positions 16 and 15 has the effect of providing a sign bit in bit position 16 and a plus or minus zero (ZERO or ONE) in bit position 15, i.e., in front of the fourteen value bits. Likewise, the content of bit positions 16 and 14 through 1 of register G is transferred to bit positions 15 through 1 in E Memory while the new parity bit, which is supplied by the Parity Block, is entered into bit position 0. The content of bit position 15 of register G is not Consequently, any overflow bit (opposite to sign transferred to memory. bit) which might be contained in bit position 15 is lost on the way to memory.

30-41. Whenever register G is read into the GP, the content of its bit positions is transferred to the corresponding WA's. When the content of the WA's is written into register G, normally WA's 16 through 1 are gated into the corresponding bit positions of register G. If register S contains address 0020, 0021, or 0022, the content of WA's 16 and 14 through 1 is cycled one place to the right, shifted one place to the right, or cycled one place to the left, respectively, while writing into bit positions 16 and 14 through 1 of register G (table 30-1). If register S contains address 0023, the content of the WA's is shifted seven places to the right, as requested during the breaking of Interpretive Instruction Words.

#### 30-42. ADDER

30-43. The Adder, the arithmetic unit of the AGC, is able to add two ONE's complement or two cyclic TWO's complement numbers at a time. Normally, an addition is carried out in the ONE's complement number system.

The Adder has two input registers (X and Y) and a bank of output gates (U). Two ONE's complement numbers to be added can be of the same or opposite sign. Numbers containing fourteen value bits can be added; the Adder generates an additional bit in bit position 15 in case of positive or negative overflow. Control pulses WY, WY12, and WYD reset both the X and Y registers; therefore, the Y register must be loaded first or simultaneously with register X. The arithmetic sum of the two values is available at output gate U less than 1  $\mu$ sec after both operands have been entered. The Sequence Generator, on command, can enter the positive quantity one (000001) or the negative quantity one (17776) into register X, or force a carry into the Adder.

As shown in figure 30-7, the bit positions of the Adder registers 30-44. (X and Y) and the output gates (U) are numbered 16 through 1. (No parity bit is entered into the Adder.) When an operand is gated from E or F Memory into register Y (via register G), its sign (SG) is entered into bit positions 16 and 15. A plus is represented by a ZERO, a minus by a ONE. Entering a sign bit into bit position 15 is equivalent to providing an additional value bit, either a plus or a minus zero (which is represented by a ZERO or a ONE) in front of the fourteen-bit value. When an operand is gated from register A into the corresponding bit positions of register X (control pulse A2X), its sign bit is entered into bit position 16 only. Bit position 15 could receive an overflow bit but, normally, contains the same bit as bit position 16. If an overflow occurs during an addition, the Adder supplies a ONE for a plus overflow, or a ZERO for a minus overflow at output gate 15. This additional output bit is labeled OV. Output gate 16 always contains the correct sign of the sum.

30-45. The upper half of figure 30-8 illustrates the principle of adding two ONE's complement numbers. For simplification, each number consists of two sign bits as normally entered into bit positions 16 and 15 of registers Y and X, and of only 3 value bits instead of 14. In reality, the largest octal number resulting from ONE's complement addition as provided by the sixteen output gates (U) is + 77777 (quantity 077777), the smallest is - 77777 (quantity 100000). Counters are incremented or decremented by adding the quantity plus one or minus one to whatever might be contained in the counter.

30-46. The lower half of figure 30-8 illustrates the principle of adding two cyclic TWO's complement numbers. A cyclic TWO's complement number stored in memory can be interpreted in two different ways. One can consider the fifteen bits stored in bit positions 15 through 1 as 15 value bits representing positive TWO's complement numbers only which express angular information from 0° to 360°. One can also consider the bit stored in bit position 15 as a sign bit and the bits stored in bit positions 14 through 1 as the value bits representing positive TWO's complement numbers which express angles from 0° to plus 180°, or negative TWO's complement numbers which express angles from 0° to minus 180°. The first way of interpretation better explains cyclic TWO's complement operations.

30-47. Whenever cyclic TWO's complement information is transferred from memory, bit 15 is entered into bit positions 16 and 15 of the Adder. Whenever a cyclic TWO's complement sum is transferred from the output gates to E Memory, the content of output gate 15 is entered into bit positions 16 and 15 of register G, and finally read from bit position 16 of register G into bit position 15 of the addressed E Memory location. In reality, the largest octal quantity which can result from a cyclic TWO's complement addition is 7777. In the examples of figure 30-8, four-bit numbers are assumed whereby the highest order bit is entered into two bit positions of register Y or X.

#### 30-48. PARITY BLOCK

30-49. When a word is transferred from memory to the CP, bits 15 through 1 are entered into register G which passes these fifteen bits on to the Parity Block. Bit 0, the parity bit, is transferred from memory directly to the Parity Block where it is stored in the SAP flip-flop (gates 34245/34246). Bits 15 through 1 are fed into a parity tree which generates a new parity bit (PC15). If bits 15 through 1 contain an odd number of ONE's, bit PC15 becomes a ZERO; if they contain an even number of ONE's, bit PC15 becomes a ONE. The new parity bit (PC15) and the original parity bit (bit 0 stored in the SAP flip-flop) are compared and signals PALE (parity alarm) and MPAL/ are generated if the two bits do not agree and if the word was received from memory (octal address 0010 or larger). All sixteen bits (bits 15 through 0) of a word stored in memory must always contain an odd number of ONE's which

Figure 30-8. Summation of Two Binary Numbers

is established by entering the proper parity bit. The parity bit provides a simple means of detecting single errors, or any odd number of errors when reading out of F or E Memory. Registers 0000 through 0007 do not store a parity bit.

30-50. Bits 16 and 14 through 1 of a word entered into register G from a CP register are passed on to the Parity Block in a similar way; however, no test for correct parity is made and bit CP15 generates signal GEMP which writes the parity bit into E Memory if required.

#### 30-51. MEMORIES

30-52. The Erasable (E) Memory is a coincident-current ferrite core.array capable of storing 2048 sixteen-bit words. The selection logic (SLE) (figure 30-6) together with the x and y selection, the z drivers, the 16 sense amplifiers (SAE's), and the memory cycle timer (MCTE) permit addressing certain location in E Memory. Information can be transferred from the addressed location to register G at time pulse T04 or vice versa at time pulse T10. Readout of the E Memory is destructive; however, information can be preserved for later use by writing it back into the addressed location after readout if no new information is to be entered. The selection logic SLE is under the control of registers S and EBANK.

30-53. The Fixed (F) Memory consists of six core rope modules which are built from Mo-perm magnetic cores and is capable of storing 36, 864 sixtenbit words. The addressing scheme employed allows the extension of Fixed Memory to 65, 536 words. The selection logic (SLF) together with various drivers, the sense amplifiers (SAF's), and the memory cycle timer (MCTF) make it possible to address a certain location in F Memory and to read its content into register G at T06. Information stored in F Memory is wired in and cannot be destroyed during readout, therefore, it does not have to be preserved for writing back into F memory. The selection logic (SLF) is under the control of registers S, FBANK, and FEXT. Register FEXT, which consists of three bit positions numbered 7 through 5, is addressed like a register in the Input-Output Control.

#### 30-54. ADDRESSING

30-55. The E Memory can be subdivided into eight E Banks (0 through 7) as indicated in table 30-2. Each bank is capable of storing 256 words. The first 8 locations of E-Bank 0 are not used because their addresses are needed to address the CP registers. Another 12 addresses are reserved for address-ing special locations and 29 for addressing counters, all of which are part of E-Bank 0. The remaining 207 addresses are used for addressing those locations of E-Bank 0 which are accessible for general use.

30-56. E-Banks 0, 1, and 2 are referred to as Unswitched E Memory because all their locations (as well as the CP registers) can be addressed by entering their addresses into register S without regard to what might be contained (XXX) in register EBANK. E-Banks 3 through 7 are referred to as Switched E Memory because all their locations can be addressed only if the respective bank number is contained in register EBANK. Locations in Unswitched E Memory can also be addressed as locations in Switched E Memory if the proper bank number is contained in register EBANK. Of course, the contents of registers FBANK and FEXT are irrelevant whenever any location in the CP or E Memory is addressed.

(text continued on page 30-32)

# TABLE 30-2 E ADDRESSING

| Regi                 | ste   | r or Location        | Octal      | Address                | c()    | FEX    | Г)     |        | c(F    | BAN    | K)     |        | c(E    | BANH   | ()     |        |        |        | с      | (S)    |        |        |             |            |        |   |

|----------------------|-------|----------------------|------------|------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------------|------------|--------|---|

|                      | 0     | Groups               | ЕМА        | Real                   | 7      | 6      | 5      | 16     | 14     | 13     | 12     | 11     | 11     | 10     | 9      | 12     | 11     | 10     | 9      | 8      | 7      | 6      | 5 4         | 4 3        | 2      | 2 |

|                      |       | СР                   | 0000-0007  | 0000-0007<br>1400-1407 | x<br>x | x<br>0 | x<br>0 | x<br>0 | 0<br>0 | 0<br>0 | 0<br>1 | 0<br>1 | 0<br>0 | 0<br>0 | 0<br>0 |             | 0 y<br>0 y |        |   |

| y                    | a     | Special<br>Locations | 0010-0023  | 0010-0023<br>1410-1423 | x<br>x | x<br>0 | x<br>0 | x<br>0 | 0<br>0 | 0<br>0 | 0<br>1 | 0<br>1 | 0<br>0 | 0<br>0 | 0<br>0 |             | y y<br>y y | у<br>У | , |

| Memory               | -BANK | Counters             | 0024-0060  | 0024-0060<br>1424-1460 | x<br>x | x<br>0 | x<br>0 | х<br>0 | 0<br>0 | 0<br>0 | 0<br>1 | 0<br>1 | 0<br>0 | 0<br>0 | 2      |             | y y<br>y y | у<br>у |   |

| 6                    | Ë.    | General Use          | 006 1-0377 | 0061-0377<br>1461-1777 | x<br>x | x<br>0 | x<br>0 | x<br>0 | 0<br>0 | 0<br>0 | 0<br>1 | 0<br>1 | у<br>у | y<br>y | y<br>y | уу          | уу<br>уу   | у<br>у |   |

| Unswitched           |       | E-Bank 1             | 0400-0777  | 0400-0777<br>1400-1777 | x<br>x | x<br>0 | ж<br>0 | x<br>1 | 00     | 0<br>0 | 0<br>1 | 1<br>1 | у<br>У | y<br>y | y<br>y |             | уу<br>уу   | у<br>у |   |

| Una                  |       | E-Bank 2             | 1000-1377  | 1000-1377<br>1400-1777 | x<br>x | x<br>0 | x<br>1 | x<br>0 | 0<br>0 | 0<br>0 | 1<br>1 | 0<br>1 | у<br>у | у<br>У | y<br>y | у<br>у<br>у | уу<br>уу   | у<br>у |   |

|                      |       | E-Bank 3             | 1400-1777  | 1400-1777              | x      | x      | x      | x      | x      | x      | x      | x      | 0      | 1      | 1      | 0      | 0      | 1      | 1      | у      | у      | у      | У           | у у        | у      | 7 |

| ed E                 | Å 10  | E-Bank 4             | 2000-2377  | 1400-1777              | x      | x      | x      | х      | x      | х      | x      | х      | 1      | 0      | 0      | 0      | 0      | 1      | 1      | У      | у      | у      | у           | у у        | у      | 1 |

| Switched ]<br>Memory | IIIat | E-Bank 5             | 2400-2777  | 1400-1777              | х      | x      | x      | x      | x      | x      | x      | x      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | У      | у      | у      | У           | у у        | у      | 1 |

| Sw                   | 4     | E-Bank 6             | 3000-3377  | 1400-1777              | x      | x      | x      | x      | х      | х      | x      | х      | 1      | 1      | 0      | 0      | 0      | 1      | 1      | У      | у      | у      | У           | у у        | У      | , |

|                      |       | E-Bank 7             | 3400-3777  | 1400-1777              | х      | x      | x      | x      | x      | x      | x      | x      | 1      | 1      | 1      | 0      | 0      | 1      | 1      | у      | у      | у      | у           | у у        | у      | 1 |

x means 0 or 1 which does not have an effect on addressing. y means 0 or 1 as defined by address.

CP registers and Special Locations will be addressed as E-Bank 0 only under exceptional circumstances.

# TABLE 30-3 F ADDRESSING

|             | oristo            | r or Location | Octal A     | ddress                 | c(FEXT)        | c(FBANK)                 | c(EBANK)       | c(S)2                                                |

|-------------|-------------------|---------------|-------------|------------------------|----------------|--------------------------|----------------|------------------------------------------------------|

|             |                   | roups         | FMA         | Real                   | 7 6 5          | 16 14 13 12 11           | 11 10 9        | 12 11 10 9 8 7 6 5 4 3 2 1                           |

|             | ed F<br>tory      | F- Bank 02    | 04000-05777 | 4000-5777<br>2000-3777 | x x x<br>x x x | x x x x x x<br>0 0 0 1 0 | x x x<br>x x x | 1 0 y y y y y y y y y y y 0 1 y y y y y              |

|             | Fixed F<br>Memory | F-Bank 03     | 06000-07777 | 6000-7777<br>2000-3777 | x x x<br>x x x | x x x x x x<br>0 0 0 1 1 | x x x<br>x x x | 1 1 y y y y y y y y y y<br>0 1 y y y y y y y y y y y |

|             |                   | F-Bank 00     | 00000-01777 | 2000-3777              | x x x          | 0 0 0 0 0                | x x x          | 0 1 ууу ууу у ууу                                    |

|             |                   | F-Bank 01     | 02000-03777 | 2000-3777              | x x x          | 0 0 0 0 1                | x x x          | 0 1 ууу ууу у ууу                                    |

|             |                   | F-Bank 04     | 10000-11777 | 2000-3777              | x x x          | 0 0 1 0 0                | x x x          | 0 1 ууу ууу у ууу                                    |

|             |                   | F-Eank 05     | 12000-13777 | 2000-5777              | x x x          | 0 0 1 0 1                | x x x          | 0 1 ууу ууу у ууу                                    |

| I X         |                   | F-Bank 06     | 14000-15777 | 2000-3777              | x x x          | 0 0 1 1 0                | x x x          | 0 1 ууу ууу у ууу                                    |

| anne        | ory               | F-Bank 07     | 16000-17777 | 2000-3777              | x x x          | 0 0 1 1 1                | x x x          | 0 1 ууу ууу у ууу                                    |

| EXT-Channel | Memory            | F-Fank 10     | 20000-21777 | 2000-3777              | x x x          | 0 1 0 0 0                | x x x          | 0 1 ууу ууу у ууу                                    |

| EXT         | 14                | F-Bank 11     | 22000-23777 | 2000-3777              | x x x          | 0 1 0 0 1                | x x x          | 0 1 ууу ууу у ууу                                    |

| Eq.         | Common            | F-Bank 12     | 24000-25777 | 2000-3777              | x x x          | 0 1 0 0 1                | x x x          | 0 1 y y y y y y y y y                                |

|             | Com               | F-Bank 13     | 26000-27777 | 2000-3777              | x x x          | 0 1 0 1 1                | x x x          | 0 1 ууу ууу у ууу                                    |

|             |                   | F-Bank 14     | 30000-31777 | 2000-3777              | x x x          | 0 1 1 0 0                | x x x          | 0 1 ууу ууу у ууу                                    |

|             |                   | F-Bank 15     | 32000-33777 | 2000-3777              | x x x          | 0 1 1 0 1                | x x x          | 0 1 ууу ууу у ууу                                    |

|             |                   | F-Bank 16     | 34000-35777 | 2000-3777              | x x x          | 0 1 1 1 0                | x x x          | 0 1 y y y y y y y y y                                |

|             |                   | F-Bank 17     | 36000-37777 | 2000-3777              | x x x          | 0 1 1 1 1                | x x x          | 0 1 ууу ууу у ууу                                    |

|             |                   | F-Bank 20     | 40000-41777 | 2000-3777              | x x x          | 1 0 0 0 0                | x x x          | 0 1 у у у у у у у у у                                |

$\bigwedge$  x means 0 or 1 which does not have an effect on addressing.

$\triangle$  y ineans 0 or 1 as defined by address.

### TABLE 30-3

# F ADDRESSING (cont)

| Re      | giste   | er or Location | Octal A       | ddress    | c(. | FEX | Т) 🛆 |    | c(FE | BANK |    |    | c(E | BANI | $\Delta$ |    |    |    | (          | c(S) | A          |    |    |       |     |

|---------|---------|----------------|---------------|-----------|-----|-----|------|----|------|------|----|----|-----|------|----------|----|----|----|------------|------|------------|----|----|-------|-----|

|         |         | Groups         | FMA           | Real      | 7   | 6   | 5    | 16 | 14   | 13   | 12 | 11 | 11  | 10   | 9        | 12 | 11 | 10 | 9          | 8    | 7          | 6  | 5  | 4 3   | 2 1 |

| t)      | nt)     | F-Bank 21      | 42000-43777   | 2000-3777 | x   | х   | х    | 1  | 0    | 0    | 0  | 1  | х   | х    | х        | 0  | 1  | y  | y.         | y    | y          | y  | у  | y. y. | y . |

| (cont)  | (cont)  | F-Bank 22      | 44000-45777   | 2000-3777 | х   | х   | х    | 1  | 0    | 0    | 1  | 0  | x   | x    | x        | 0  | 1  | v  | Ŋ          | y.   | у          | y. | y  | y. y. | у у |

| ×       | Memory  | F-Bank 23      | 46000-47777   | 2000-3777 | х   | х   | x    | 1  | 0    | 0    | 1  | 1  | x   | x    | x        | 0  | 1  | У  | у          | y.   | <i>y</i> . | λ. | y  | y y   | у у |

| Channel | Mer     | F-Bank 24      | 50000-51777   | 2000-3777 | х   | х   | x    | 1  | 0    | 1    | 0  | 0  | x   | х    | х        | 0  | 1  | y  | у          | y.   | <i>y</i> . | y. | y. | y y   | у у |

| -Cha    | Ц<br>ц  | F-Bank 25      | 52000-53777   | 2000-3777 | x   | х   | х    | 1  | 0    | 1    | 0  | 1  | x   | x    | x        | 0  | 1  | у  | у          | y    | y          | у  | у  | у у   | у у |

| FEXT    | Common  | F-Bank 26      | 54000-55777   | 2000-3777 | x   | х   | x    | 1  | 0    | 1    | 1  | 0  | x   | x    | x        | 0  | 1  | У  | y          | у    | у          | у  | у  | у у   | у у |

| E E     | Cor     | F-Bank 27      | 56000-57777   | 2000-3777 | x   | х   | х    | 1  | 0    | 1    | 1  | 1  | x   | x    | x        | 0  | 1  | y  | ĩ.         | у    | У          | у  | у  | у у   | у у |

|         |         | F-Bank 30      | 060000-061777 | 2000-3777 | 0   | х   | х    | 1  | 1    | 0    | 0  | 0  | x   | х    | х        | 0  | 1  | у  | у          | у    | у          | у  | у  | у у   | у у |

|         | ν,      | F-Bank 31      | 062000-063777 | 2000-3777 | 0   | x   | x    | 1  | 1    | 0    | 0  | 1  | x   | x    | x        | 0  | 1  | у  | y          | у    | y          | у  | у  | у у   | уу  |

| 0       | -0 10   | F-Bank 32      | 064000-065777 | 2000-3777 | 0   | х   | х    | 1  | 1    | 0    | 1  | 0  | x   | х    | х        | 0  | 1  | y  | y          | y    | y          | у  | y. | y y   | у у |

|         | Channel | F-Bank 33      | 066000-067777 | 2000-2777 | 0   | х   | х    | 1  | 1    | 0    | 1  | 1  | x   | х    | х        | 0  | 1  | y  | <i>ì</i> . | ì.   | у          | y  | у. | y y   | у у |

|         | 5       | F-Bank 34      | 070000-071777 | 2000-3777 | 0   | х   | x    | 1  | 1    | 1    | 0  | 0  | x   | x    | x        | 0  | 1  | y  | y          | Ŋ.   | Ņ.         | ŷ. | у  | у у   | у у |

|         | I X A A | F-Bank 35      | 072000-073777 | 2000-3777 | 0   | x   | x    | 1  | 1    | 1    | 0  | 1  | x   | x    | x        | 0  | 1  | y. | y          | у    | y.         | y. | y. | y y   | y y |

|         | 4       | F-Bank 36      | 074000-075777 | 2000-3777 | 0   | x   | x    | 1  | 1    | 1    | 1  | 0  | x   | x    | x        | 0  | 1  | у  | ì.         | Ņ.   | y.         | y  | у  | y y   | y y |

|         |         | F-Bank 37      | 076000-077777 | 2000-3777 | 0   | х   | x    | 1  | 1    | 1    | 1  | 1  | x   | x    | x        | 0  | 1  | y  | λ.         | y    | Ŋ.         | Ŋ. | у  | y y   | y y |

$\begin{array}{c} & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$

### TABLE 30-3

### F ADDRESSING (cont)

| Register or Location |   | or Location | Octal Address |           |   | c(FEXT) |   |    | c(FBANK) |    |    |    |    |    | c(EBANK) |    |    |    |    | c(S) | A     |    |            |    |    |

|----------------------|---|-------------|---------------|-----------|---|---------|---|----|----------|----|----|----|----|----|----------|----|----|----|----|------|-------|----|------------|----|----|

| nc <sub>b</sub> ,    |   | oups        | FMA           | Real      | 7 | 6       | 5 | 16 | 14       | 13 | 12 | 11 | 11 | 10 | 9        | 12 | 11 | 10 | 9  | 8    | 7 3   | 5  | 4          | 3  | 2  |

|                      |   | F-Banl; 40  | 100000-101777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 0  | 0  | 0  | x  | х  | х        | 0  | 1  | у  | λ. | у    | у у   | У  | 5          | у  | у  |

|                      |   | F-Bank 41   | 102000-103777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 0  | 0  | 1  | x  | x  | х        | 0  | 1  | у  | y  | у    | у у   | у  | у          | у  | у  |

| el 4                 |   | F-Bank 42   | 104000-105777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 0  | 1  | 0  | x  | x  | x        | 0  | 1  | y  | у  | у    | у у   | у  | у          | у  | у  |

| Channel              |   | F-Bank 43   | 106000-107777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 0  | 1  | 1  | x  | x  | x        | 0  | 1  | y  | у  | у    | уу    | у  | у          | y  | у  |

| 1                    |   | F-Bank 44   | 110000-111777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 1  | 0  | 0  | x  | x  | x        | 0  | 1  | у  | у  | у    | у у   | у  | у          | у  | у  |

| FEXT                 |   | F-Bank 45   | 112000-113777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 1  | 0  | 1  | x  | x  | x        | 0  | 1  | у  | у  | у    | у у   | у  | у          | у  | у  |

| 1. The               | Γ | F-Bank 46   | 114000-115777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 1  | 1  | 0  | x  | x  | x        | 0  | 1  | у  | у  | у    | у у   | у  | у          | у  | у  |

|                      | Γ | F-Bank 47   | 116000-117777 | 2000-3777 | 1 | 0       | 0 | 1  | 1        | 1  | 1  | 1  | x  | x  | x        | 0  | 1  | у  | y  | у    | у у   | у  | у          | y. | у  |

|                      |   | F-Bank 50   | 120000-121777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 0  | 0  | 0  | x  | x  | х        | 0  | 1  | у  | у  | у    | у у   | у  | у          | у  | у  |

| ŝ                    |   | F-Bank 51   | 122000-123777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 0  | 0  | 1  | x  | x  | x        | 0  | 1  | y  | У  | у    | у у   | у  | у          | у  | у  |

| Channel              | Γ | F-Banl: 52  | 124000-125777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 0  | 1  | 0  | x  | x  | x        | 0  | 1  | y. | у  | у    | у у   | у  | у          | у  | у  |

| - Cha                | Γ | F-Bank 53   | 126000-127777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 0  | 1  | 1  | x  | x  | х        | 0  | 1  | y  | y  | y    | y y   | y  | y          | y  | y. |

| FEXT.                |   | F-Bank 54   | 130000-131777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 1  | 0  | 0  | x  | x  | х        | 0  | 1  | y  | y  | у    | s s   | y. | y.         | y  | y  |

| ы                    |   | F-Bank 55   | 132000-133777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 1  | 0  | 1  | x  | x  | x        | 0  | 1  | y  | у  | y    | y. y. | у  | y          | y  | y  |

|                      |   | F-Banl: 56  | 134000-135777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 1  | 1  | 0  | x  | х  | x        | 0  | 1  | у  | у  | у    | y. y. | y  | y          | y  | y  |

|                      |   | F-Bank 57   | 136000-137777 | 2000-3777 | 1 | 0       | 1 | 1  | 1        | 1  | 1  | 1  | x  | x  | x        | 0  | 1  | v  | y  | v    | y y   | v  | <i>y</i> . | 1. | y  |

$\triangle$  x means 0 or 1 which does not have an effect on addressing.

x y means 0 or 1 as defined by address.

Banks 44 through 77 do not exist (paragraph 30-57)

# TABLE 30-3 F ADDRESSING (cont)

| Register or Location |            | Octal Address |           |   | c(FENT) |   |    | c(FBANK) |    |    |    |    |    | c(EBANK) |    |    | c(s) 🖄 |            |            |              |           |    |            |            |  |  |

|----------------------|------------|---------------|-----------|---|---------|---|----|----------|----|----|----|----|----|----------|----|----|--------|------------|------------|--------------|-----------|----|------------|------------|--|--|

| Bion                 | Groups     | FMA           | Real      | 7 | 6       | õ | 16 | 14       | 13 | 12 | 11 | 11 | 10 | 9        | 12 | 11 | 10     | 9          | 8          | 7 6          | 5         | 4  | 3          | 2          |  |  |

|                      | F-Bank 60  | 140000-141777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 0  | 0  | 0  | x  | х  | х        | 0  | 1  | Ŋ      | Ŋ.         | у          | y y          | у         | y. | 2          | y :        |  |  |

|                      | F-Bank 61  | 142000-143777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 0  | 0  | 1  | x  | x  | x        | 0  | 1  | у      | 3.         | <i>.</i> . | <i>ì. ì.</i> | y         | Ŋ. | у.         | -          |  |  |

| el 6                 | F-Bank 62  | 144000-145777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 0  | 1  | 0  | x  | х  | x        | 0  | 1  | У      | y          | y.         | y y          | y         | γ. | y.         | 2          |  |  |

| hann                 | F-Bank 63  | 146000-147777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 0  | 1  | 1  | x  | x  | x        | 0  | 1  | У      | y.         | <i>y</i>   | y y          | y.        | у  | <i>ì.</i>  | 5          |  |  |

| L-CI                 | F-Bank 64  | 150000-151777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 1  | 0  | 0  | x  | x  | x        | 0  | 1  | У      | <i>y</i> . | y.         | у. у.        | y.        | у  | y.         | у          |  |  |

| FEXT-Channel         | F-Bank 65  | 152000-153777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 1  | 0  | 1  | x  | x  | x        | 0  | 1  | у      | y          | y.         | y. y         | y.        | У  | y          | 3.         |  |  |

| щ                    | F-Bank 66  | 154000-155777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 1  | 1  | 0  | x  | x  | x        | 0  | 1  | y.     | У          | у          | y. y.        | у         | у  | y          | y          |  |  |

|                      | F-Bank 67  | 156000-157777 | 2000-3777 | 1 | 1       | 0 | 1  | 1        | 1  | 1  | 1  | x  | x  | x        | 0  | 1  | y      | y.         | y.         | y y          | у         | У  | у          | У          |  |  |

|                      | F-Bank 70  | 160000-161777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 0  | 0  | 0  | x  | x  | x        | 0  | 1  | Ŋ      | y.         | <i>y</i>   | <i>z. z.</i> | 2.        | y  | y.         | y          |  |  |

| 2                    | F-Bank 71  | 162000-163777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 0  | 0  | 1  | x  | x  | x        | 0  | 1  | y      | у          | У          | y y          | y         | У  | <i>s</i> . | <i>S</i> . |  |  |

|                      | F-Bank 72  | 164000-165777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 0  | 1  | 0  | x  | х  | х        | 0  | 1  | у      | y.         | Ŋ          | y y          | <i>ì.</i> | у  | y.         | y          |  |  |

| FEXT - Channel       | F-Bank 73  | 166000-167777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 0  | 1  | 1  | x  | x  | х        | 0  | 1  | λ.     | ì.         | <i>ì.</i>  | y y          | y.        | Ŋ. | <i>ì</i> . | N          |  |  |

| 0-1                  | F-Banl: 74 | 170000-171777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 1  | 0  | 0  | x  | x  | x        | 0  | 1  | Ŋ.     | y.         | 5          | y y          | ì.        | y. | ÿ.         | y.         |  |  |

| FEX                  | F-Bank 75  | 172000-173777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 1  | 0  | 1  | x  | x  | x        | 0  | 1  | у      | у          | 2          | N 3          | y.        | Ŋ. | y .        | y          |  |  |

|                      | F-Banl: 76 | 174000-175777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 1  | 1  | 0  | x  | x  | x        | 0  | 1  | y      | Ŋ          | N          | <i>2 2</i>   | у         | y  | y.         | у          |  |  |

|                      | F-Bank 77  | 176000-177777 | 2000-3777 | 1 | 1       | 1 | 1  | 1        | 1  | 1  | 1  | x  | x  | x        | U  | 1  | 1.     | V.         | 1.         | y y          | 1.        | 1. | v          | 5          |  |  |

$\triangle$  x means 0 or 1 which does not have an effect on addressing.

x y means 0 or 1 as defined by address.

Banks 44 through 77 do not exist (paragraph 30-57)

30-31

#### FR-2-130

30-57. The F Memory address field provided can be subdivided into 64 F-Banks (octal 00 through 77 as indicated in table 30-3). Each bank is capable of storing 1024 words. Only 36 F-Banks (00 through 43) are built into the AGC, another 28 F-Banks (44 through 77) could be added, which would require some major modifications of the computer.

30-58. F-Banks 00 through 27 are referred to as FEXT-Channel X because all their locations can be addressed by entering their addresses into registers S and FBANK without regard to what might be contained (XXX) in register FEXT. F-Banks 30 through 37 are referred to as FEXT-Channel 0-3 because all their locations can be addressed if channel numbers 0, 1, 2, or 3 (0XX) are contained in register FEXT. F-Banks 40 through 47, 50 through 57, 61 through 67, etc., are referred to as FEXT-Channel 4, 5, 6, etc., respectively, because all their locations can be addressed only if the correct channel number is contained in register FEXT.

30-59. F-Banks 02 and 03 are also referred to as Fixed-Fixed Memory; the other banks of FEXT-Channel X are referred to as Variable-Fixed Memory. All locations in Fixed-Fixed Memory can be addressed by entering their addresses into register S without regard to what might be contained (XXXXX) in register FBANK. All other locations of F Memory can be addressed only if the proper bank number is contained in register FBANK. Locations in Fixed-Fixed Memory can also be addressed like any other location in F Memory if the proper bank number is contained in register FBANK. The content of register EBANK is irrelevant whenever a location in F Memory is addressed.

30-60. Two different classes of pseudo addresses are used: Erasable Memory Addresses (EMA's) and Fixed Memory Addresses (FMA's). When register S contains ZERO's in both bit positions 12 and 11 it indicates that the register contains a real address which represents an EMA. (Refer to table 30-2). When both bit positions 10 and 9 also contain ZERO's it indicates that a CP register or a location in E-Bank 0 is addressed, regardless of the contents of register EBANK. When bit positions 10 or 9 but not both contain a ONE, a location in E-Bank 1 or 2 is addressed regardless of the contents of register EBANK. When bit positions 10 and 9 both contain a ONE, a location is addressed in that E-Bank the number of which is contained in register EBANK.

30-61. The EMA's are composed of four octal digits which represent eleven binary digits (bits) numbered 11 through 1. Bits 11 through 9 indicate an E-Bank number ( in many cases contained in register EBANK ). Bits 8 through 1 represent that part of the real address which is contained in bit positions 8 through 1 of register S.

30-62. When register S contains a ONE in bit position 12 or 11, or in both, it indicates that the register contains a real address which represents an FMA. (Refer to table 30-3). Whenever bit position 12 contains a ONE, Fixed-Fixed Memory is addressed, regardless of the contents of registers

FBANK and FEXT. Whenever bit position 12 contains a ZERO and bit position 11 a ONE, a location is addressed in that F Bank which is defined by the contents of registers FBANK and FEXT.

30-63. When bit position 16 and 14 of register FBANK both contain ZERO's, or a ZERO and a ONE, and bit position 12 of register S contains a ZERO and bit position 11 a ONE, it indicates that a bank in FEXT-Channel X is addressed in which case the content of register FEXT is irrelevant. When bit positions 16 and 14 of registers FBANK both contain ONE's, a bank in FEXT-Channel 0-3, or 4 through 77 is addressed.

30-64. The FMA's are composed of six octal digits which represent sixteen bits numbered 16 through 1. Bits 16 through 11 indicate an F-Bank number. In many cases this number is contained in register FBANK, or register FEXT and bit positions 13 through 11 of register FBANK. Bits 10 through 1 represent that part of the real address which is contained in bit positions 10 through 1 of register S.

#### 30-65. E LOCATION ASSIGNMENTS AND COUNTER OPERATIONS