ND-1021042

# PROJECT

# APOLLO

# LUNAR EXCURSION MODULE

# PRIMARY GUIDANCE, NAVIGATION, AND CONTROL SYSTEM MANUAL

VOLUME II

GENERAL MOTORS

# ND-1021042

1 FEB 1966

INITIAL TORR 26432 TYPE I APPROVED BY NASA

# APOLLO

LUNAR EXCURSION MODULE

# PRIMARY GUIDANCE, NAVIGATION, AND CONTROL SYSTEM MANUAL

VOLUME II OF II

PREPARED FOR

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION MANNED SPACECRAFT CENTER

BY

AC ELECTRONICS DIVISION OF GENERAL MOTORS MILWAUKEE,WISCONSIN 53201

NASA CONTRACT NAS 9-497

# ND-1021042 MANUAL

#### CONTENTS

| Chapter  |              |                                                     | Volume II                                                                                | Page                             |

|----------|--------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------|

| 4 (cont) |              | 4-5.5<br>4-5.6<br>4-5.7<br>4-5.8<br>4-5.9<br>4-5.10 | Central Processor                                                                        | 4-428<br>4-435<br>4-439<br>4-460 |

|          | 4-6          | Signal Co                                           | onditioner                                                                               | 4-492                            |

|          | 4-7          | LEM Opt                                             | ical Rendezvous Subsystem                                                                | 4-492                            |

| 5        | MISSIC       | ON OPERA                                            | ATIONS                                                                                   | 5-1                              |

|          | 5-1          | Scope .                                             |                                                                                          | 5-1                              |

|          | 5-2          | IMU Coar                                            | rse Alignment                                                                            | 5-1                              |

|          | 5 <b>-3</b>  | IMU Fine                                            | e Alignment                                                                              | 5-1                              |

|          | 5-4          | Transfer                                            | Orbit                                                                                    | 5-2                              |

|          | 5-5          | Powered<br>5-5.1<br>5-5.2<br>5-5.3                  | Descent<br>Phase I - Braking<br>Phase II - Final Approach<br>Phase III - Landing         | 5-2<br>5-2<br>5-2<br>5-7         |

|          | 5 <b>-</b> 6 | Lunar Sta                                           | ay                                                                                       | 5 -7                             |

|          | 5 <b>-</b> 7 | Ascent.                                             |                                                                                          | 5 <del>-</del> 7                 |

|          | 5-8          | Rendezvo                                            | ous and Docking                                                                          | 5-7                              |

| 6        | CHEC         | KOUT ANI                                            | D MAINTENANCE EQUIPMENT                                                                  | 6-1                              |

|          | 6-1          | Scope .                                             |                                                                                          | 6-1                              |

| 7        | CHEC         | KOUT .                                              |                                                                                          | 7-1                              |

|          | 7-1          | Scope .                                             |                                                                                          | 7-1                              |

|          | 7-2          | Primary<br>7-2.1<br>7-2.2<br>7-2.3                  | Guidance, Navigation, and Control System<br>Preparation<br>Checkout<br>Test Descriptions | 7-1<br>7-1<br>7-1<br>7-1         |

#### CONTENTS (cont)

| Chapter |      | · ·                                                                             | Page  |

|---------|------|---------------------------------------------------------------------------------|-------|

|         | 7-3  | Inertial Subsystem         7-3.1       Preparation         7-3.2       Checkout | 7-1   |

|         | 7-4  | Computer Subsystem         7-4.1       Preparation         7-4.2       Checkout | 7-2   |

|         | 7-5  | LEM Optical Rendezvous Subsystem                                                | 7-2   |

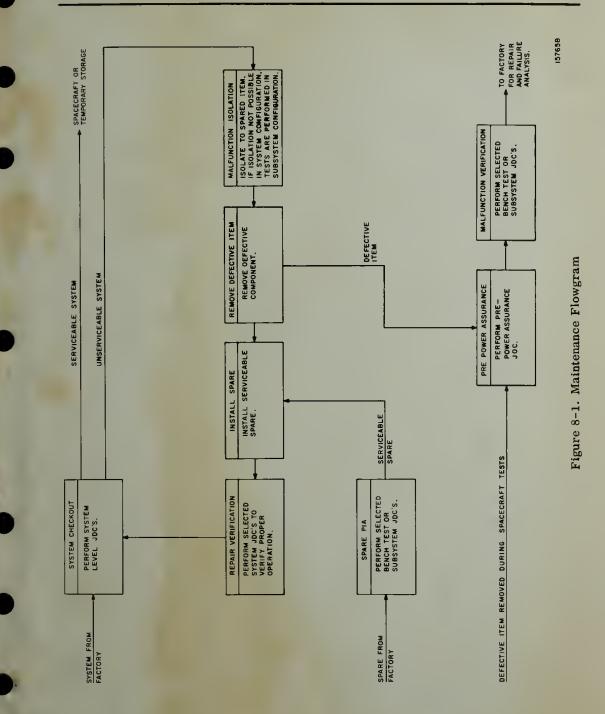

| 8       | MAIN | TENANCE                                                                         | 8-1   |

|         | 8-1  | Scope                                                                           | 8-1   |

|         | 8-2  | Maintenance Concept                                                             | 8-1   |

|         | 8-3  | Malfunction Isolation                                                           | 8-2   |

|         | 8-4  | Double Verification8-4.1Malfunction Verification8-4.2Repair Verification        | 8-2   |

|         | 8-5  | Pre-Installation Acceptance Test                                                | 8-6   |

|         | 8-6  | Removal and Replacement                                                         | 8-6   |

|         | 8-7  | Maintenance Schedule                                                            | 8-6   |

|         | 8-8  | Optical Cleaning                                                                | 8-6   |

| APPENDI | X A  | LIST OF TECHNICAL TERMS AND ABBREVIATIONS                                       | A-1   |

| APPENDI | хв   | RELATED DOCUMENTATION                                                           | 1/B-2 |

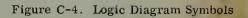

| APPENDI | хс   | LOGIC SYMBOLS                                                                   | .C-1  |

Π-iv

#### **ILLUSTRATIONS**

Figure

Page

#### Volume $\Pi$

| 4-125 | Order Code Processor, Block Diagram              | . 4-233     |

|-------|--------------------------------------------------|-------------|

| 4-126 | Command Generator, Block Diagram                 | . 4-235     |

| 4-127 | Control Pulse Generator, Block Diagram           |             |

| 4-128 | Register SQ Control, Logic Diagram               | 4-239/4-240 |

| 4-129 | Register SW and Decoder, Logic Diagram           | 4-243/4-244 |

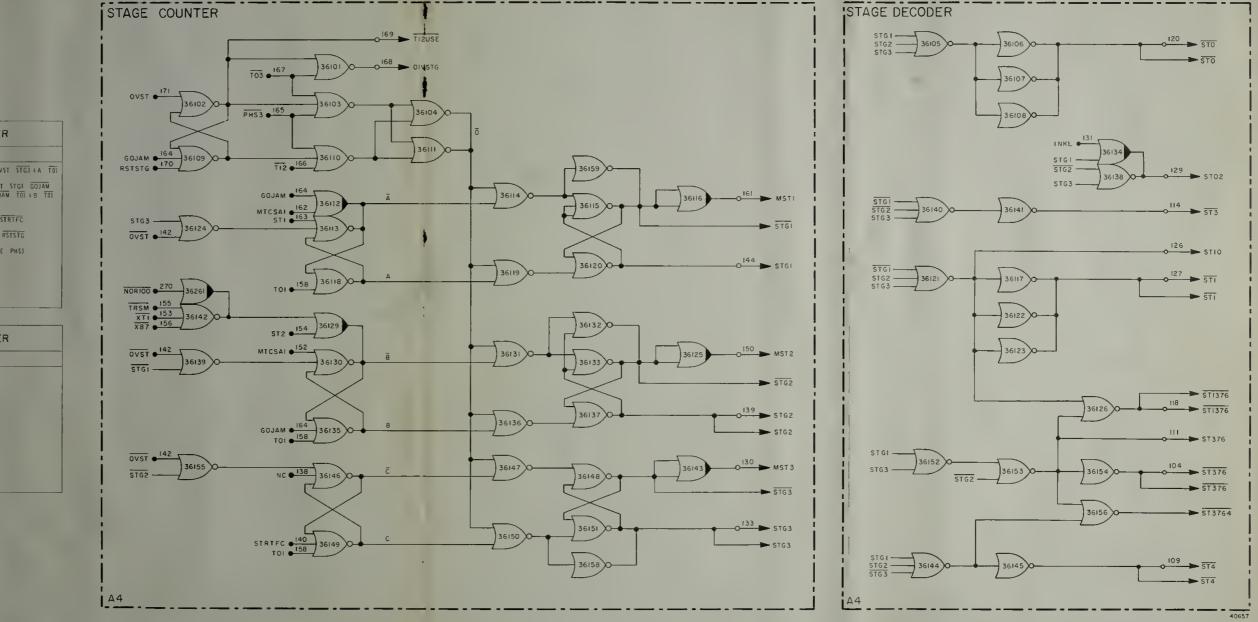

| 4-130 | Stage Counter and Decoder, Logic Diagram         |             |

| 4-131 | Subinstruction Decoder, Logic Diagram            |             |

| 4-132 | Instruction Decoder, Logic Diagram               |             |

| 4-133 | Counter and Peripheral Instruction Control Logic |             |

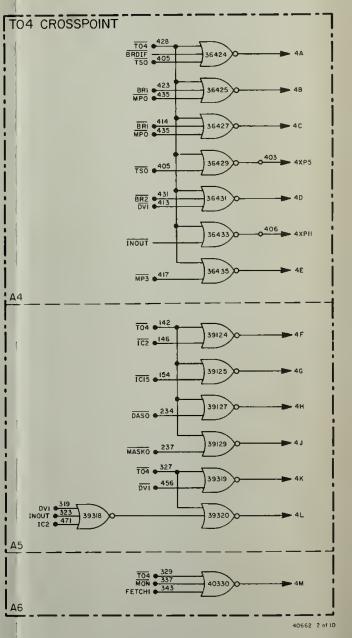

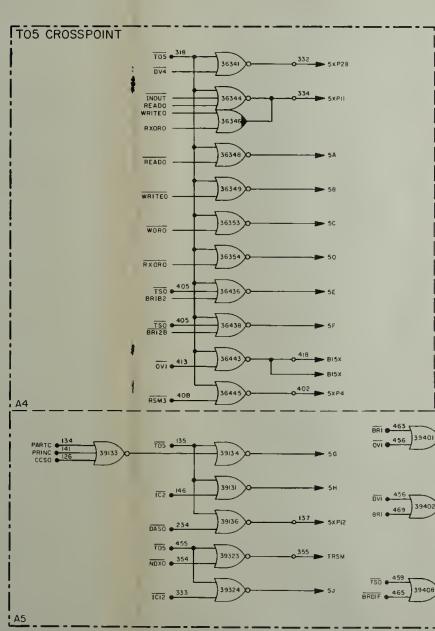

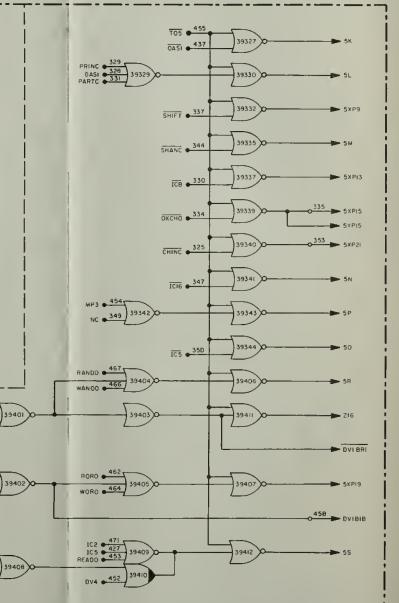

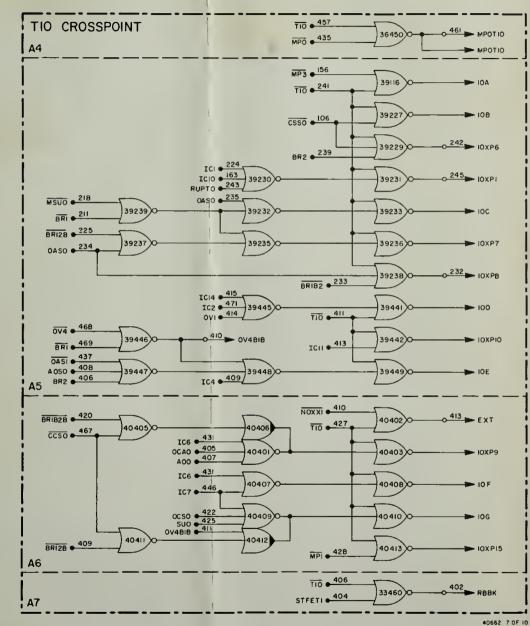

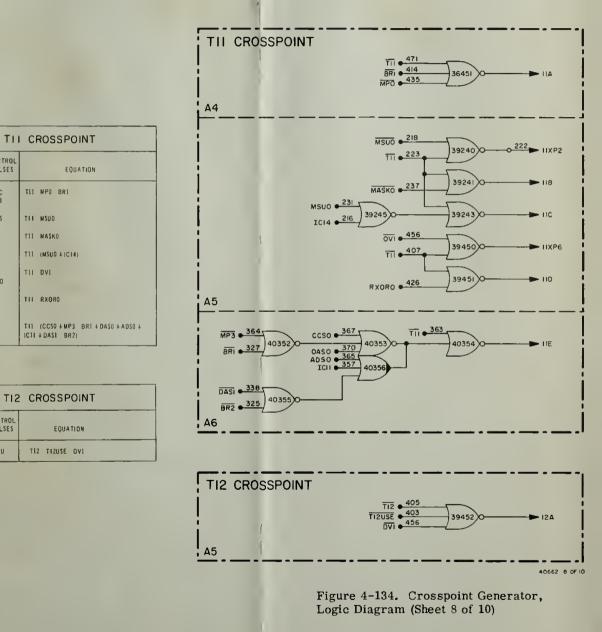

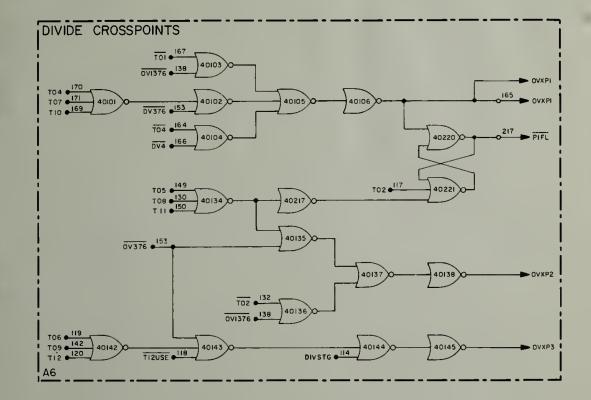

| 4-134 | Crosspoint Generator, Logic Diagram              | 4-281/4-282 |

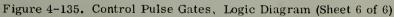

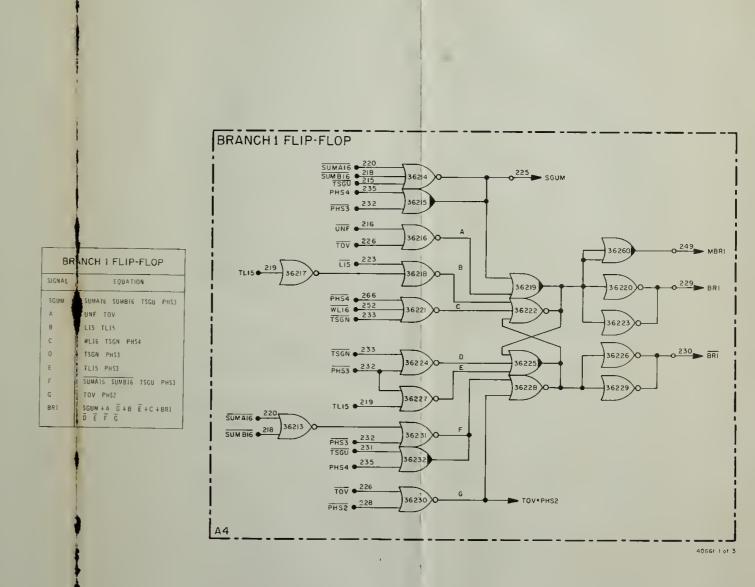

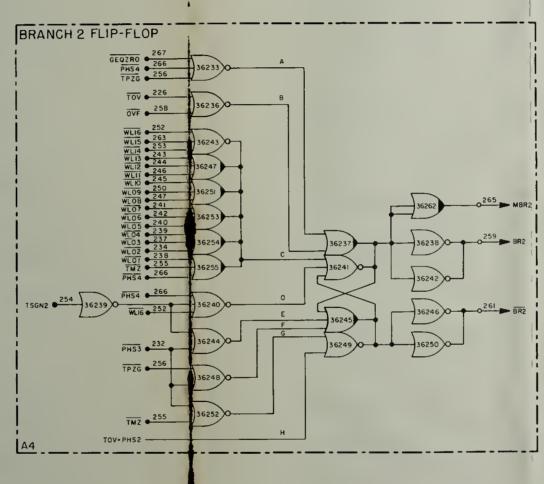

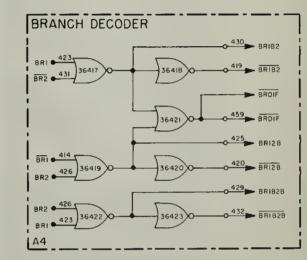

| 4-135 | Control Pulse Gates, Logic Diagram               | 4-351       |

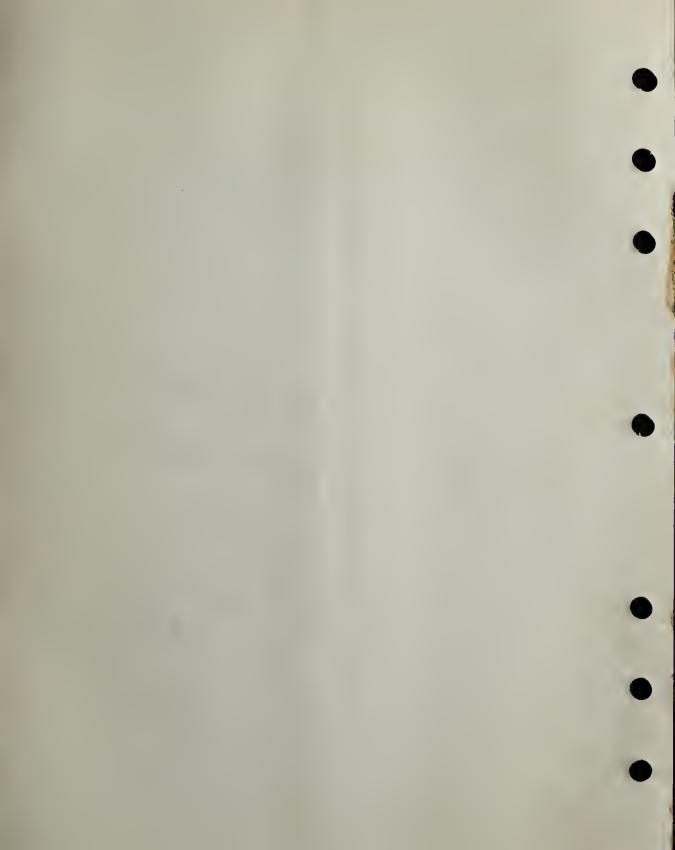

| 4-136 | Branch Control, Logic Diagram                    | 4-359/4-360 |

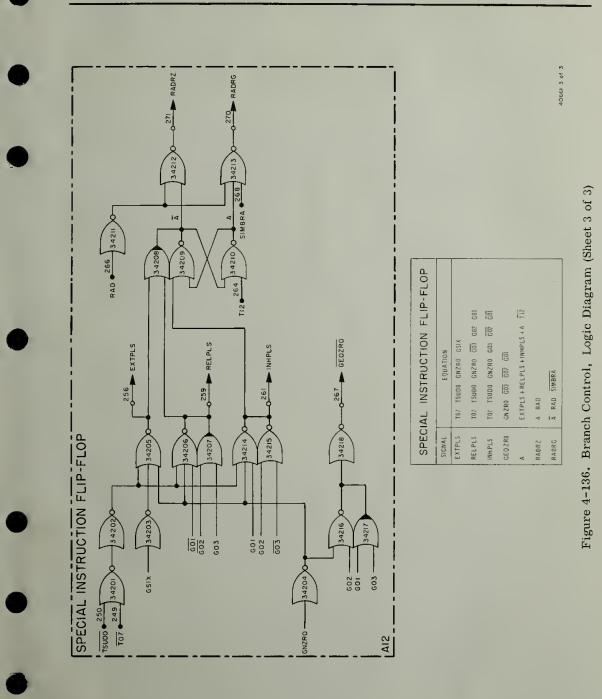

| 4-137 | Word Formats                                     | 4-366       |

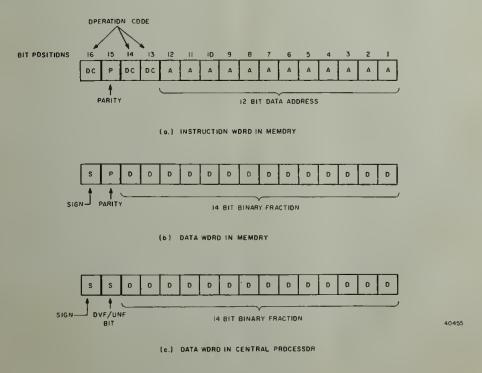

| 4-138 | Central Processor, Functional Diagram            | 4-369/4-370 |

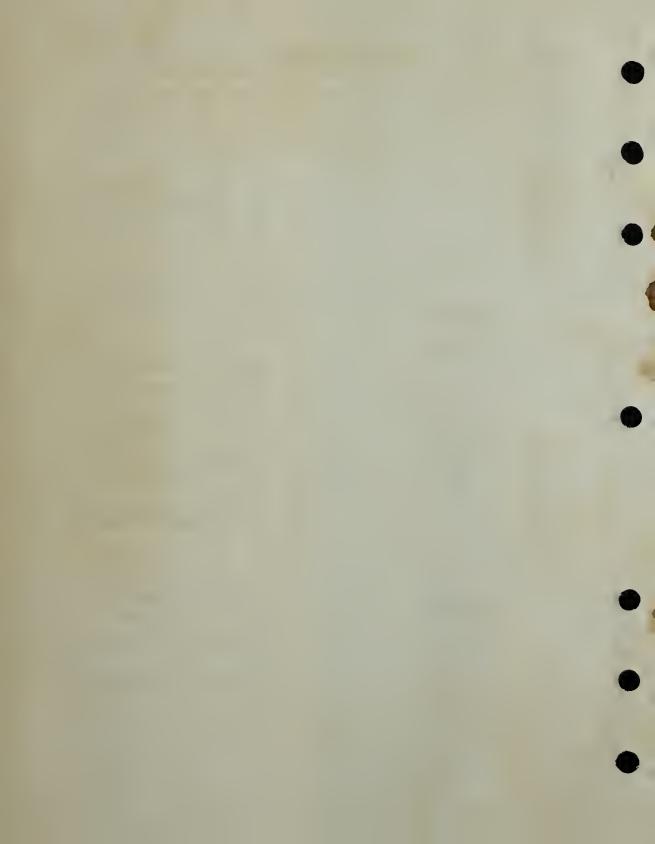

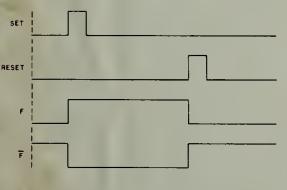

| 4-139 | Flip-Flop Register, Single Bit Positions         | 4-371       |

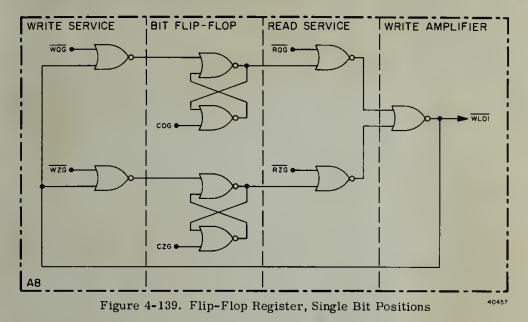

| 4-140 | Write, Clear, and Read Timing                    | 4-372       |

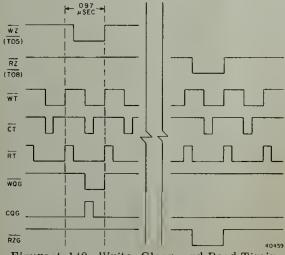

| 4-141 | Addressable Registers Service                    | 4-373/4-374 |

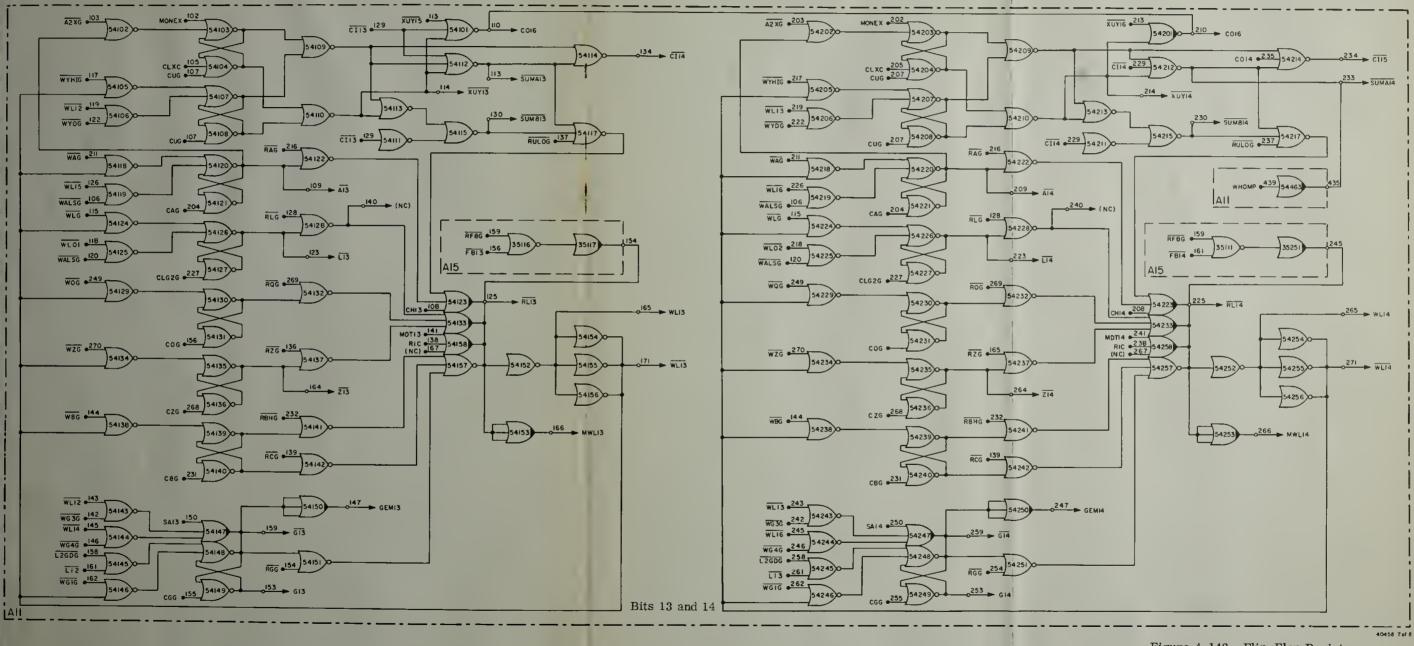

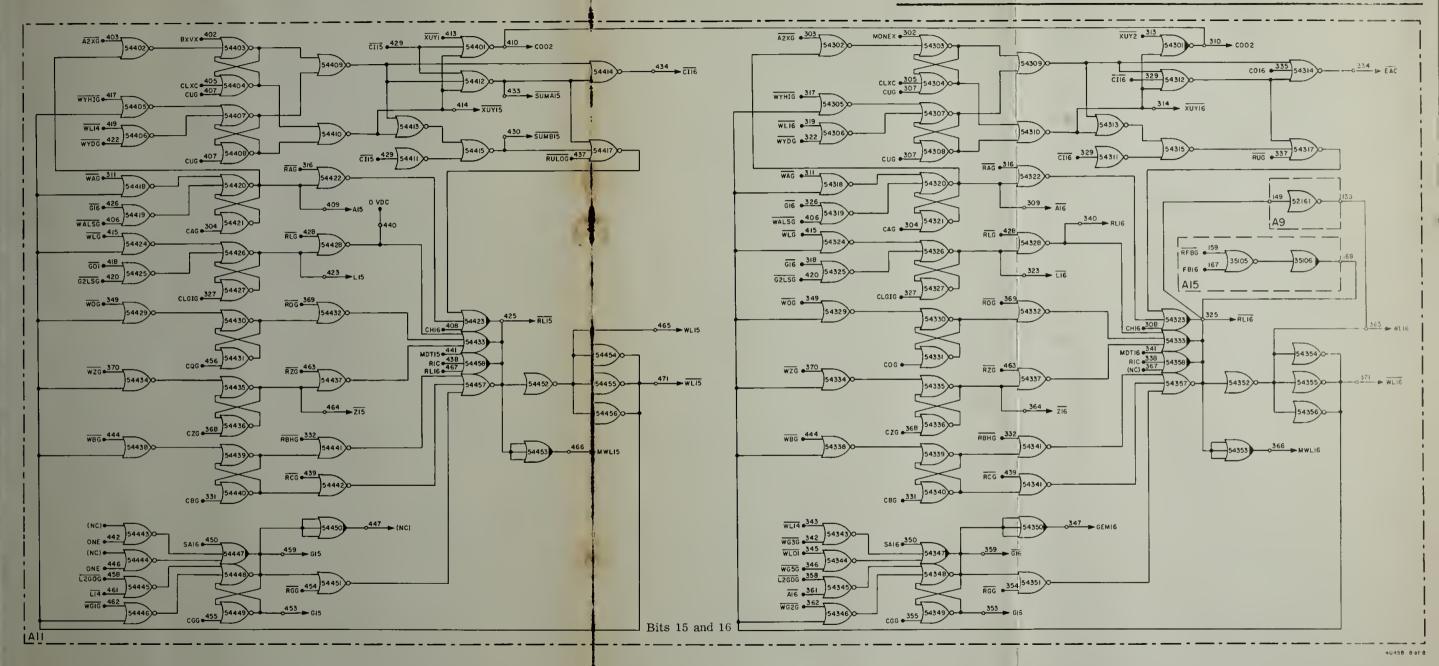

| 4-142 | Flip-Flop Registers                              | 4-375/4-376 |

| 4-143 | Register A Service                               | 4-391/4-392 |

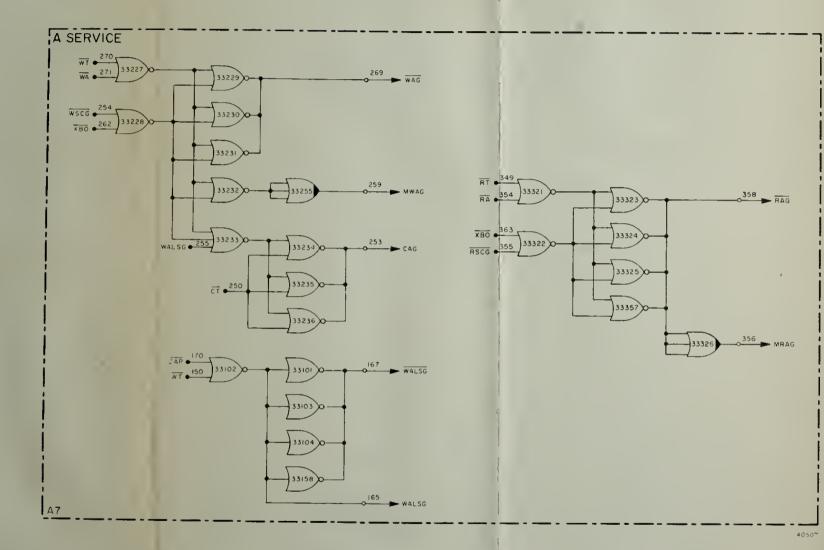

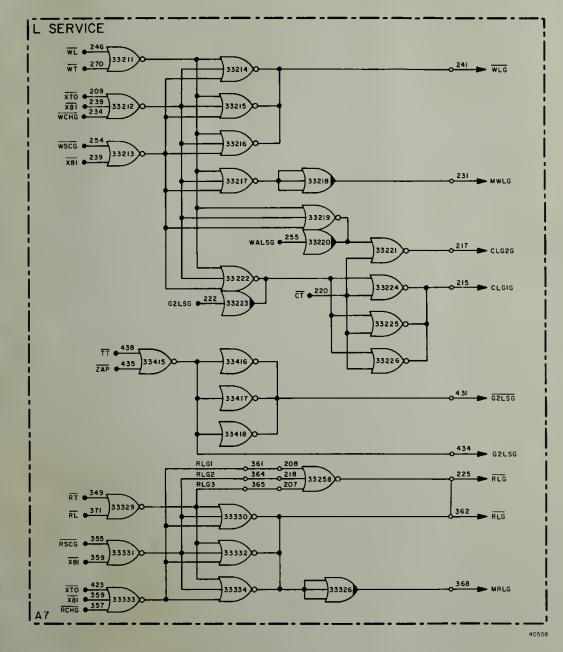

| 4-144 | Register L Service                               | 4-395       |

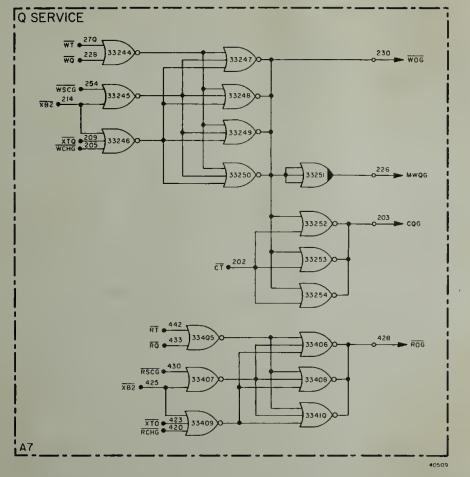

| 4-145 | Register Q Service                               | 4-396       |

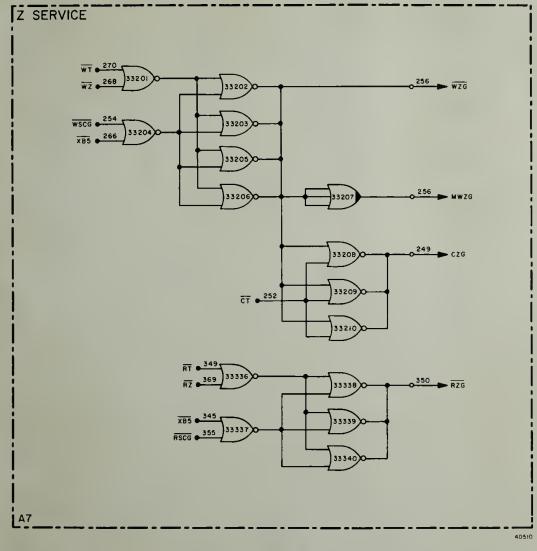

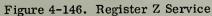

| 4-146 | Register Z Service                               | 4-397       |

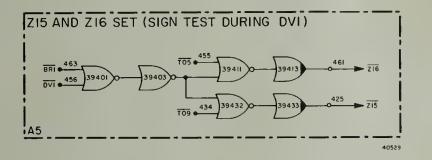

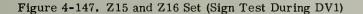

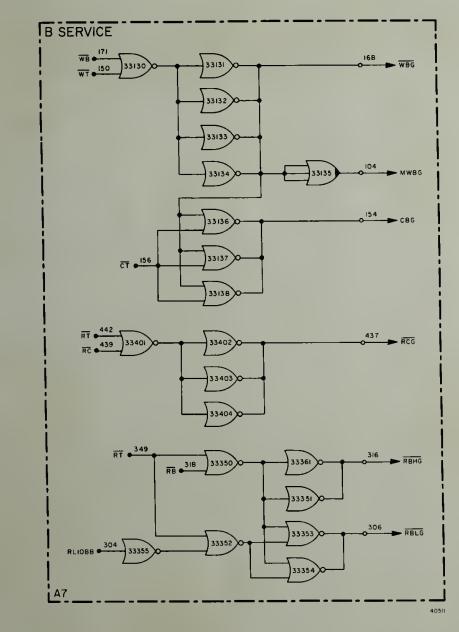

| 4-147 | Z15 and Z16 Set (Sign Test During DV1)           |             |

| 4-148 | Register B Service                               | 4-399       |

| 4-149 | Register G Service                               |             |

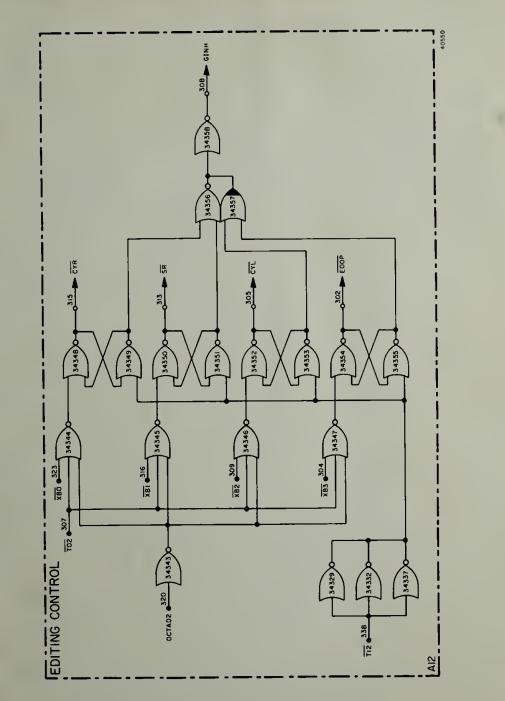

| 4-150 | Editing Control                                  |             |

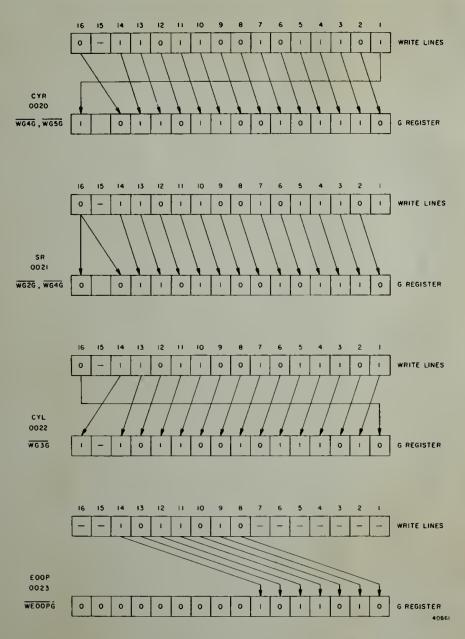

| 4-151 | Editing Transformations                          | 4-404       |

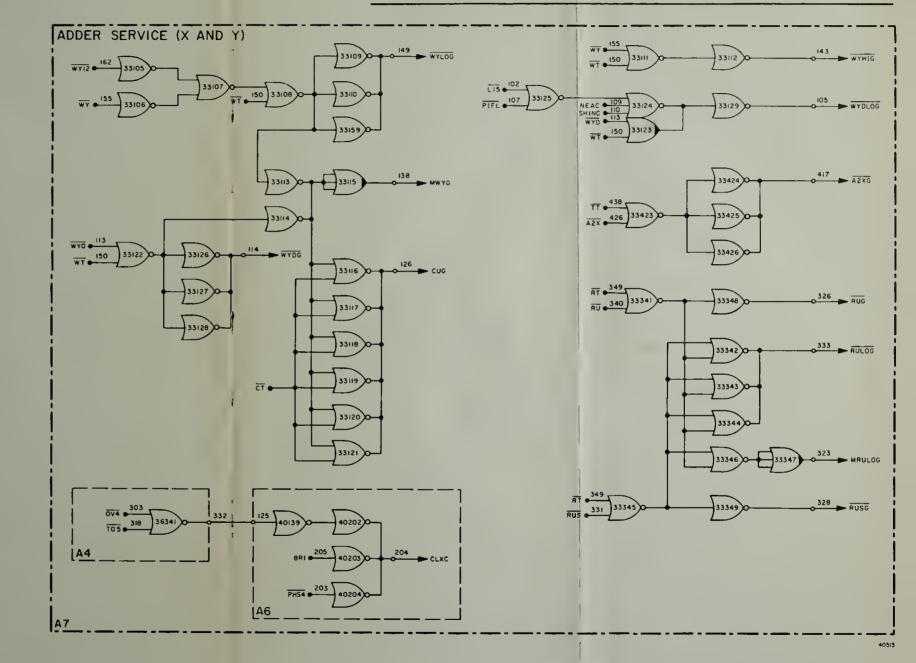

| 4-152 | Adder Service (Registers X and Y)                | 4-409/4-410 |

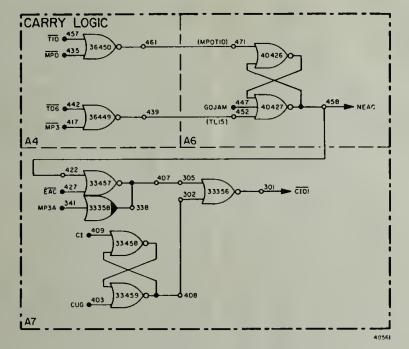

| 4-153 | Carry Logic                                      | 4-412       |

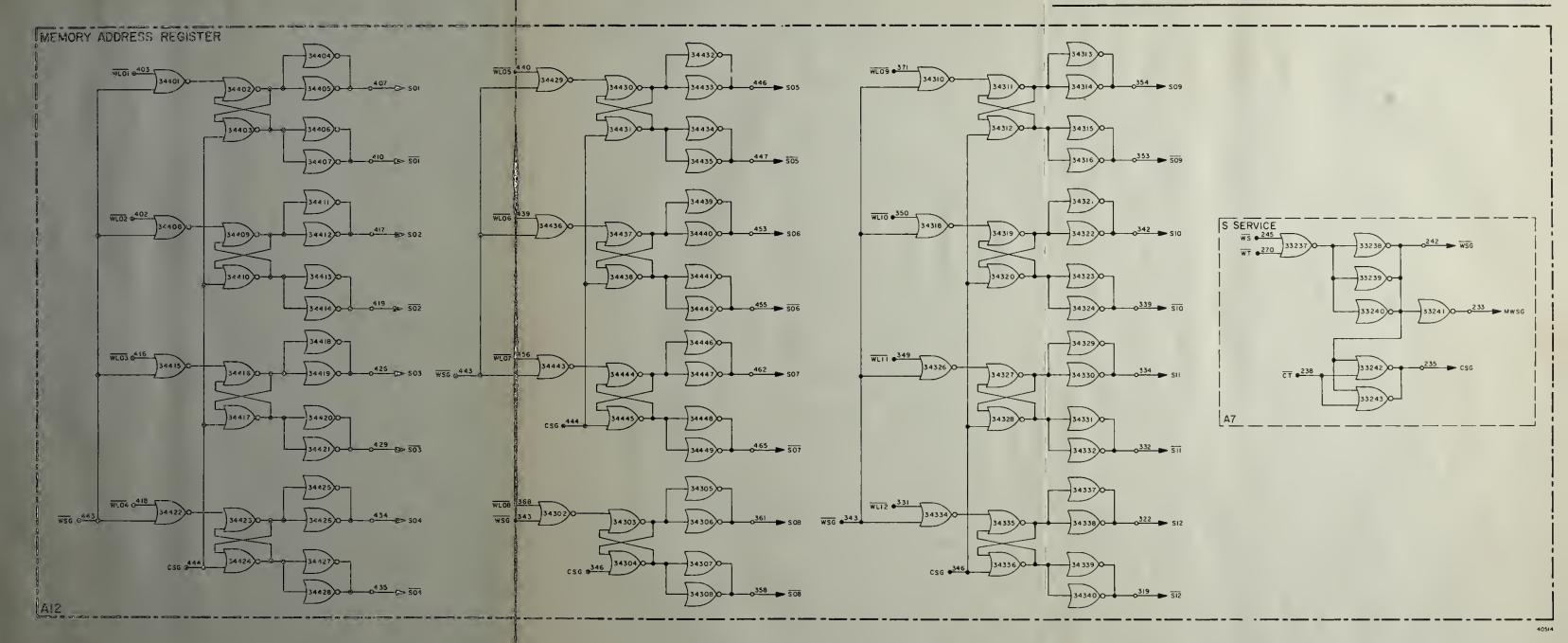

| 4-154 | Memory Address Register (S)                      | 4-417/4-418 |

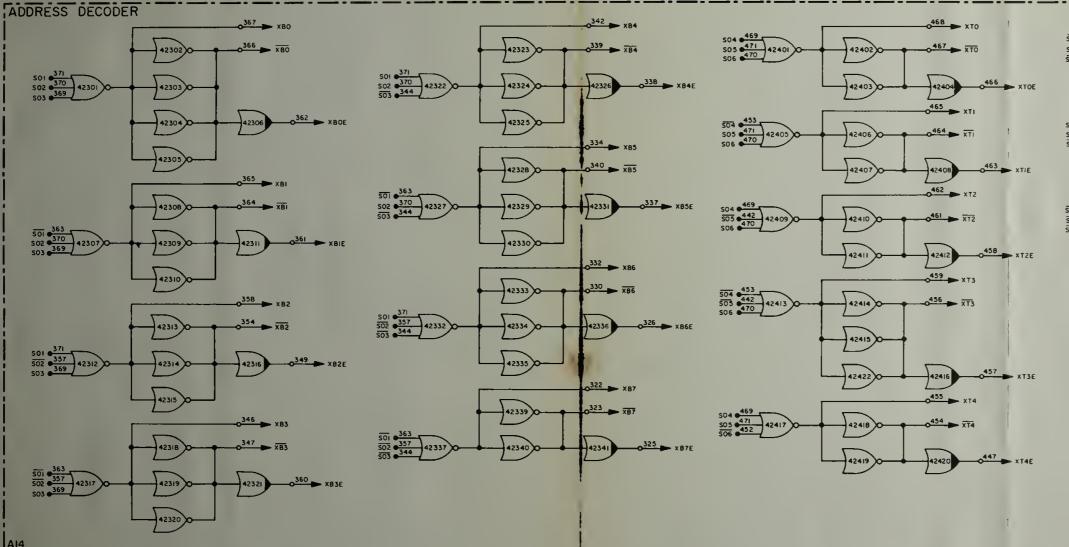

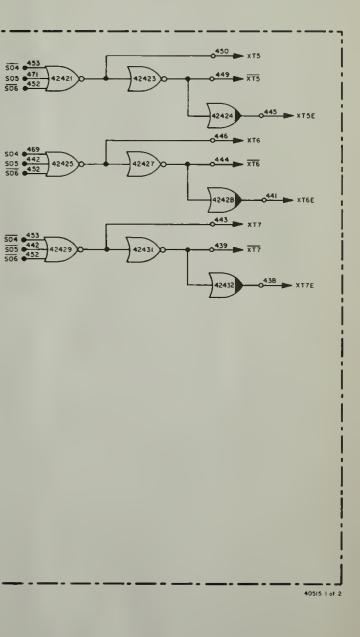

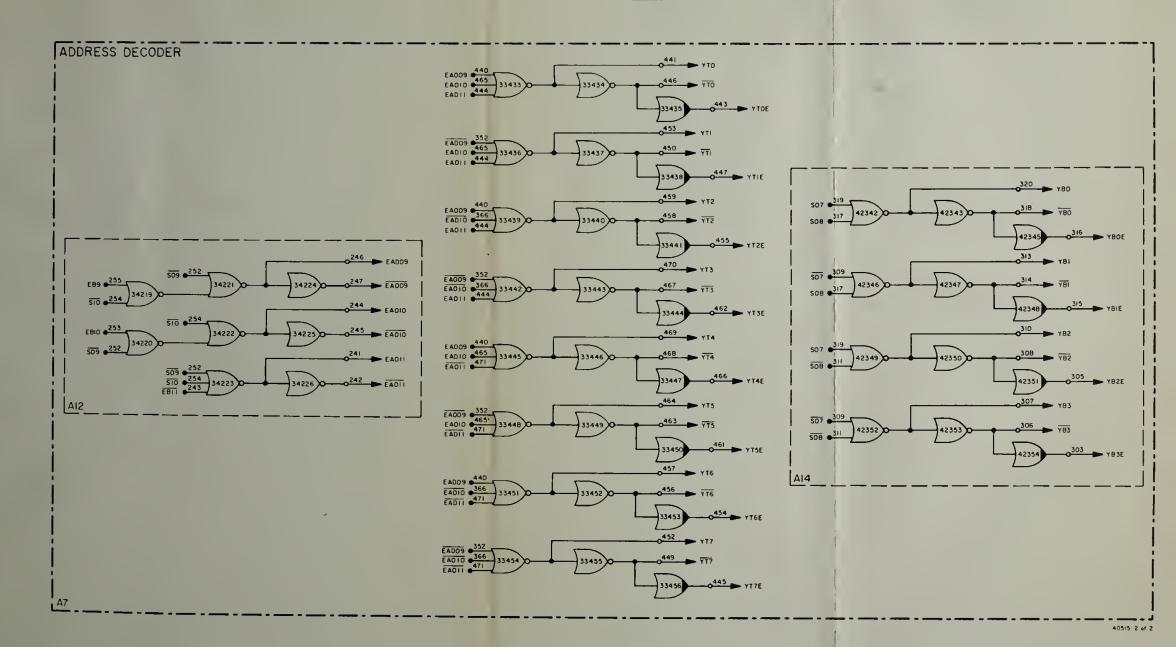

| 4-155 | Address Decoder                                  | 4-421/4-422 |

| 4-156 | Counter Address Signals                          | 4-427       |

| 4-157 | Parity Logic                                     | 4-429/4-430 |

| 4-158 | Priority Control, Functional Block Diagram       |             |

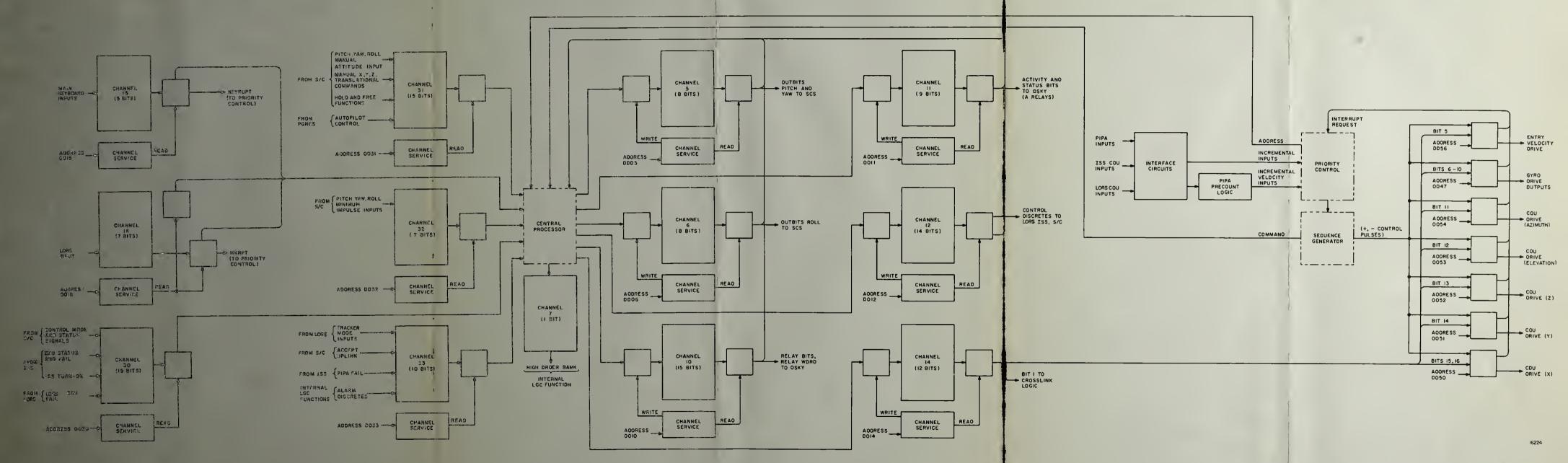

| 4-159 | Input-Output Channels, Functional Diagram        |             |

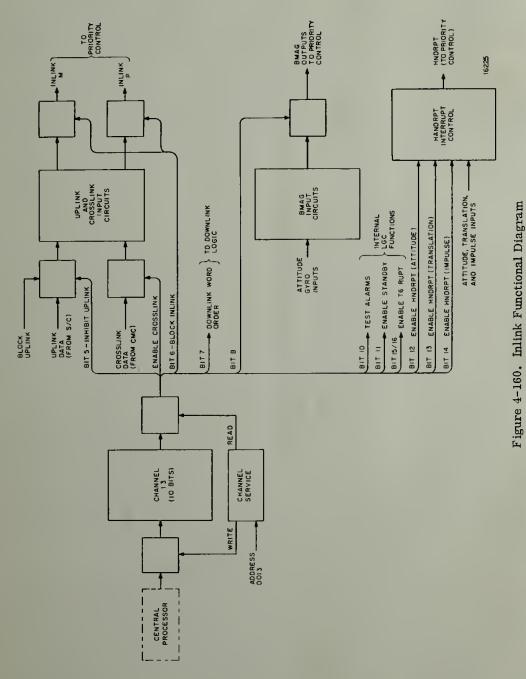

| 4-160 | Inlink Functional Diagram                        | 4-440       |

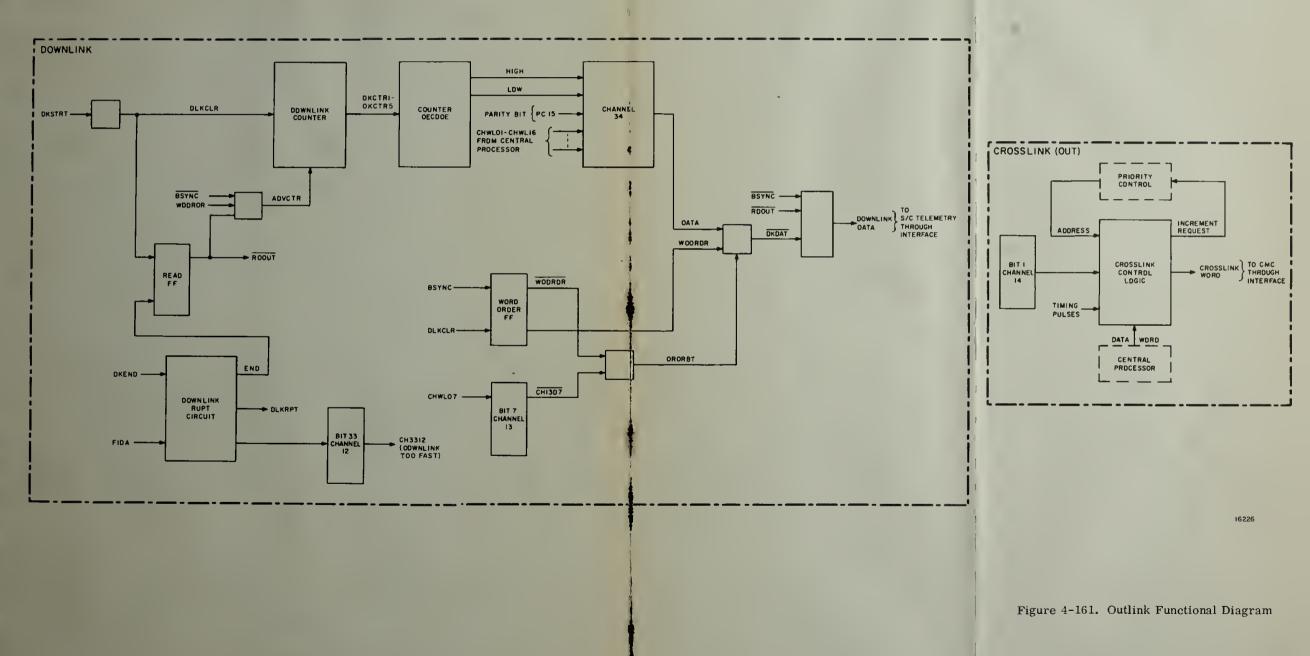

| 4-161 | Outlink, Functional Diagram                      |             |

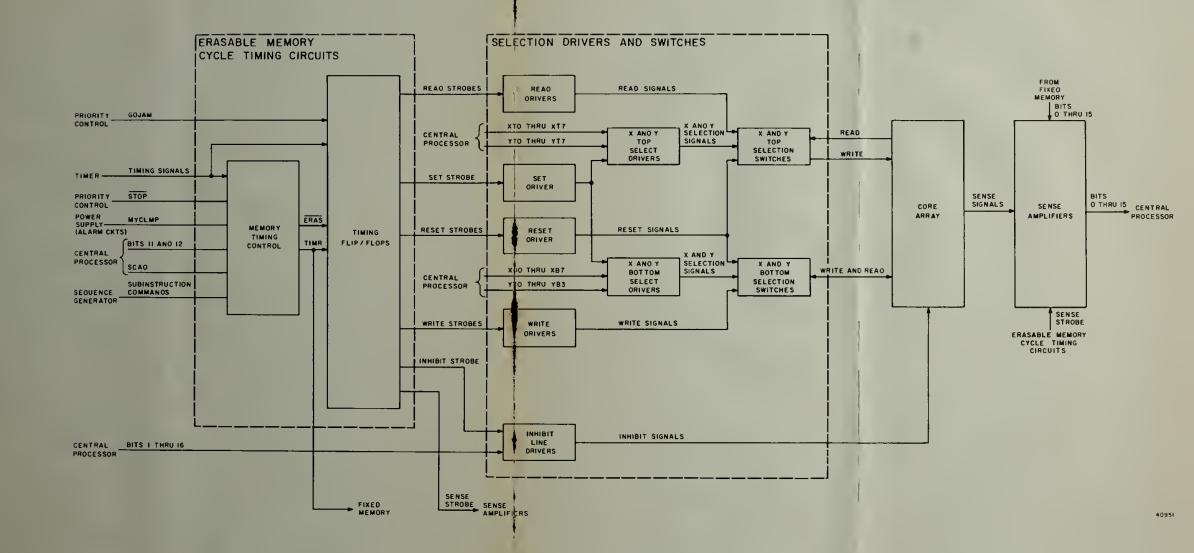

| 4-162 | Erasable Memory, Functional Diagram              | 4-445/4-446 |

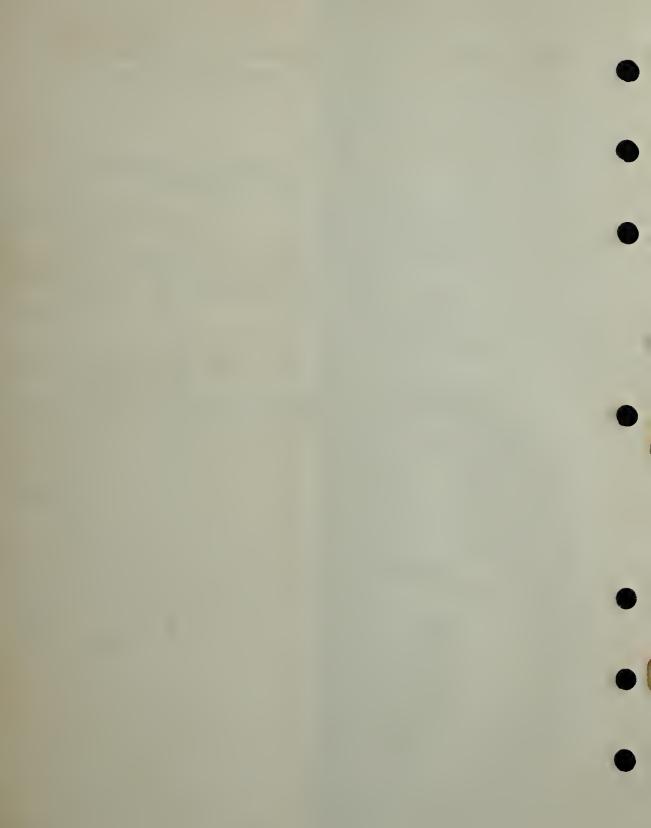

| 4-163 | Erasable Memory Timing Diagram                   | 4-448       |

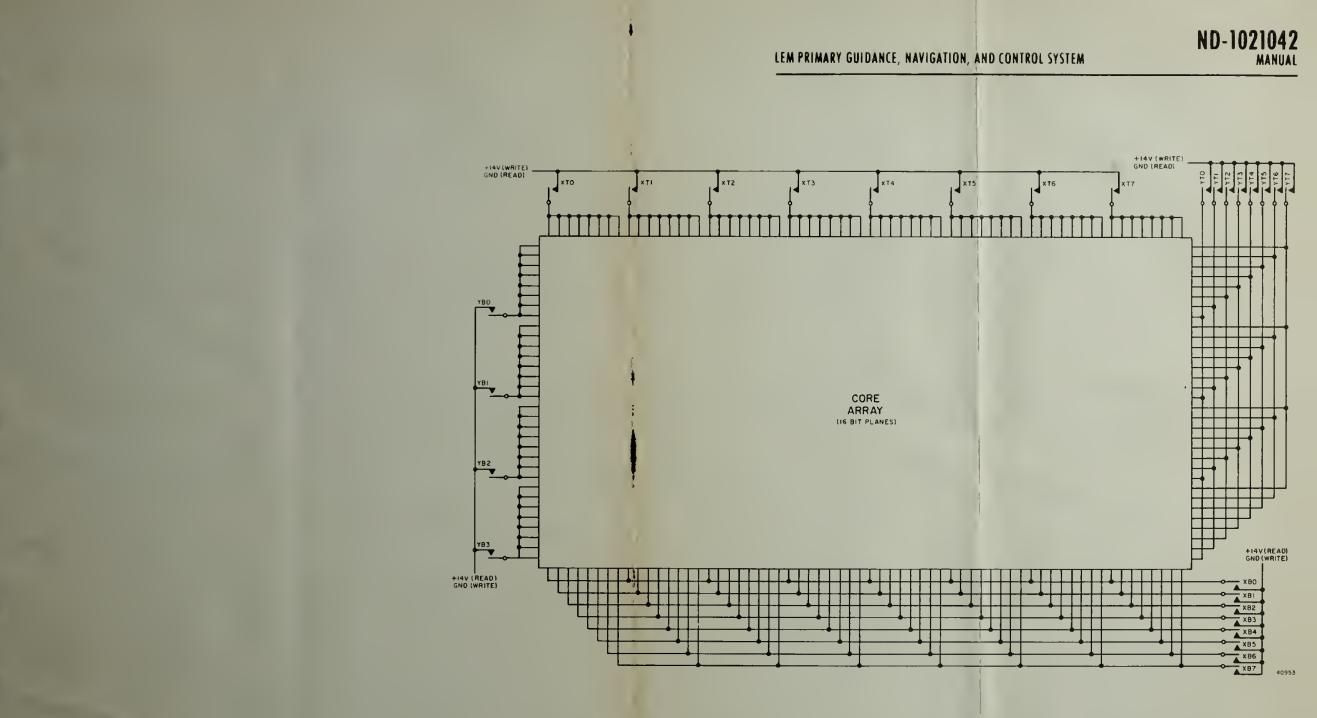

| 4-164 | X and Y Selection, Simplified Diagram            | 4-451/4-452 |

|       |                                                  |             |

#### ILLUSTRATIONS (cont)

| Figure |                                                                                   | Page        |

|--------|-----------------------------------------------------------------------------------|-------------|

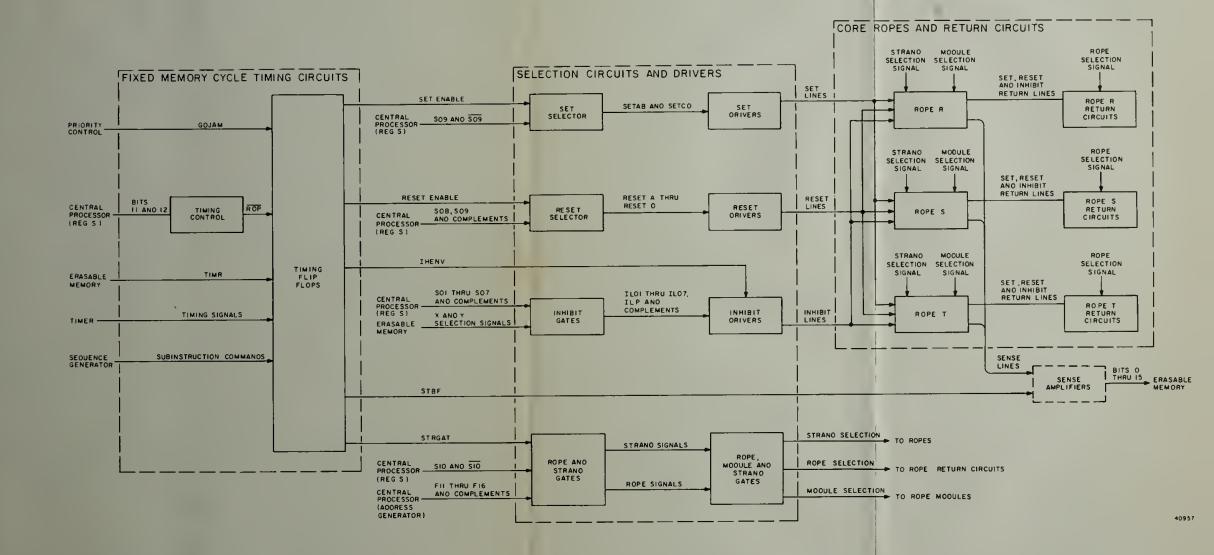

| 4-165  | Fixed Memory, Functional Diagram                                                  | 4-453/4-454 |

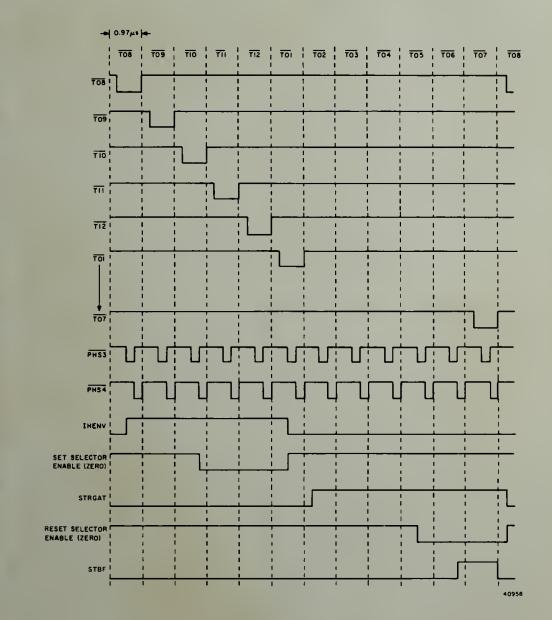

| 4-166  | Fixed Memory, Timing Diagram                                                      | 4-459       |

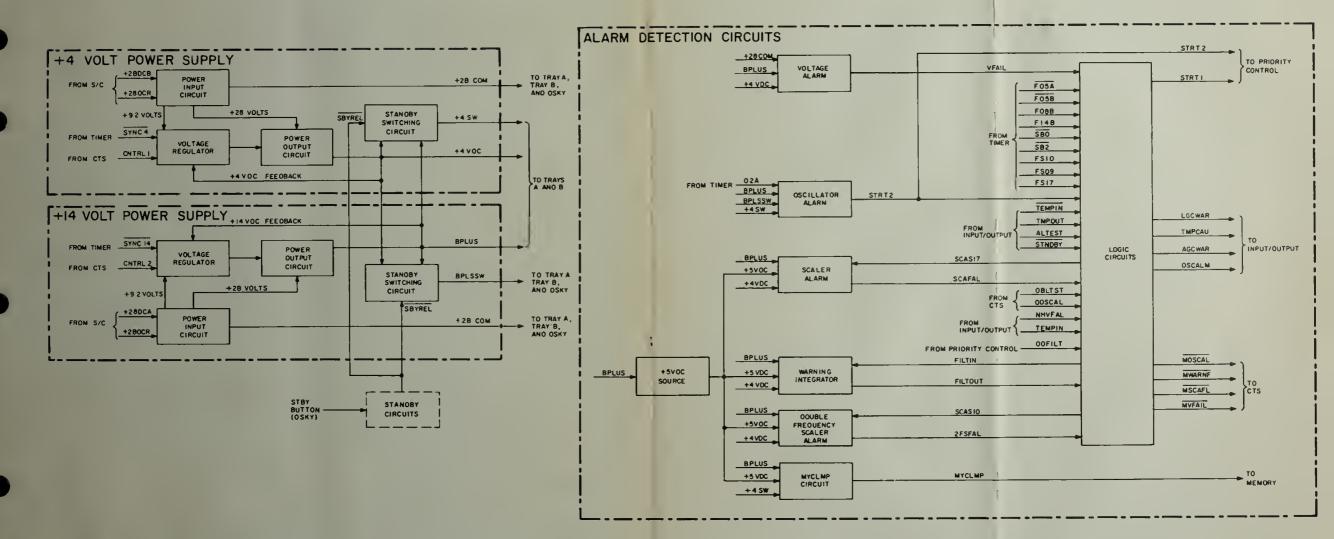

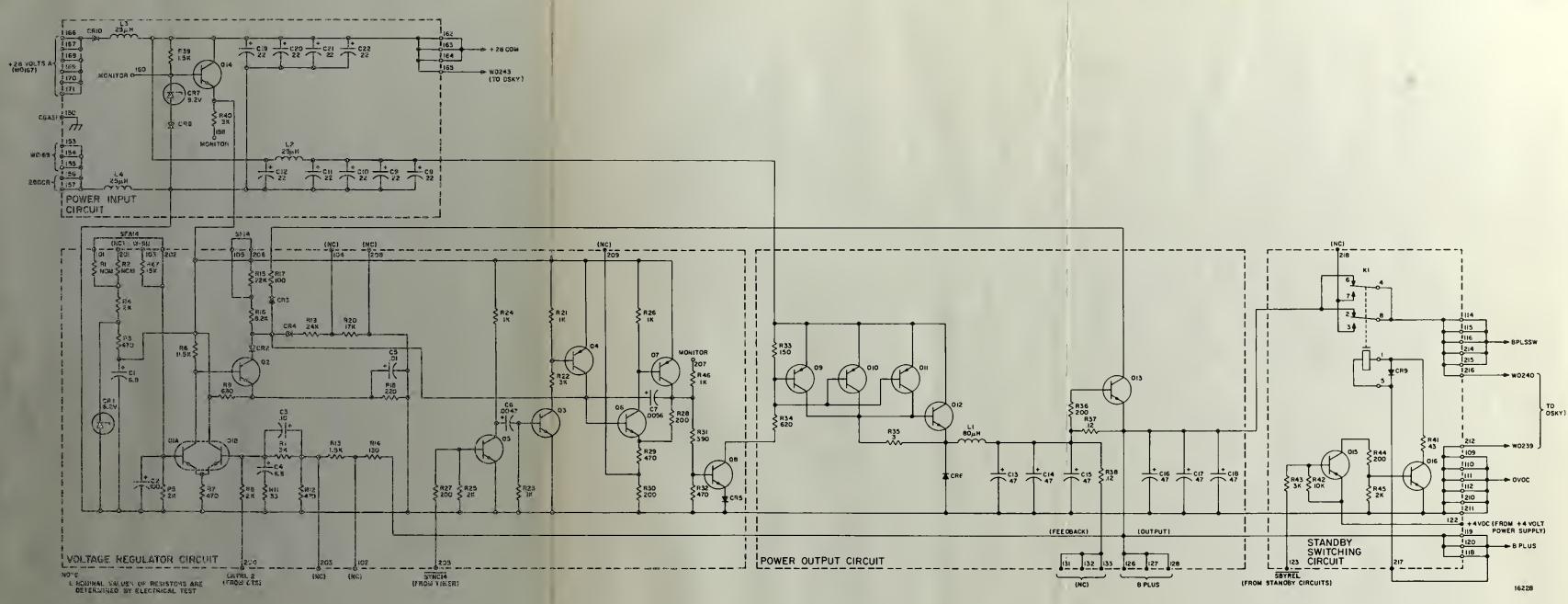

| 4-167  | Power Supply, Functional Diagram                                                  | 4-461/4-462 |

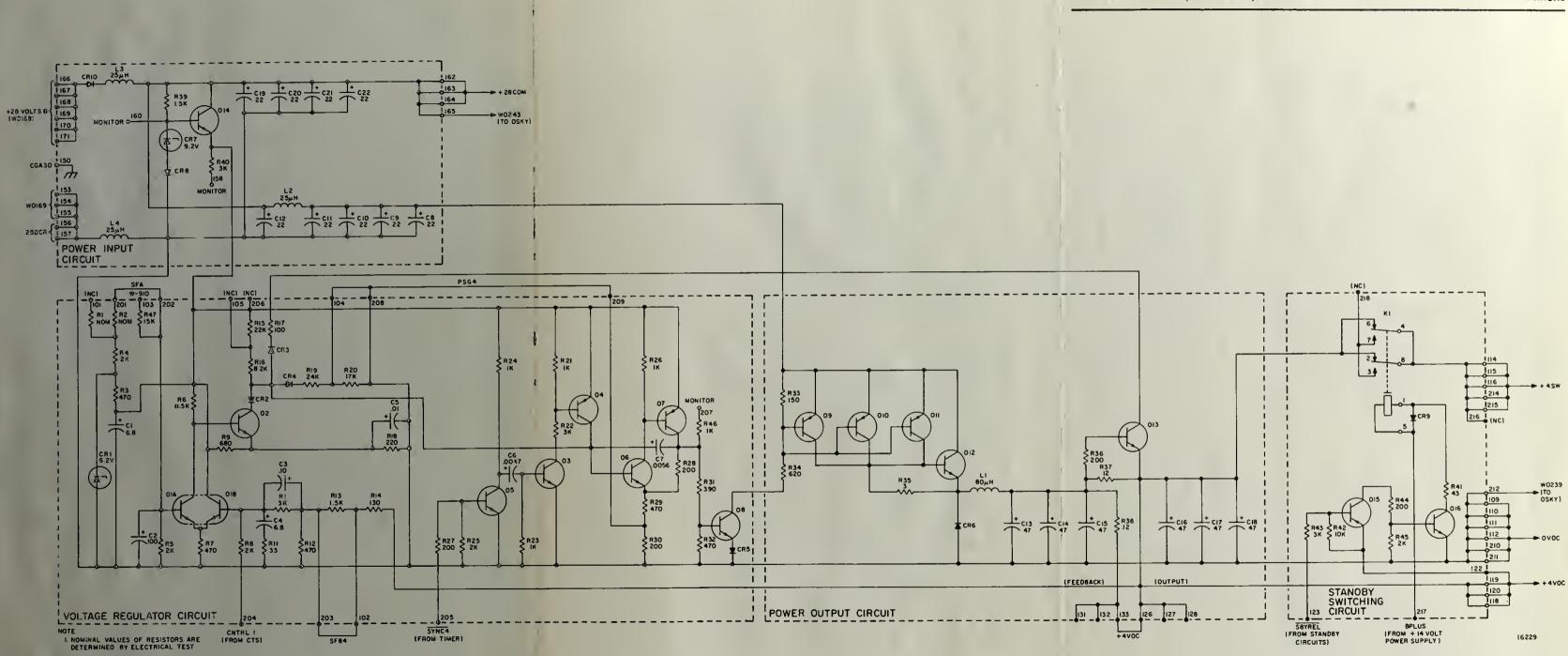

| 4-168  | +4 VDC Power Supply, Schematic Diagram                                            | 4-465/4-466 |

| 4-169  | +14 VDC Power Supply, Schematic                                                   | 4-469/4-470 |

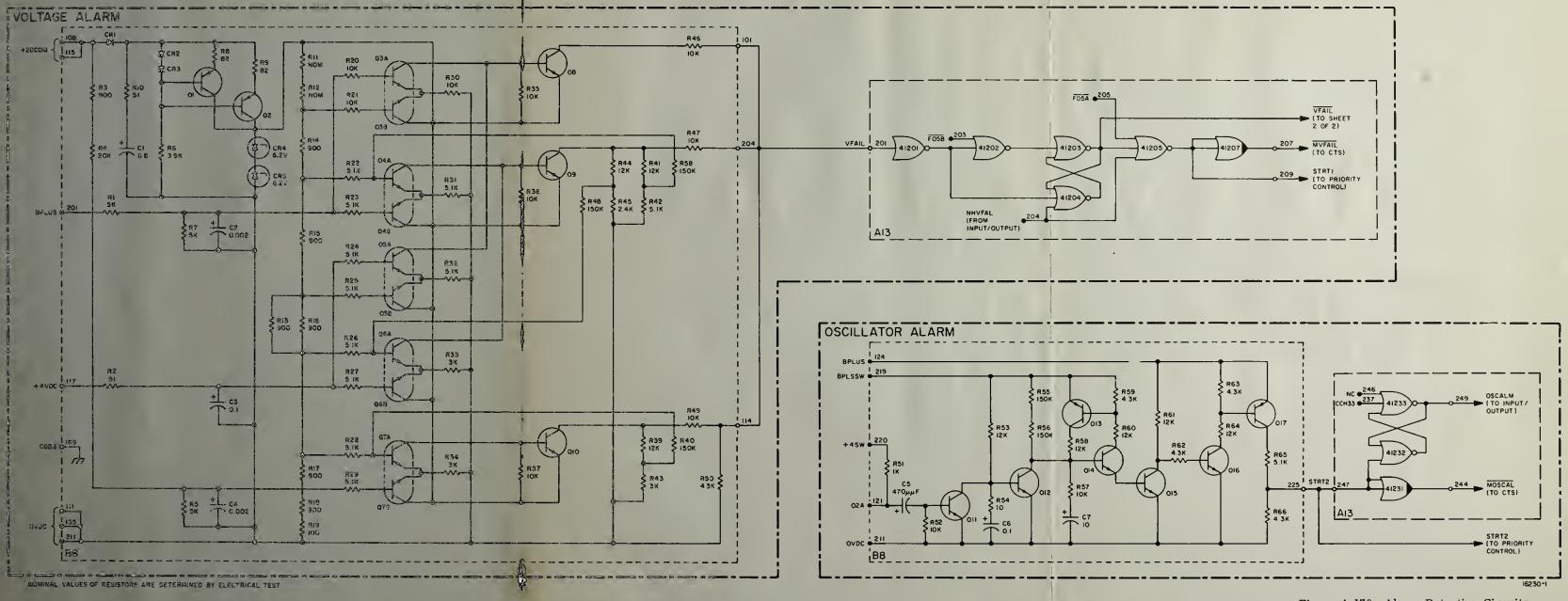

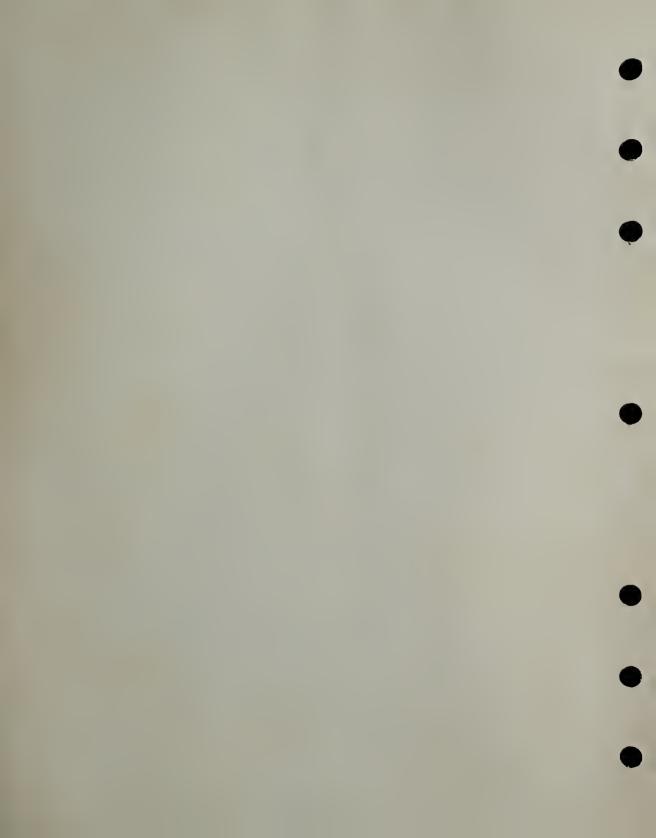

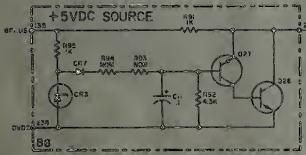

| 4-170  | Alarm Detection Circuits, Schematic Diagram                                       | 4-487/4-498 |

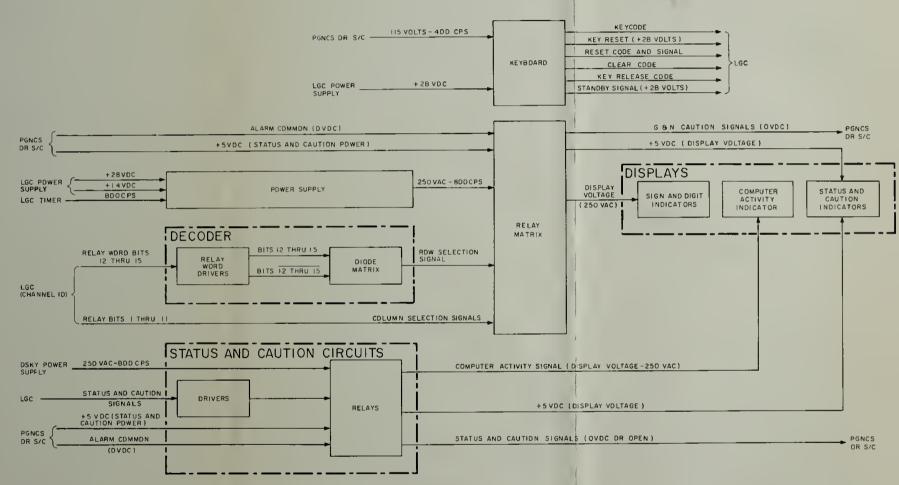

| 4-171  | DSKY, Functional Diagram                                                          | 4-493/4-494 |

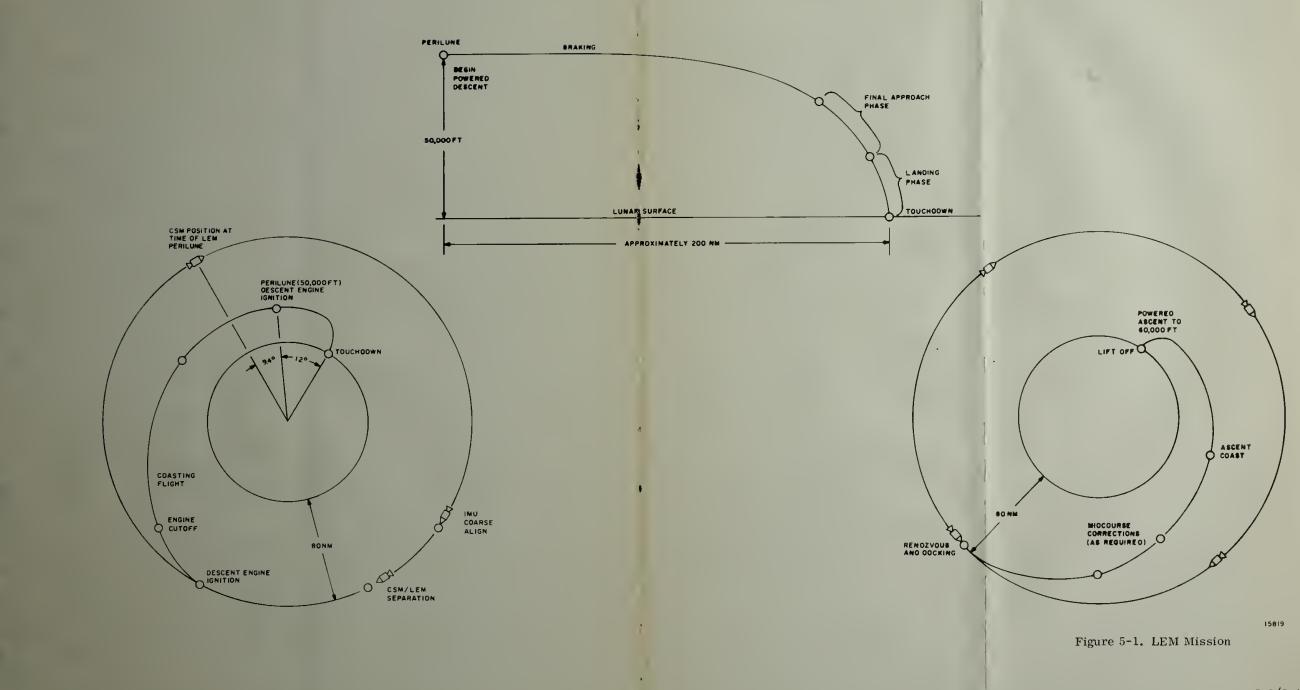

| 5-1    | LEM Mission                                                                       | 5-3/5-4     |

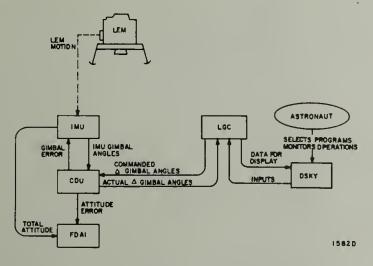

| 5-2    | LEM IMU Coarse Alignment.                                                         | 5-3         |

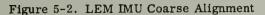

| 5-3    | LEM INU Fine Alignment                                                            | 5-3         |

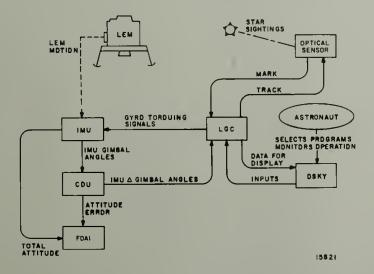

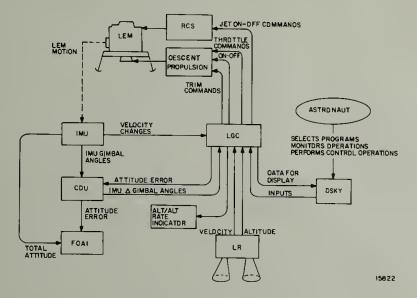

| 5-4    | Powered Descent.                                                                  | 5-6         |

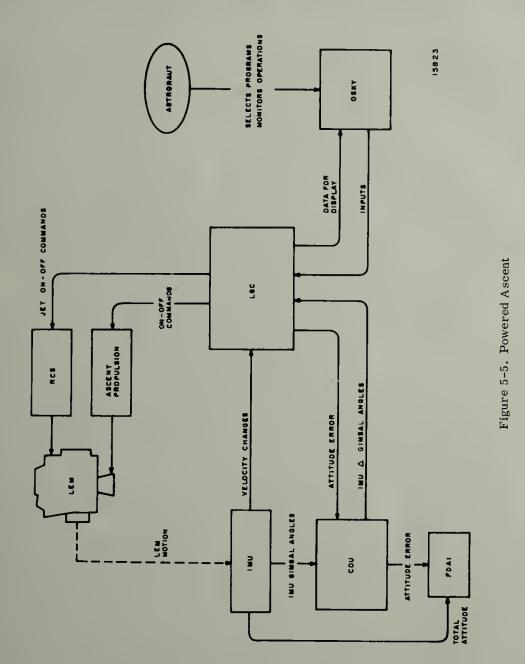

| 5-5    | Powered Ascent                                                                    | 5-8         |

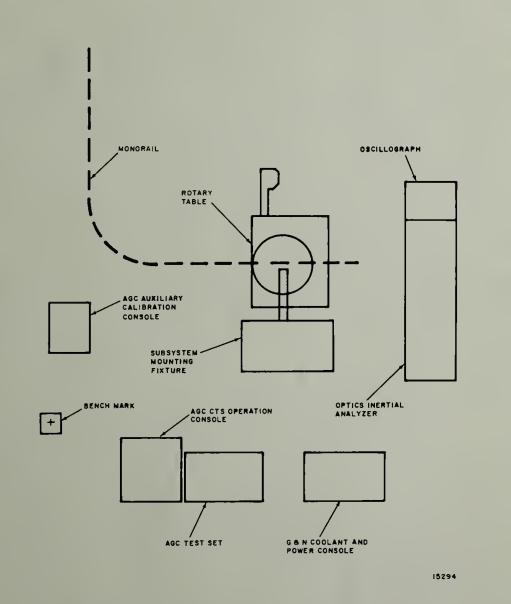

| 6-1    | Typical Universal Test Station Layout                                             | 6-11/6-12   |

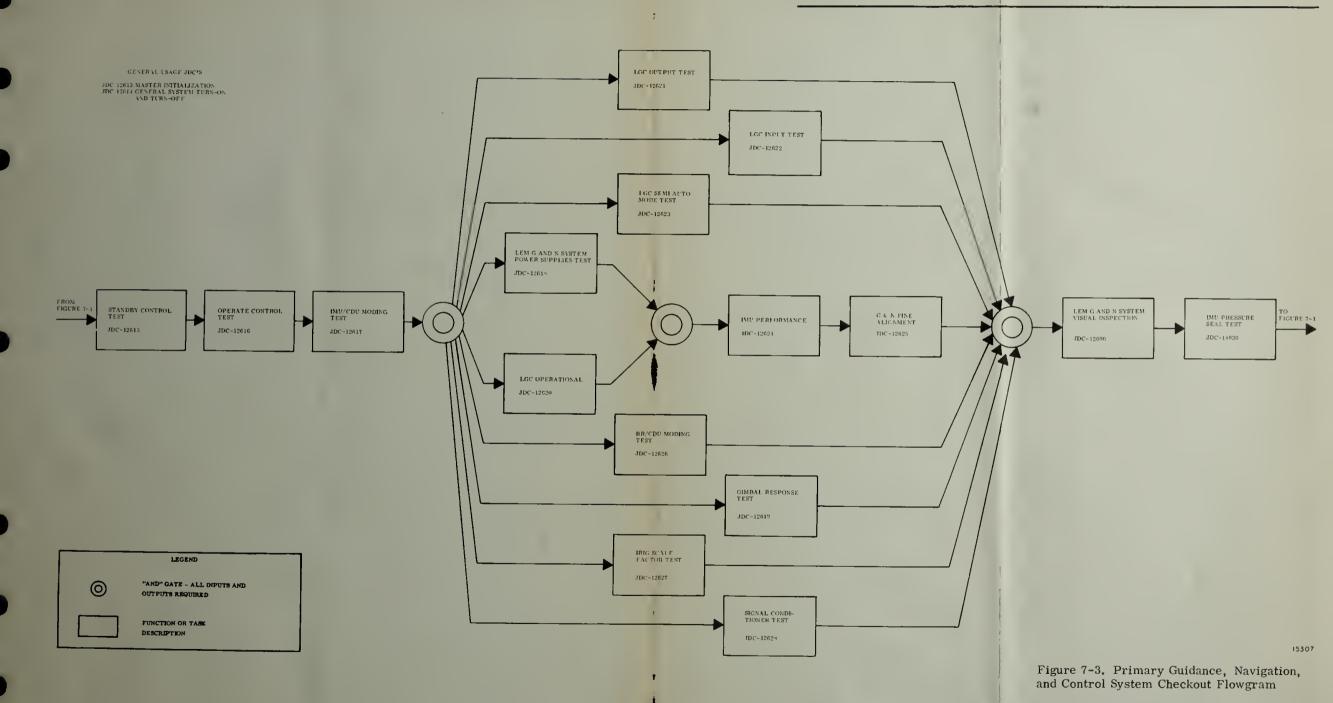

| 7-1    | Primary Guidance, Navigation, and Control System Master                           |             |

| - 0    | Checkout Flowgram                                                                 | 7-17/7-18   |

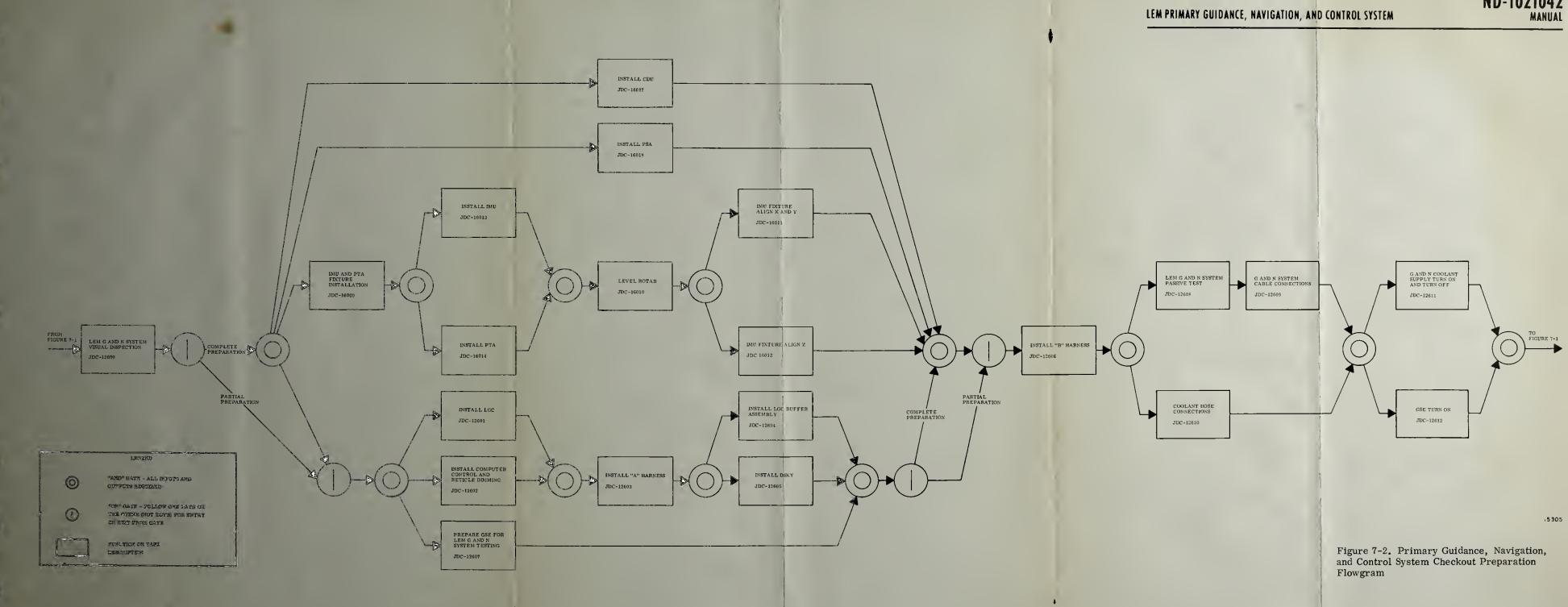

| 7-2    | Primary Guidance, Navigation, and Control System<br>Checkout Preparation Flowgram | 7-19/7-20   |

| 7-3    | Primary Guidance, Navigation, and Control System                                  | 1-19/1-20   |

|        | Checkout Flowgram                                                                 | 7-21/7-22   |

| 7-4    | Inertial Subsystem Master Checkout Flowgram.                                      | 7-23/7-24   |

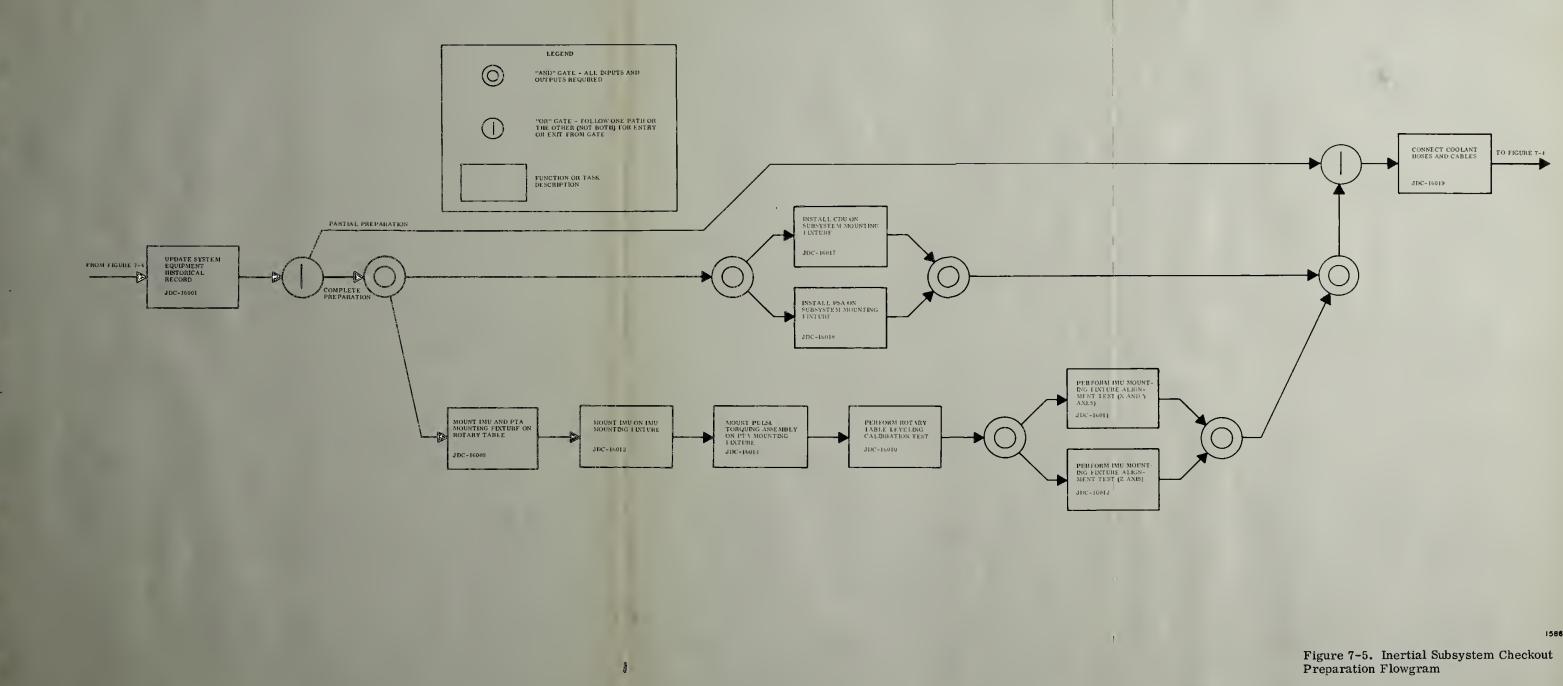

| 7-5    | Inertial Subsystem Checkout Preparation Flowgram                                  | 7-25/7-26   |

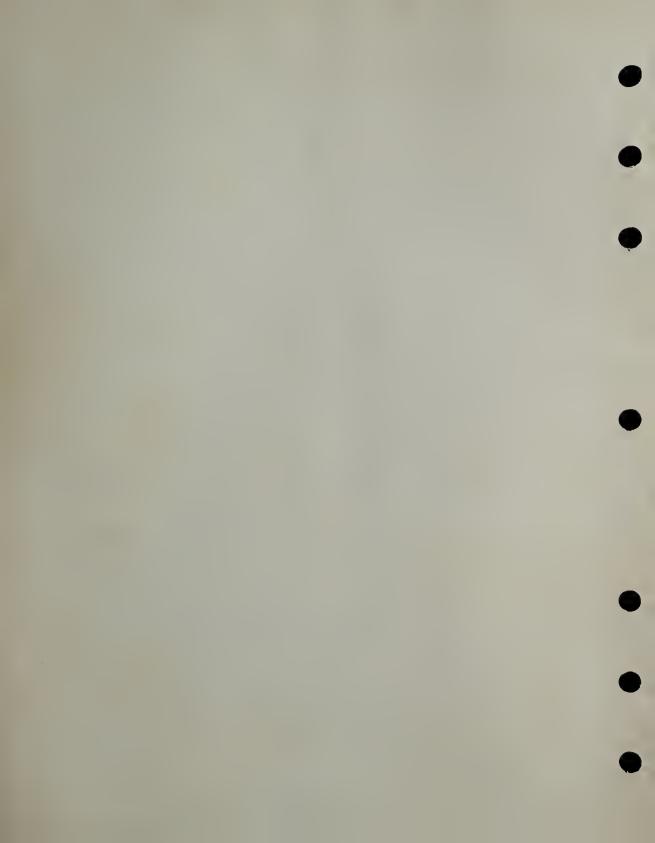

| 7-6    | Inertial Subsystem Checkout Flowgram                                              | 7-27/7-28   |

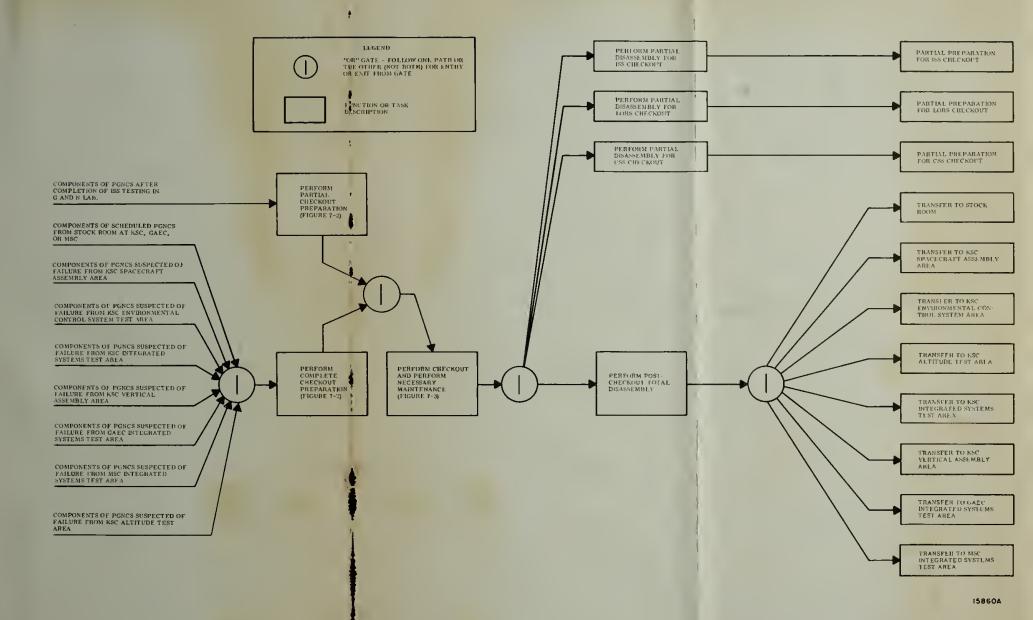

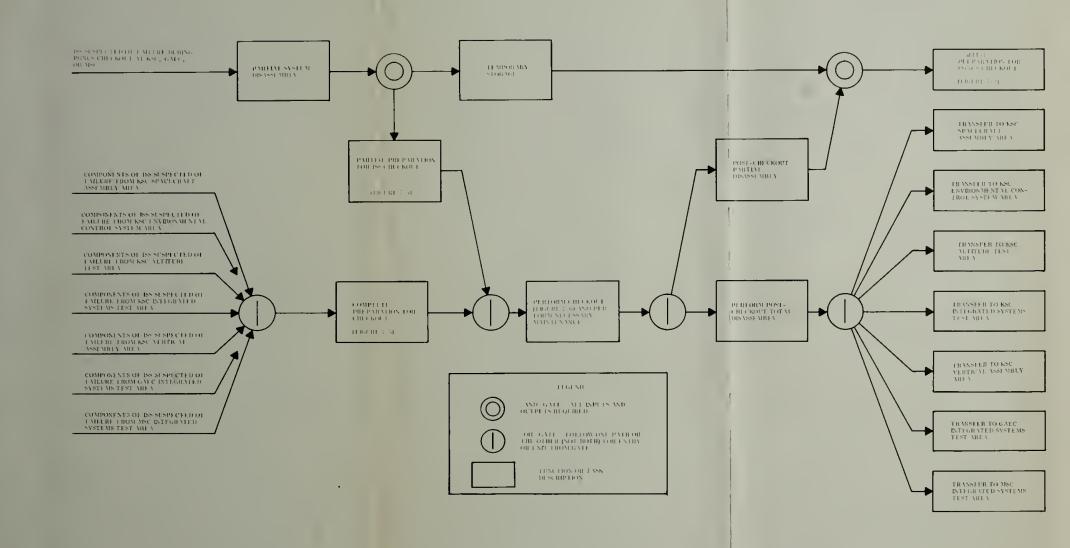

| 8-1    | Maintenance Flowgram                                                              | 8-3         |

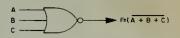

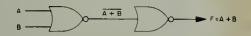

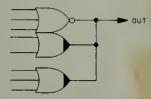

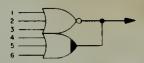

| C-1    | NOR Gate Symbols                                                                  | C-2         |

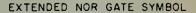

| C-2    | NOR Gate Schematic                                                                | C-4         |

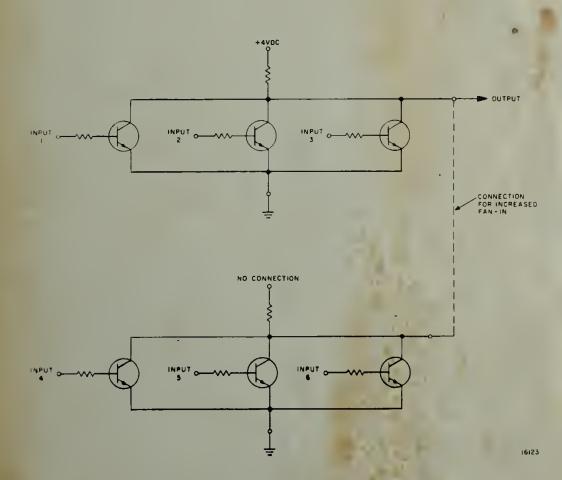

| C-3    | NOR Gate Flip-Flop                                                                | C-5         |

| C-4    | Logic Diagram Symbols                                                             | C-6         |

ND-1021042

MANUAL

#### TABLES

Number

Page

#### Volume $\Pi$

| 4-IX      | Commands Per Subinstruction                    | 4-251 |

|-----------|------------------------------------------------|-------|

| 4-X       | Subinstructions Per Command                    | 4-264 |

| 4-XI      | Counter Cell Signals                           | 4-278 |

| 4-XII     | Subinstruction CCS0                            | 4-280 |

| 4-XIII    | Subinstruction DV0                             | 4-303 |

| 4-XIV     | Subinstruction DV1, Part 1                     | 4-304 |

| 4-XV      | Subinstructions DV3, DV7, and DV6, Part 1      | 4-305 |

| 4-XVI     | Subinstructions DV1, DV3, DV7, and DV6, Part 2 | 4-306 |

| 4-XVII    | Subinstruction DV4                             | 4-307 |

| 4-XVIII   | Subinstruction MP0                             | 4-309 |

| 4-XIX     | Subinstruction MP1                             | 4-310 |

| 4-XX      | Subinstruction MP3                             | 4-311 |

| 4-XXI     | Crosspoint Pulse ZIP                           | 4-312 |

| 4-XXII    | Subinstruction STD2                            | 4-314 |

| 4-XXIII   | Subinstruction TC0                             | 4-314 |

| 4-XXIV    | Subinstruction TCF0                            | 4-315 |

| 4-XXV     | Subinstruction TCSAJ3                          | 4-315 |

| 4-XXVI    | Subinstruction GOJ1                            | 4-315 |

| 4-XXVII   | Subinstruction DAS0                            | 4-316 |

| 4-XXVIII  | Subinstruction DAS1                            | 4-317 |

| 4-XXIX    | Subinstruction LXCH0                           | 4-318 |

| 4-XXX     | Subinstruction INCR0                           | 4-318 |

| 4-XXXI    | Subinstruction ADS0                            | 4-319 |

| 4-XXXII   | Subinstructions CA0 and DCA1                   | 4-320 |

| 4-XXXIII  | Subinstructions CS0 and DCS1                   | 4-320 |

| 4-XXXIV   | Subinstruction NDX0                            | 4-321 |

| 4-XXXV    | Subinstruction RSM3                            | 4-321 |

| 4-XXXVI   | Subinstruction NDX1                            | 4-322 |

| 4-XXXVII  | Subinstruction XCH0                            | 4-323 |

| 4-XXXVIII | Subinstruction DXCH0                           | 4-324 |

| 4-XXXIX   | Subinstruction DXCH1                           | 4-324 |

| 4-XL      | Subinstruction TS0                             | 4-325 |

| 4-XLI     | Subinstruction AD0                             | 4-326 |

| 4-XLH     | Subinstruction MASK0                           | 4-327 |

| 4-XLIII   | Subinstruction BZF0                            | 4-328 |

| 4-XLIV    | Subinstruction MSU0                            | 4-329 |

| 4-XLV     | Subinstruction QXCH0                           | 4-330 |

| 4-XLVI    | Subinstruction AUG0                            | 4-330 |

| 4-XLVII   | Subinstruction DIM0                            | 4-331 |

| 4-XLVIII  | Subinstruction DCA0                            | 4-332 |

| 4-XLIX    | Subinstruction DCS0                            | 4-333 |

| 4-I.      | Subinstruction SU0                             | 4-334 |

|           |                                                |       |

#### TABLES (cont)

| Number        |                                            | Page       |

|---------------|--------------------------------------------|------------|

| 4-LX          | Subinstruction RXOR0                       | 4-342      |

| 4-LXI         | Subinstruction RUPT0                       | 4-343      |

| 4-LXII        | Subinstruction RUPT1                       | 4-343      |

| 4-LXIII       | Subinstruction PINC                        | 4-344      |

| 4-LXIV        | Subinstruction MINC                        | 4-344      |

| 4-LXV         | Subinstruction PCDU                        | 4-345      |

| 4-LXVI        | Subinstruction MCDU                        | 4-345      |

| 4-LXVII       | Subinstruction DINC                        | 4-346      |

| 4-LXVIII      | Subinstruction SHINC                       | 4-347      |

| 4-LXIX        | Subinstruction SHANC                       | 4-347      |

| 4-LXX         | Subinstruction INOTRD                      | 4-348      |

| 4-LXXI        | Subinstruction INOT LD                     | 4-348      |

| 4-LXXII       | Subinstructions FETCH0 and STORE0          | 4-349      |

| 4-LXXIII      | Subinstruction FETCH1                      | 4-349      |

| 4-LXXIV       | Subinstruction STORE1                      | 4-350      |

| 4-LXXV        | Control Pulse Orgin                        | 4-357      |

| 4-LXXVI       | Register A and L Write Line Inputs         | 4-393      |

| 4-LXXVII      | Write Amplifiers External Inputs           | -413/4-414 |

| 4-LXXVIII     | Erasable Memory Address Selection          |            |

| 4-LXXIX       | E Addressing                               | 4-447      |

| 4-LXXX        | F Addressing                               | 4-455      |

| 4-LXXXI       | Power Distribution                         | 4-472      |

| 6-I           | Checkout and Maintenance Test Equipment    | 6-1        |

| 6 <b>-</b> II | Checkout and Maintenance Tools             | 6-5        |

| 6-III         | List of Operating Procedure JDC's for GSE  | 6-6        |

| 7-I           | Equipment Required for Checkout            | 7-2        |

| 7-П           | PGNCS Interconnect Cables                  | 7-4        |

| 7-III         | Inertial Subsystem Interconnect Cables     | 7-9        |

| 7-IV          | Computer Subsystem Interconnect Cables     | 7-14       |

| 8-I           | PGNCS and ISS Loop Diagrams and Schematics | 8-4        |

| 4-LI          | Subinstruction NDXX0                       | 4-334      |

| 4-LII         | Subinstruction NDXX1                       | 4-335      |

| 4-LIII        | Subinstruction BZMF0                       |            |

| 4-LIV         | Subinstruction READ0                       | 4-337      |

| 4-LV          | Subinstruction WRITE0                      | 4-338      |

| 4-LVI         | Subinstruction RAND0                       | 4-339      |

| 4-LVII        | Subinstruction WAND0                       |            |

| 4-LVIII       | Subinstruction ROR0                        |            |

| 4-LIX         | Subinstruction WOR0                        |            |

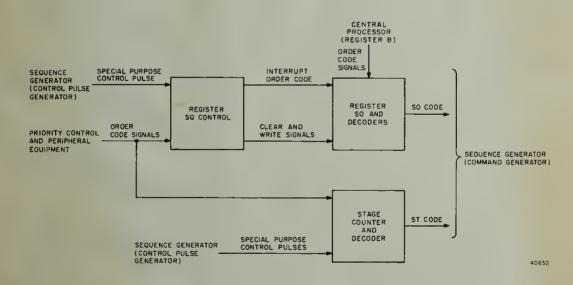

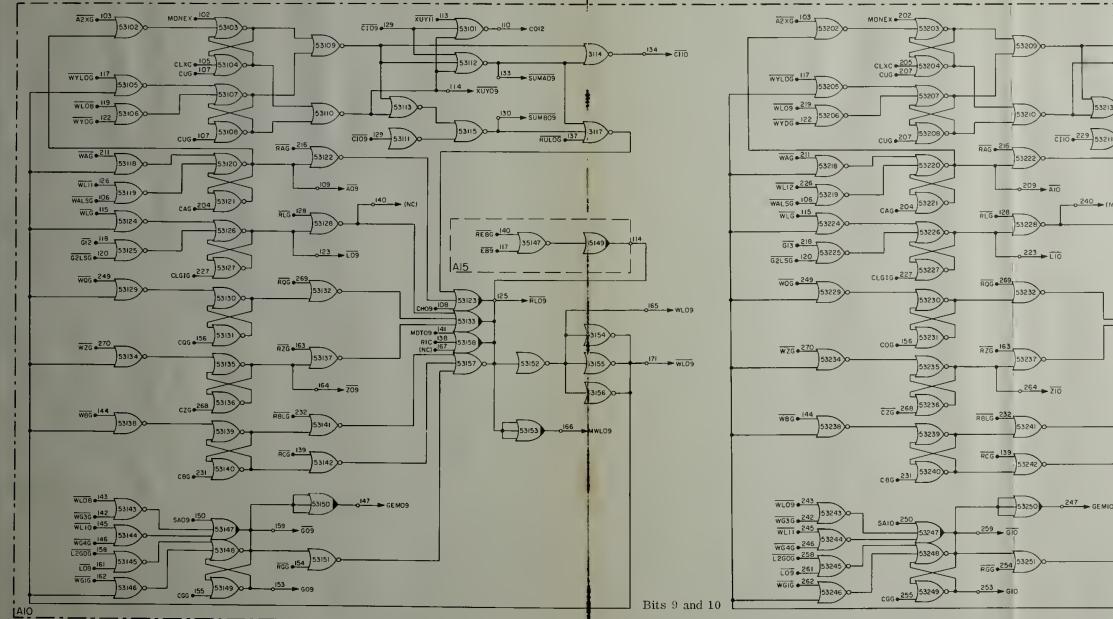

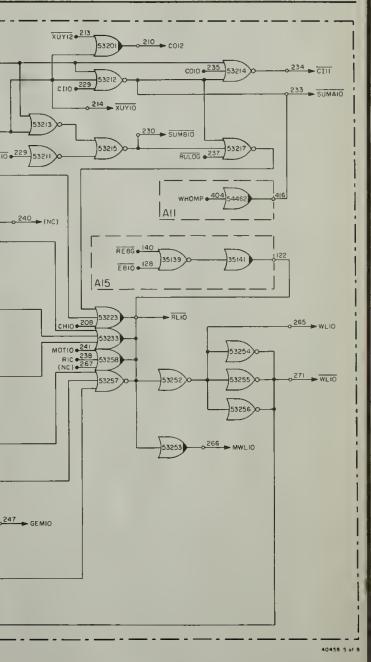

4-5.4.1 Order Code Processor. The order code processor (figure 4-125) consists of the register SQ control, register SQ and decoders, and stage counter and decoders. The register SQ control is regulated by special purpose control pulse NISQ from the control pulse generator. Control pulse NISQ produces clear and write signals for register SQ and initiates a read signal for register B. The clear, read, and write signals place the order code content of register B onto the write lines and into register SQ. The order code signals from the priority control and the peripheral equipment pertain to start, interrupt, and transfer control to specified address instructions. These order code signal is start or transfer control to specified address, no further action occurs because the order code for each of these instructions is binary 0 000 000. If the order code signal is interrupt, register SQ is set to 1 000 111. Other special purpose control pulses provide regulatory functions within the register SQ control during interrupt and some address-dependent instructions.

Figure 4-125. Order Code Processor, Block Diagram

Register SQ is a seven-bit register with only six of its bit positions (16 and 14 through 10) connected to the central processor write lines. The seventh (high-order) bit position is the extend bit. This high-order bit position is used for extending the order code field; it contains a logic ZERO for basic instructions and a logic ONE for extracode, channel, and interrupt instructions. Bit positions 16, 14, and 13 produce the SQ signals. At any time, only one of the eight possible SQ signals is present to indicate the octal number specified by these bit positions. Bit positions 12 and 11 contain the quarter code. These bits are decoded into one of four QC signals to indicate the octal number specified by these two bit positions. Bit position 10 is not used for basic and extracode instructions; however, it is used for the channel and interrupt instructions.

The stage counter is a three-stage Gray counter especially adapted for various counts other than the Gray code. Most instructions are several MCT's long and use the two low-order bits of the stage counter. The stage counter controls the length of each instruction. The stage counter always starts an instruction with count 000. Then it may be advanced to 001, 010, or 011 by special purpose control pulses ST1 and ST2 from the control pulse generator. The Gray code count is used for the divide instruction. Control pulse DVST advances the counter through the states 000, 001, 011, 111, 110, and 100. Then control pulse ST2 sets the stage counter to 010 to complete the divide instruction. The content of the stage counter is decoded into the ST code signals. Some of the ST code signals reflect the standard binary count from octal 0 through 3, and others reflect the Gray code count of octal 0, 1, 3, 7, 6, and 4. The order code signals from the priority control and the peripheral equipment set the stage counter to a particular state in a manner similar to that in which register SQ is set. The interrupt order code signal sets the stage counter to 000, the start order code signal sets it to 001, and the transfer control to specified address signal sets it to 011. The outputs of register SQ and stage decoders arc sent to the command generator where they are used to produce subinstruction and instruction commands.

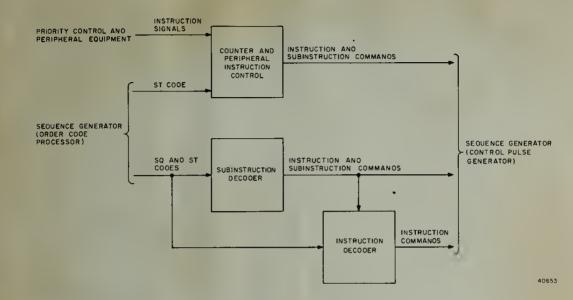

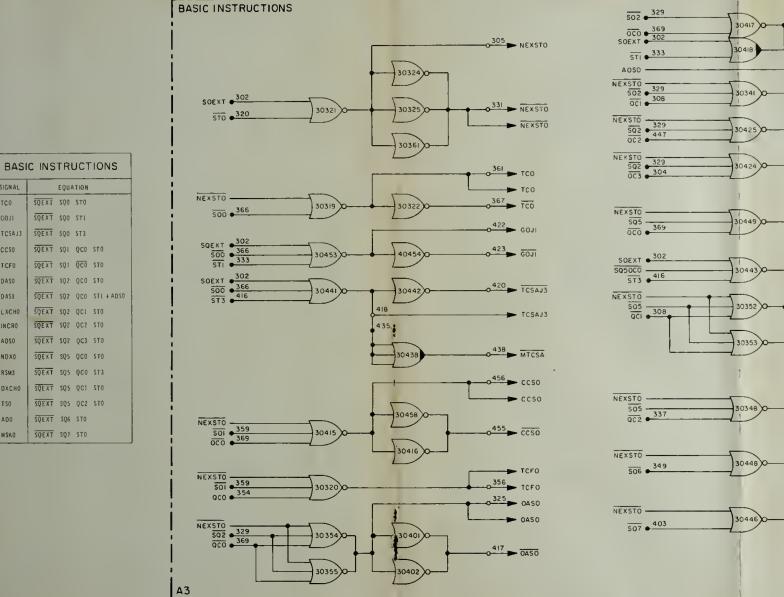

4-5.4.2 <u>Command Generator</u>. The command generator (figure 4-126) contains the subinstruction decoder, instruction decoder, and the counter and peripheral instruction control. The subinstruction decoder receives the SQ and ST code signals from the order code processor. These signals represent the order codes of all machine instructions and are decoded into subinstruction and instruction commands. For example, channel instruction WOR has a binary order code 1 000 101 and stage code 000. The SQ code signals SQEXT, SQ0, QC2, and SQR10 are combined with ST code signal ST0 to produce subinstruction command WOR0.

Figure 4-126. Command Generator, Block Diagram

The instruction decoder receives the coded signals from the order code processor in addition to certain subinstruction commands. It produces signals called instruction commands. An instruction command is used for two or more subinstructions as compared to a subinstruction command which is used for only one subinstruction. For example, instruction command IC1 generates a combination of control pulses shared by subinstructions NDX0 and NDXX0. Instruction command IC1 is produced by signals SQEXT, SQ5, and ST0 for subinstruction NDX0 or by signals SQ5, QC0, and ST0 for subinstruction NDXX0. Other instruction commands are produced from subinstruction commands. For example, IC8 is produced by ORing DXCH0 with LXCH0.

The counter and peripheral instruction control receives instruction signals from the priority control and the peripheral equipment. These signals are applied to separate circuits which control the individual counter and peripheral instructions. The instruction signals from the priority control pertain to counter locations and the instruction(s) associated with each location. For example, signal C31A is interpreted as counter 31 address. The content of this location can only be changed by instruction DINC whose subinstruction command is produced by the counter and peripheral instruction control. Another example is signal C42P, interpreted as counter 42 positive increment or signal

ND-1021042

C42M, counter 42 negative increment. The peripheral equipment supplies instruction signals such as MREAD and MLOAD for the fetch and store instructions, respectively. While the particular instruction is being executed, the counter and peripheral instruction control stores the input signals in the same way that order code signals are stored by register SQ. Since some of the peripheral instructions are several MCT's long, they use the ST code signals. The subinstruction and instruction command outputs of the command generator are used by the control pulse generator in conjunction with time pulses T01 through T12 to produce action pulses.

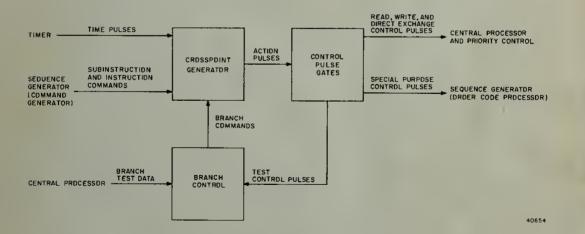

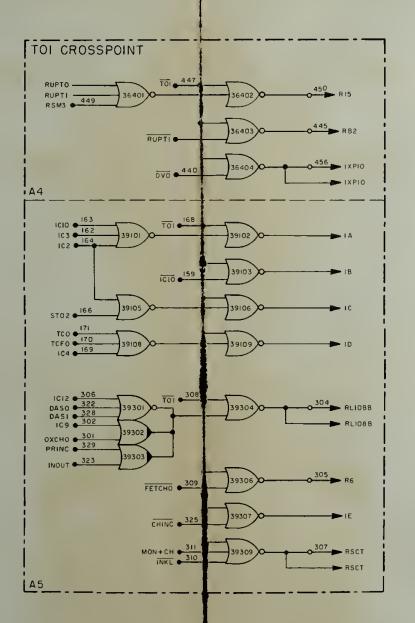

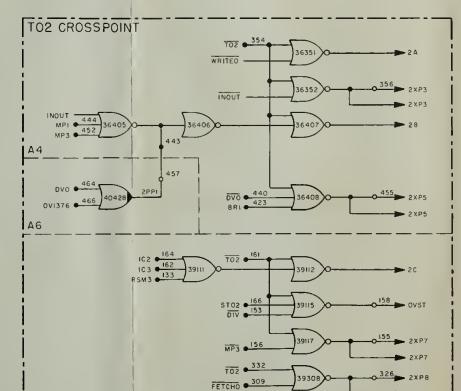

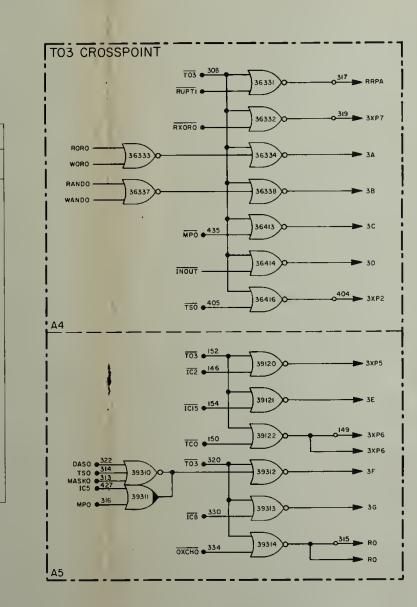

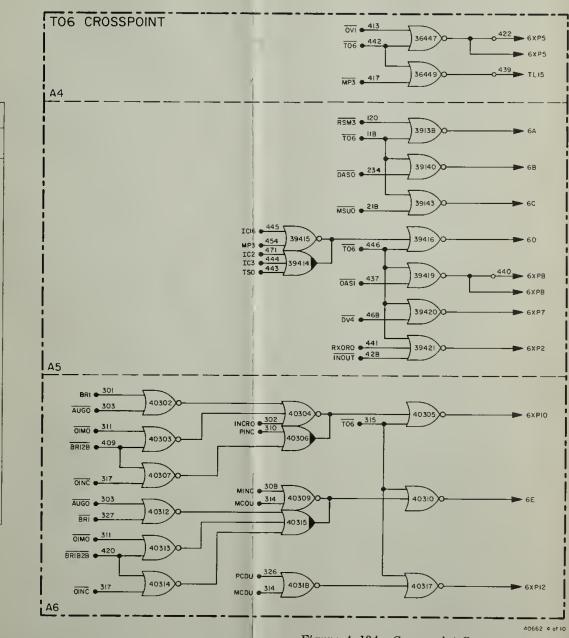

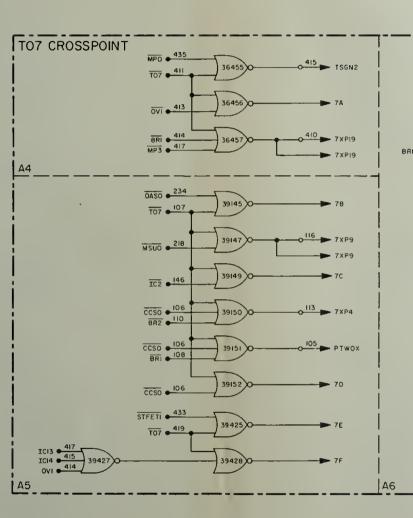

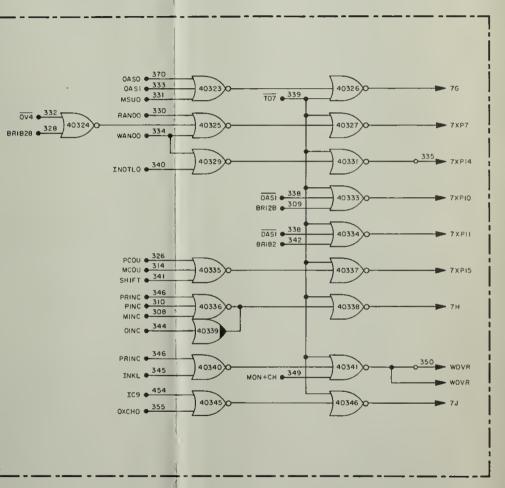

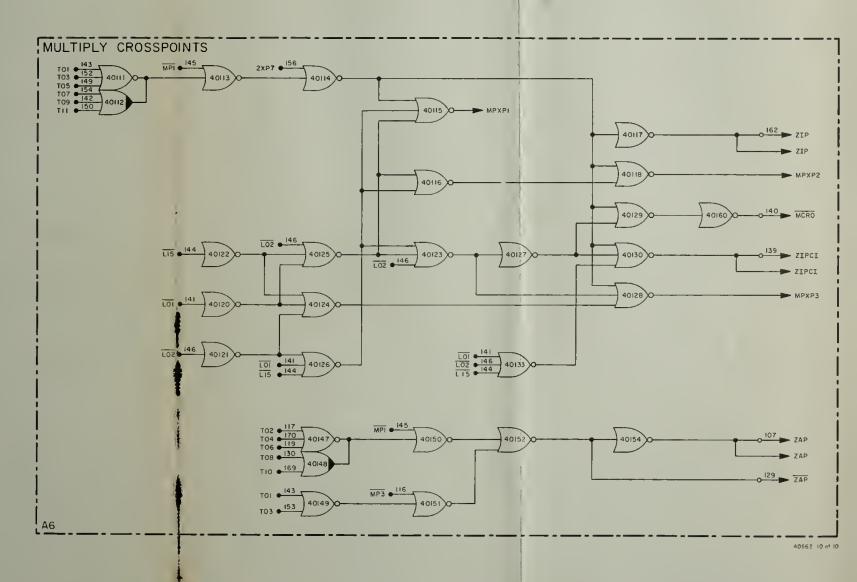

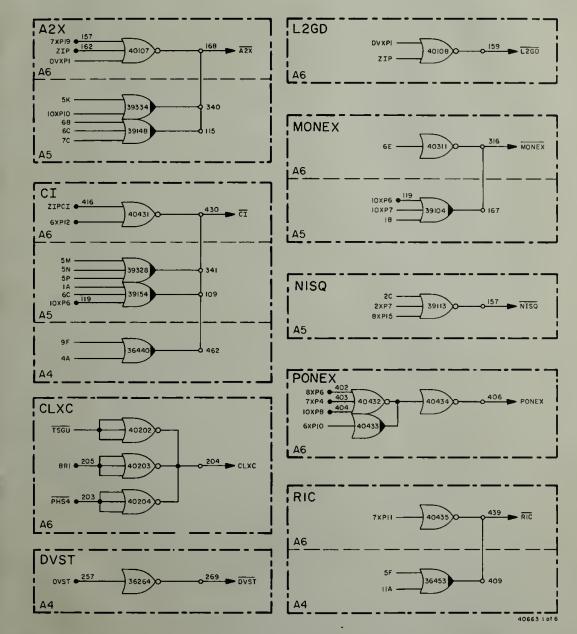

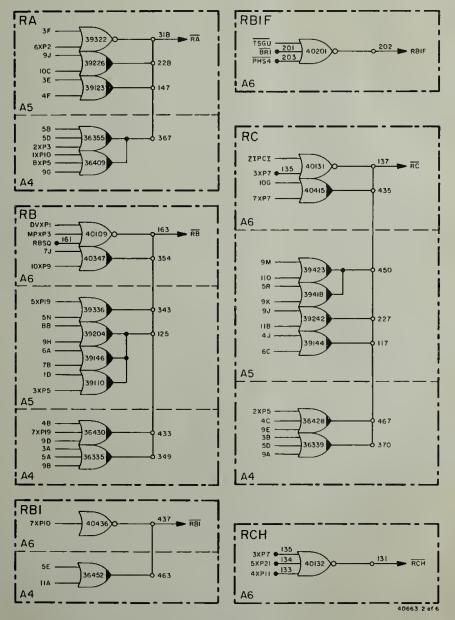

4-5.4.3 <u>Control Pulse Generator</u>. The control pulse generator (figure 4-127) contains the crosspoint generator, control pulse gates, and branch control. The crosspoint generator receives instruction and subinstruction commands from the command generator and branch commands from the branch control. The crosspoint generator produces an action pulse when a command signal and a time pulse are ANDed. This action is called the crosspoint operation. For example, action pulse 5XP12 is produced from subinstruction command DAS0 and time pulse T05. Many instructions use identical action pulses. When this is the case, several command signals such as TC0, TCF0, or IC4 will produce the same action pulse during time period T01. The branch commands are used to change the action pulse that normally is produced at a given time. For example, when certain conditions exist, a branch command will produce action pulse 8XP6 in addition to another action pulse normally produced at time period T08. The action pulses are supplied to the control pulse gates which convert them to specific control pulses for use in instruction execution.

The control pulse gates perform the Boolean NOR function. There is one gate for each control pulse. These gates split the action pulses into as many control pulses as

Figure 4-127. Control Pulse Generator, Block Diagram

are required for a particular operation. For example, action pulse 3XP6 is converted to control pulses RZ and WQ. Some of the control pulses produced by the control pulse gates are used by the sequence generator. These include the special purpose control pulses which control the operation of the order code processor and the test control pulses which are applied to the branch control. The other control pulse groups, namely the read, write, and direct exchange control pulses are used in the central processor and the priority control. The purpose of each control pulse is described in paragraph 4-5.2, Machine Instructions.

The branch control is connected to the write lines of the central processor. Data which is placed onto the write lines by read control pulses is tested in the branch control. The branch control contains two stages. Branch 1 normally tests for sign and branch 2 tests for full quantities such as plus or minus zero. Both branches test for positive and negative overflow and have the overflow bits written directly into the branch register. Positive overflow is 01 where branch 1 is the high order bit. Negative overflow is 10. The branch commands sent to the crosspoint generator affect the action pulses at given times. The branch control also contains the special instruction flip-flop which controls the execution of RELINT, INHINT, and EXTEND instructions.

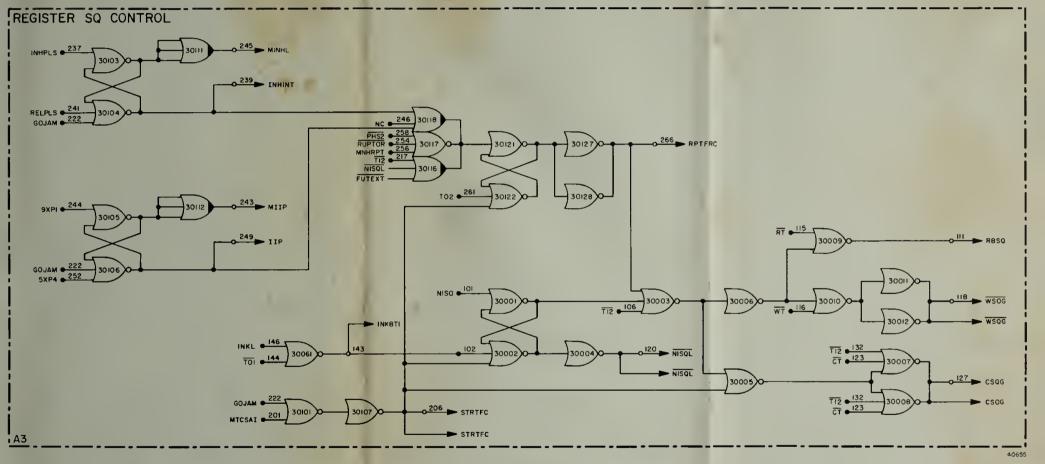

4-5.4.4 Register SQ Control. The register SQ control (figure 4-128) is regulated by special purpose control pulse NISQ from the control pulse generator. Control pulse NISQ causes the register SQ control to produce clear signal CSQG, read signal RBSQ, and write signal WSQG. These signals place the order code (content of register B) onto the write lines and into register SQ at the beginning of each new instruction. The order code signals applied to the register SQ control from the priority control (GOJAM and RUPTOR) and peripheral equipment (MTCSAI) pertain to start, interrupt, and transfer control to specified address instructions, respectively. A distinct priority is associated with each of these three instructions. Interrupt and transfer control to specified address instructions can never be requested when the computer is forcing the execution of the start instruction, which has the highest priority. Certain peripheral instructions occupy the next level of priority, followed by the counter instructions and in turn the transfer control to specified address instruction, which has priority over the interrupt instruction; all six of these instruction categories have priority over basic instructions. In addition, the interrupt instruction cannot be executed when the next instruction being called is an extracode instruction. The register SQ control establishes this priority. It also provides signals to force register SQ to the 0 000 000 state for start and transfer control to specified address instructions, and state 1 000 111 for the interrupt instruction. The register SQ control is able to inhibit the processing of all subsequent interrupts when specified by the program and will permit only one interrupt to be processed at a time. Certain monitor functions built into the register SQ control may be used when the computer is connected to the peripheral equipment.

When control pulse NISQ is applied to the set side of the NISQL flip-flop (figure 4-128), the NISQL flip-flop will set, provided signal STRTFC is not present. Control pulse NISQ is produced during time period T02 or T08 depending on the subinstruction which produces the control pulse. Once the NISQL flip-flop is set, it remains set until signal INKBT1 or STRTFC is produced. Signal INKBT1 occurs at time period T01 when

no counter incrementing is in progress as indicated by the absence of signal INKL. Signal STRTFC may occur anytime during an MCT if produced by signal GOJAM or at a time period predetermined by the peripheral equipment if produced by signal MTCSAI.

Signals CSQG, RBSQ, and WSQG are produced during time period T12 provided that the NISQL flip-flop is set and signal RPTFRC is not present. The clear, read, and write signals are phased by the clear timing signal CT, the read timing signal RT, and the write timing signal WT, respectively. When the start or transfer control to specified address instruction is to be executed, the NISQL flip-flop is reset and signals RBSQ and WSQG are inhibited. However, signal CSQG is produced by signal STRTFC and forces the SQ register to the 0 000 000 state. If signal RPTFRC is present, signals CSQG, RBSQ, and WSQG are not produced. Signal RPTFRC is applied to register SQ and forces it to the 1 000 111 state.

The priority control supplies signal RUPTOR to the register SQ control when the interrupt instruction is to be executed. Signal RUPTOR may be inhibited in the register SQ control by several conditions, one of which is the programmed interrupt inhibit called INHINT. The INHINT condition is established by executing instruction INHINT whose order code is 00.0004. This instruction produces signal INHPLS which is applied to the set side of the INHINT flip-flop (figure 4-128). The INHINT flip-flop will set provided signal GOJAM is not present at the application of signal INHPLS. Once the flip-flop is set, it remains sct until signal GOJAM or RELPLS is produced. Signal RELPLS is produced by instruction RELINT which releases the interrupt inhibit condition. Instruction RELINT has the order code 00.0003. Signal MINHL from the INHINT flip-flop is connected to an indicator on the peripheral equipment. This indicator lights when the INHINT flip-flop is set.

Another condition which inhibits signal RUPTOR is the interrupt in progress (IIP) condition. The IIP condition is established during the execution of the interrupt instruction to indicate that an interrupt is in progress. Subinstruction RUPT0 produces signal 9XP1 which is applied to the set side of the IIP flip-flop (figure 4-128). The IIP flip-flop will set provided signal GOJAM is not present at the application of signal 9XP1. Signal 9XP1 is an action or crosspoint pulse produced during time period T09 of subinstruction RUPTO. Once the IIP flip-flop is set, it remains set until signal GOJAM or 5XP4 is produced. Signal 5XP4 is produced by subinstruction RSM3 which is executed at the completion of an interrupt sequence. Subinstruction RSM3 is part of the RESUME instruction (order code 05.0017) which returns control to the program that was being executed before the interrupt occurred. Signal 5XP4 is also an action or crosspoint pulse which is produced during time period T05. Signal MIIP from the IIP flip-flop is connected to the peripheral equipment. A switch on the peripheral equipment will permit signal MIIP to light an indicator and to cause a monitor T12 stop. This causes the time pulse generator (which produces signals T01 through T12) to stop at time period T12 until it is released by the peripheral equipment. The peripheral equipment can supply signal MNHRPT to the register SQ control. This signal is produced by a switch closure and inhibits signal RUPTOR.

Figure 4-128. Register SQ Control, Logic Diagram

Signal FUTEXT is produced by the register SQ and decoder circuits. This signal is present when the next instruction to be executed is an extracode instruction. Signal FUTEXT is produced when instruction EXTEND or NDX is executed and occurs at time period T08 or T10, respectively. Signal RUPTOR is inhibited by the future extend condition because this condition cannot be re-established when returning to the interrupted program through instruction RESUME. The order codes for instructions EXTEND and NDX which establish the future extend condition are 00.0006 and 15, respectively.

Signal RUPTOR will cause the RPTFRC flip-flop to set at time period T12 subject to the phasing of signal PHS2. A new instruction must be in the process of being called in order for the RPTFRC flip-flop to set. This condition is established by signal NISQL. The RPTFRC flip-flop will set only if signal STRTFC is not present at the same time the set signal is present. The flip-flop is reset at time period T02 or when signal GOJAM or MTCSAI is present.

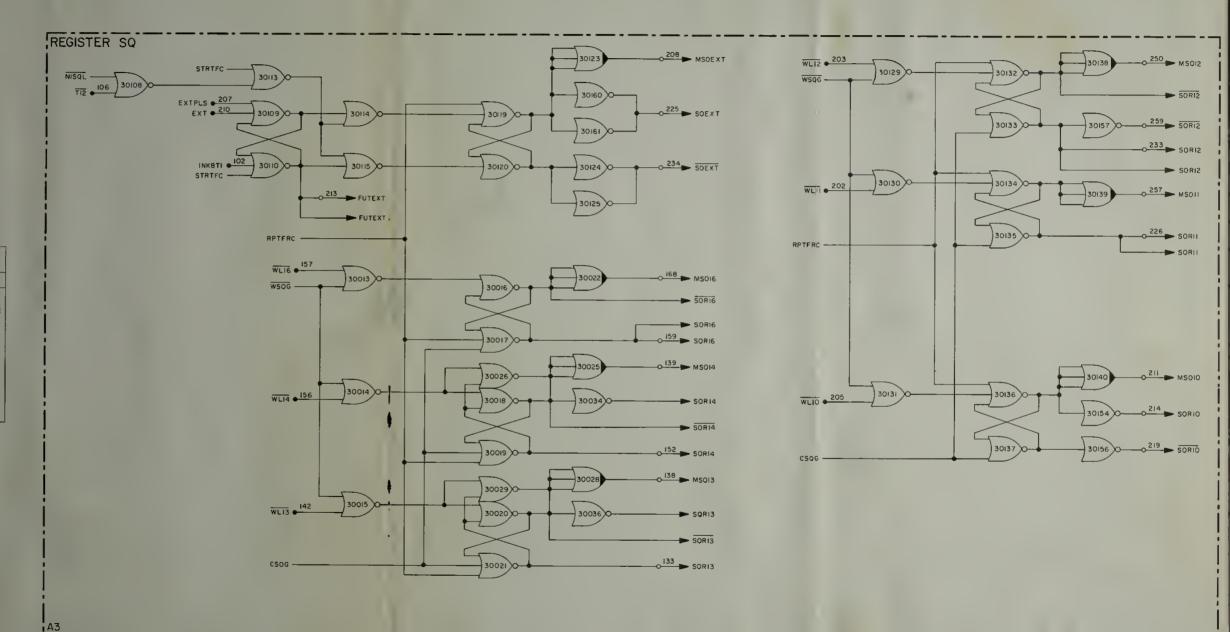

4-5.4.5 <u>Register SQ and Decoders</u>. Register SQ is a seven-bit register which stores the content of the extended order code field as each instruction is being executed. The content of register SQ and decoders produces signals SQEXT, SQ0 through SQ7, QC0 through QC3, and SQR10. These signals are used by the command generator to produce subinstruction and instruction commands.

Register SQ (figure 4-129) is connected to the central processor by write line signals WL16 and WL14 through WL10. The register SQ control produces signal RBSQ which places the order code content of register B onto the write lines. It also produces signal CSQG which clears register SQ and WSQG which writes the new order code into register SQ. Signal CSQG does not clear the SQEXT bit position. This bit position is set when an extracode instruction is to be executed and is controlled by the FUTEXT flipflop.

Special purpose control pulses EXTPLS and EXT are applied to the set side of the FUTEXT flip-flop. The flip-flop will set provided signal STRTFC is not present at the application of signals EXTPLS or EXT. Signal EXTPLS is produced at time pulse T08 by instruction EXTEND. The order code for the EXTEND instruction is 00.0006. Signal EXT is produced at time pulse T10 of subinstruction NDXX1. The FUTEXT flip-flop remains set until signal INKBT1 or STRTFC is produced. Signal INKBT1 occurs at time pulse T01 when no counter incrementing is in progress.

The SQEXT flip-flop can be set at time pulse T12 provided the NISQL and the FUTEXT flip-flops are set. If signal STRTFC is present, the NISQL and FUTEXT flip-flops will be reset and their outputs will cause the SQEXT flip-flop to reset also. Signal RPTFRC also sets the SQEXT flip-flop provided a new instruction is being called and signal STRTFC is not present. Once the SQEXT flip-flop is set, it remains set until the next basic instruction is executed. The resetting of the SQEXT flip-flop is accomplished when signal FUTEXT is not present and signals NISQL and T12 are.

When the start or transfer control to specified address instruction is to be executed, signal STRTFC resets the SQEXT flip-flop as specified in the preceeding paragraph. It

also produces signal CSQG which clears bit positions 16 and 14 through 10 of register SQ. As a result, register SQ is forced to the 0 000 000 state which causes the execution of instruction GOJ or TCSA depending on the state of the stage counter. When the interrupt instruction is to be executed, signal RPTFRC sets bit positions SQEXT and 12 through 10 and resets bit positions 10, 14, and 13 of register SQ. As a result, register SQ is forced to the 1 000 111 state which causes the execution of instruction RUPT.

Signals MSQEXT, MSQ16, and MSQ14 through MSQ10 are connected to indicators on the peripheral equipment so that the content of register SQ can be monitored at any time.

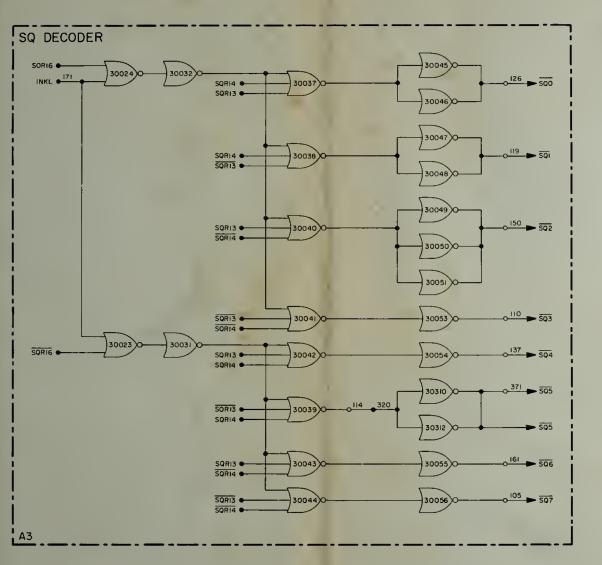

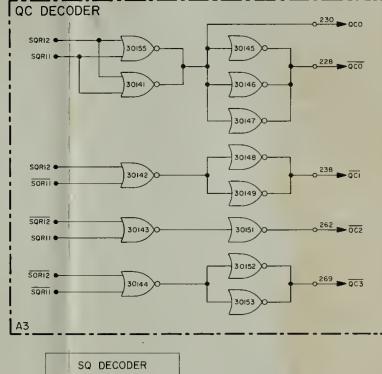

The SQ decoder produces signals SQ0 through SQ7 from the outputs of bit positions 16, 14, and 13 of register SQ. These signals are used in the command generator together with signals SQEXT, QC0 through QC3, and SQR10 to produce subinstruction and instruction commands. Signals SQ0 through SQ7 are inhibited by signal INKL. Signal INKL is produced when a counter instruction is being executed. When signal INKL is present, no commands can be produced other than those for the counter and peripheral instructions.

The QC decoder produces signals QC0 and QC3 for the outputs of bit positions 12 and 11 of register SQ. These signals are also used to produce subinstruction and instruction commands and are not inhibited by counter incrementing.

4-5.4.6 Stage Counter and Decoder. The stage counter and decoder (figure 4-130) is regulated by special purpose control pulses ST1, ST2, DVST, RSTSTG, and TRSM from the control pulse generator and by order code signals GOJAM and MTCSAI from the priority control and peripheral equipment, respectively. The stage counter is used as a storage device which is forced to a different state after the execution of each subinstruction. The stage counter remains in a given state for one MCT, the duration of every subinstruction. The stage counter is forced through various counts depending on the instruction being executed. Most instructions are two MCT's long and are completed by executing subinstruction STD2. As a result, the stage counter is advanced through states 000 and 010. Some instructions are three MCT's long and are completed by executing subinstruction STD2. The stage counter states for these instructions are 000, 001, and 010. Other combinations of states are simply 000 for the transfer control instruction, 000 and 001 for the index instructions, 000 and 011 for the RESUME instruction, and 000, 001, and 011 for the multiply instruction. The divide instruction is seven MCT's long. Gray code counts 000, 001, 011, 111, 110, and 100 are used to enumerate six MCT's of this instruction. The seventh MCT is controlled by state 010 which is that of subinstruction STD2.

The stage counter contains three primary level flip-flops A, B, and C, and three secondary level flip-flops STG1, STG2, and STG3, respectively. The secondary level flip-flops are set to the state of the primary level flip-flops at time pulse T12 for most instructions. For the divide instruction, the transfer of states occurs at time pulses T03 and T12. The primary level flip-flops are reset at time pulse T01 to establish the state 000.

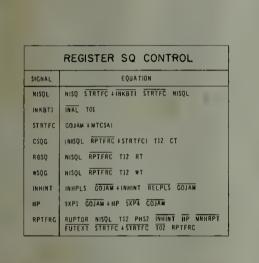

| REGISTER SQ |                                                                                   |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------|--|--|--|--|

| SIGNAL      | EQUATION                                                                          |  |  |  |  |

| FUTEXT      | (EXTPLS + EXT) STRTFC + INKBTI STRTFC FUTEXT                                      |  |  |  |  |

| SQEXT       | FUTEXT NISQ T12 + RPTFRC NISQL T12 STRTFC<br>+ SQEXT- (FUTEXT + NISQL T12 STRTFC) |  |  |  |  |

| SQR16       | WLI6 WSQC CSQC + SQRI6 CSQG RPTFRC                                                |  |  |  |  |

| SQR14       | WL14 WSQC CSQC + SQR14 CSQC RPTFRC                                                |  |  |  |  |

| SQR13       | WL13 WSQC CSQG + SQR13 CSQG RPTFRC                                                |  |  |  |  |

| SQR12       | WL12 WSQG CSQG + RPTFRC + SQRI2 CSQG                                              |  |  |  |  |

| SQR11       | WLII WSQG CSQC + RPTFRC + SQRII CSQG                                              |  |  |  |  |

| SQRIO       | WL10 WSQC CSQG + RPTFRC + SQR11 CSQG                                              |  |  |  |  |

Figure 4-129. Register SQ and Decoder, Logic Diagram (Sheet 1 of 2)

4-243/4-244

40656 1 01 2

SIGNAL

SQO

sqi

5Q2

SQ 3

SQ 4

sqs

SQG

SQ7

EQUATION

SQRIG SQRIA SQRI3 INKL

SQRIG SQRI4 SQRI3 INKL

SQRIG SQRI4 SQRI3 INKL

SQRIG SQRI4 SQRI3 INKL

SQRIG SQRIA SQRI3 INKL

SQR16 SQR14 SQR13 INKL SQR16 SQR14 SQR13 INKL

SQRIG SQRI4 SQRI3 INKL

| QC DECODE |             |  |

|-----------|-------------|--|

| SIGNAL    | EQUATION    |  |

| QCO       | SQR12 SQR11 |  |

| QC1       | SQR12 SQR11 |  |

| QC2       | SQR12 SQR11 |  |

| QC3       | SQR12 SQR11 |  |

40656 2 of 2

Figure 4-129. Register SQ and Decoder, Logic Diagram (Sheet 2 of 2)

|        | STAGE COUNTER                                                                                |

|--------|----------------------------------------------------------------------------------------------|

| SIGNAL | EQUATION                                                                                     |

| A      | STI +(GOJAM +MTGSAI) $\overline{TOI}$ + DVST $\overline{STG3}$ + A $\overline{T}$            |

| 8      | ST2 GOJAM 4 MTCSAI TOI + DVST STGI GOJAM<br>+ NDRIOG X67 XTI TRSM GDJAM TOI + 8 TOI<br>GOJAM |

| C      | DVST STG2 STRTFC +C TO STRTFC                                                                |

| TIZUSE | OVST COJAM + TIZUSE GOJAM RSTSTG                                                             |

| D      | T12 TIZUSE PHS3 + TO3 TIZUSE PHS3                                                            |

| STGI   | A D + STGI (A $\pm \vec{D}$ )                                                                |

| STG2   | B D 4 STG2 (B 4 D)                                                                           |

| \$TG3  | $C = D + STG3 (C + \overline{D})$                                                            |

|        |                                                                                              |

|        | STAGE DECODER       |  |  |  |

|--------|---------------------|--|--|--|

| SIGNAL | EQUATION            |  |  |  |

| ST0    | STG3 STG2 STGI      |  |  |  |

| STD?   | STG3 STG2 STG1 INKL |  |  |  |

| ST3    | STG3 STG2 STG1      |  |  |  |

| STID   | STG3 STG2 STG1      |  |  |  |

| ST1376 | STID + ST376        |  |  |  |

| ST 376 | STG2 (STG1 + STG3)  |  |  |  |

| ST3764 | ST376 + ST4         |  |  |  |

| ST4    | STG3 STG2 STGI      |  |  |  |

-

## ND-1021042 MANUAL

Figure 4-130. Stage Counter and Decoder, Logic Diagram

4-247/4-248

The stage counter can establish state 001 three ways. When the start instruction is to be executed, signal GOJAM sets flip-flop A and resets flip-flop B. Flip-flop C is reset by signal STRTFC. Control pulse ST1 sets flip-flop A (at time pulse T10) and control pulse DVST sets the flip-flop (at time pulse T02) provided that flip-flop STG3 is not set during the Gray code count sequence.

The state010 can only be produced in one way, by control pulse ST2 which sets flipflop B at time pulse T08 or T10 depending on the subinstruction which produces the control pulse.

The state 011 can be produced four ways. When the transfer control to specified address instruction is to be executed, signal MTCSAI sets flip-flops A and B and signal STRTFC resets flip-flop C. During the execution of subinstruction MP1, control pulses ST1 and ST2 are produced at time pulse T10. These control pulses set flip-flops A and B and cause the execution of subinstruction MP3. During the execution of instruction RESUME, control pulse TRSM sets flip-flop B at time pulse T05. Instruction RESUME is an address-dependent instruction consisting of subinstructions NDX0 and RSM3. The content of register S must be octal 0017 for control pulse ST1 sets flip-flop B. At time pulse T10 of subinstruction NDX0, control pulse ST1 sets flip-flop A thereby establishing the state 011 for subinstruction RSM3. During the execution of the divide instruction, control pulse DVST sets flip-flop A at time pulse T02 provided that flip-flop STG3 is not set. Flip-flop B is set by DVST provided flip-flop STG1 is set. Since flip-flop STG2 is not set when control pulse DVST is produced, flip-flop C remains reset, thus establishing state 011.

States 111, 110, and 100 are established by control pulse DVST at time pulse T02 of instruction divide. Flip-flops A, B, and C are set provided that flip-flop STG3 is not set and flip-flops STG1 and STG2 are set, respectively. This establishes state 111. States 110 and 100 are established in a similar way and are dependent on the states of flip-flops STG1, STG2, and STG3.

The contents of flip-flops A, B, and C are transferred to flip-flops STG1, STG2, and STG3, respectively, at time pulse T12 if the T12USE flip-flop is not set. The transfer is subject to the phasing of signal PHS3. The T12USE flip-flop is set at time pulse T02 by control pulse DVST provided signal GOJAM is not present. Once the flip-flop is set, it remains set until reset by control pulse RSTSTG (which occurs at time pulse T08 of subinstruction DV4) unless signal GOJAM occurs first. When the T12USE flip-flop is set, the contents of the primary level flip-flops are transferred to the secondary level flip-flops at time pulse T03 according to the phase of signal PHS3. Signal DIVSTG is also produced at time pulse T03 under these conditions. When the secondary level flip-flops are set, they cannot be reset unless signal D is present. Signals MST1, MST2, and MST3 are connected to lights on the peripheral equipment to indicate the state of the stage counter.

The stage decoder (figure 4-130) produces signals ST0, ST1D, STD2, ST3, ST4, ST1376, ST376, and ST3764. This signal group is the decoded output of the stage counter

and is used in conjunction with signals SQEXT, SQ0 through SQ7, QC0 through QC3, and SQR10 to produce subinstruction and instruction commands. Signals ST0, ST1D, STD2, ST3 and ST4 are produced when the stage counter is set to states 000, 001, 010, 011, and 100, respectively. Signal ST376 is produced when the stage counter is in state 011, 111, or 110. Likewise, signal ST1376 is produced when the stage counter is set to state 001, 011, 111, or 110, and signal ST3764 is produced during states 011, 111, 110, or 100.

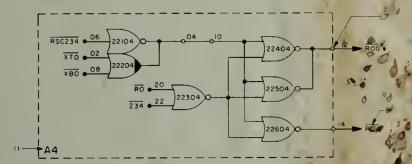

4-5.4.7 <u>Subinstruction Decoder</u>. The subinstruction decoder receives the SQ and ST code signals from the order code processors and produces signals called subinstruction and instruction commands. Signals SQEXT, SQ0 through SQ7, QC0 through QC3, and SQR10 comprise the SQ code signals. Signals ST0 through ST4, ST376, ST1376, and ST3764 comprise the ST code signals. The SQEXT and SQR10 signals represent the high and low order bits, respectively, of register SQ. Signals SQ0 through SQ7 represent octal quantities 0 through 7 respectively, in bit positions 16, 14, and 13 of register SQ. Signals QC0 through QC3 represent octal quantities 0 through QC3 represent octal quantities 0 through QC3 represent octal quantities 0 through 3, respectively, in bit positions 12 and 11 of register SQ. The SQ and QC signals are the decoded outputs of the register SQ and decoder circuits. The ST code signals represent the state of the stage counter. For example, signal ST1 represents state 001. The ST signals are the decoded outputs of the stage counter and decoder circuits.

The subinstruction decoder utilizes the SQ and ST code signals in producing subinstruction and instruction commands. The command signals in turn are ANDed with time pulses T01 through T12 as necessary to produce crosspoint signals. This action is accomplished in the crosspoint generator. The crosspoint signals produce the control pulses which regulate the data flow of the computer. By definition, a subinstruction command is used for only one subinstruction. For example, command STD2 is used only during subinstruction STD2. An instruction command is therefore defined as a command which is used by two or more subinstructions. For example, command IC3 is used for subinstructions STD2, TC0, and TCF0. Table 4-IX lists all of the commands produced by the various SQ and ST codes. The subinstructions which relate to the specific SQ and ST codes are also listed in table 4-IX.

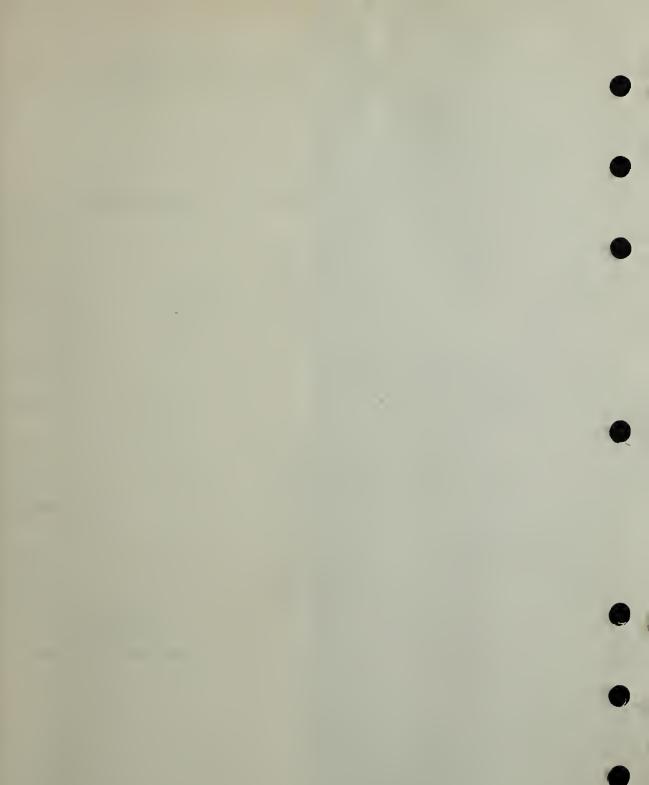

Figure 4-131 shows the logic circuits that produce the subinstruction commands for basic, channel, and extracode instructions. Signal CCS0 is used as an example to illustrate the production of commands. When subinstruction CCS0 is to be executed, register SQ is set to the 0 001 00X state and the stage counter is set to 000. As a result, the order code processor supplies signals SQ1, QC0, and ST0 to the command generator. Since CCS is a basic instruction, the high order bit of register SQ is a logic ZERO and signal SQEXT is not present. The circuit for basic instructions detects this condition and produces signal NEXST0. Had signal ST1 been present instead of ST0, signal NEXST0 would not be produced. Signals NEXST0, SQ1, and QC0 are then ANDed to produce subinstruction command CCS0.

The QC signals are produced by the two high order bits of the address field. Instructions which do not use the extended order code field have commands that are produced

| Subinstruction     | SQ Code     | ST Code | BR1 and BR2 | Commands            |  |  |

|--------------------|-------------|---------|-------------|---------------------|--|--|

| BASIC INSTRUCTIONS |             |         |             |                     |  |  |

| STD2               |             | 2       |             | STD2<br>IC3         |  |  |

| TC0                | 00          | 0       |             | TC0<br>IC3          |  |  |

| CCS0               | 010         | 0       |             | CCS0<br>IC12        |  |  |

| TCF0               | 011-<br>013 | 0       |             | TCF0<br>IC3         |  |  |

| DAS0               | 020         | 0       |             | DAS0<br>IC10        |  |  |

| DAS1               | 020         | 1       |             | DAS1                |  |  |

| LXCH0              | 021         | 0       |             | IC8<br>IC9          |  |  |

| INCR0              | 022         | 0       |             | INCR0<br>PRINC      |  |  |

| ADS0               | 023         | 0       |             | ADS0<br>DAS1        |  |  |

| CA0                | 03          | 0       |             | IC6<br>IC13         |  |  |

| CS0                | 04          | 0       |             | IC7<br>IC13         |  |  |

| NDX0               | 050         | 0       |             | NDX0<br>IC1<br>IC13 |  |  |

| NDX1               | 050         | 1       |             | IC2                 |  |  |

| RSM3               | 050         | 3       |             | RSM3                |  |  |

#### Table 4-IX. Commands Per Subinstruction

(Sheet 1 of 6)

| Subinstruction            | SQ Code | ST Code      | BR1 and BR2 | Commands               |  |  |

|---------------------------|---------|--------------|-------------|------------------------|--|--|

| BASIC INSTRUCTIONS (cont) |         |              |             |                        |  |  |

| DXCH0                     | 051     | 0            |             | DXCH0<br>IC8<br>IC10   |  |  |

| DXCH1                     | 051     | 1            |             | IC5<br>IC9             |  |  |

| TS0                       | 052     | 0            |             | TS0<br>IC9             |  |  |

| XCH0                      | 053     | 0            |             | IC5<br>IC9             |  |  |

| AD0                       | 06      | 0            |             | AD0<br>IC11<br>IC13    |  |  |

| MASK0                     | 07      | 0            |             | MASK0<br>IC14          |  |  |

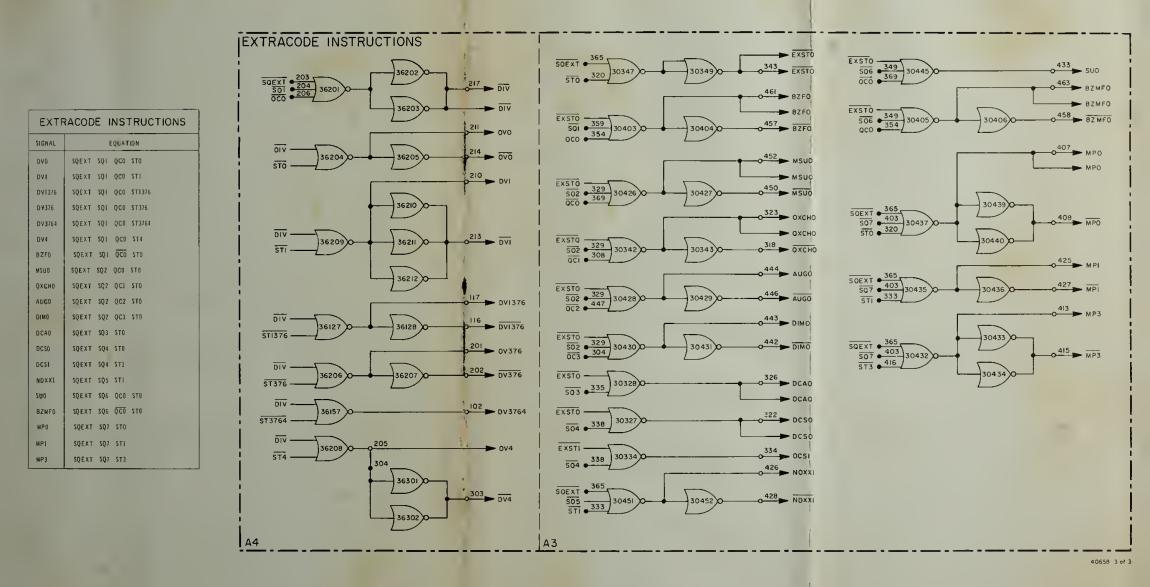

|                           | EXTR    | ACODE INSTRU | JCTIONS     |                        |  |  |

| DV0                       | 110     | 0            |             | DV0<br>DIV             |  |  |

| DV1                       | 110     | 1            |             | DV1<br>DV1376<br>DIV   |  |  |

| DV3                       | 110     | 3            |             | DV1376<br>DV376<br>DIV |  |  |

| DV7                       | 110     | 7            |             | DV1376<br>DV376<br>DIV |  |  |

Table 4-IX. Commands Per Subinstruction

.

| Subinstruction                | SQ Code     | ST Code | BR1 and BR2    | Commands                    |  |

|-------------------------------|-------------|---------|----------------|-----------------------------|--|

| EXTRACODE INSTRUCTIONS (cont) |             |         |                |                             |  |

| DV6                           | 110         | 6       |                | DV1376<br>DV376<br>DIV      |  |

| DV4                           | 110         | 4       |                | DV4                         |  |

| BZF0                          | 111-<br>113 | 0       | XX<br>X0<br>X1 | IC15<br>IC17<br>IC16        |  |

| MSU0                          | 120         | 0       |                | MSU0<br>IC12                |  |

| QXCH0                         | 121         | 0       |                | QXCH0<br>IC9                |  |

| AUG0                          | 122         | 0       |                | AUG0<br>PRINC               |  |

| DIM0                          | 123         | 0       |                | DIM0<br>PRINC               |  |

| DCA0                          | 13          | 0       |                | DCA0<br>IC4<br>IC10<br>IC13 |  |

| DCA1                          | 13          | 1       |                | IC6<br>IC13                 |  |

| DCS0                          | 14          | 0       |                | DCS0<br>IC4<br>IC10<br>IC13 |  |

| DCS1                          | 14          | 1       |                | IC7<br>IC13                 |  |

Table 4-IX. Commands Per Subinstruction

ND-1021042

MANUAL

| Subinstruction                | SQ Code     | ST Code | BR1 and BR2          | Commands                     |

|-------------------------------|-------------|---------|----------------------|------------------------------|

| EXTRACODE INSTRUCTIONS (cont) |             |         |                      |                              |

| NDXX0                         | 15          | 0       |                      | IC1<br>IC13                  |

| NDXX1                         | 15          | 1       |                      | NDXX1<br>IC2                 |

| SU0                           | 160         | 0       |                      | SU0<br>IC11<br>IC13          |

| BZMF0                         | 161-<br>163 | 0       | XX<br>00<br>X1<br>1X | IC15<br>IC17<br>IC16<br>IC16 |

| MP0                           | 17          | 0       |                      | MP0<br>IC14                  |

| MP1                           | 17          | 1       |                      | MP1                          |

| MP3                           | 17          | 3       |                      | MP3                          |

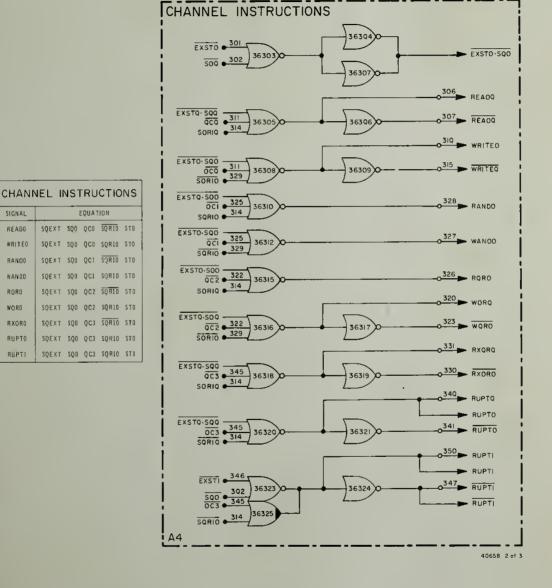

| CHANNEL INSTRUCTIONS          |             |         |                      |                              |

| READ0                         | 1000        | 0       |                      | READ0<br>INOUT               |

| WRITE0                        | 1001        | 0       |                      | WRITE0<br>INOUT              |

| RAND0                         | 1010        | 0       |                      | RAND0<br>INOUT               |

| WAND0                         | 1011        | 0       |                      | WAND0<br>INOUT               |

| ROR0                          | 1020        | 0       |                      | ROR0<br>INOUT                |

Table 4-IX. Commands Per Subinstruction

(Sheet 4 of 6)

| Subinstruction              | SQ Code | ST Code      | BR1 and BR2 | Commands                |

|-----------------------------|---------|--------------|-------------|-------------------------|

| CHANNEL INSTRUCTIONS (cont) |         |              |             |                         |

| WOR0                        | 1021    | 0            |             | WOR0<br>INOUT           |

| RXOR0                       | 1030    | 0            | 1.0         | RXOR0<br>INOUT<br>IC14  |

|                             | INTE    | RRUPT INSTRU | UCTIONS     |                         |

| RUPT0                       | 1031    | 0            |             | RUPT0                   |

| RUPT1                       | 1031    | 1            |             | RUPT1                   |

| GOJ1                        | 00      | 1            |             | GOJ1                    |

|                             | COT     | JNTER INSTRU | CTIONS      |                         |

| PINC                        |         |              |             | PINC<br>PARTC<br>INKL   |

| MINC                        |         |              |             | MINC<br>PARTC<br>INKL   |

| PCDU                        |         |              |             | PCDU<br>PARTC<br>INKL   |

| MCDU                        |         |              |             | MCDU<br>PARTC<br>INKL   |

| DINC                        |         |              |             | DINC<br>PARTC<br>INKL   |

| SHINC                       |         |              |             | SHIFT<br>INK L          |

| SHANC                       |         |              |             | SHANC<br>SHIFT<br>INK L |

#### Table 4-IX. Commands Per Subinstruction

| Subinstruction          | SQ Code | ST Code | BR1 and BR2 | Commands                                  |

|-------------------------|---------|---------|-------------|-------------------------------------------|

| PERIPHERAL INSTRUCTIONS |         |         |             |                                           |

| TCSAJ3                  | 00      | 3       |             | TCSAJ3                                    |

| INOTRD                  |         |         | 9           | CHINC<br>INKL<br>MON+CH                   |

| INOTLD                  |         |         |             | INOTLD<br>CHINC<br>INKL<br>MON+CH         |

| FETCH0                  |         | 0       |             | FETCH0<br>MON<br>INKL<br>MON+CH           |

| FETCH1                  |         | 1       |             | MON<br>STFET1<br>INKL<br>MON+CH           |

| STORE0                  |         | 0       |             | FETCH0<br>MON<br>INKL<br>MON+CH           |

| STORE1                  |         | 1       |             | MON<br>STFET1<br>STORE1<br>INKL<br>MON+CH |

Table 4-IX. Commands Per Subinstruction

(Sheet 6 of 6)

# ND-1021042 MANUAL

434 DASI

437 DASI

328 LXCHO

449 INCRO

430 NOXO

429 NOXO

414 - RSM3

419 RSM3

0330 DXCHO

0<sup>431</sup> ► A00

406 MASKO

0404 MASKO

MASKO

- Охсно

AOSO

н Цхсно

30421

30419

30420

30450 X

30444

30350)0

30351

30447

40658 1 OF 3

Figure 4-131. Subinstruction Decoder, Logic Diagram (Sheet 1 of 3)

0011 SQEXT SQO STI TCSAJ3 SQEXT SQ0 ST3 SQEXT SQL QC0 STO CCS0 SQEXT SQ1 QCO STO T CF0 DASO SQEXT SQ2 QC0 STO DASI SOEXT SOZ QCO STL + ADSO SQEXT SQ2 QC1 STO LXCHO SQEXT SQ2 QC2 STO INCRO SQEXT SQ2 QC3 STO ADSO NDX0 SQEXT SQS QCO STO RSM3 SQEXT SQ5 QC0 ST3 SQEXT SQ5 QC1 STO DXCHO SQEXT SQ5 QC2 STO T SO SQEXT SQ6 STO AD0 SQEXT SQ1 STO MSKO

EQUATION

SQEXT SQO STO

SIGNAL

TCO

4-257/4-258

Figure 4-131. Subinstruction Decoder, Logic Diagram (Sheet 2 of 3)

# ND-1021042 MANUAL

Figure 4-131. Subinstruction Decoder, Logic Diagram (Sheet 3 of 3)

without the QC signals. The basic instructions which can use any computer address are TC, CA, CS, AD, and MASK. The subinstruction commands produced without QC signals are TC0, AD0, and MASK0. Instructions CA and CS are controlled by instruction command signals from the instruction decoder.

The basic instructions which use the entire order code field are:

| (1) CCS  | (5) INCR   | (9) DXCH |

|----------|------------|----------|

| (2) TCF  | (6) ADS    | (10) TS  |

| (3) DAD  | (7) NDX    | (11) XCH |

| (4) LXCH | (8) RESUME |          |

These instructions have commands which are produced with a QC signal. Other important points concerning basic instructions are that signal DAS1 is an instruction command and signal LXCH0 is not used to produce crosspoint pulses.

Signal DAS1 is an instruction command because it is used for subinstructions DAS1 and ADS0. Subinstruction LXCH0 is controlled by instruction commands IC8 and IC9 which are produced by signal LXCH0. The logic diagram for basic instructions contains the circuits which produce commands TCSAJ3 and GOJ1. These commands are for peripheral and interrupt instructions, respectively, and are included here because they have order codes similar to basic instructions. Signal MTCSA is fed to the peripheral equipment.

The channel instructions and RUPT instruction are controlled by commands which are produced from the entire order code content of register SQ and the content of the stage counter. For example, when subinstruction WAND0 is to be executed, register SQ is set to the 1 000 011 state and the stage counter is set to 000. As a result, signals SQEXT, SQ0, QC1, and SQR10 are present and ANDed to produce subinstruction command WAND0.

The extracode instructions are also shown in figure 4-131. Special attention is given to the commands for the divide instruction because of the Gray code count used to control the commands. When instruction DV is to be executed, register SQ is set to the 1 001 00X state and the stage counter is set to 000. As a result, signals SQEXT, SQ1, QC0, and ST0 are supplied to the subinstruction decoder. Signals SQEXT, SQ1, and QC0 are ANDed to produce instruction command DIV. In addition, signals DIV and ST0 are ANDed to produce subinstruction command DV0. Since signal DIV is produced without an ST signal, it remains for the duration of the divide instruction. It is also used to produce subinstructions DV1 and DV4 and instruction commands DV1376, DV376, and DV3764. Subinstructions DV1, DV3, DV7, and DV6 start at time pulse T04 and end at the following time pulse T03. Instruction command DV1376 produces crosspoint pulse for time pulse T01, T02, and T03 whereas instruction command DV376 produces crosspoint pulses for time pulses S04 through T12. Instruction command DV3764 is not used to produce crosspoint pulses but it does turn off fixed memory timing during four MCT's of the divide instruction.

The remaining commands for the extracode instructions are similar to the commands for the basic instructions. Instructions DCA, DCS, NDXX, and MP do not encroach on the address field for their order codes. As a result, the commands for these instructions do nut use a QC signal. Signals BZF0, DCS1, and BZMF0 are not used to produce crosspoint pulses but are used to produce instruction command signals which control the associated subinstructions.

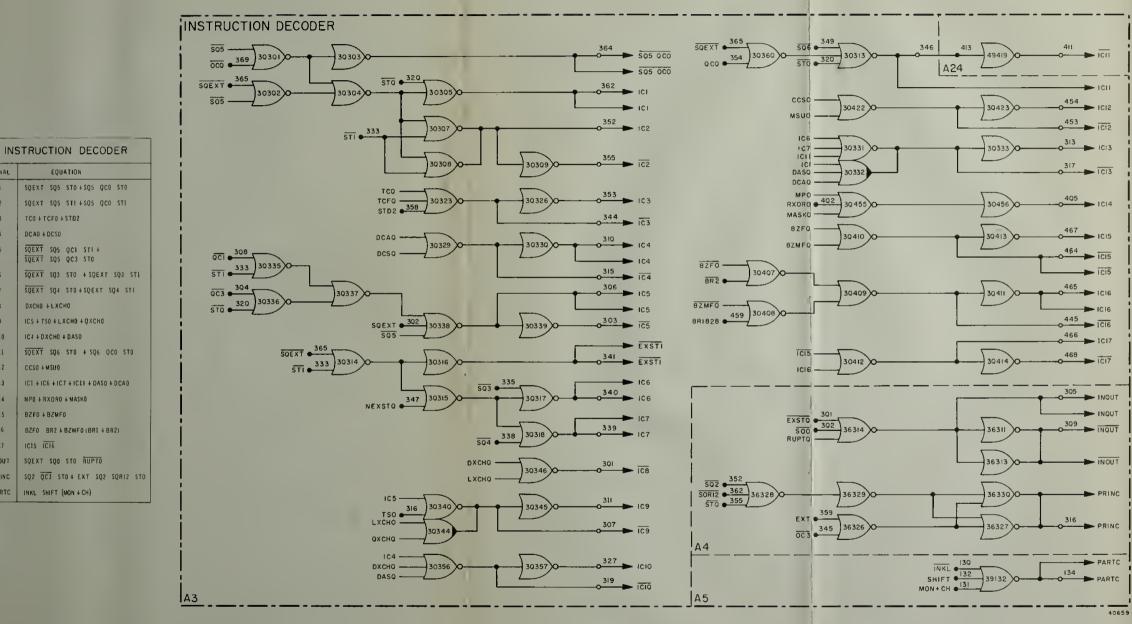

4-5.4.8 Instruction Decoder. The instruction decoder receives the SQ and ST code signals from the order code processor and commands from the subinstruction decoder. The instruction decoder produces commands that are used for two or more subinstructions. These commands are ANDed with time pulses T01 through T12 as necessary to produce crosspoint pulses. Table 4-IX lists the commands produced for each subinstruction. Table 4-X lists the subinstructions that use a particular command for producing crosspoint pulses.

| Command | Subinstructions  | Command | Subinstructions   |

|---------|------------------|---------|-------------------|

| AD0     | AD0              | DIV     | DV0               |

| ADS0    | ADS0             |         | DV1<br>DV3        |

| AUG0    | AUG0             |         | DV7<br>DV6        |

| CCS0    | CCS0             | DV0     | DV0               |

| CHINC   | INOTRD<br>INOTLD | DV1     | DV1               |

| DAS0    | DAS0             | DV4     | DV4               |

| DAS1    | DAS1<br>ADS0     | DV376   | DV3<br>DV7<br>DV6 |

| DCA0    | DCA0             | DV1376  | DV1               |

| DCS0    | DCS0             |         | DV3<br>DV7        |

| DIM0    | DIM0             |         | DV6               |

| DINC    | DINC             | DXCH0   | DXCH0             |

|         |                  |         |                   |

| Table 4-X. Subinstructions Per | Command |

|--------------------------------|---------|

|--------------------------------|---------|

(Sheet 1 of 4)

| Command | Subinstructions  | Command | Subinstructions  |

|---------|------------------|---------|------------------|

| FETCH0  | FETCH0<br>STORE0 | IC12    | MSU0             |

|         |                  | IC 13   | CA0              |

| GOJ1    | GOJ1             |         | CS0              |

| IC1     | NDX0             |         | NDX0<br>AD0      |

| ICI     | NDX0<br>NDXX0    |         | DCA0             |

|         | ND/210           |         | DCA1             |

| 1C2     | NDX1             |         | DCS0             |

|         | NDXX1            |         | DCS1             |

| 100     |                  |         | NDXX0            |

| IC3     | STD2<br>TC0      |         | SU0              |

|         | TCF0             | IC14    | MASK0            |

|         | 1010             |         | MP0              |

| IC4     | DCA0             |         | RXOR0            |

|         | DCS0             |         |                  |

| 105     | DVGUU            | IC15    | BZF0             |

| IC5     | DXCH1<br>XCH0    |         | BZMF0            |

|         |                  | IC16    | BZF0             |

| IC6     | CA0<br>DCA1      |         | BZMF0            |

|         |                  |         |                  |

| IC7     | CS0              | IC17    | BZF0             |

|         | DCS1             |         | BZMF0            |

| IC8     | LXCH0<br>DXCH0   | INCR0   | INCR0            |

| IC9     | LXCH0            | INKL    | PINC             |

|         | DXCH1            |         | MINC             |

|         | TS0              |         | PCDU             |

|         | XCH0             |         | MCDU             |

|         | QXCH0<br>DAS0    |         | DINC<br>SHINC    |

|         |                  |         | SHANC            |

| IC10    | DXCH0            |         | INOTRD           |

|         | DCA0<br>DCS0     |         | INOTLD           |

| 10.11   |                  |         | FETCH0           |

| IC11    | AD0              |         | FETCH1           |

|         | SU0<br>CCS0      |         | STORE0<br>STORE1 |

|         | 0000             |         | STORET           |

#### Table 4-X. Subinstructions Per Command

(Sheet 2 of 4)

| Command | Subinstructions  | Command | Subinstructions  |

|---------|------------------|---------|------------------|

| INOTLD  | INOTLD           | PARTC   | PINC<br>MINC     |

| INOUT   | READ0            |         | PCDU             |

|         | WRITE0           |         | MCDU             |

|         | RAND0<br>WAND0   |         | DINC             |

|         | ROR0             | PCDU    | PCDU             |

|         | WOR0             |         | 1000             |

|         | RXOR9            | PINC    | PINC             |

| MASK0   | MASK0            | PRINC   | INCR0            |

|         |                  |         | AUG0             |

| MCDU    | MCDU             |         | DIM0             |

| MINC    | MINC             | QXCH0   | QXCH0            |

| MON     | FETCH0           | RAND0   | RAND0            |

|         | FETCH1<br>STORE0 | READ0   | READ0            |

|         | STORE1           | I READU | ALAD0            |

|         |                  | ROR0    | ROR0             |

| MON+CH  | INOTRD<br>INOTLD | RSM3    | RSM3             |

|         | FETCH0           | 1/01/10 | RSM3             |

|         | FETCH1           | RUPT0   | RUPT0            |

|         | STORE0<br>STORE1 | RUPT1   | DUDTI            |

|         | STORET           | KUPII   | RUPT1            |

| MP0     | MP0              | RXOR0   | RXOR0            |

| MP1     | MP1              | SHANC   | SHANC            |

| MP3     | M P3             | SHIFT   | SHINC            |

| MSU0    | MSU0             |         | SHANC            |

|         | 11000            | STD2    | STD2             |

| NDX0    | NDX0             |         |                  |

| NDXX1   | NDXX1            | STFET1  | FETCH1<br>STORE1 |

|         | 1127111          |         | 01 OILET         |

|         |                  |         |                  |

| Table 4-X. S | ubinstructions | Per Command |

|--------------|----------------|-------------|

|--------------|----------------|-------------|

(Sheet 3 of 4)

| Command | Subinstructions | Command | Subinstructions |

|---------|-----------------|---------|-----------------|

| STORE1  | STORE1          | TCSAJ3  | TCSAJ3          |

| SU0     | SU0             | TS0     | TS0             |

|         | <b>7</b> 00     | WAND0   | WAND0           |

| TC0     | TC0             | WOR0    | WOR0            |

| TCF0    | TCF0            | WRITE0  | WRITE0          |

| Table 4-X. Subinstructions Per Con |

|------------------------------------|

|------------------------------------|

#### (Sheet 4 of 4)

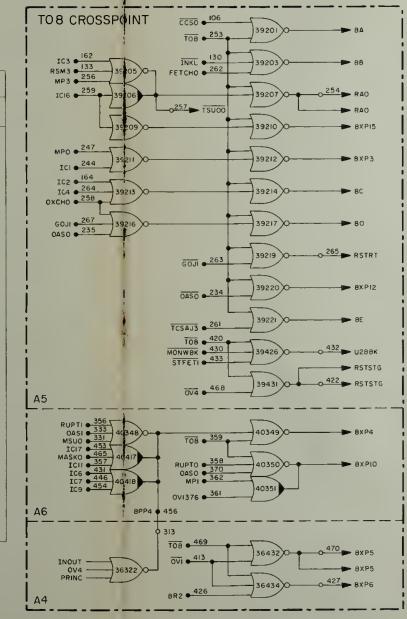

Figure 4-132 shows the logic circuits that produce most of the instruction commands for basic, channel, extracode, counter, and peripheral instructions. Two examples are used to describe how the instruction commands are produced. First, consider signal IC5 which is used for subinstructions DXCH1 and XCH0. When subinstruction DXCH1 is to be executed the order code content of register SQ is 0 101 01X and the stage counter is set to 001. As a result, signals SQ5, QC1, and ST1 are present. Since the high order bit is a logic ZERO, signal SQEXT is not present. These conditions are detected by an AND function and signal IC5 is produced. When subinstruction XCH0 is to be executed signals SQ5, QC3, and ST0 are present and signal SQEXT is not present. These conditions are also detected by an AND function and signal IC5 is produced.

The second way to produce instruction command signals is by ORing various subinstruction commands. For example, signal IC12 is produced by subinstruction command CCS0 or MSU0. Another example is signal IC10 which is produced by subinstruction command DXCH0 or DAS0. It is also produced by instruction command signal IC4. Commands IC16 and IC17 are dependent on branch conditions. Signal IC16 is produced by signals BZF0 and BR2 or by signals BZMF0 and either BR1 or BR2. Signal IC17 is produced when signal IC16 is not present because of improper branch conditions during subinstructions BZF0 and BZMF0.

.

SIGNAL

103

3C2

103

104

105

106

107

108

109

IC10

1011

1012

(C13

IC14

1015

1016

1017

INOUT

PRINC

PARTC

DCA0 + DCS0

CCS0 + MSU0

BZF0 + BZMF0

IC15 IC16

Figure 4-132. Instruction Decoder, Logic Diagram

#### 4-269/4-270

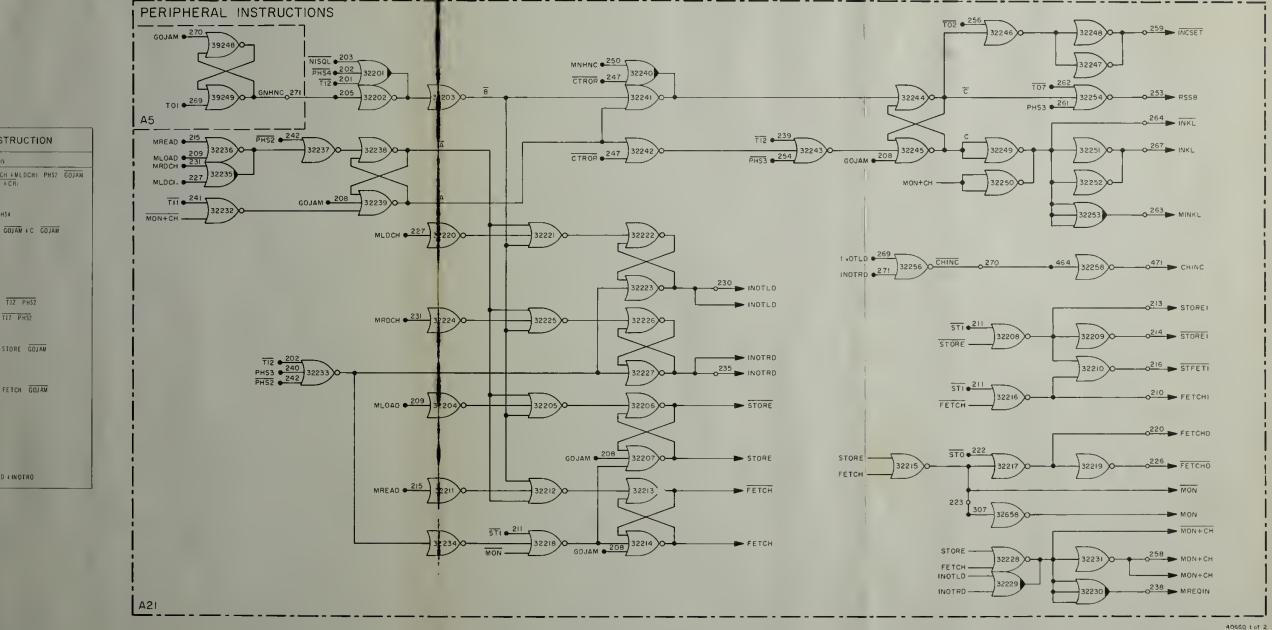

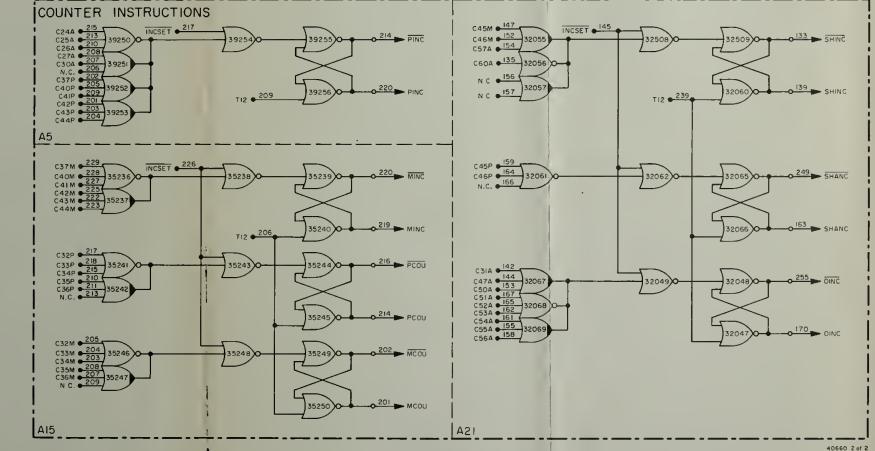

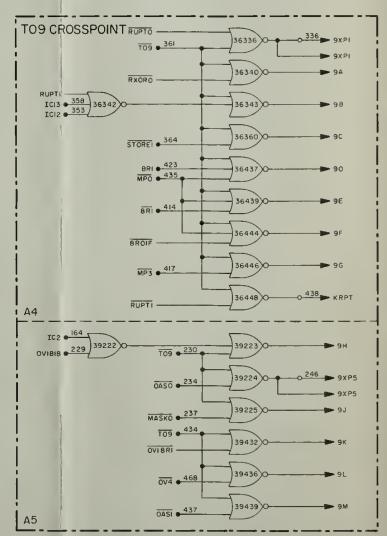

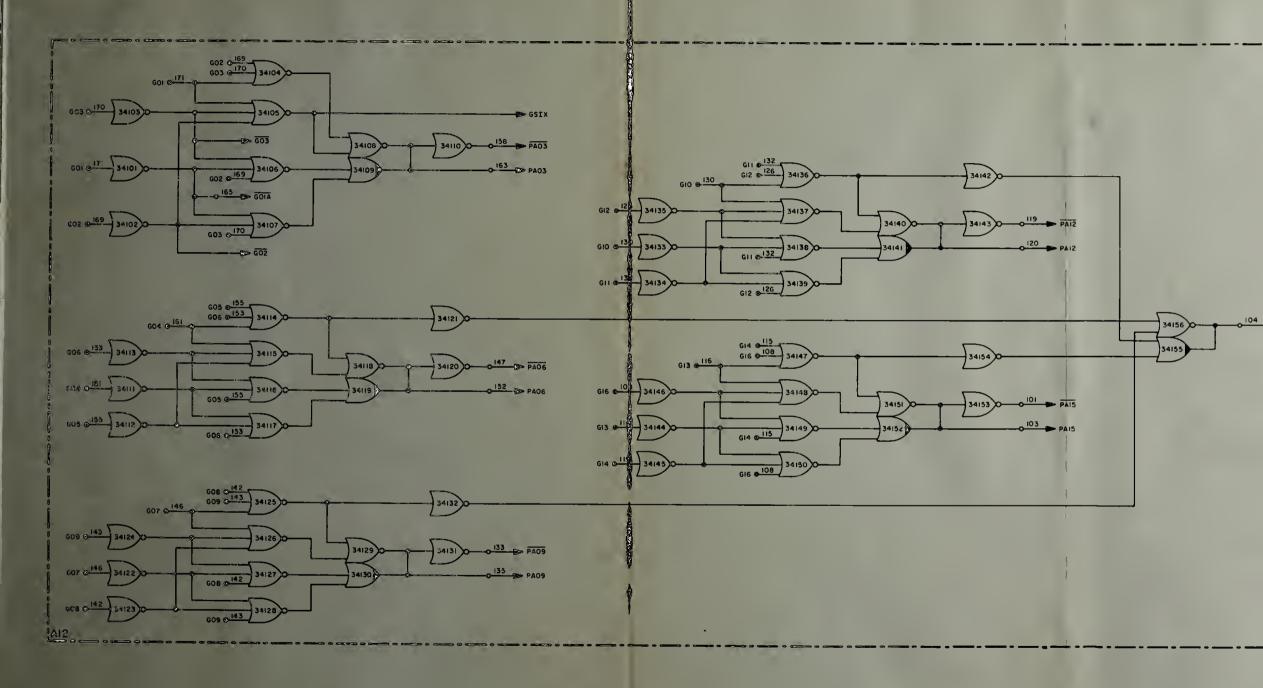

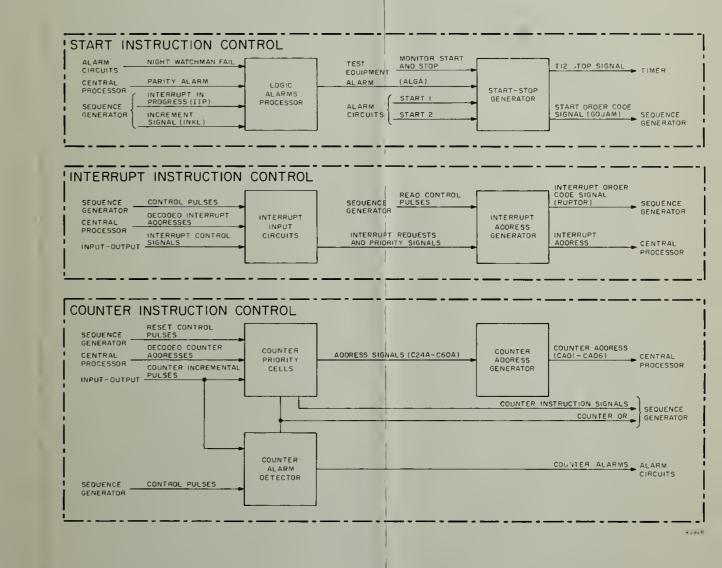

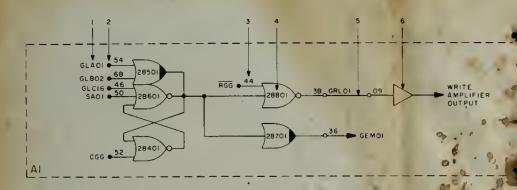

4-5. 4.9 <u>Counter and Peripheral Instruction Control</u>. The counter and peripheral instruction control (figure 4-133) is regulated by signals from the priority control and peripheral equipment. The signals supplied by the priority control are the start order code signal (GOJAM), the counter OR signal (CTROR), and the various counter increment signals that request a particular counter instruction. The prime function of signal GOJAM is to take top priority by inhibiting and resetting many circuits in the counter and peripheral instruction control. Signal CTROR is used to produce the increment signal (INKL) in addition to various strobe signals. The signals supplied by the peripheral equipment are MREAD, MLOAD, MRDCH, MLDCH for FETCH, STORE, INOTRD, and INOTLD instructions, respectively. The peripheral equipment also supplies signal MNHNC for inhibiting the counter increment operation. The counter and peripheral instruction control supplies the following subinstruction commands to the control pulse generator:

| (1) STOR | E1 (4) | PCDU  | (7) | SHANC |

|----------|--------|-------|-----|-------|

| (2) PINC | (5)    | MCDU  | (8) | DINC  |

| (3) MINO | C (6)  | SHINC |     |       |

It also supplies the following instruction commands:

| (1) | INKL   | (3) | MONTCH | (5) | FETCH0 |

|-----|--------|-----|--------|-----|--------|

| (2) | STFET1 | (4) | CHINC  |     |        |

The instruction command signal INKL must always be produced before a counter or peripheral instruction can be executed. Signal INKL interrupts the operation of the register SQ control, SQ decoder, and stage decoder so that no instruction or subinstruction command will be produced while the counter or peripheral instruction is being executed. Signal INKL does not destroy the order code in register SQ; it simply delays recognition of the order code until the counter or peripheral instruction has been executed.

A counter or peripheral instruction cannot be executed if a GOJAM condition exists. Signal GOJAM is applied to the set side of the GNHNC flip-flop. If time pulse T01 is not present, signal GOJAM will set the GNHNC flip-flop. The flip-flop will remain set until the following T01 time pulse. Signal B controls the time at which a counter or peripheral instruction can be executed. Signal B is present at time pulse T12 provided signal NISQL is also present. Signal NISQL is produced by the register SQ control. This signal is present only at the end of each instruction; its absence at time pulse T12 prevents a counter or peripheral instruction from being executed between subinstructions. Signal B is produced during the last quarter interval of time pulse T12 as indicated by the presence of signal PHS4.

When a counter instruction is to be executed, signal CTROR from the priority control is present. The presence of signals B and CTROR will allow a counter increment to occur provided the operation is not manually inhibited by signal MNHNC from the peripheral equipment or by signal A. Signal A is produced whenever a peripheral instruction is to be executed and gives the peripheral instructions priority over the counter instructions. If the preceding conditions are met, flip-flop C will set. The set input to

flip-flop C can be overridden by signal GOJAM if both the set and reset inputs occur at the same time. Signal C will be present for almost a full MCT, starting during the last quarter interval of time pulse T12 and remaining until the third quarter interval of the following T12 pulse. The third quarter reset interval is controlled by signal PHS3. If additional counter incrementing is to take place, the C flip-flop will remain set. It can be reset any time by signal GOJAM or at time pulse T12 if both a counter and a peripheral instruction are requested at the same time. When this happens, signal A in addition to signals T12 and PHS3 will reset the C flip-flop. At the end of all counter incrementing, the absence of signal CTROR will cause the flip-flop to reset at time pulse T12.