TRAINING SECTION

APOLLO FIELD OPERATIONS

RAYTHEON COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

### AN AUTO-INSTRUCTIONAL

## TEACHING TEXT

ON

DIGITAL COMPUTER FUNDAMENTALS

Raytheon Company 1963 All rights reserved.

Printed in the United States of America

All rights reserved. This book or any part thereof may not be reproduced in any form without permission of the Company.

# TABLE OF CONTENTS

| INSTRUCTIONS                 |         |

|------------------------------|---------|

| VOLUME I                     | FRAMES  |

| Semiconductor Circuits       | 1 - 197 |

| VOLUME II                    |         |

| Counting Systems             | 1 - 89  |

| VOLUME III                   |         |

| Boolean Algebra              | 1 - 121 |

| VOLUME IV                    |         |

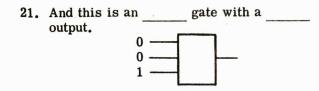

| Digital Techniques and Logic | 1 - 155 |

#### INSTRUCTIONS

The subject of this program is Digital Computer Fundamentals. Knowledge of these fundamentals will provide an understanding of the approach to, and necessity for, the various digital computer techniques and circuits.

The program is presented by auto-instructional techniques called programed learning. Briefly, these techniques present the information in carefully sequenced small steps called <u>frames</u>. With few exceptions, each step, or frame, requires a written response. However, in order to make a correct response you must pay close attention to the frame content.

The information presented in each frame is placed on the right-hand side of the page. The confirmation of your response is on the left-hand side of the page, next to the succeeding frame.

To prevent your accidentally observing the correct response, we have included a removable page-sized frame cover. This cover is placed on the page under the frame you are studying. After writing in, or "constructing" your response, slide the cover down to the succeeding frame. This will expose the confirmation response to the frame you have just completed.

You will not be able to quickly flip through the pages of the course skipping from "high point to high point" as in an ordinary text. Your complete concentration is required. It is to your advantage to take your time, follow the correct sequence (don't skip around), and carefully think out your response before writing it. When tired, take a break. There is no time limit, you set your own pace.

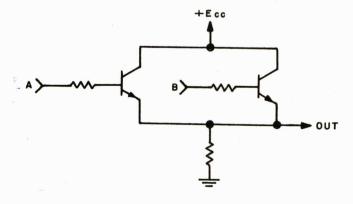

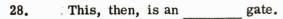

It is imperative that on those frames requiring written responses you write your response in the area provided for it. A response is required for each blank underlined space. Writing the response is important; it has the effect of making you an active participant in the learning process. You will not be asked to create a response; where required, you will be guided by hints, or cues, within the text, or asked for information previously presented.

After writing your response, immediately slide the cover sheet down, or, where necessary turn the page to confirm your response. This immediate confirmation is vital. The immediate knowledge of the correctness of your response is a strong reinforcement of your learning. We have carefully arranged and phrased the frames to allow a minimum of wrong responses. Should you make a wrong response, return to the frame and cross out your answer, and after re-reading the information presented, write in the correct response.

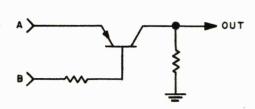

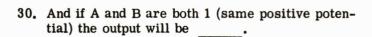

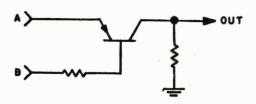

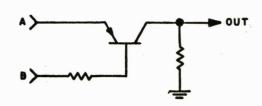

There is no doubt about the effectiveness of programed learning; it has been proven. Follow instructions and you will learn more in less time, and learn it better than you would learn by conventional training methods.

Remove your cover sheet, place it under the next frame and use as previously directed.

|      |                                                    | i.   | The following introductory material is presented in the same form as the text. To answer one of the most common questions, and possibly one you are asking yourself, this is not a test, it is a text! Although presented in a different form this information is still a book. |

|------|----------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i.   | text book                                          | ii.  | This text differs from the normal text in that it uses an auto-instructional approach, also called programed learning. The subject matter content is carefully sequenced, giving it another name, a Program.                                                                    |

|      |                                                    |      | This textbook can also be called a                                                                                                                                                                                                                                              |

|      |                                                    |      | T.                                                                                                                                                                                                                                                                              |

| ii.  | Program                                            | iii. | Programed learning presents the information in small steps called "frames." This small step you are now reading is a                                                                                                                                                            |

| iii. | frame                                              | iv.  | Have you noticed that you cannot skip right through? You must take each frame in sequence, read it carefully and then you participate by your response in the blank space.                                                                                                      |

|      |                                                    |      |                                                                                                                                                                                                                                                                                 |

| iv.  | writing or placing or constructing (or equivalent) | v.   | After having written your response you must immediately move the cover sheet down, or turn the page, to confirm your response. If your response is not correct, cross it out. Re-read the frame and then write in the correct.                                                  |

| v.   | response                                           | vi.  | If the blank space occurs within a sentence, do not write your response until you have the complete sentence.                                                                                                                                                                   |

| vi.  | read<br>(or equivalent)                            | vii. | There will also be frames in which your response will be to write or draw a correct version of the subject matter. Be sure to draw these on the page, or an accompanying sheet of paper, allowing you to check your                                                             |

|      |                                                    |      |                                                                                                                                                                                                                                                                                 |

|      |                                                    |      | •                                                                                                                                                                                                                                                                               |

vii. response

viii. You will also find occasional information frames whose contents are presented solely for information - no response of any kind is required. In this case you will be told to "proceed to the next frame." What you are now reading is an example of an informational frame.

Now that you have the idea, start the program.

# VOLUME I SEMICONDUCTOR CIRCUITS

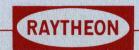

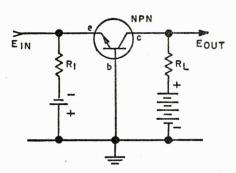

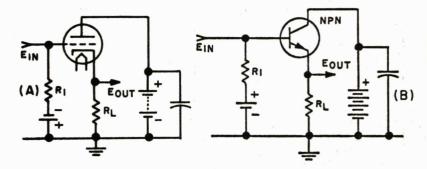

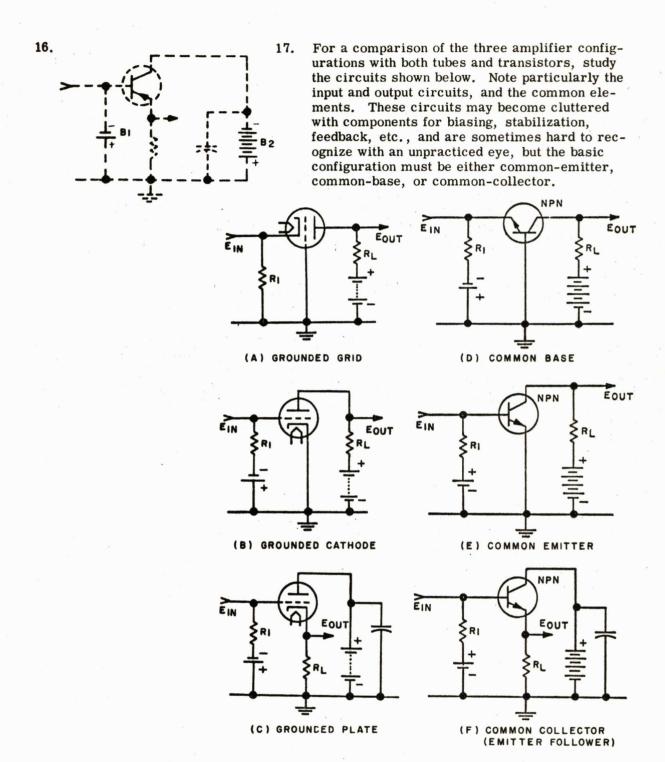

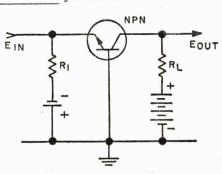

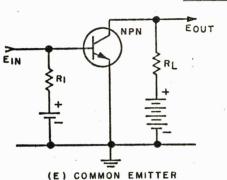

1. Tube amplifiers have three general configurations shown in illustrations A, B, and C below. They are (A) the grounded-grid, (B) the grounded-cathode (the most common), and (C) the grounded-plate or cathode follower. Note that "grounded" refers to signal ground, not necessarily DC ground. In transistor amplifiers we again have three configurations, each one equivalent to one of the tube configurations. However, with transistors we use the term "common" instead of "grounded."

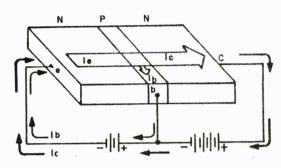

(Proceed to next frame)

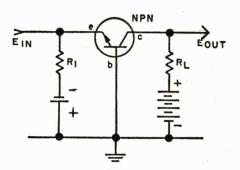

2. "Common refers to the transistor element which is common to both the input and the output circuits. In this basic amplifier the input signal is applied between the emitter and the of the transistor.

2. base

3. The output is taken across the collector and the of the transistor.

3. base

4. Since the base is common to both the input and the output circuits, we call this a amplifier.

4. common-base

5. common-base

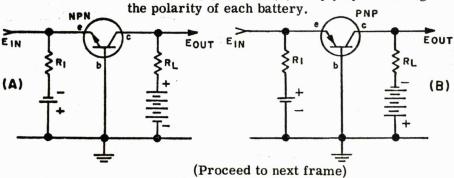

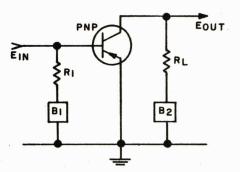

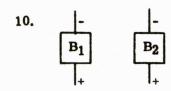

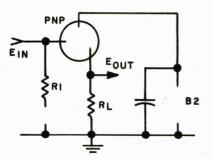

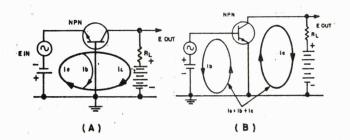

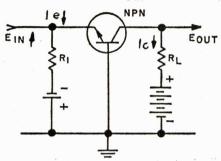

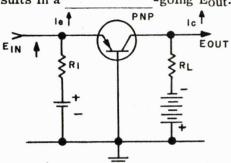

6. In the common-base, and the other two amplifier configurations which follow, we can change from NPN (A) to PNP (B) simply by reversing the polarity of each battery

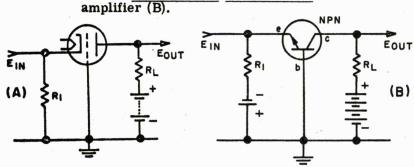

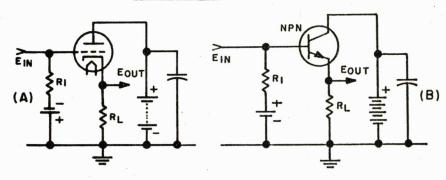

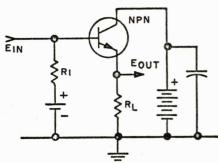

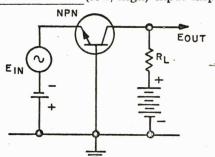

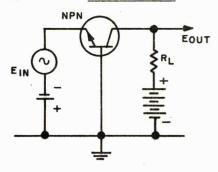

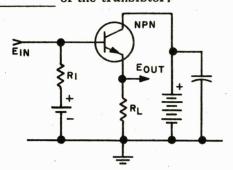

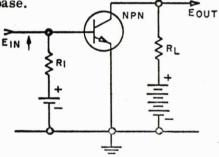

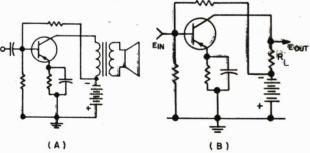

7. Here we have the popular grounded-cathode amplifier (A) and its transistor equivalent (B). Note that the transistor's input is between its and its

- 7. base -- emitter (or vice versa)

- 8. And the output is taken across the and the of the transistor.

- 8. collector -- emitter (or vice versa)

- 9. Since the emitter is common to both the input and output circuits, we call this a \_\_\_\_\_\_ amplifier.

- 9. common-emitter

- 10. On the circuit shown below, indicate the proper battery polarities for a common-emitter PNP amplifier.

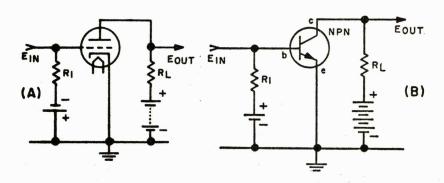

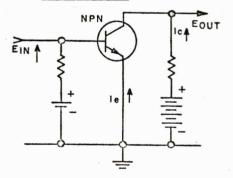

11. Lastly we have the grounded-plate amplifier (A), more commonly called the cathode follower, and the equivalent transistor circuit (B). It takes a close look and a little thought to realize that the input signal is applied between the base and \_\_\_\_\_\_ of the transistor.

11. collector

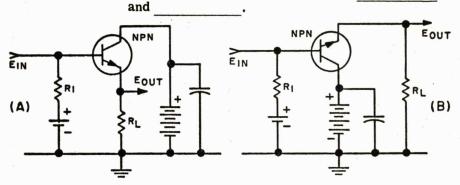

12. Compare circuits (A) and (B) shown below.Note that they are exactly the same and that the collector is at signal ground. However,(B) shows more clearly that the input signal is applied between the transistor's

12. base -- collector (or vice versa)

13. Now it is easy to see that the output signal is taken between the \_\_\_\_\_ and \_\_\_\_

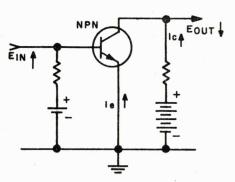

- 13. emitter -- collector (or vice versa)

- 14. So we can call this a common-amplifier.

14. collector

15. Just as the tube version (A) is usually called a cathode follower, we often call the common-collector amplifier (B) an \_\_\_\_\_ follower.

15. emitter

16. Complete the circuit shown below for a PNP emitter follower.

(Proceed to next frame)

- 18. emitter-base (or vice versa)

- 19. The emitter-base junction, remember, is (forward/reverse) biased.

19. forward

20. Forward bias encourages high conduction across a junction. Therefore the input source sees a (low/high) input impedance.

20. low

- 21. base-collector (or vice versa)

- 22. The base-collector junction is always biased in amplifiers.

22. reverse

23. Since the reverse bias discourages conduction across the base-collector junction the output circuit appears as a impedance.

23. high

24. So we see that the common-base amplifier has a \_\_\_\_\_ input impedance and a \_\_\_\_\_ output impedance.

24. low -- high

25. With a low input impedance  $(Z_{in})$  and a high output impedance  $(Z_{out})$ , we can say that the common-base amplifier has an impedance gain. Typical values are  $30 \, \Omega - 150 \, \Omega$  for  $Z_{in}$  and 300 K - 500 K for  $Z_{out}$ , giving an of several thousand.

- 25. impedance gain

- 26. Let's start a chart showing the characteristics of our three amplifier configurations. We will add to this chart as we uncover more information.

**COMMON-BASE**

COMMON-EMITTER

COMMON-COLLECTOR

Z<sub>in</sub> Low 30Ω- 150Ω Z<sub>out</sub> High 300K - 500K Z<sub>gain</sub> High n x 1000

27. Now for the common-emitter amplifier.

As with the common-base the input signal is applied across the forward biased emitter-base junction. Therefore we expect a Zin.

- 27. low

- 28. base

- 28. The typical values of common-emitter  $Z_{in}$  of  $500\Omega$   $1500\Omega$  are not nearly so low as the  $30\Omega$   $150\Omega$  of the common-amplifier. There is another factor which we will now consider.

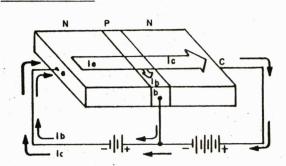

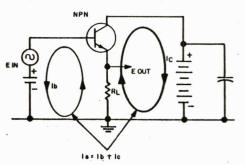

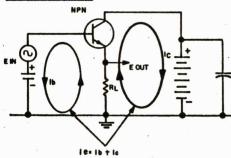

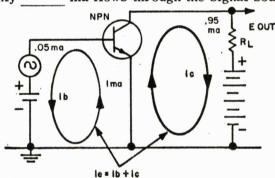

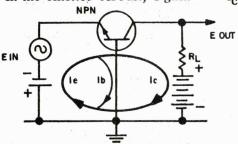

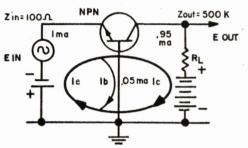

- 29. Current flows in a transistor as shown below. That is, a heavy current flows from emitter to collector through the base. The current flow in the base lead is very

- 29. small, light, low, etc.

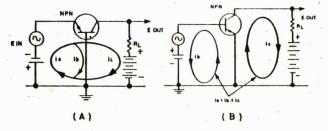

- 30. Here, current flow is shown schematically for common-base (A) and common-emitter (B).

Note that in the common-base (A) the signal source must carry a current, while in the common-emitter (B) the signal source carries only a current.

- 30. large, heavy, etc. -- small, light, etc.

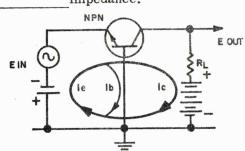

- 31. With a large current flowing in the input circuit of the common-base, the source "sees" a impedance.

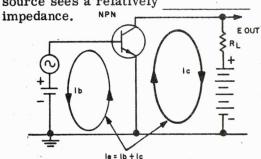

32. On the other hand, with only a small current in the input circuit of the common-emitter, the source sees a relatively

33. Thus we see that, although both amplifiers have their input circuits across forward biased junctions, the heavy current in the input circuit of the common-base (A) leads to a much impedance than the light current in the input circuit of the common-emitter (B).

34. Now let's see what the output impedance looks like in the common-emitter amplifier. We said previously that the output signal was taken between the transistor's \_\_\_\_\_ and its

31. low

32. high

33. lower

- 34. collector -- emitter (or vice versa)

- 35. But between the emitter and the collector we have both the reverse biased base-collector junction and the base junction.

35, forward

36. The reverse biased base-collector junction gives a output impedance, as in the common-base amplifier.

36. high

37. However, in the common-emitter amplifier, the forward biased emitter-base junction is in series opposition with the reverse biased base-collector junction. Therefore, the output impedance is considerably \_\_\_\_\_ (raised/lowered).

37. lowered

38. So while the common-base has a typical output impedance of 300K - 500K, the common-emitter's output impedance is in the order of 30K - 50K.

(Proceed to next frame)

39. With a  $Z_{in}$  of 1000  $\Omega$  and a  $Z_{out}$  of 40K, for example, the common-emitter amplifier will have an impedance gain of about .

|                                                          | CON                 | MMON-BASE                            | CON | MON- | EMI | TTER                | COMMON-COLLECTOR |

|----------------------------------------------------------|---------------------|--------------------------------------|-----|------|-----|---------------------|------------------|

| Z <sub>in</sub><br>Z <sub>out</sub><br>Z <sub>gain</sub> | Low<br>High<br>High | 30Ω- 150Ω<br>300K - 500K<br>n x 1000 |     |      | -   | 1500 Ω<br>50K<br>10 |                  |

| 4 | 0 |

|---|---|

|   | 4 |

40. Now for the common-collector amplifier, or emitter follower. We have shown that its input is applied between the and the

- 40. base -- collector (or vice versa)

- 41. The base-collector junction, as in all amplifiers, is \_\_\_\_\_ biased.

41. reverse

42. With the signal source looking into a reverse biased junction we can expect a input impedance.

42. high

43. Also, the signal source is in a (low, high) current path.

43. low

44. With a low current input circuit and a reverse biased input junction, the input impedance will be very \_\_\_\_\_.

44. high

45. Indeed, Z<sub>in</sub> for the common-collector amplifier is typically 20K - 500K or more as compared with about 100 ∩ for the common-base and 1000 ∩ for the common-emitter.

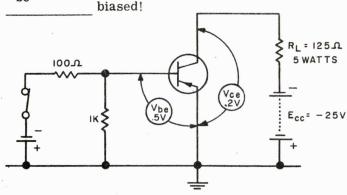

46. The output of the common-collector amplifier is taken from between the \_\_\_\_\_ and the of the transistor.

- 46. collector -- emitter (or vice versa)

- 47. With the collector at signal ground, we are not concerned with the \_\_\_\_\_\_ biased base-collector junction.

47. reverse

48. The output is taken across the emitter load resistor. Since the full current of the transistor must pass through this resistor we have a output impedance.

48. low

49. With a high  $Z_{in}$  of 20K - 500K and a low  $Z_{out}$  of  $50\Omega$  -  $1000\Omega$ , the common-collector amplifier has a fractional Z gain.

Take a few seconds now to compare the impedance characteristics of our three amplifier configurations on the chart below.

|                                                          | COMMON-BASE                                                 | COMMON-EMITTER                                                                                 | COMMON-COLLECTOR                                 |

|----------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Z <sub>in</sub><br>Z <sub>out</sub><br>Z <sub>gain</sub> | Lowest 30A- 150A<br>Highest 300K - 500K<br>Highest n x 1000 | Low 500 \( \text{\Pi} - 1500 \( \text{\Pi} \)  High 30 \( \text{K} - 50 \( \text{K} \)  n x 10 | Highest 20K - 500K<br>Lowest 50 1000 Less than 1 |

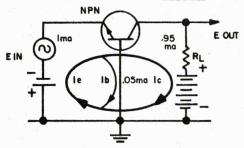

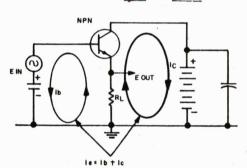

50. Now let's take a closer look at the current flow in our three amplifier configurations. As illustrated here,  $I_e = \_\_\_+ \_\_\_$ .

50.  $I_e = \underline{I_b} + \underline{I_c}$

53.

19

51. Generally  $I_{C}$  = 92% to 98% of  $I_{e}$  and  $I_{b}$  = 2% to 8% of  $I_{e}$ . In our examples we will assume that  $I_{C}$  = 95%  $I_{e}$  and  $I_{b}$  = 5%  $I_{e}$ .

(Proceed to next frame)

52. Here we have the common-emitter circuit with static element currents indicated.

Note that for a current of .95 ma through R<sub>L</sub>, only ma flows through the signal source.

- 52. .05 53. That is

- 53. That is,  $I_c$  is  $\frac{.95}{.05} = \underline{\qquad}$  times  $I_b$ .

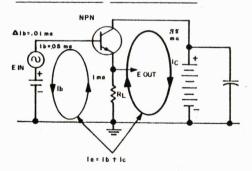

- 54. If the amplifier is operated on the linear part of the transistor's characteristic curves, then a small change in I<sub>b</sub> will cause a corresponding amplified change in I<sub>c</sub>. Since I<sub>c</sub> is 19 x I<sub>b</sub>, the change in I<sub>c</sub> will be 19 x the change in I<sub>b</sub>.

|                                                       |                       | 55. | For example, if $I_b$ increases by .001 ma<br>( $\Delta I_b = .001$ ). $I_c$ will increase by<br>19 x .001 = ma ( $\Delta I_c$ ).                                                                                                                                   |

|-------------------------------------------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.                                                    | .019                  | 56. | Since I <sub>C</sub> changes 19 times as much as I <sub>b</sub> , we can say that we have a current of 19.                                                                                                                                                          |

| 66.                                                   | gain                  | 57. | In mathematical terms, for common-emitter: current gain = $\Delta  I_c / \Delta  I_b$ . (The symbol $\Delta$ is the Greek letter delta. In mathematics it mean "change in.") Using the same figures: current gain = $\Delta  I_c / \Delta  I_b = .019 / .001 = \$ . |

| 57.                                                   | 19                    | 58. | In any configuration, the relation $\DeltaI_{c}/\DeltaI_{b}$ is known by the Greek letter $\beta$ (beta) and is a characteristic of a given type of transistor, just as $\mu = \Deltae_{b}/\Deltae_{c}$ is a characteristic of a given type vacuum tube.            |

|                                                       | *                     |     | (Proceed to next frame)                                                                                                                                                                                                                                             |

|                                                       |                       | 59. | We said that $\beta = \Delta I_c/\Delta I_b$ is a characteristic of a given type of transistor. Also, in the common-emitter configuration, $\Delta I_c/\Delta I_b$ = currengain. Therefore, in the common-emitter configuration, $\beta = \underline{\hspace{1cm}}$ |

| 59.                                                   | current gain          | 60. | Typical values of common-emitter current gain range from 25 to 50. So we can also say that $\beta$ for typical junction transistors ranges from to                                                                                                                  |

|                                                       | COMMON-BASE           | COI | MMON-EMITTER COMMON-COLLECTOR                                                                                                                                                                                                                                       |

| Z <sub>in</sub><br>Z <sub>ou</sub><br>Z <sub>ga</sub> | t Highest 300K - 500K |     |                                                                                                                                                                                                                                                                     |

| Iga                                                   | in                    | β   | $= \Delta I_{c}/\Delta I_{b},$ 5 - 50                                                                                                                                                                                                                               |

60. 25 -- 50

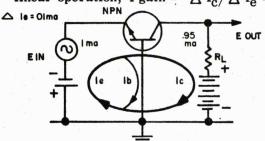

61. As we can see in this diagram,  $\beta = \Delta I_c/\Delta I_b$  does not give us current gain (I gain) for the common-base configuration. Since the signal source is in the emitter circuit, I gain =  $\Delta I_c/\Delta$ .

- 61. I gain =  $\triangle I_c/\triangle \underline{I_e}$

- 62. However, Ic is only about \_\_\_\_\_% of Ie.

62.  $I_c = 95\% I_e$

63. With the figures given in the diagram, assuming linear operation, I gain =  $\Delta I_c/\Delta I_e$  = \_\_\_\_.

63. .95

64. The relation  $\Delta$   $I_c/\Delta$   $I_e$  for any configuration is known by the Greek letter  $\alpha$  (alpha). Like  $\beta$ ,  $\alpha$  is a characteristic of a given type transistor. In the common-base configuration  $\alpha = \Delta I_c/\Delta I_e$  is equal to \_\_\_\_\_

|                                                                                       | COMMON-BASE                                                                            | COMMON-EMITTER                              | COMMON-COLLECTOR                                                            |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------|

| $egin{array}{l} \mathbf{Z_{in}} \\ \mathbf{Z_{out}} \\ \mathbf{Z_{gain}} \end{array}$ | Lowest $30\Omega - 150\Omega$<br>Highest $300K - 500K$<br>Highest $n \times 1000$      |                                             | Highest $20K$ - $500K$<br>Lowest $50\Omega$ - $1000\Omega$<br>Less than $1$ |

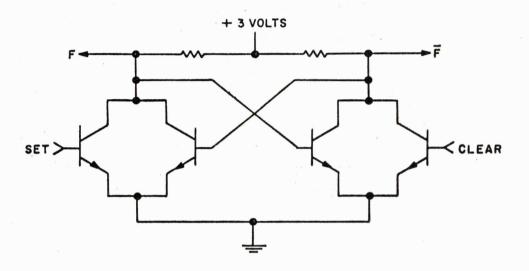

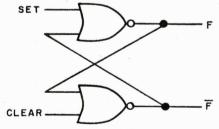

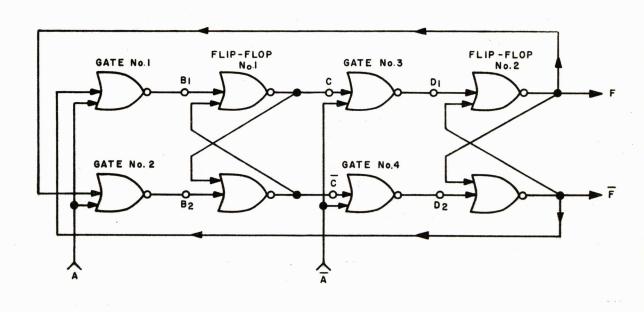

| Igain                                                                                 | $\mathbf{Z} = \Delta \mathbf{I}_{\mathbf{C}} / \Delta \mathbf{I}_{\mathbf{e}},$ $9298$ | $\beta_{25-50} = \Delta I_{c}/\Delta I_{b}$ |                                                                             |

64. current gain

65. If the common-base configuration has a current gain of less than 1, what good is it? Remember that the common-base has an input impedance in the neighborhood of 100 ohms and an output impedance of 500K or so.

(Proceed to next frame)

66. We can see that a  $\triangle$   $I_e$  of .1 ma requires that the signal source provides an  $E_{in}$  of  $\triangle$   $I_e$  x  $Z_{in}$  = .1 ma x 100 ohms = volt.

67. Since  $I_c$  = .95  $I_e$  and  $\Delta I_e$  = .1 ma,  $\Delta I_c$  = .95 x .1 ma = .095 ma in linear operation. But, this .095 ma is in a 500K circuit. Therefore  $E_{out}$  =  $\Delta I_c$  x  $Z_{out}$  is in the neighborhood of .095 ma x 500K = \_\_\_\_\_\_ volts.

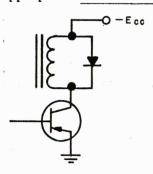

68. With an  $E_{in}$  of .01 volt and an  $E_{out}$  of 47.5 volts, this common-base amplifier has a tremendous of 47.5/.01 or 4750.

69. Since we have ignored various losses, impedance mismatch, and other factors, we must take these figures with a grain of salt. Nevertheless, they serve to show that the common-base amplifier gives high voltage gain inspite of a current gain of less than one. Realistic values of Egain range from 300 to 1500.

(Proceed to next frame)

- 70. We can also say that  $E_{gain} = I_{gain} \times Z_{gain}$  (losses, etc.). In the case above, with  $Z_{in}$  =  $100 \Omega$  and  $Z_{out} = 500K$ ,  $E_{gain}$  = .95 x 500000/100 = \_\_\_\_\_ (losses etc.).

- 71. In the common-emitter amplifier we have both  $I_{gain}$  and  $Z_{gain}$ , but the  $Z_{gain}$  is much than in the common-base.

66. .01

67. 47.5

68. voltage gain

70. 4750

- 71. lower, less etc.

- 72. With typical values,  $E_{gain} = I_{gain} \times Z_{gain}$  losses etc. = 40 x 40 losses, etc. = 1600 losses etc. Typical values for commonemitter  $E_{gain}$  are 200 1000. This is a little than for the common-base.

|                                                          | COMMON-BASE                                          | COMMON-EMITTER                                                                                                                                                     | COMMON-COLLECTOR                                                          |

|----------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Z <sub>in</sub><br>Z <sub>out</sub><br>Z <sub>gain</sub> | $\begin{array}{llllllllllllllllllllllllllllllllllll$ | $\begin{array}{cccc} \text{Low} & 500\Omega & \text{-} & 1500\Omega \\ \text{High} & 30\text{K} & \text{-} & 50\text{K} \\ & \text{n} & \text{x} & 10 \end{array}$ | Highest $20K$ - $500K$<br>Lowest $50\Omega$ - $1000\Omega$<br>Less than 1 |

| Igain                                                    | $4 = \frac{\Delta I_{c}/\Delta I_{e}}{.9298}$        | $m{\beta} = \Delta I_{c}/\Delta I_{b},$ 25 - 50                                                                                                                    |                                                                           |

| $E_{gain}$                                               | 300 - 1500                                           | 200 - 1000                                                                                                                                                         |                                                                           |

- 72. less, lower, etc.

- 73. With your present knowledge of transistor amplifiers you should be able to deduce that current gain for the common-collector amplifier is given by the ratio  $\triangle$  I  $/\triangle$  I

- 73.  $I_{gain} = \triangle I_{\underline{e}} / \triangle I_{\underline{b}}$

- 74. Using our same values of static element current in linear operation, we see that  $I_{gain} = \Delta I_e/\Delta I_b = I_e/I_b = 1/.05 = 20$ . Typical values range from 25 to 50.  $I_{gain}$  for the common-collector is practically the same as for the

- 74. common-emitter

- 75. Although the common-collector has a good current gain, it has an impedance gain of much less than one. The net result is that, like the cathode follower, the emitter follower has a voltage gain of less than one.

|                                                          | COMMON-BASE                                     | COMMON-EMITTER                                                                             | COMMON-COLLECTOR                                                           |

|----------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Z <sub>in</sub><br>Z <sub>out</sub><br>Z <sub>gain</sub> |                                                 | 50 \( \text{Low} \) 500 \( \text{L} - 1500 \cdot \) 00K High 30K - 50K \( \text{n} \) x 10 | Highest $20K - 500K$<br>Lowest $50\Omega - 1000\Omega$<br>Less than 1      |

| Igain                                                    | $\alpha = \Delta I_{c} / \Delta I_{e},$ $.9298$ | $\beta = \Delta I_{c} / \Delta I_{b},$ 25 - 50                                             | $\begin{array}{c} \Delta I_{\mathrm{e}}/\Delta I_{\mathrm{b}}, \\ 25$ - 50 |

| Egain                                                    | 300 - 1500                                      | 200 - 1000                                                                                 | Less than 1                                                                |

(Proceed to next frame)

76. What about phase inversion in transistor amplifiers? Well, let's look at the NPN commonbase first. The emitter is forward biased with a negative potential. So a positive-going Ein will cause a/an (increase/decrease) in the forward bias.

77. decrease 77. The decrease in forward bias in turn causes a/an \_\_\_\_\_ (increase/decrease) in  $I_e$ .

77. decrease 78. The decrease in  $I_e$  means we have a/an \_\_\_\_\_ in  $I_e$ .

78. decrease

79. The decrease in  $I_c$  causes a decrease in the IR drop across  $R_L$  resulting in a (positive/negative)-going  $E_{out}$ .

79. positive

80. Therefore, in the common-base amplifier, we (do/do not) have phase inversion.

80. do not

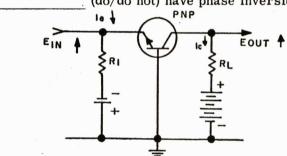

81. In a PNP common-base amplifier a positive-going  $E_{in}$  will increase the positive forward bias, and thereby \_\_\_\_\_  $I_e$ .

81. increase

82. The resulting increase  $\overline{\ln} I_C$  causes a/an in the IR drop across  $R_L$ .

82. increase

83. Since the collector is reverse biased with a negative potential, the increased IR drop across R<sub>L</sub> results in a -going E<sub>out</sub>.

83. positive

84. So we see again that, although they operate differently in some respects, the PNP and NPN versions of a given amplifier produce the same results, in this case absence of phase inversion. You may remember that the tube counterpart, the grounded-grid, also has no phase inversion.

(Proceed to next frame)

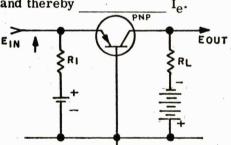

85. In the NPN common-emitter amplifier a positivegoing Ein the positive forward bias at the base.

85. increases

86. The increased forward bias causes  $I_e$ , and therefore  $I_c$ , to \_\_\_\_\_.

86. increase

87. Increased  $I_c$  and the resulting IR drop across  $R_L$  cause a \_\_\_\_\_-going  $E_{out}$ .

87. negative

88. With a negative-going output from a positive-going input, it is obvious that the common-emitter (does/does not) give phase inversion.

88. does

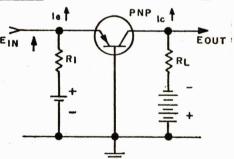

89. In the NPN common-collector (or emitter follower) amplifier, a positive-going  $E_{in}$  increases the forward bias, causing  $I_e$  and the IR drop across  $R_L$  to \_\_\_\_\_.

89. increase

90. positive

91. So we can conclude that, like the cathode follower, the emitter follower \_\_\_\_\_\_ (does/does not) give phase inversion.

|                                                                                       | COMMON-BASE                                                    | COMMON-EMITTER                                                        | COMMON-COLLECTOR                                                                |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------|

| $egin{array}{c} \mathbf{Z_{in}} \\ \mathbf{Z_{out}} \\ \mathbf{Z_{gain}} \end{array}$ | Lowest 30Ω - 150Ω<br>Highest 300K - 500K<br>Highest n x 1000   | Low 500 \( \text{Low} - 1500 \( \text{L} \)  High 30 K - 50 K  n x 10 | Highest 20K - 500K<br>Lowest 50 \( \Omega \) - 1000 \( \Omega \)<br>Less than 1 |

| Igain                                                                                 | $ \alpha = \Delta I_{\text{C}} / \Delta I_{\text{e}}, $ .92.98 | $\beta = \Delta I_{c} / \Delta I_{b},$ 25 - 50                        | $\begin{array}{ccc} \Delta I_{e}/\Delta I_{b}, \\ 25-50 \end{array}$            |

| Egain                                                                                 | 300 - 1500                                                     | 200 - 1000                                                            | Less than 1                                                                     |

| Inversion                                                                             | No                                                             | Yes                                                                   | No                                                                              |

91. does not

92. Thus far, for the sake of simplicity, our examples of transistor circuits have used separate batteries for forward and reverse bias. In typical applications, values of reverse bias fall in the range of 6 to 60 volts while forward bias is only a few tenths of a volt. Therefore, we should be able, by use of voltage dividing resistors, to obtain \_\_\_\_\_\_ bias from the \_\_\_\_\_\_ bias battery.

- 92. forward -- reverse

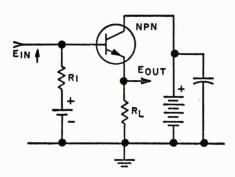

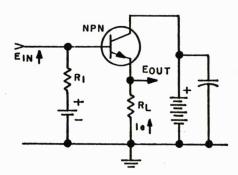

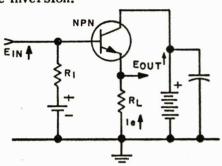

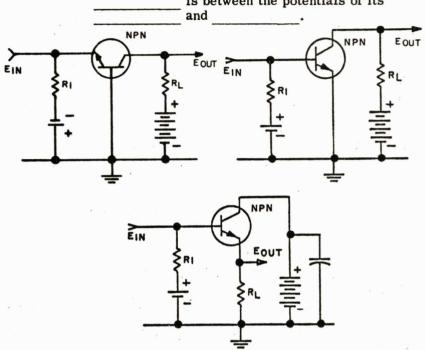

- 93. In the three basic circuits below, note that in each case the potential on the transistor's is between the potentials of its

93. base -- emitter -- collector or base -- collector -- emitter

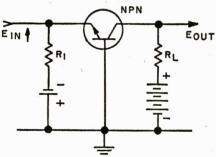

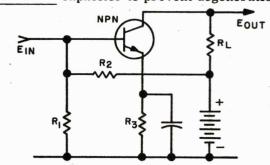

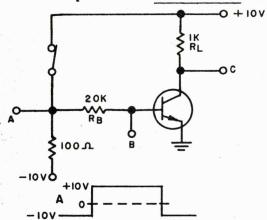

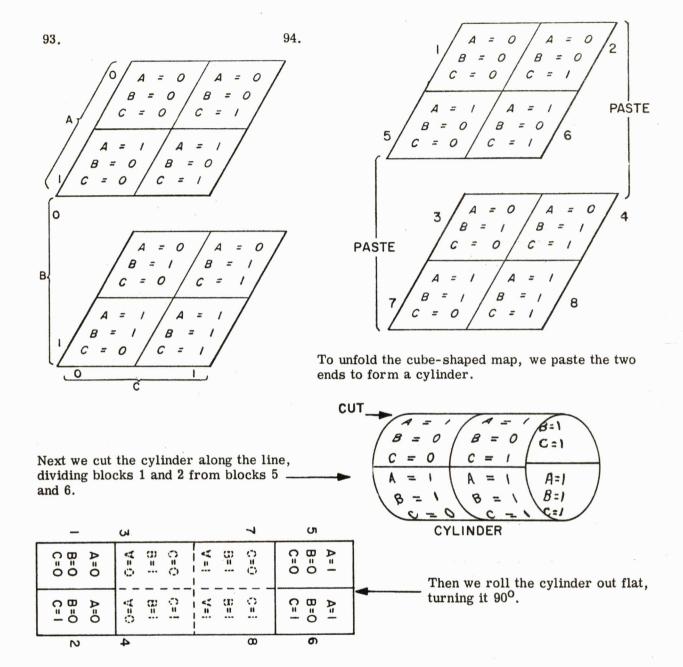

94.

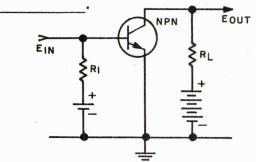

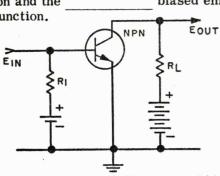

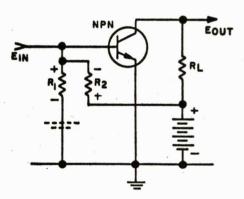

In this common-emitter circuit below the forward bias battery is eliminated and the base is now biased a little positive with respect to the emitter by the voltage divider composed of and

- 94. R<sub>1</sub> -- R<sub>2</sub> (or vice versa)

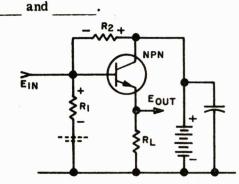

- 95. In this common-base amplifier, the base is biased positive with respect to the emitter by the \_\_\_\_\_ composed of

R2 and R3.

NPN

R3

R1

R3

R1

R2

R3

- 95. voltage divider

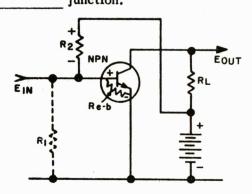

- 96. Again in the common-collector, we derive base bias from the voltage divider consisting of

- 96. R<sub>1</sub> -- R<sub>2</sub> (or vice versa)

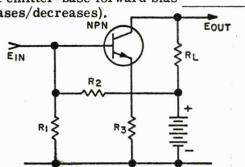

- 97. In some cases it may be possible to replace R<sub>1</sub>, as shown in this common-emitter circuit, with the internal resistance of the junction.

- 97. emitter-base (or vice versa)

- 98. By simply reversing the battery and the emitter arrow, each of the preceding NPN circuits becomes a perfectly valid \_\_\_\_\_ circuit.

| 98.  | PNP                               | 99.  | Transistors are much more sensitive to heat than vacuum tubes. Although there is no heat generating filament, any IR drop across the transistor must be dissipated to prevent temperature buildup. Most of the IR drop in a transistor occurs at the reverse biased, high resistance (relatively), base-collector junction. Therefore, most of the heat (I <sup>2</sup> R) is developed at the junction. |

|------|-----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 99.  | base-collector<br>(or vice versa) | 100. | Without going into detail, we will simply state that a rise in temperature at the base-collector junction leads to an increase in current flow through the transistor. Since the heat generated is equal to I <sup>2</sup> R, the increased current leads to (increased/decreased) heating.                                                                                                              |

| 100. | increased                         | 101. | Again, the increased temperature leads to increased through the transistor.                                                                                                                                                                                                                                                                                                                              |

| 101. | current                           | 102. | We can easily see that this vicious circle of temperature, current, temperature, current quickly leads to the of the transistor.                                                                                                                                                                                                                                                                         |

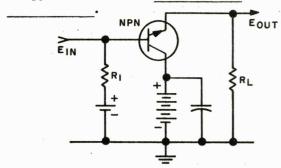

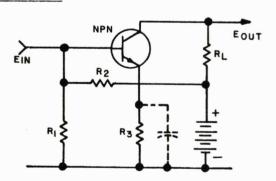

| 102. | burn out, destruction, ruin, etc. | 103. | This thermal-runaway is most serious in the common-emitter configuration. To limit current flow, a limiting resistor (R3 below) is inserted in thelead.                                                                                                                                                                                                                                                  |

|      |                                   |      | NPN EOUT                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |                                   |      | $\begin{array}{c c} R_1 \\ \hline \\ R_3 \\ \hline \\ \hline \\ \hline \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                            |

| 103. | emitter                           | 104. | As emitter current increases, the I <sub>e</sub> x R <sub>3</sub> drop causes the emitter terminal to become more (positive/negative).                                                                                                                                                                                                                                                                   |

104. positive

105. As the emitter terminal becomes more positive, the net emitter-base forward bias (increases/decreases).

105. decreases

106. The decreased forward bias stabilizes the temperature-current relationship by (increasing/decreasing) the emitter current.

106. decreasing

107. As with a cathode bias resistor, the emitter stabilization resistor may be shunted with a capacitor to prevent degeneration.

107. bypass

108. In vacuum tubes we have little trouble matching the high impedance output of one stage to the high impedance grid circuit of the next stage. In transistors, however, we have problems. For example, with common-emitter stages, Zout may be 40K and Zin 1K. One approach, shown below, is to use coupling.

108. transformer

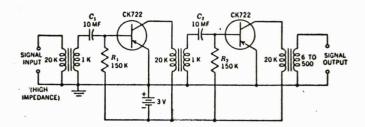

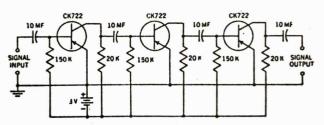

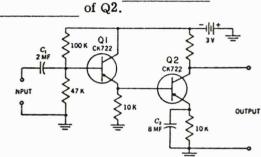

109. But for audio, good transformers are expensive, and cheap transformers give poor frequency response. A second approach, shown here, is to put up with a mismatch and use coupling. Note that an extra stage has been added to make up for the loss in gain.

109. resistance or RC

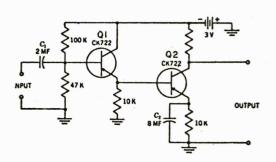

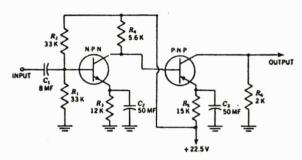

110. Here is a two stage amplifier with high  $Z_{in}$ , high  $Z_{out}$  and matched interstage coupling. (Compare impedances on the chart below.)

Note that the input transistor is connected in the \_\_\_\_\_ configuration while the output stage is a \_\_\_\_\_

|                                                          | COMMON-BASE                                                  | COMMON-EMITTER                                             | COMMON-COLLECTOR                                                          |

|----------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|

| Z <sub>in</sub><br>Z <sub>out</sub><br>Z <sub>gain</sub> | Lowest 30Ω - 150Ω<br>Highest 300K - 500K<br>Highest n x 1000 | Low $500\Omega - 1500\Omega$<br>High $30K - 50K$<br>n x 10 | Highest $20K$ - $500K$<br>Lowest $50\Omega$ - $1000\Omega$<br>Less than 1 |

| Igain                                                    | $\alpha = \Delta I_{c} / \Delta I_{e},$ $.9298$              | $\beta = \Delta I_{c}/\Delta I_{b},$ 25 - 50               | $\Delta_{25}^{I} - 50^{I}_{b}$                                            |

| Egain                                                    | 300 - 1500                                                   | 200 - 1000                                                 | Less than 1                                                               |

| Inversion                                                | No                                                           | Yes                                                        | No                                                                        |

- 110. common-collector -- common-emitter

- 111. Notice also in this circuit that direct coupling is used between the \_\_\_\_\_ of Q1 and the

- 111. emitter -- base

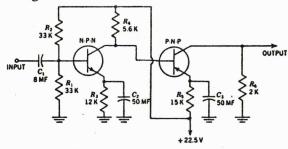

- 112. This direct-coupled circuit has a voltage gain of about 660. It takes advantage of the "complementary symmetry" of NPN and transistors.

112. PNP

113. As with vacuum tube amplifiers, negative feedback can be used to raise the input impedance. In a single stage, leaving the emitter stabilization resistor, R3, unbypassed, provides the required degeneration or

- 113. negative feedback

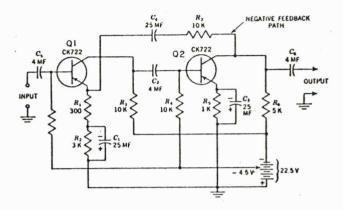

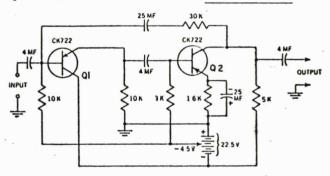

- 114. In this two stage amplifier, we have negative feedback from the collector of transistor Q2 to the emitter of transistor Q1 through the components and .

- 114. R7 -- C4 (or vice versa)

- 115. Note that this feedback is developed across an unbypassed section of the emitter resistance,  $R_{\_}$ , while stabilization is provided by  $R_{\_}$ .

115. R<sub>1</sub> -- R<sub>2</sub>

116. Here we have negative feedback from the collector of Q2 to the base of Q1. Note that Q1 is connected as a common-

116. collector

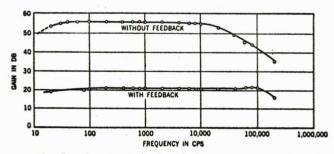

117. Although negative feedback raises the input impedance and flattens the frequency response, as shown here, it also greatly \_\_\_\_\_ the gain.

The effect of negative feedback on the frequency response of the amplifier.

- 117. reduces, lowers, etc.

- 118. Perhaps you have noticed the high values of capacitance used in coupling and bypassing. This is necessary because transistors are current devices, and these capacitors must handle signal currents, rather than signal voltages.

(Proceed to next frame)

- 119. Let us conclude this section on amplifier circuits with a short discussion of power gain  $(P_{gain})$  and power amplifiers. Since P = EI and  $P_{ac} = I^2Z$ , we can also say that  $P_{gain} = E_{gain} \times I_{gain}$  and  $P_{gain} = (I_{gain})^2 \times$ \_\_\_\_\_.

- 120. That is, if an amplifier has a current gain of 10 and a voltage gain of 300, it has a power gain of:

$$P_{gain} = E_{gain} \times I_{gain} = 300 \times 10 =$$

121. Or if we have a current gain of 10 and an impedance gain of 30,  $P_{gain} = (I_{gain})^2 \times Z_{gain} = 10^2 \times 30 =$ \_\_\_\_\_.

120. 3,000

121. 3000

|                                                          | COMMON-BASE                                          | COMMON-EMITTER                                                                                                                                          | COMMON-COLLECTOR                                                          |

|----------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Z <sub>in</sub><br>Z <sub>out</sub><br>Z <sub>gain</sub> | $\begin{array}{llllllllllllllllllllllllllllllllllll$ | $\begin{array}{ccccc} 2 & \text{Low} & 500\Omega & -1500\Omega \\ & \text{High} & 30\text{K} & -50\text{K} \\ & & \text{n} & \text{x} & 10 \end{array}$ | Highest $20K$ - $500K$<br>Lowest $50\Omega$ - $1000\Omega$<br>Less than 1 |

| Igain                                                    | $\alpha = \Delta I_{c}/\Delta I_{e},$<br>.9298       | $\beta = \Delta I_{C} / \Delta I_{b}$ , 25 - 50                                                                                                         | $\Delta I_{\rm e}/\Delta I_{\rm b}, \ 25-50$                              |

| Egain                                                    | 300 - 1500                                           | 200 - 1000                                                                                                                                              | Less than 1                                                               |

| Inversion                                                | No                                                   | Yes                                                                                                                                                     | No                                                                        |

| $P_{gain}$                                               | 100 - 1000<br>20 - 30 db                             | 300 - 10,000<br>25 - 40 db                                                                                                                              | 10 - 100<br>10 - 20 db                                                    |

122. common-emitter

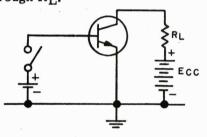

123. Here we have a simple class A audio power amplifier (A). On paper, this circuit appears very similar to the voltage amplifier (B), except that R<sub>L</sub> has been replaced by the output \_\_\_\_\_ and loudspeaker.

123. transformer

124. The power amplifier and voltage amplifier may look alike, but transistor power circuits and the transistors themselves, must be designed to handle larger currents and to dissipate greater amounts of

124. heat

125. Although class A push-pull operation offers the same advantages over single-ended operation for transistors as it does with vacuum tubes (lower distortion, more than two times the power, etc.), push-pull transistor audio power amplifiers are usually operated class .

125. B

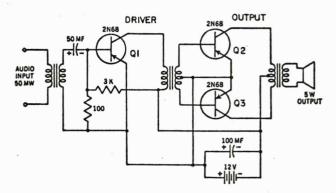

126. The advantage of class B operation is its greater efficiency. In the simplified circuit below, the class B push-pull output stage, Q2 and Q3, draws only 1 ma with no signal input and 550 ma at maximum signal input with 5 watts output to the loudspeaker.

Thus, efficiency = Power Out/Power In = Power Out/(Ein x Iin) = 5 watts/(12V x.55A) = 5 watts/6.6 watts = %

126. 75+

127. By comparison, the class A driver stage, Q1, draws an average current of 100 ma, signal or no signal, and is handling much less audio power. The efficiency of class B means not only lower power consumption, but also less heat buildup within the transistor and more power output from a given transistor type.

(Proceed to next frame)

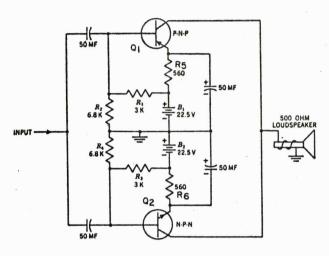

128. This class A push-pull amplifier avoids the need of center tapped input and output transformers by taking advantage of the complementary symmetry of PNP and \_\_\_\_\_ transistors.

128. NPN

129. In this circuit, note that R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, and R<sub>4</sub> provide emitter-base \_\_\_\_\_, while R<sub>5</sub> and R<sub>6</sub> are \_\_\_\_\_ resistors.

129. bias -- stabilizing

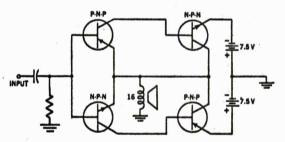

130. Here is a simplified circuit of a class B pushpull, direct coupled amplifier. Note that the output impedance is very \_\_\_\_\_\_ (high/low).

130. low

131. In presenting these various amplifier circuits we have not attempted to give a detailed description of their operation. They have been presented merely to give you an idea of the types of amplifier circuits in which transistors are used.

(Proceed to next frame)

132. So far, our discussion of transistor circuits has been limited to various types of amplifiers with small signal inputs, such as are used in radio receivers. We will now discuss some of the circuits employed in digital equipment.

(Proceed to next frame)

133. In this circuit, with the switch open, the barrier potential within the transistor will cause

(a large/little or no) current to flow through R<sub>L</sub>.

133. little or no

134. With the switch closed, however, a large current will flow through R<sub>L</sub> due to the strong bias on the emitter-base junction.

134. forward

135. To look at it another way, with the switch open and the base floating, the transistor acts as a very resistance.

135. high

136. With the switch closed and the base forward biased, the transistor presents a very resistance.

136. low

137. We refer to the high resistance, esentially nonconducting condition of the transistor as OFF, and the low resistance, conducting condition as

137. ON

138. The OFF resistance of the transistor can be increased to several hundred K ohms by grounding the base instead of leaving it floating. The OFF resistance can be further increased by applying .2 volts or more of bias to the emitter-base junction.

138, reverse

139. In the ON condition, the emitter-collector resistance is reduced to a few ohms by the strong bias at the emitter-base junction.

139, forward

switch or relay from the standpoint of ON and OFF resistance, the transistor can perform the switching operation much more rapidly. For example, switching rates of several million times a second are not uncommon. Even in slow speed applications such as control of lights, small motor, transistorized automobile ignition, etc., transistors give more uniform and reliable performance due to the absence of arcing and contact wear.

(Proceed to next frame)

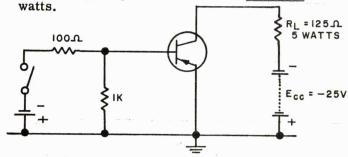

141. Here we have a typical PNP transistor switch. With the large forward bias on the base-emitter junction, conduction is so heavy that  $V_{ce}$  drops to a level below  $V_{be}$ . Since  $V_{ce}$  is less than  $V_{be}$ , the base-collector junction is actually

## TYPICAL VALUES

Ic = 80 µA SWITCH OPEN

Ic = 0.2A SWITCH CLOSED

IC = 0.2A SWITCH CLOSED

I = IOmA = CURRENT THROUGH SWITCH

V<sub>ce</sub>=.2V SWITCH CLOSED V<sub>be</sub>=.5V SWITCH CLOSED

INPUT POWER = 15 MILLIWATTS LOAD POWER = 5 WATTS

141. forward

142. We will not attempt to explain here how V<sub>Ce</sub> can be less than V<sub>be</sub>. However, a transistor operating under these conditons is said to be SATURATED. That is, in saturated operation, the base-collector junction becomes biased.

142. forward

143. The symbol V<sub>Ce</sub> (SAT) is often used to denote the collector-emitter voltage of a transistor in operation.

143. saturated

144. Heating in a transistor switch is quite different than in an ordinary amplifier. Using the circuit below, heating in the OFF conditions is equal to  $V_{Ce} \times I_{C} \cong 25V \times 80 \mu mp \cong$

144. .002

145. In the ON condition heat is equal to  $V_{Ce} \times I_{C} \cong .2V \times .2 \text{ amps } \cong$  watts

TYPICAL VALUES

te . BOHA SWITCH OPEN

16 = 0.2A SWITCH CLOSED

I . IOMA . CURRENT THROUGH SWITCH

V<sub>Ce</sub> = .2V SWITCH CLOSED V<sub>be</sub> = .5V SWITCH CLOSED INPUT POWER = 15 MILLIWATTS

LOAD POWER = 5 WATTS

145. . 04

146. If we calculate heat during the switching operation, we find, for example, that when  $V_{Ce} = 12V$ ,  $I_C = 0.1$  amp. Therefore, heat =  $12V \times .1$  amp = 1.2 watts. If  $V_{Ce} = 6V$  and  $I_C = .15$  amps, heat = 0.9W. Likewise, when  $V_{Ce} = 18V$  and  $I_C = .05$  amps, heat = 0.9W. So we see the heat developed during switching is much than during ON or OFF periods.

146. greater, larger, etc.

147. The switching time is usually extremely short (a few microseconds at most) compared to ON or OFF time. Therefore, the average heat dissipation, for a given maximum I<sub>C</sub> is much in a switching circuit than in an amplifier.

147. less

148. To put it another way, a given transistor can handle much current in a switching circuit than in an amplifier.

148. more

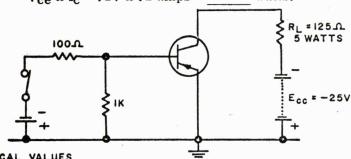

149. When switching inductive loads, the transistor must be protected from destructive high energy transients. This can be done by shunting the load with an appropriate

149. diode

150. square

151. forward

150. Now let's consider the transient response (not to be confused with destructive transients) of a typical transistor switching circuit. When the switch is closed and opened, the resulting waveform at point A is a wave.

151. The waveform at point B, however, does not follow exactly the waveform at point A. When the switch is closed it takes a finite time for the emitter-base capacitance to charge through RB in order to \_\_\_\_\_\_ bias the emitter junction.

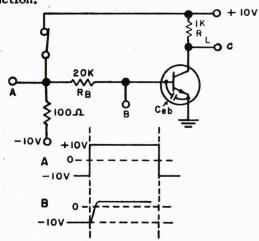

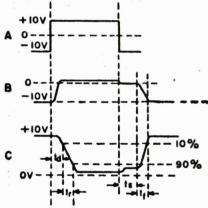

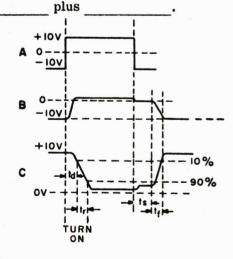

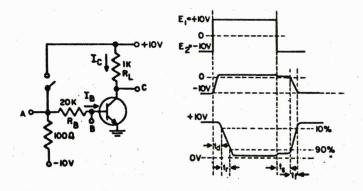

152. The time required for  $I_C$  to rise (voltage at point C to fall) 10% of its ultimate value is called DELAY TIME, abbreviated

153. The time required for the emitter current to diffuse across the base region, and other factors also affect t<sub>d</sub> or

A -10V

B -10V

C +10V

O -10V

RB

O -10V

RB

O -10V

RB

O -10V

RB

O -10V

153. delay time

- 154. Delay time can be reduced by several means, including (increasing/decreasing) the value of  $R_B$  and (increasing/decreasing) the OFF bias voltage.

- 154. decreasing -- decreasing

- 155. The time required for  $I_{c}$  to rise ( $V_{c}$  to fall) from 10% to 90% of its ultimate value is called RISE TIME, abbreviated

155. t<sub>r</sub>

156. The total time from the closing of the switch to 90% of ultimate  $V_{\rm C}$  is referred to as TURN-ON TIME. Turn-on time is equal to

- 156. delay time (or t<sub>d</sub>) -rise time (or t<sub>r</sub>)

(or vice versa)

- 157. Once V<sub>C</sub> reaches the 90% point, the transistor is pretty well into saturation. In saturation, remember, the collector becomes biased.

157. forward

158. The collector now begins emitting carriers due to the bias.

158. forward

159. Some of these carriers, emitted by the \_\_\_\_\_, become stored in the base region and, in some cases, in the collector region.

159. collector

160. When the switch is opened, these carriers must be removed before the emitter-base junction can return to bias.

160. reverse

161. The time required for the stored carriers to dissipate and  $V_{\rm C}$  to drop to the 90% level is the STORAGE TIME, abbreviated

161. ts

162. Finally the voltage at point C rises to the original +10V. The time required to traverse the 90% to 10% region is the FALL TIME, abbreviated

162. t<sub>f</sub>

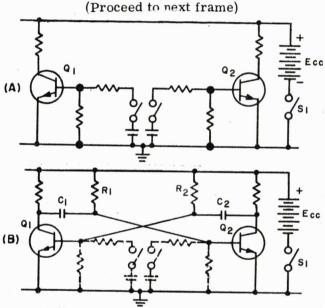

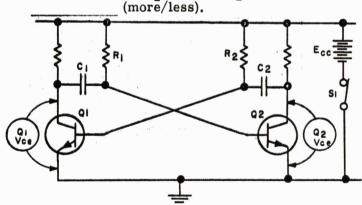

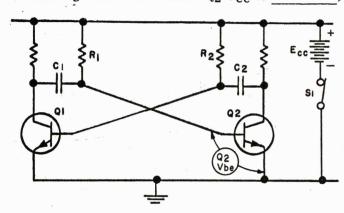

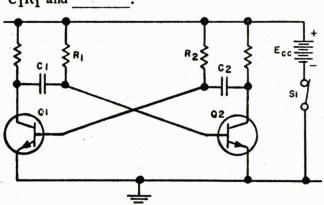

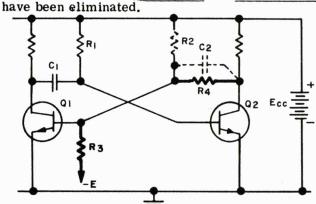

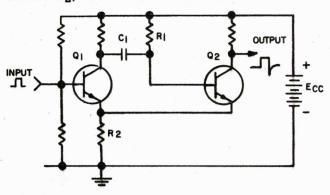

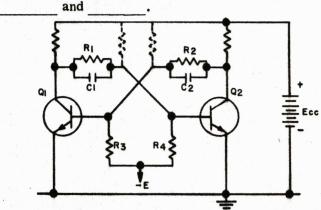

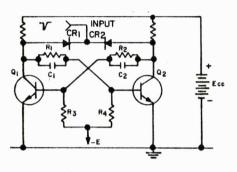

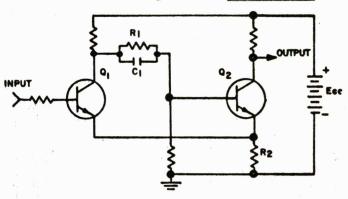

163. In diagram (A) we have two saturated switching circuits placed back to back, or perhaps base to base. By substituting C<sub>1</sub>, C<sub>2</sub>, R<sub>1</sub> and R<sub>2</sub> for the original control components in diagram (B), each transistor now controls the other in an oscillatory fashion. This circuit is one form of multivibrator.

164. When switch  $S_1$  is closed, one transistor, let's say  $Q_1$ , is bound to conduct a little more heavily than the other. Since  $Q_1$  is conducting more heavily, its  $V_{Ce}$  (collector to emitter voltage) is dropping faster than that of  $Q_2$ . This negative going voltage is coupled through  $C_1$  to the base of  $Q_2$ , causing  $Q_2$  to conduct

165. The lowered conduction of  $Q_2$  results in an increase in the  $V_{Ce}$  of  $Q_2$ . This voltage rise is coupled to the base of  $Q_1$ , causing  $Q_1$  to \_\_\_\_\_ (increase, decrease) conduction.

164. less

165. increase

166. This cumulative process, which takes place in a fraction of a microsecond, continues until  $Q_1$  is saturated and  $Q_2$  is cutoff. In this condition  $Q_1$   $V_{Ce}$  is essentially (ground/ $E_{Cc}$ ) and  $Q_2$   $V_{Ce}$  is essentially

166. ground -- Ecc

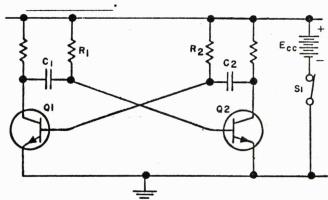

167. With current through the transistors at a steady state, C<sub>1</sub> now starts to charge up through

167. Q1 -- R1 (or vice versa) 168. As C<sub>1</sub> charges, Q<sub>2</sub> V<sub>be</sub> starts to rise and eventually (a few microseconds in slow speed multivibrators) Q<sub>2</sub> comes out of cutoff. The resulting conduction causes Q<sub>2</sub> V<sub>ce</sub> to \_\_\_\_\_

168. decrease, drop, etc.

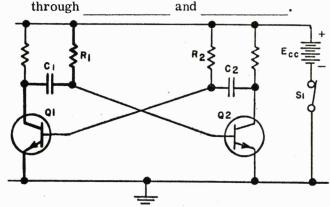

169. This falling voltage is coupled through C<sub>2</sub> to the base of Q<sub>1</sub>, cutting off Q<sub>1</sub> just as Q<sub>1</sub> previously cutoff Q<sub>2</sub>. This process repeats at a rate determined by the time constants of C<sub>1</sub>R<sub>1</sub> and \_\_\_\_\_.

169. C2R2

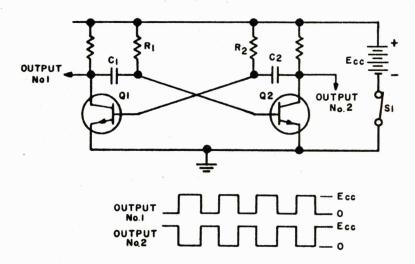

170. Outputs may be taken from the collectors of Q<sub>1</sub> and Q<sub>2</sub>. As shown these two outputs are essentially square waves out of phase with each other.

170. 180

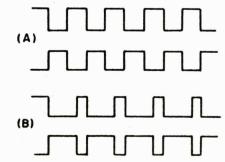

171. If the time constants of C1R1 and C2R2 are equal, the square waves are symmetrical (A).

If, however, the time constants are unequal, square waves result. (B)

- 171. unsymmetrical

- 172. Because it is not stable in either of its switched states, this is called an ASTABLE multivibrator. (A means not.) And since it runs freely without any input pulses it is also called a -running multivibrator.

172. free-running

173. Although it will run free without input pulses, trigger pulses may be applied to either base to synchronize its operation. Thus, a positive pulse applied to a base shortly before the transistor comes out of cut-off, will trigger the transistor into

173. conduction

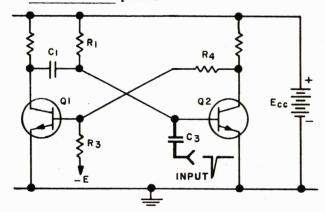

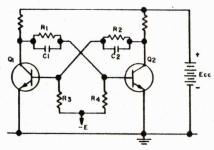

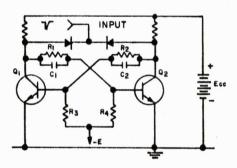

174. Here we have altered the coupling between Q2 collector and Q1 base. When Q1 is ON and Q2 is OFF, the discharging of C1 returns Q2 to conduction as in the free-running multivibrator. But when Q2 is ON and Q1 is OFF Q1 cannot be turned ON because and

174. C2 -- R2

175. Switching states at this point requires a trigger.

This pulse can be applied to Q<sub>2</sub> base via C<sub>3</sub>

as a pulse.

175. negative

176. R4

177. C<sub>1</sub>

176. In the stable state, with  $Q_1$  OFF and  $Q_2$  ON, the negative trigger pulse drives  $Q_2$  base into cut-off. The rising voltage at  $Q_2$  collector is coupled to  $Q_1$  base through

- 177. As Q<sub>1</sub> comes out of cut-off, Q<sub>2</sub> is driven into cut-off by the falling potential at Q<sub>1</sub> collector, which is coupled to Q<sub>2</sub> base through \_\_\_\_\_.

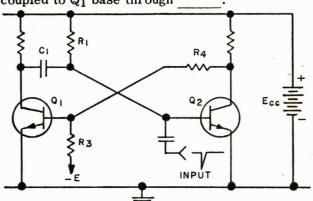

- 178. So we see that this multivibrator has one stable state (Q1 OFF, Q2 ON) and one unstable state (Q1 ON, Q2 OFF). Because it has one stable state, we call this a monostable, or one-shot multivibrator. Square wave outputs can be taken from either collector.

OUTPUT

No.1

(Proceed to next frame)

R<sub>1</sub>

R<sub>2</sub>

OUTPUT

No.2

SI

INPUT

179. Here is an emitter-coupled one-shot multivibrator. In the stable state Q<sub>1</sub> is (ON/OFF) and Q<sub>2</sub> is

179. OFF -- ON

180. The positive pulse turns on Q<sub>1</sub> which in turn cuts off Q<sub>2</sub>. C<sub>1</sub> then discharges to bring Q<sub>2</sub> out of cut-off. When Q<sub>2</sub> starts to conduct and draws current through R<sub>2</sub>, Q<sub>1</sub> becomes biased by the resulting IR drop across R<sub>2</sub>, and returns to the stable state.

180. reverse

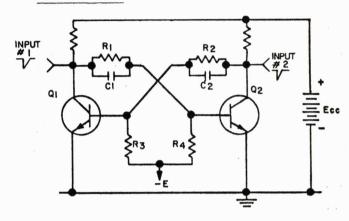

181. This circuit is similar to our astable multivibrator except that: 1)  $R_1$  and  $R_2$  are connected to the collectors  $Q_1$  and  $Q_2$  instead of to  $E_{cc}$ ; and, 2) the bases are returned to -E through

181. R<sub>3</sub> -- R<sub>4</sub> (or vice versa)

182. Since there is no way to discharge C<sub>1</sub> or C<sub>2</sub> towards E<sub>CC</sub> to bring the base of an OFF transistor out of cut-off, this circuit will not change state without the application of external trigger pulses.

(Proceed to next frame)

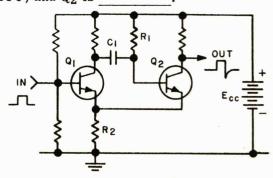

183. Here we see negative pulses applied to the collector of Q<sub>1</sub> and Q<sub>2</sub>. Such a pulse at the collector of an ON transistor is shunted to ground by the low internal resistance and has no effect. At the collector of an OFF transistor, the pulse sees a high shunt resistance and is passed through the capacitor to the of the ON transistor.

183. base

184. The negative pulse at the base of the ON transistor, say  $Q_2$ , cuts that transistor off. The rising voltage at  $Q_2$  collector is then coupled through  $C_2$  to turn  $Q_1$ , thus completing a change of state.

184. ON

185. The astable multivibrator, remember, is not stable in either state; the monostable multivibrator is stable in one state. This multivibrator is called bistable because it is stable in states.

185. 2 or both

186. And because it seems to "flip" states with one pulse and "flop" back at the next pulse, the bistable multivibrator is referred to as a "flip-flop."

(Proceed to next frame)

187. By adding two diodes to this bistable multivibrator, we can use one trigger input point instead of two. Let's assume that Q<sub>1</sub> is ON and Q<sub>2</sub> is OFF. A trigger pulse (negative) at the input point has little tendency to go through CR<sub>1</sub> because Q<sub>1</sub> is ON and Q<sub>1</sub> collector is at essentially potential.

187. 0 volts or ground

188. However, the potential of  $Q_2$  collector is essentially  $+E_{CC}$ . Therefore, the negative pulse passes through  $CR_2$  to the collector of  $Q_2$ . Since  $Q_2$  is OFF and represents a high impedance, the pulse passes through  $C_2$  to  $Q_1$  base and turns  $Q_1$

188. OFF

189. Because CR<sub>1</sub> and CR<sub>2</sub> steer the trigger pulse to the proper part of the circuit, they are called ing diodes.

189. steering

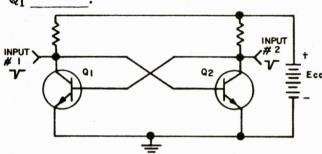

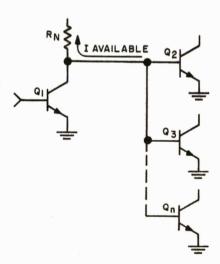

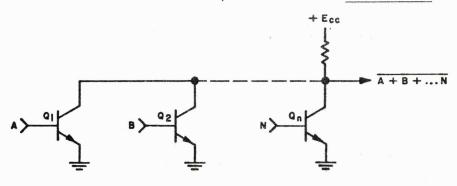

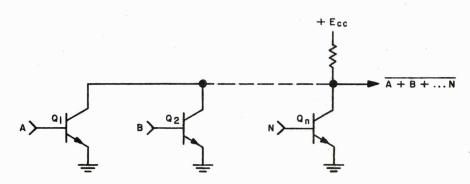

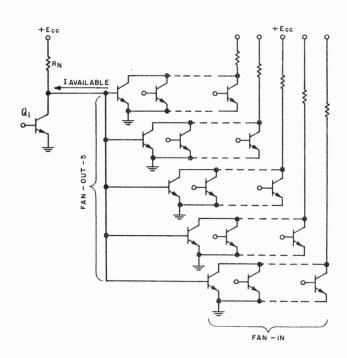

190. A DCTL (Direct Coupled Transistor Logic)

flip-flop is shown here. Operation is very similar to that of the conventional flip-flop. With

Q1 OFF and Q2 ON, a negative pulse at Input #1

turns Q2 OFF. The rising Q2 V<sub>Ce</sub> then turns

190. ON

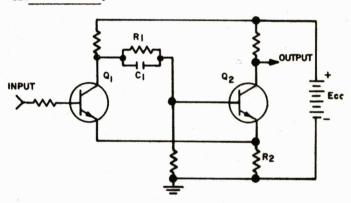

191. This circuit is one version of a Schmitt trigger. It is a regenerative circuit. Its state depends upon the relation of the input voltage to the emitter potential of Q<sub>1</sub>, as determined by R<sub>2</sub>. When the input voltage is lower than Q<sub>1</sub> emitter potential, Q<sub>1</sub> is \_\_\_\_\_(ON/OFF) and Q<sub>2</sub> is

191. OFF -- ON

192. As the input voltage increases, a critical value is reached at which  $Q_1$  begins to conduct. The decreasing  $Q_1$   $V_{Ce}$ , coupled through  $C_1$  begins to conduction in  $Q_2$ .

192. decrease

193. The decreased conduction of  $Q_2$  and the resulting decrease in IR drop across  $R_2$  cause a regenerative \_\_\_\_\_ in  $Q_1$  conduction.

193. increase

194. The regenerative action causes a very rapid change of state  $(Q_1 \text{ ON}, Q_2 \text{ OFF})$ . If the input voltage now decreases, a point is reached where conduction in  $Q_1$  starts to

194. decrease

195. The increasing  $Q_1$   $V_{ce}$  and  $Q_2$   $V_{be}$ , again aided by regenerative action, turn  $Q_2$

195. ON

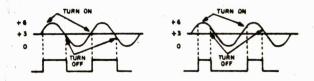

196. The values of input voltage at which the Schmitt trigger changes state are determined by bias and other circuit operating parameters. In the illustration below we see two different outputs produced from the same sine wave input with two different values of turn-on and turn-off voltage. Note that the turn-off voltage is than the turn-on voltage.

196. less, lower, etc.

197. Because its output depends on the instantaneous value of the input voltage regardless of its shape, and because its strong regenerative action gives extremely short rise time and fall time, the Schmitt trigger is useful for waveform restoration, signal level shifting, squaring of various waveforms, and for DC level detection.

This completes Semiconductor Circuits.

## VOLUME II COUNTING SYSTEMS

1. Before learning binary arithmetic, most students ask themselves this obvious question, "What's wrong with the everyday decimal system of arithmetic that requires that I learn the binary system of arithmetic?"

The answer is that there is nothing wrong with the decimal system as such. It works fine for everyday use such as handling money and for figuring various problems. Mechanical devices work well with the decimal system, witness the adding machines, comptometers, cash registers, etc. However, most of us live in an electronics world. Here decimal arithmetic creates problems. We will first look into some of the problems created by use of decimal arithmetic and then learn how they are overcome by the use of binary arithmetic.

(Proceed to next frame)

2. Imagine if you wish electronic systems that could generate and detect either ten amplitude levels of voltage and/or current; or trains of pulses ranging from one to ten. Of course these can and have been devised, but they are not simple circuits.

Most of the original electronic circuits used for counting by decimal, or tens, required feedback loops, and as a result these circuits were anything but simple. They were relatively

2. complex or complicated (or equivalent word)

| 3. | One of the reasons for the complexity of                |

|----|---------------------------------------------------------|

|    | electronic circuits using the decimal system            |

|    | is because the decimal system is based upon ten digits. |

These are: 0-1-\_\_\_-\_\_-\_\_-

3. 0-1-2-3-4-5-6-7-8-9

| 4. | To ease the requirements of electronic circuits |

|----|-------------------------------------------------|

|    | used for arithmetic purposes (computers, etc.)  |

|    | we can use lesser-known systems of arithmetic   |

|    | based upon values less than ten.                |

An example would be a system based upon the number eight, called an octal system. An octal system works with only eight digits.

These are: 0-1-\_\_\_\_.

(Fill in the remaining digits.)

4. 0-1-2-3-4-5-6-7

5. Let's keep reducing the number of digits available to us. Imagine a limit of five digits (called quinary). We would then list the following five digits.

5. 0-1-2-3-4

6. Fine, but that is still too many digits for our requirements. Assume a limit of two digits. These would be and .

6. 1 -- 0 or 0 -- 1 7. The prefix qui stands for five, and quinary stands for arithmetic based on the number 5. The prefix tri stands for three, and trinary represents arithmetic based upon the number 3.

The prefix bi stands for two, and arithmetic based on the number 2 is called \_\_\_\_\_\_.

7. binary

Binary arithmetic is based on the number and can be represented by the two digits and

8. 2 -- 0 -- 1 or 2 -- 1 -- 0

Let us discuss some of the ways in which we can develop binary arithmetic symbols in electronic circuits. Assume two different voltage levels, 0V and +1V.

Your task is to assign one of the binary digits to the 0V level and the other binary digit to the +1V level.

+1V = \_\_\_\_

9. 1 or 0 0 or 1

10. 0 -- 1 (or vice versa)

10. Did you carefully note that the response to the preceding frame stated that you could indicate either voltage level with the 0 or 1 digit?

This brings up an important point; unfortunately there is no industry-wide standard. Depending upon the choice of the manufacturer, or the individual engineer, the choice of a binary digit for a zero voltage level could be either \_\_\_\_\_ or \_\_\_\_.

11. What other ways are there to electronically represent the binary symbols of 0 and 1?

Many. Let us discuss the more well-known methods. A relay, open or closed. A flip-flop, conducting or non-conducting. Various voltage levels, zero or plus, zero or minus, plus or minus, different values of plus, different values of minus.

For recognition of the binary symbols of 0 and 1, presence or absence is the most often used method. For instance, presence or absence of a hole in a punched card or paper tape. Another method is the presence or absence of a magnetic field, such as on magnetic tape.

We hope you are beginning to see some of the many advantages of the use of binary symbols over decimal symbols in electronic circuits.

## (Proceed to next frame)

12. Before going too far let us clear up a possible source of confusion. The decimal system is based upon the number 10. The base of the system being the number 10, it is referred to as the "base 10." However, the fundamental number, or base, of the system in use could also be called the "root" or "radix." Should you see those words used, they are also correct and have the same meaning as the word "base."

The decimal system uses the number 10 as its root, or radix. Another way to express this is to say that the decimal system uses the base 10. For the binary system, we would say it uses the base

| 12. | 2  | 13.          | We should now have an appreciation of the prob-<br>lems of using decimal symbols and the ease of<br>using binary symbols in electronics. The next<br>step is to review decimal arithmetic. This will<br>act as an introduction to learning binary arith-<br>metic. |

|-----|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |    |              | (Proceed to next frame)                                                                                                                                                                                                                                            |

|     |    |              |                                                                                                                                                                                                                                                                    |

|     |    | <b>14.</b> . | To help us learn the subject it is best to review arithmetic as expressed by exponents or powers. There are three rules used in expressing numbers by powers. The first one is simple, it is:                                                                      |

|     |    |              | "Any number expressed to the power of 0 is equal to 1."                                                                                                                                                                                                            |

|     |    |              | For example, the base 10 to the power of 0, (written $10^0$ ), equals 1. The base 2 to the power of 0, (written $2^0$ ), equals                                                                                                                                    |

|     |    |              |                                                                                                                                                                                                                                                                    |

| 14. | 1  | 15.          | The second of the simple rules used in expressing exponents is:                                                                                                                                                                                                    |

|     |    |              | "A number expressed to a power of 1 is equal to the number itself."                                                                                                                                                                                                |

|     |    |              | For example, the base 2 to the power of 1, written $2^1$ , is equal to 2 itself.                                                                                                                                                                                   |

|     | ,  |              | This means that $10^1$ is equal to                                                                                                                                                                                                                                 |

|     |    |              |                                                                                                                                                                                                                                                                    |

| 15. | 10 | 16.          | As a reminder:                                                                                                                                                                                                                                                     |

The base 10 to the power of 0  $(10^0)$  = \_\_\_\_\_.

16.

$$10^{0} = 1$$

$2^{1} = 2$

17. The last rule is: "For powers of 2 or more, the number used in the base is multiplied by itself by the number of times expressed in its power."

Sounds impressive, but if we examine it closely we see that it is relatively simple. In the decimal system we use the base 10. The base 10 to the power of 2 would be a good example to illustrate the simplicity of the rule.

The number used is 10, multiplied by itself the number of times expressed in its power, which is 2, and it is written as  $10 \times 10$ . Thus  $10^2 = 10 \times 10$ .

The value of  $10^3$  is written as \_\_\_\_\_.

18. The value of  $10^2$ , written as  $10 \times 10$ , is equal to 100. The value of  $10^3$ , written as  $10 \times 10 \times 10$ , is equal to \_\_\_\_\_.

19. Try these examples as an exercise in exponents, or powers, of the base 10.

|     |    | written as | , |   |

|-----|----|------------|---|---|

| and | is | equal to   | • |   |

|     |    | written as |   | , |

| and | ie | equal to   |   |   |

$$10^7 = 10 \times 10 \times 10 \times 10$$

$\times 10 \times 10 \times 10$

$= 10,000,000$

20. Now let us create a table illustrating the values of exponents of the base 10, the exponents to be from 0 to 9. (If required, use a piece of scrap paper or the back of the preceding page for any figuring.)

21. Another way of illustrating the table is shown below. Note that the least significant value is to the right.

| 109 | 108               | 107 | 106 | 10 <sup>5</sup> | 104       | 10 <sup>3</sup> | 10 <sup>2</sup> | 101 | 100 |

|-----|-------------------|-----|-----|-----------------|-----------|-----------------|-----------------|-----|-----|

| 000 | 100<br>000<br>000 | 000 | 000 | 100<br>000      | 10<br>000 | 1000            | 100             | 10  | 1   |

(Proceed to next frame)

22. Using the base 10 to any power we can express any decimal number. As shown below the number 3 can be expressed by placing it under the column 100.

| 109                | 108               | 107              | 10 <sup>6</sup> | 10 <sup>5</sup> | $10^{4}$  | 103  | 102 | 10 <sup>1</sup> | 100 |

|--------------------|-------------------|------------------|-----------------|-----------------|-----------|------|-----|-----------------|-----|

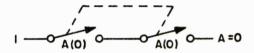

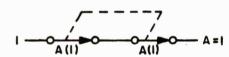

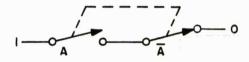

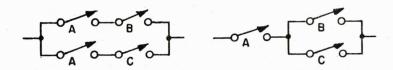

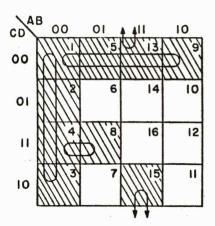

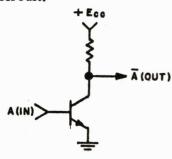

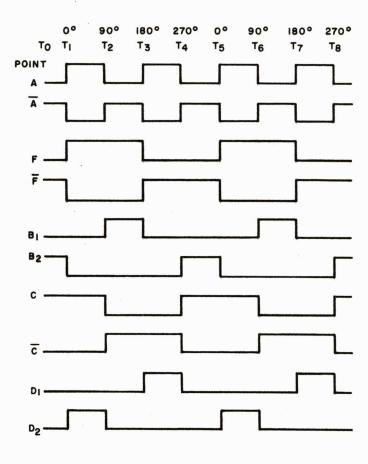

| 1000<br>000<br>000 | 100<br>000<br>000 | 10<br>000<br>000 | 1000<br>000     | 100<br>000      | 10<br>000 | 1000 | 100 | 10              | 1   |