Saturn Preflight Program Verification Plan

1 May 1971

Oxley, B. G. K99/5-1 Contract No. NAS 8-14000

MSFC-DRL-008A

Line Item<sup>2</sup>82

IBM No. 71W-00141

Prepared for the GEORGE C. MARSHALL SPACE FLIGHT CENTER Huntsville, Alabama

# Saturn Preflight Program Verification Plan

1May 1971

**Classification and Content Approval** VDooltt

Data Manager Approval

Program Office Approval

Space Systems Center/Huntsville/Alabama

#### PREFACE

The Saturn Preflight Program Verification Plan for the Saturn Launch Vehicle Preflight Program describes the methods which will be used to insure that the Preflight program meets all functional requirements and is operational for use in Saturn mission countdowns and preflight testing.

The Saturn Preflight Program Verification Plan combines the objectives formerly covered by the Program Verification Plan for Saturn Launch Vehicle Prepare to Launch Programs, MSFC-DRL-008A, Line Item 293, IBM No. 71W-00143 and the Saturn Preflight Program Verification Plan, MSFC-DRL-008A, Line Item 292, IBM No. 71W-00141. This document supersedes the two documents formerly directed towards Preflight verification and should, therefore, be the only reference for Preflight verification.

The objective of this plan is to specify the verification requirements for the baseline Preflight Program and the verification requirements for the changes implemented as a function of specific mission and/or vehicle operational requirements. Since the Preflight Program as defined applies to all mission configurations, any corrections to deviations or changes implemented to satisfy specific mission requirements will be reflected in periodic updates to this document. Program configuration control is maintained through use of a digital symbolic program comparison routine executed for each program revision to identify all the differences in the new configuration. This method insures that only those areas specified to change are different.

Part I contains the requirements for verifying the baseline Preflight program common to all Saturn launch vehicles. Part II defines the verification required to validate specific mission and vehicle dependent Preflight program changes to the baseline. Part II will be updated for each vehicle and will contain the methods to be used to verify changed areas of the Preflight program.

The 360/44 simulator will be used as the major tool for the PTL verification effort. This simulation contains a mathematically modeled platform, flight type LVDC/LVDA hardware and simulated LVDA interfacing equipment (DCS, switch selector, CIU, etc.).

# TABLE OF CONTENTS

| Paragraph  | Title                                                                    |            |  |

|------------|--------------------------------------------------------------------------|------------|--|

| Section 1: | GENERAL PREFLIGHT PROGRAM VERIFICATION                                   |            |  |

|            | 1.1 Introduction                                                         | 1-1        |  |

|            | 1.2 General Preflight Program Requirements                               | 1-2        |  |

|            | 1.2.1 Program Functional Requirements<br>1.2.2 Applicable Document List  | 1-2<br>1-3 |  |

|            | 1.3 Ground Rules for Preflight Programming                               | 1-3        |  |

|            | 1.3.1 RCA-110A Communication Link<br>1.3.2 Prelaunch Checkout Philosophy | 1-3<br>1-4 |  |

|            |                                                                          |            |  |

| Section 2: | LVDC NOMINAL CONDITIONS VERIFICATION                                     |            |  |

|            | 2.1 Introduction                                                         | 2-1        |  |

|            | 2.2 Accelerometer Pulse Count                                            | 2-2        |  |

|            | 2.3 CIU Read                                                             | 2-4        |  |

|            | 2.4 Command Receiver Linkage                                             | 2-4        |  |

|            | 2.5 Commanded Flight Linkage                                             | 2-5        |  |

|            | 2.6 Discrete Input Monitor                                               | 2-6        |  |

|            | 2.7 Discrete Output Monitor                                              | 2-7        |  |

|            | 2.8 Data Output Multiplexer Test                                         | 2-10       |  |

|            | 2.9 Exercise Attitude Command Test                                       | 2-12       |  |

|            | 2.10 Gimbal Angle Monitor                                                | 2-19       |  |

|            | 2.11 G&C Steering Test                                                   | 2-22       |  |

|            | 2.12 Ladder Error Test                                                   | 2-22       |  |

|            | 2.13 Load Routine                                                        | 2-24       |  |

|            | 2.14 Memory Error Test                                                   | 2-24       |  |

|            | 2.15 Minor Loop, Switch Selector, and Real Time<br>Counter Test          | 2-25       |  |

|            | 2.16 Sector Dump                                                         | 2-26       |  |

i

#### SECTION 1

#### GENERAL PREFLIGHT PROGRAM VERIFICATION

#### 1.1 Introduction

The LVDC Preflight Verification Plan provides a procedure which requires the LVDC Preflight Program to use all of its program logic. An LVDC preflight routine performs its function by executing a set of program logic. The only variations from a fixed logic path are determined by:

- RCA-110A input word options

- Error conditions

The LVDC Preflight Verification Plan contains three verification sections:

- LVDC Preflight Nominal Conditions Verification

- LVDC Preflight Error Conditions Verification

- LVDC Preflight Prepare to Launch Verification

In the Nominal Conditions Verification, variations introduced by RCA-110A input word options are exercised. The combination of options selected for input to the preflight routine requires the routine to perform all of its functions.

In the Error Conditions Verification, variations introduced by anomalies are exercised. The LVDC preflight routines which respond to error conditions are exercised. Each RCA-110A input word error or each hardware performance error tested by the routine is generated by the control programs.

For both Nominal and Error Conditions Verification, the plan provides the results expected when the preflight routine is executed with the specified input.

In the LVDC Preflight Prepare to Launch Verification, the same requirements apply to the input as in the Nominal and Error Conditions Verification. That is, the input exercises the functions of the routine for both nominal and error conditions. However, the launch criticality of the monitor functions of the Prepare to Launch routine necessitates an emphasis on the test status of external inputs to the routine. Thus, the plan details the contents of external inputs such as discrete inputs, discrete input spares, staging interrupts, accelerometers, gimbals, and variable azimuth quantities. These external inputs are neither RCA-110A input word options nor necessarily error conditions, yet they can significantly affect program logic path.

#### 1.2 General Preflight Program Requirements

#### 1.2.1 Program Functional Requirements

The LVDC Preflight Program performs the following functions under control of the SLCC:

- Load and/or verify the LVDC memory.

- Exercise, monitor, and verify internal functions of the LVDC and LVDA.

- Exercise and/or monitor selected Instrument Unit subsystems.

- Participate in overall guidance and control system tests.

- Perform limited data processing for the Launch Computer Complex.

These preflight routines are versatile and flexible in that they are adaptable to prelaunch conditions for the entire Saturn series of missions as presently conceived. In conjunction with the launch computer, these routines provide the following subsystem checkout capabilities:

- Operational checkout of the LVDC.

- Operational checkout of the LVDA.

- Operational checkout of the Switch Selector LVDA interface.

- Operational checkout of the accelerometer and gimbal angle processing features.

- Operational checkout of the vehicle discretes.

- Operational checkout of the LVDA-PCM interface.

#### 1.2.2 Applicable Document List

All documents used in verification of the preflight program are listed in Appendix A. All preflight routines, tested in verification described herein, are described in detail in the "LVDC Preflight Description" document (Reference 1).

# 1.3 Ground Rules for Preflight Programming

In defining the preflight routines, certain assumptions were made and ground rules were followed concerning the RCA-110A communication link and the prelaunch checkout philosophy.

#### 1.3.1 RCA-110A Communication Link

Those aspects of the interface between the Launch Vehicle Data Adapter and the RCA-110A, which are extensively utilized by the preflight routines, are described in this section.

One aspect of the interface between the RCA-110A and the LVDA/LVDC is the interrupts between them. In preflight, an interrupt to the LVDA/LVDC from the

RCA-110A will force a program recycle in the LVDC. Whereas, an interrupt from the LVDC to the RCA-110A electrical support equipment (ESE) forces the RCA-110A to read the telemetry buffer register.

Another aspect of the interface is the synchronization signals. The SYNC discrete to the LVDC serves two purposes:

- It notifies the LVDC that the launch computer is about to send information to the LVDC.

- It serves as a "data received" indication from the launch computer after the LVDC has sent out data, accompanied by an interrupt, to the launch computer and must be acknowledged before the LVDC continues on to the next program function.

The SYNC RESET signal indicates to the RCA-110A launch computer that the LVDC has recognized the SYNC signal and is proceeding to honor it.

Other preflight communication bridges between the RCA-110A and the LVDA/LVDC are 14 mode/data lines, six mode register lines, and 35 hardwire lines. The mode/data lines provide a means for the RCA-110A launch computer to relay mode commands or data to the LVDC. The mode register lines indicate to the launch computer the preflight routine currently being executed in the LVDC, and the hardwire lines are the means by which the LVDC/LVDA transmits data to the launch computer without requiring the processing of PCM/DDAS data.

#### 1.3.2 Pre-Launch Checkout Philosophy

During preflight checkout, the launch computer sequentially commands the LVDC into various routines. Only one routine can be commanded at a time. When the

LVDC is not executing a commanded routine, it is "idling" in a self-check loop in the Mode Sort Routine, periodically searching for the SYNC signal.

Upon receipt of the SYNC signal, the LVDC reads the 14 mode/data lines and proceeds to execute the commanded routine. Upon entering the commanded routine, the appropriate mode indication is loaded into the mode register, sent to the PCM/DDAS assembly, and sent to the launch computer via the hardwires. Pertinent data, if any, from the commanded routine is telemetered during execution of the routine, and the LVDC return<sup>S</sup> to its "idling" conditions when execution is completed.

Should the LVDC recognize an error condition, it will issue a special error status code to the launch computer, telemeter any error messages associated with the error condition, and wait for the SYNC signal before continuing. After processing the error, the LVDC will continue with the routine it was executing before the error condition arose or return to the Mode Sort Routine.

In the event that the launch computer desires to terminate an LVDC routine prematurely, it can do so with an RCA-110A interrupt signal which forces a program recycle.

#### SECTION 2

#### LVDC NOMINAL CONDITIONS VERIFICATION

#### 2.1 Introduction

The LVDC Preflight Nominal Conditions Verification requires the preflight routines to exercise logic variations determined by the RCA-110A input word options. The procedure for each preflight routine is defined in five sections:

- Function

- Options

- Input

- Comments

- Expected Output

The Function section provides a description of the purpose of the preflight routine.

The Options section details the items which are specified by the RCA-110A input word(s).

The Input section prescribes the combination(s) of input word options to select in exercising the preflight routine.

The Comments section contains any explanations which relate to selection of input and/or operation of the control program.

The Expected Output reports the results which must be obtained from the routine to indicate successful execution of the preflight routine.

The LVDC Preflight Nominal Conditions Verification plan does not select all possible combinations of input word options in exercising the preflight routines. However, the combination of options selected for input do verify that the preflight routine can respond to all combinations by selecting combinations which force the preflight routine to process each bit of the input word options in both an ON and an OFF state.

#### 2.2 Accelerometer Pulse Count

#### 2.2.1 Function

The Accelerometer Pulse Count Routine accumulates delta pulse counts and the associated time intervals for the accelerometers.

# 2.2.2 Options

Specify the first, second, and third accelerometer to be interrogated. Specify syllable selection for pulse count accumulations. Specify number of pulses to accumulate.

Specify mode 1, 2, or 3. (The mode determines the axis for the specified count and the time interval accuracy.)

2.2.3 Input

| Input | Mode | Axis<br>lst | Axis<br>2nd | Axis<br>3rd | Sy1 | Count |

|-------|------|-------------|-------------|-------------|-----|-------|

| 1     | 1    | X           | Y           | Z           | 0   | 1958  |

| 2     | 2    | Z           | Y           | Х           | 1   | 0002  |

| 3     | 3    | Y           | X           | Z           | 0   | 0001  |

| 4     | 3    | X           | Z           | Y           | 1   | 0001  |

2.2.4 Comments

Each mode is selected.

Each axis is selected for interrogation first, second, and third.

Syllable 0 and 1 are each selected.

Counts specified are multiples of the output rates for the axis to which they correspond.

Platform Simulation Rates:

| Axis | Rate                         |

|------|------------------------------|

| Х    | 195.8125 pulses every second |

| Y    | 1 pulse every 16 seconds     |

| Z    | 1 pulse every 32 seconds     |

2.2.5 Expected Output

| Input | Axis | Count | Max<br>Deviation | Time Delta<br>Seconds |

|-------|------|-------|------------------|-----------------------|

| 1     | Х    | 1958  | + 3              | 10.0                  |

|       | Y    | 0     | +1               | 9.0                   |

|       | Z    | 0     | +1               | 9.0                   |

For combinations 2, 3, and 4, the counts for the X, Y, and Z axes should be equal to the product of the platform simulated output rate specified in section 2.2.4, and the respective associated time interval. The X axis count should be within a  $\pm 5$  counts tolerance. The Y and Z axes counts should be within a zero (0) count tolerance.

In all cases, the B Channel count should be within  $\pm 1$  count of the A Channel count.

## 2.3 CIU Read

#### 2.3.1 Function

The CIU Read Routine telemeters the data received for the CIU address requested.

2.3.2 Options

Specify 12 CIU data address bits.

2.3.3 Input

| 12 bit CIU address | 10 bit CIU data |

|--------------------|-----------------|

| 5252 <sub>8</sub>  | 12528           |

| 2525               | 0525            |

# 2.3.4 Comments

Each CIU address bit is requested in both states. The data bits specified are supplied to the LVDC by the model 44 preflight simulator control program and are requested in both states.

2.3.5 Expected Output

| Addr              | PIO Tag | Data                   |

|-------------------|---------|------------------------|

| 5252 <sub>8</sub> | 4008    | 525377776 <sub>8</sub> |

| 2525              | 400     | 252777776              |

# 2.4 Command Receiver Linkage

#### 2.4.1 Function

The Command Receiver Linkage Routine provides direct access to the DCS Processor of the LVDC Flight Program for preflight.

2.4.2 Options

None.

2.4.3 Input

Verify Linkages - Entry to LVDC flight at location 4,17,0,274,4,17.

Verify Interrupt Processor interfaces by requesting telemeter single memory location and sector dump.

2.4.4 Comments

The preflight simulator control program requires that T-SYNC be allowed and that the command receiver interrupt be limited before entry to flight from preflight. The DCS commands executed exercise all preflight-flight interfaces.

2.4.5 Expected Output

Flight DCS Processor output data. The control program verifies this data and indicates status completion.

2.5 Commanded Flight Linkage

2.5.1 Function

Commanded Flight Linkage enters the flight program to run repeatable flight simulation.

2.5.2 Options

None.

#### 2.5.3 Input

Command Repeatable Flight Simulation. Upon completion, sum checks are taken. These sum checks must correspond to those received in flight program verification.

2.5.4 Comments

The sum checks assure that LVDC preflight does not interfere with the execution of repeatable flight simulation.

2.5.5 Expected Output

None.

# 2.6 Discrete Input Monitor

## 2.6.1 Functions

The Preflight Discrete Input Monitor routine performs these functions sequentially:

- Inhibit all interrupts except TLC.

- Read Discrete Input, Discrete Input Spares, and Interrupt Storage Registers.

- Limit all interrupts except TLC.

- Telemeter register readings.

- Recycle upon receipt of SYNC.

2.6.2 Options

None.

2.6.3 Input

Set Pattern for Registers

| Pattern | DIN            | DIS     | INT          |

|---------|----------------|---------|--------------|

| 1       | 3,5,7,9,11,,23 | 1,3,5,7 | 1,5,7        |

| 2       | 4,6,8,10,,24   | 2,4,6,8 | 2,3,4,6,8,10 |

Command routine with first pattern set. Reset first pattern, set second pattern, and recycle routine.

#### 2.6.4 Comments

All functions are verified. The status of interrupt storage bits 12 and 11 are undeterminable. These bits are indicated off in expected output.

Information which is not telemetered is available to the control program through the FCDD registers. This information can then be presented to the user.

#### 2.6.5 Expected Output

Register bits must be set as in the input pattern. The inhibit register must indicate all interrupts are inhibited. The limiting register must indicate limiting bits for each interrupt set. See Table 2.6.

#### 2.7 Discrete Output Monitor

## 2.7.1 Functions

The Discrete Output Monitor Routine allows for the set or reset of all discrete output register bits (except D.O.2) and the execution of a switch selector command.

| PATTERN 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| DIN REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 = SET                                     |

| 2       2       2       2       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 | 2 1                                         |

| DIS REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INT REGISTER                                |

| 8 7 6 5 4 3 2 1<br>1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 1 1<br>2 1 0 9 8 7 6 5 4 3 2 1<br>1 1 1   |

| INHIBIT REGISTER (Not Telemetered)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LIMIT REGISTER (Not Telemetered)            |

| 1 1 1<br>2 1 0 9 8 7 6 5 4 3 2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 1 1<br>2 1 0 9 8 7 6 5 4 3 2 1            |

| 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 1 1                                       |

| PATTERN 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |

| DIN REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |

| 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1<br>4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2 1                                         |

| 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |

| DIS REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INT REGISTER                                |

| 8 7 6 5 4 3 2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 1 1<br>2 1 0 9 8 7 6 5 4 3 2 1            |

| 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 1 1 1 1 1                                 |

| INHIBIT REGISTER (Not Telemetered)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LIMIT REGISTER (Not Telemetered)            |

| 1 1 1<br>2 1 0 9 8 7 6 5 4 3 2 1<br>1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 1 1<br>2 1 0 9 8 7 6 5 4 3 2 1<br>1 1 1 1 |

Table 2.6

## 2.7.2 Options

Set or reset of discrete output register.

D.O. register bits.

Switch Selector Load.

- Read bit.

- Reset bit.

- Stage bits (5).

2.7.3 Input

|    | Set/Reset | <u>D.O.</u> | SW-SEL. | READ | RESET | STAGES |

|----|-----------|-------------|---------|------|-------|--------|

| 1) | Set       | 3-13        | No      | 0    | 0     | None   |

| 2) | Reset     | 1           | Yes     | 0    | 0     | IU,S1  |

| 3) | Reset     | 3-13        | No      | 1    | 1     | A11    |

| 4) | Set       | 0           | Yes     | 1    | 0     | IU,S1  |

| 5) | Reset     | 1           | Yes     | 0    | 1     | None   |

| 6) | Set       | 1           | Yes     | Ν    | Ν     | None   |

#### 2.7.4 Comments

The setting of D.O.1 in the last verification combination prohibits any further commands to preflight. Halt must be applied and power-up performed to clear the D.O.1 bit, since D.O.1 resets SYNC.

Information not telemetered is available to the control program through the FCDD registers.

- 2.7.5 Expected Output (none telemetered)

- 1 = SET

|    | Discrete Output<br>Register               | Switch Selector<br>Feedbacks | Switch Selector<br>Register |

|----|-------------------------------------------|------------------------------|-----------------------------|

|    | 1 1 1 1<br>3 2 1 0 9 8 7 6 5 4 3 2 1      |                              |                             |

| 1) | 1 1 1 1 1 1 1 1 1 1 1 1                   | 0008                         | 000008                      |

| 2) | $1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \$ | 377                          | 10400                       |

| 3) |                                           | 377                          | 10400                       |

| 4) |                                           | 377                          | 50400                       |

| 5) |                                           | 000                          | 20000                       |

| 6) | 1                                         | 000                          | 00000                       |

## 2.8 Data Output Multiplexer Test Routine

2.18.1 Function

The Preflight DOM Test Routine exercises features of the DOM by issuing telemetry in a specified sequence.

2.8.2 Options

None.

2.8.3 Input

Command execution of DOM Test Routine and monitor DOM telemetry.

2.8.4 Comments

The telemetry contents correspond to those for conditions using the control program.

# 2.8.5 Expected Output

# DOM TEST

Expected output is based on known inputs to the preflight simulator control program.

| TAG  | DATA       | ITEM DESCRIPTION     |

|------|------------|----------------------|

| 0228 | 0200400028 | ICR SET              |

| 057  | 00000006   | DIN READ             |

| 053  | 001777576  | DIS READ             |

| 077  | 774007776  | SSFB READ            |

| 022  | 020040002  | ICR SET              |

| 023  | 00000000   | EMR READ             |

| 067  | 000377776  | CIU READ             |

| 043  | 000017776  | RCA INPUT REG. READ  |

| 022  | 020040002  | ICR SET              |

| 107  | XXXXXXXXX  | X ACCELEROMETER READ |

| 127  | XXXXXXXXX  | Y ACCELEROMETER READ |

| 117  | XXXXXXXXX  | Z ACCELEROMETER READ |

| 022  | 020040002  | ICR SET              |

| 236  | 00000000   | S.S. REG. LOAD       |

| 012  | 00000000   | D.O. REG. LOAD       |

| 052  | 00000000   | S.S./D.O.            |

| 000  | 070707070  | TELEMETRY OUTPUT     |

| 022  | 020040002  | ICR SET              |

| 103  | 7777XXXXX  | REAL TIME CLOCK READ |

| 057  | 00000006   | DIN READ             |

| 022  | 020040002  | ICR SET              |

| 023  | 000002000  | FG1 AND LAD 1        |

| 163  | 000004000  | FG2 AND LAD 2        |

| 153  | 000014000  | FG3 AND LAD 3        |

# 2.9.1 Function

This routine has two modes of operation. Mode 1 provides for automatic sequential driving of the pitch, roll, and yaw ladders. Mode 2 allows individual or simultaneous driving of the three ladders through predetermined increments at a rate determined by the frequency of SYNC discretes, issued by the launch computer.

2.9.2 Options

Mode 1 (automatic):

• None.

Mode 2:

• Ladder converter to select.

• Roll increment.

- Yaw increment.

- Pitch increment.

- Sign of increments.

#### 2.9.3 Input

| Converter | Pitch<br>Increment | Roll<br>Increment | Yaw<br>Increment | Number of<br>Increments |

|-----------|--------------------|-------------------|------------------|-------------------------|

| В         | +.12°              | +.06°             | +.24°            | 64                      |

| В         | 24°                | +.12°             | +.12°            | 64                      |

| А         | +.06°              | 24°               | 18°              | 64                      |

| A         | 0                  | 0                 | 0                | 4                       |

| А         | +.42°              | +.42°             | 42°              | 35                      |

## 2.9.4 Comments

Each option is requested in both states. SYNC will be issued by the control program at the fastest allowed rate and will be issued in such a manner as to drive each axis past maximum ladder output. This will test the issuance of special status codes.

```

2.9.5 Expected Output

None telemetered.

Ladder strip charts.

Status code history.

```

## 2.9.5.1 Status Code History

| MODE 1 | STATUS CODE HISTORY  |

|--------|----------------------|

| 008    | Mode Sort            |

| 13     | Exer. Att. Com. Test |

| 00     | Mode Sort            |

| MODE 2 | STATUS CODE HISTORY INPUTS 1, 2, and 3   |

|--------|------------------------------------------|

| 008    | Mode Sort                                |

| 17     | Exer. Att. Com. Test                     |

| 43     | Exer. Att. Com. Error (Driving past max) |

| 46     | Exer. Att. Com. Test (Returning to null) |

| 00     | Mode Sort                                |

| MODE 2 | STATUS CODE HISTORY INPUTS 4 and 5  |

|--------|-------------------------------------|

| 008    | Mode Sort                           |

| 17     | Exer. Att. Com. Test                |

| 46     | Exer. Att. Com. (Returning to null) |

| 00     | Mode Sort                           |

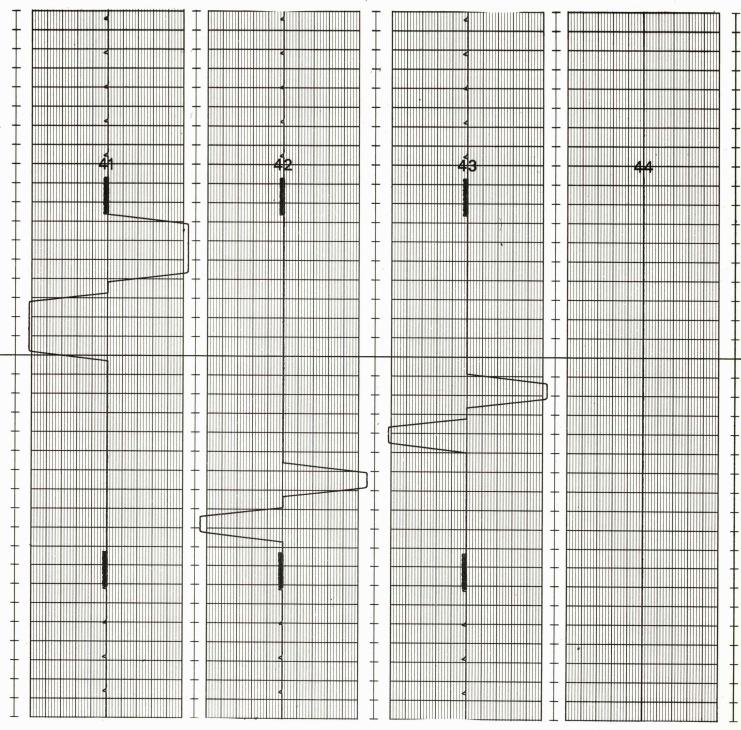

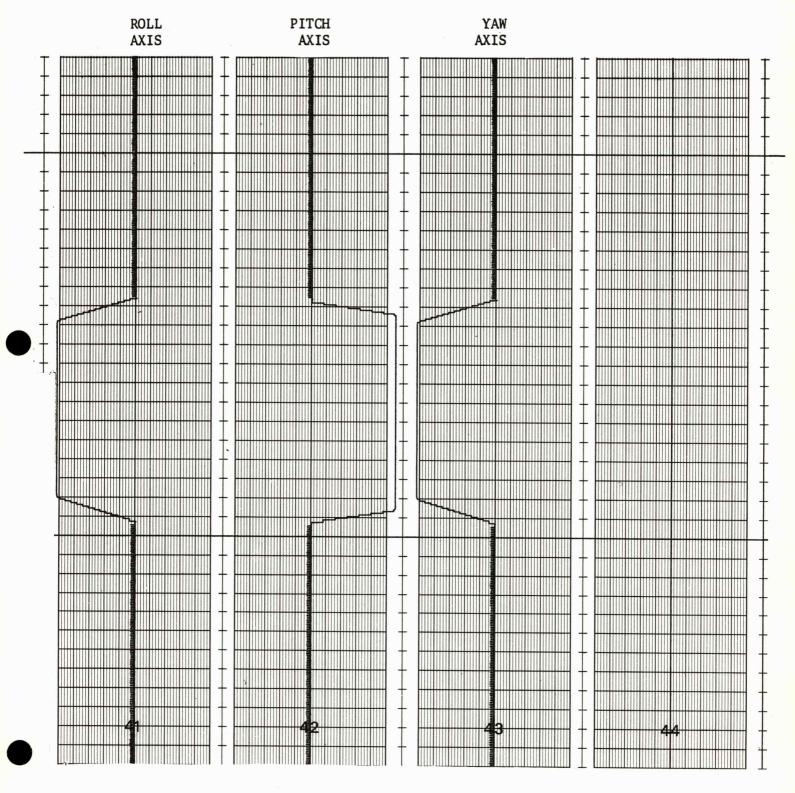

2.9.5.2 Ladder Strip Charts

ladder sensitivity = 50

rate = 100, power 100

PITCH

AXIS

YAW AXIS

# EXERCISE ATTITUDE COMMAND TEST MODE 2 (INPUT 1)

ROLL PITCH YAW AXIS AXIS AXIS T t ++ + T T Į Т t 9

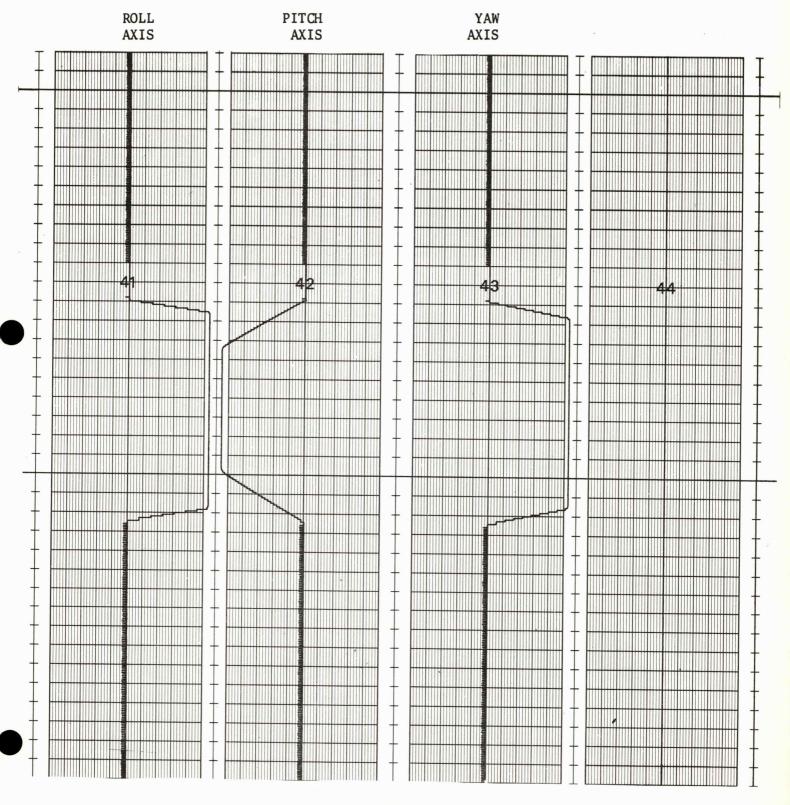

# EXERCISE ATTITUDE COMMAND TEST MODE 2 (INPUT 2)

ladder sensitivity = 50

rate = 5

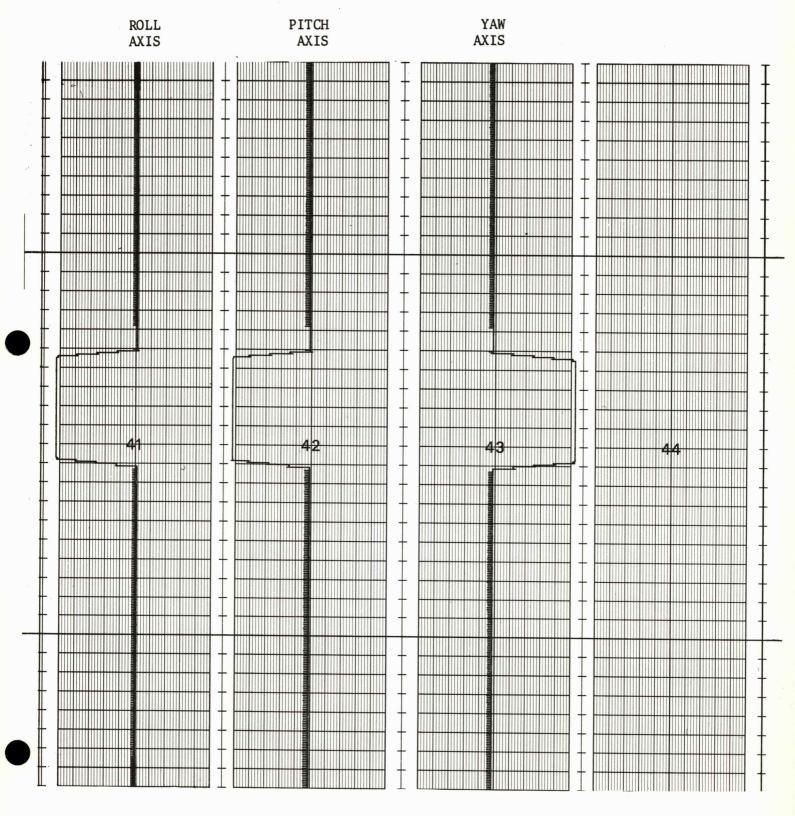

# EXERCISE ATTITUDE COMMAND TEST MODE 2 (INPUT 3)

ladder sensitivity = 50

rate = 5

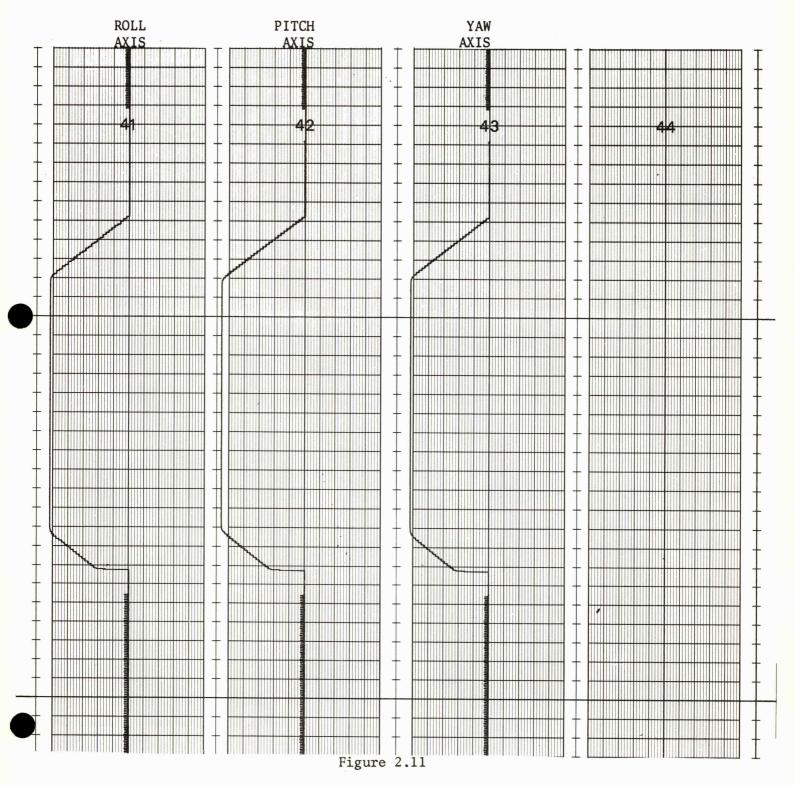

# EXERCISE ATTITUDE COMMAND TEST MODE 2 (INPUT 5)

ladder sensitivity = 50

rate = 5

#### 2.10.1 Function

The Gimbal Angle Monitor routine determines platform attitude utilizing the gimbals. Sequentially, the routine will:

- Read the gimbals.

- Monitor disagreement bit.

- Compute corrected readings.

- Telemeter results.

2.10.2 Options

Specify resolvers to monitor.

Select computation of corrected readings.

2.10.3 Input

|    | Resolvers |    |    |    |    |    | Corrected |           |    |          |

|----|-----------|----|----|----|----|----|-----------|-----------|----|----------|

|    | <u>C1</u> | C2 | C3 | F1 | F2 | F3 | B1        | <u>B2</u> | B3 | Readings |

| 1) | Y         | N  | Y  | N  | Y  | N  | Y         | N         | Y  | Ν        |

| 2) | Ν         | Y  | Ν  | Y  | N  | Y  | N         | Y         | N  | Y        |

| 3) | Y         | Y  | Y  | Y  | Y  | Y  | Y         | Y         | Y  | Y        |

2.10.4 Comments

Each resolver is requested in both states. Corrected readings are computed for all gimbals. The disagreement bit is monitored in a non-failure condition.

2.10.5 Expected Output

# GIMBAL ANGLE MONITOR

# (INPUT 1)

| TAG  | DATA       | TYPE          |

|------|------------|---------------|

| 0208 | 0001000028 | COARSE G.A. 1 |

| 014  | 00000000   | COARSE G.A. 3 |

| 010  | 311506232  | FINE G.A. 2   |

| 004  | 00000000   | BACKUP G.A. 1 |

| 400  | 00000000   | BACKUP G.A. 3 |

(INPUT 2)

| TAG  | DATA       | TYPE                 |

|------|------------|----------------------|

| 0548 | 0000000008 | COARSE G.A. 2        |

| 050  | 000003642  | COUNTER B CORRECTION |

| 044  | 000003642  | COUNTER A CORRECTION |

| 040  | 00000000   | FINE G.A. 1          |

| 0 34 | 00000000   | COUNTER B CORRECTION |

| 0 30 | 00000000   | COUNTER A CORRECTION |

| 024  | 00000000   | FINE G.A. 3          |

| 020  | 00000000   | COUNTER B CORRECTION |

| 014  | 00000000   | COUNTER A CORRECTION |

| 010  | 342607054  | BACKUP G.A. 2        |

| 004  | 000007054  | COUNTER B CORRECTION |

| 400  | 000007054  | COUNTER A CORRECTION |

(INPUT 3)

| TAG  | DATA       | TYPE                 |

|------|------------|----------------------|

| 1508 | 0001000028 | COARSE G.A. 1        |

| 144  | 000003644  | COUNTER B CORRECTION |

| 140  | 000003644  | COUNTER A CORRECTION |

| 134  | 00000000   | COARSE G.A. 2        |

| 130  | 000003642  | COUNTER B CORRECTION |

| 124  | 000003642  | COUNTER A CORRECTION |

| 120  | 00000000   | COARSE G.A. 3        |

| 114  | 000003642  | COUNTER B CORRECTION |

| 110  | 000003642  | COUNTER A CORRECTION |

| 104  | 00000000   | FINE G.A. 1          |

| 100  | 00000000   | COUNTER B CORRECTION |

| 074  | 00000000   | COUNTER A CORRECTION |

| 070  | 311506232  | FINE G.A. 2          |

| 064  | 000006232  | COUNTER B CORRECTION |

| 060  | 000006232  | COUNTER A CORRECTION |

| 054  | 00000000   | FINE G.A. 3          |

| 050  | 00000000   | COUNTER B CORRECTION |

| 044  | 00000000   | COUNTER A CORRECTION |

| 040  | 00000000   | BACKUP G.A. 1        |

| 0 34 | 00000000   | COUNTER B CORRECTION |

| 030  | 00000000   | COUNTER A CORRECTION |

| 024  | 342607054  | BACKUP G.A. 2        |

| 020  | 000007054  | COUNTER B CORRECTION |

| 014  | 000007054  | COUNTER A CORRECTION |

| 010  | 00000000   | BACKUP G.A. 3        |

| 004  | 00000000   | COUNTER B CORRECTION |

| 400  | 00000000   | COUNTER A CORRECTION |

2.11 G&C Steering Test Routine

2.11.1 Function

The G&C Steering Routine provides linkage to the Flight Initialize routine and to the Minor Loop of the flight routine.

2.11.2 Options

None.

2.11.3 Input

Command execution of the routine.

2.11.4 Comments

Output is handled by the Minor Loop. The only exit from this routine is by an executed halt.

2.11.5 Expected Output (none telemetered) See Figure 2.11.

2.12 Ladder Error Test

2.12.1 Function

The purpose of this routine is to exercise the ladder error detection circuitry.

2.12.2 Options

None.

2.12.3 Input

Command execution of Ladder Error Test routine.

# G&C STEERING LADDER STRIP CHART

# PLATFORM INITIALLY LEVEL, DEVIATE 5 degrees

ladder sensitivity = 50

rate = 5

## 2.12.4 Expected Output

None.

2.12.5 Comments

Output received only on error

2.13 Load Routine

2.13.1 Function

This routine allows the information previously placed in temporary storage by the Verify and Prepare to Load Routine to be transferred to the permanent memory locations specified.

2.13.2 Options

None.

2.13.3 Input

The Load Routine verification is executed in the verification of Verify and Prepare to Load.

2.13.4 Expected Output

None telemetered.

2.13.5 Comments

Proper verification is obtained in the Verify and Prepare to Load Routine procedure.

2.14 Memory Error Test

2.14.1 Function

This routine performs the testing of the memory error detection circuitry and logic. This check is divided into the following two categories:

- Tests initiated with the shift instruction. The shift instruction generates a memory SYNC pulse when the error detect logic is testing for no memory current.

- Tests initiated with the PIO instruction. The PIO instruction followed by a CLA, XOR, SUB, or MPH will select multiple address memory lines.

The above tests are repeated for all available modules.

2.14.2 Options

None.

2.14.3 Input

Request execution of memory error test routine.

2.14.4 Expected Output None.

2.15 Minor Loop, Switch Selector, and Real Time Counter Test Routine

2.15.1 Function

This routine tests the Real Time Counter (it must increment by 1 every 3 instructions), the Minor Loop Counter (must generate an interrupt 1.28 seconds after the minor loop counter is loaded), and the Switch Selector Counter (bit 1 in the Interrupt Storage Register must be set 1.28 seconds after the Switch Selector Counter is loaded).

2.15.2 Options

None.

2.15.3 Input

Command execution of the program.

2.15.4 Expected Output None.

2.15.5 Comments

The LVDC Error Detection Program has the capability of simulating an error condition in the Minor Loop, Switch Selector & Real Time Counter routine. If the routine functions properly without at error, it will return to Mode Sort upon completion.

2.16 Sector Dump Routine

2.16.1 Function

The purpose of this routine is to allow the RCA-110A launch computer to verify that all 256 locations within a given sector contain the correct instructions and/or data. The RCA-110A specifies the module and the sector(s) within that module which are to be dumped.

2.16.2 Options

Module.

Starting Sector.

Ending Sector.

2.16.3 Input

| Module | Starting Sector | Ending Sector |

|--------|-----------------|---------------|

| 2      | 008             | 178           |

| 5      | 12              | 05            |

| 0      | 00              | 00            |

#### 2.16.4 Expected Output

A sequential dump of sectors 0-17 of module 2. A sequential dump of sectors 12-17 and 0-5 of module 5. A dump of sector 0 of module 0.

NOTE: Sector locations are telemetered in groups of 32 words, 8 groups per sector.

2.16.5 Comments

Output from a Sector Dump can be checked against that received by doing a forced memory module dump (control program option).

Module and sector bits have been chosen such that the starting sector is less than the ending sector, starting sector is greater than the ending sector, and the starting sector is equal the ending sector.

2.17 Sector Sum Check Routine

# 2.17.1 Function

The purpose of this routine is to allow the RCA-110A launch computer to verify that the instructions and/or data (constants) in a given sector have not been affected by LVDC operations. The Launch Computer specifies the module and the sector(s) within that module to be sum-checked.

2.17.2 Options

Module.

Starting Sector.

Ending Sector.

#### 2.17.3 Input

| Module | Starting Sector | Ending Sector |

|--------|-----------------|---------------|

| 2      | 008             | 178           |

| 5      | 12              | 05            |

| 0      | 00              | 00            |

# 2.17.4 Expected Output

Sector sum-check of sectors 0-17 of module 2. Sector sum-check of sectors 12-17 and 0-5 of module 5. Sector sum-check of sector 0 of module 0.

### 2.17.5 Comments

The LVDC sector sum checks should equal the sum checks calculated by the preflight simulator control program.

Module and sector bits have been chosen such that the starting sector is less than the ending sector, starting sector is greater than the ending sector, and the starting sector is equal the ending sector.

# 2.18 Special Loader

### 2.18.1 Function

The Preflight Special Loader is a package which performs the same functions as these routines:

- Verify and Prepare to Load Routine.

- Load Routine.

- Sector Dump Routine.

This package is contained in module 1, sector 17. The Special Loader Mode Determine routine may be entered from the preflight Power Up and Initialize routine or Mode Sort routine.

## 2.18.2 Options

The options and input word formats for the Special Loader routines are the same as those of the Verify and Prepare to Load, Load, and Sector Dump routines, however, the ending sector bits of the Sector Dump routine input word are ignored. Only one sector is dumped per command.

2.18.3 Input

2.18.3.1 Verify Fixed Linkages

Entry to special loader is 1,17,0,001. All routines and subroutines are contained in 1,17.

Tables of 100 locations each must start at 0,04,234 and 0,06,234.

2.18.3.2 Sector Dump

| Module | Starting<br>Sector | Ending<br>Sector |

|--------|--------------------|------------------|

| 0      | 008                | 008              |

| 1      | 00                 | 00               |

| 2      | 07                 | 07               |

| 4      | 10                 | 12               |

# 2.18.3.3 Prepare to Load

| Module | Sector | Address | Data       |

|--------|--------|---------|------------|

| 5      | 008    | 0008    | 0000000008 |

| 5      | 00     | 007     | 77777776   |

| 2      | 07     | 070     | 252525252  |

| 4      | 10     | 300     | 525252524  |

# 2.18.3.4 Load

Perform modifications indicated in Prepare to Load .

# 2.18.3 Verify

| Module | Sector | Address | Data Expected |

|--------|--------|---------|---------------|

| 5      | 008    | 0008    | 000000008     |

| 5      | 00     | 007     | 77777776      |

| 2      | 07     | 070     | 252525252     |

| 4      | 10     | 300     | 525252524     |

# 2.18.4 Comments

Restore altered core locations. Output from sector dump can be checked against that received by doing a forced dump (control program option). Verification requests select all input bits in each state.

2.18.5 Expected Output

# 2.18.5.1 Sector Dump

| Module | Sector |      |

|--------|--------|------|

| 0      | 008    |      |

| 1      | 00     |      |

| 2      | 07     |      |

| 4      | 10     | 2-30 |

## 2.18.5.2 Prepare to Load

| Control Word     | Data       |

|------------------|------------|

| (The control     | 0000000008 |

| program verifies | 77777776   |

| contents of      | 252525252  |

| telemetry        | 525252524  |

### 2.18.5.3 Load

None telemetered.

2.18.3.4 Verify

| Control Word     | Data       |

|------------------|------------|

| (The control     | 0000000008 |

| program verifies | 777777776  |

| contents of      | 252525252  |

| telemetry)       | 525252524  |

## 2.19 Switch Selector Test

# 2.19.1 Function

The Switch Selector Routine provides the capability of exercising the vehicle switch selector drivers in the LVDA. The routine tests all readings in the reset condition for zero, and tests stage select bits of the input word to prevent exercising more than two switch selectors at one time. It then issues the requested address to the selected switch selector, delays 20 milliseconds, and verifies switch selector feedbacks directly through the CIU (if present). It also verifies the stage select bit through the CIU (if present).

2.19.2 Options

Specify stage bits (maximum of 2).

Specify address bits.

Specify CIU present.

Specify switch selector relay present.

Specify a switch selector read command.

Specify switch selector channel A or B.

2.19.3 Input

| Stage Bit(s) | Address          | CIU | Relay | Read | Channel |

|--------------|------------------|-----|-------|------|---------|

| S2,IU        | 370 <sub>8</sub> | Y   | Ν     | Y    | А       |

| S1,S4        | 007              | N   | Y     | N    | В       |

| IU,Spare     | 377              | Ŷ   | Y     | Y    | А       |

### 2.19.4 Comments

All options will be exercised in both on and off state. The switch selector feedback shall be delayed in relationship to the issuance of the options in order to simulate the actual hardware.

2.19.5 Expected Output

No output expected.

# 2.20 Telemetry Test Routine

2.20.1 Function

The Telemetry Test Routine provides the capability to check the telemetry system for proper operation by providing computer telemetry and DOM telemetry at a selectable rate.

# 2.20.2 Options

Select mode 0 (indefinite length loop):

- 4.183 ms. telemetry rate (A).

- 4.347 ms. telemetry rate (B).

- 4.511 ms. telemetry rate (C).

- 8.285 ms. telemetry rate (D).

- 8.941 ms. telemetry rate (E).

- Rate supplied by previous load.

Select mode 1 (run each rate (A-E) 3 minutes)

# 2.20.3 Input

| Mode | 4.183 | 4.347 | 4.511 | 8.285 | 8.941 | Rate Supplied<br>By Previous Load |

|------|-------|-------|-------|-------|-------|-----------------------------------|

| 0    | Yes   | No    | No    | No    | No    | No                                |

| 0    | No    | Yes   | No    | No    | No    | No                                |

| 0    | No    | No    | Yes   | No    | No    | No                                |

| 0    | No    | No    | No    | Yes   | No    | No                                |

| 0    | No    | No    | No    | No    | Yes   | No                                |

| 0    | No    | No    | No    | No    | No    | Yes                               |

|      |       |       |       |       |       |                                   |

1 Run rates (A-E) for a period of three minutes each

# 2.20.4 Comments

All telemetry rates will be exercised in the verification procedure. The routine will exit to Mode Sort if the mode = 1 upon completion. If the mode = 0, the only exit from the routine is via the RCA-110A interrupt, which causes an exit to Forced Begin.

|      | Telemetry Data |      |

|------|----------------|------|

| PIO  | DATA           | TYPE |

| 0018 | 7070707068     | LVDC |

| 771  | 77777776       | LVDC |

| 521  | 525252524      | LVDC |

| 025  | 252525252      | LVDC |

| 077  | 774007776      | DOM  |

Tolematmr Data

The control program verifies the telemetry and indicates the telemetry rate issued.

# 2.21 Verify and Prepare to Load

#### 2.21.1 Function

This routine has two distinct modes. Mode 1 (Yerify) allows the launch computer to obtain the contents of any LVDC memory location. Mode 2 (Prepare to Load) allows the launch computer to specify the desired contents of any LVDC memory location. (The actual core modification occurs upon execution of the Load Routine subsequent to the Prepare to Load).

2.21.2 Options

Mode (Verify, Prepare to Load).

Last group.

Simplex or duplex (Prepare to Load only).

Module.

Sector.

Address.

Data to load (Prepare to Load only).

|    | Mode          | Module | Sector       | Address | S/D | Last<br>Group | Data                   |

|----|---------------|--------|--------------|---------|-----|---------------|------------------------|

| 1) | Prep. to Load | 5      | 018          | 1258    | 0   | 1             | 525252524 <sub>8</sub> |

| 2) |               |        | Perform Load |         |     |               |                        |

| 3) | Verify        | 5      | 01           | 125     | 0   | 1             |                        |

| 4) | Prep. to Load | 2      | 10           | 252     | 1   | 0             | 252525252              |

|    | Prep. to Load | 4      | 06           | 377     | 1   | 1             | 77777776               |

| 5) |               |        | Perform Load |         |     |               |                        |

| 6) | Verify        | 2      | 10           | 252     | 0   | 0             |                        |

|    | Verify        | 4      | 06           | 377     | 0   | 1             |                        |

2.21.4 Comments

The contents of the telemetered control word are verified by the control program and any failure is reported. The data word contents are displayed.

After a Prepare to Load, the successful execution of the Load Routine provides verification of the Load Routine.

# 2.21.5 Expected Output

|    | Control Word | Data                   |

|----|--------------|------------------------|

| 1) | (The control | 525252524 <sub>8</sub> |

| 2) | program      |                        |

| 3) | verifies     | 525252524              |

| 4) | contents of  | 252525252              |

|    | telemetry)   | 77777776               |

| 5) |              |                        |

| 6) |              | 252525252              |

|    |              | 777777776              |

# SECTION 3

# LVDC PREFLIGHT ERROR CONDITIONS VERIFICATION

# 3.1 Introduction

The LVDC Preflight Error Conditions Verification exercises those preflight program variations caused by recognition of error conditions. The preflight routines report the error conditions by the telemetry of error messages. The Error Conditions Verification, therefore, exercises each routine of the LVDC Preflight Program which can telemeter error messages. The control program used to perform the verification plan forces the RCA-110A input word error or the hardware performance error tested for by each routine. The preflight routine telemetry is compared against expected, and any deviations are reported by the control program. Upon successful completion of the tests for a preflight routine, the error message telemetry received is printed.

This section contains two parts for each preflight routine tested:

- Preflight Function

- Error Test Organization

The Preflight Function describes the purpose of the routine, emphasizing the routines relation to the error conditions tested. The number of error messages which can be telemetered by the routine is indicated. Appendix B lists the error messages by routine.

The Error Test Organization defines the method the control program employs in indicating the error conditions to the preflight routine. Certain error conditions are mutually exclusive. For example, the error condition which states that COD counter 1 is greater than COD counter 2, and the error condition which

states that COD counter 2 is greater than COD counter 1 are mutually exclusive conditions. Thus, the Error Test is sub-divided into sequences, where a sequence defines the error condition(s) generated for a single execution of the preflight routine. When the control program completes a sequence, all conditions are reset to normal and the next sequence is performed.

Certain control program capabilities and limitations are pertinent to the Error Test definition. These include:

- The contents of COD counter 1 and 2 for any axis and any resolver may be specified in failure control counter 'A' and 'B'.

- Timing functions within LVDA may be stopped while LVDC continues operation (DST discrete control). This control stops real time clock from incrementing and simultaneously stops timer 1 and 2 counters from decrementing.

- The rate at which accelerometers increment by channel and axis may be specified.

- The contents and operation of most registers internal to the LVDA can not be directly controlled. These include interrupt inhibit, interrupt limit, ladder error circuitry, and memory error circuitry functions.

- The preflight simulator control program can, however, identify execution of any PIO by the LVDC Preflight Program. The control program can stop execution, specify results of PIO by loading the LVDC accumulator and then restarting the LVDC Preflight Program. In this operation the LVDC Preflight Program timing is unaffected. Thus, the effect is a real time operation of the preflight routines where error conditions are supplied by a control program.

Appendix B lists the error message telemetry by routine and by sequence within the routine.

# 3.2 LVDC Timing and Counter Subroutine

# 3.2.1 Preflight Function

The LVDA Timing and Counter subroutine is executed in the Mode Sort loop. This subroutine monitors:

- Real time clock.

- Minor Loop timer.

- Switch Selector timer.

- Duplex COD counters.

- Duplex accelerometers.

Twenty-four error messages can be telemetered by this subroutine (see Appendix B).

3.2.2 Error Test Organization

## 3.2.2.1 First Sequence

- a) Stop LVDC on a read error monitor register instruction (PIO 023), guaranteeing that execution is not in LVDA Timing and Counter Subroutine.

- b) Drive 'A' accelerometers X, Y, Z at max. rate.

Drive 'B' accelerometers X, Y, Z at 0 rate.

This will result in delta A not equal delta B.

c) Set for failure control of COD counters A and B. Set for counter 'A' to be 6024<sub>8</sub>.

Set for counter 'B' to be  $6040_8$ .

This will cause errors in A - B order.

- d) Load BYPASS word to make subroutine run accelerometer tests.

- e) Set FCDD bit which stops timing functions in LVDA (FCDD discrete control bit DST). This stops real time clock from counting and stops timers from counting down.

- f) Reset ICR 11 bit when subroutine sets it. (single step function)

## 3.2.2.2 Second Sequence

- a) See step a) above

- b) Set for failure control COD counters A & B

- c) Set counter 'A' =  $6020_8$ . Set counter 'B' =  $6006_8$ .

This will generate disagreement bit and failure in B - A order.

d) Single step to set minor loop inhibit and reset inhibit causing failure indication on inhibit function.

3.2.2.3 Third Sequence

- a) See step a) above.

- b) Single step to set switch selector inhibit, reset inhibit, causing failure indication on inhibit function.

# 3.2.2.4 Fourth Sequence

- a) See step a) above.

- b) Single step to read interrupt storage register, and advance two instructions.

c) Set accumulator = 0, causing reset of interrupt control latch but not minor loop bit.

This indicates failure of limiting function.

- 3.2.2.5 Fifth Sequence

- a) See step a) above.

- b) Set single step to reset switch selector interrupt bit in the interrupt storage register, advance two instructions to read the ISR, and put switch selector bit into the accumulator, indicating a limit function failure.

- c) Load BYPASS to prevent running of minor loop test. This makes the sequence of PIO's correct for step b).

# 3.2.2.6 Sixth Sequence

- a) See step a) above.

- b) Single step past first minor loop test (inhibit set) to second load of minor loop counter. Go to reset of minor loop bit when the interrupt is received. Advance two instructions to read ISR, and put minor loop bit in the accumulator.

This indicates failure of reset logic.

c) Load BYPASS to cancel effects of step c] above.

# 3.2.2.7 Seventh Sequence

- a) See step a) above.

- b) As for minor loop, single step past first switch selector test (inhibit set) to second load of switch selector counter. Go to reset of switch selector interrupt, and advance two instructions to read ISR. Put switch selector bit into accumulator. This indicates failure of limiting function.

- c) Load BYPASS to prevent running of minor loop test. This makes the sequence of PIO's for step b) correct.

- 3.2.2.8 Eighth Sequence

- a) See step a) above.

- b) Set to fail COD counters A.

Set counter 'A' =  $6010_8$ .

Set counter 'B' =  $6016_8$ .

This sets disagreement bit on, but difference tests will pass.

- c) Reset ICR 8 when test sets it. This causes disagreement bit to occur when it is not expected.

- d) Load BYPASS to cancel effects of step c) above.

# 3.2.2.9 Ninth Sequence

- a) See step a) above.

- b) Set to fail COD counter. Set counter 'A' =  $6010_8$ . Set counter 'B' =  $6016_8$ .

- c) Single step to set internal control register bit 8 during test of disagreement bit logic, i.e., when ICR 11 first set. ICR 8 will disable disagreement bit when it is expected.

## 3.2.2.10 Tenth Sequence

- a) Reset ERROR mode flag.

- b) Display completed message.

3.3.1 Preflight Function

The Minor Loop, Switch Selector, Real Time Counter routine is a commanded preflight routine. This routine verifies the operation of the real time clock and the two timers. The minor loop timer and the switch selector timer are checked by calculating the time interval between the load of the counter and receipt of the interrupt.

Six error messages can be telemetered from the routine (see Appendix B).

3.3.2 Error Test Organization

3.3.2.1 First Sequence

- a) Command Preflight to the Minor Loop, Switch Selector, Real Time Counter routine.

- b) Set FCDD bit which stops LVDA timing functions (FCDD discrete control bit DST). This causes a real time clock failure.

3.3.2.2 Second Sequence

- a) See step a) above.

- b) Single step to load minor loop counters. Load counters with a 0.This will cause minor loop interrupt to occur early.

### 3.3.2.3 Third Sequence

- a) See step a) above.

- b) Single step to check for Switch Selector bit after minor loop occurred properly (second read of ISR). Put Switch Selector bit into accumulator indicating switch selector occurred early.

- 3.3.2.4 Fourth Sequence

- a) See step a) above.

- b) Single step to load switch selector counter. Reload counter with full counter. This will cause no switch selector interrupt to occur.

- 3.3.2.5 Fifth Sequence

- a) See step a) above.

- b) Single step to load switch selector counter. Reload with 1 bit. This will cause no minor loop operation and an early switch selector interrupt.

- 3.3.2.6 Sixth Sequence

- a) See step a) above.

- b) Single step to release minor loop inhibit. Inhibit minor loop interrupt. This will cause no minor loop interrupt and a switch selector interrupt at the correct time.

# 3.3.2.7 Seventh Sequence

- a) Reset error mode flag.

- b) Display completed message.

3.4 Mode Sort Routine

### 3.4.1 Preflight Function

The Mode Sort routine is executed as a minor loop. The routine monitors the EMR register and accepts mode commands from the ground. There are other functions performed in the loop; however, they are discussed in each subroutine. There are four error messages in the Mode Sort routine (see Appendix B).

# 3.4.2.1 First Sequence

a) Single step to EMR read in the Error Monitor subroutine of the mode sort loop. Put a 600<sub>8</sub> into the accumulator. These are TLC bits which cannot be accepted. From this point, single step to next error read (second read in mode sort loop), and set EM8 bit in the accumulator. This will cause an error, since EM8 is not accepted on second read of EMR.

#### 3.4.2.2 Second Sequence

a) Load command receiver/RCA register with zeros. This is an error, as only mode commands (mode bit = 1) are accepted in Mode Sort.

## 3.4.2.3 Third Sequence

- a) Reset error mode flag.

- b) Display 'completed' message.

#### 3.4.2.4 Fourth Sequence

a) Set the SCB bit and reset the SCA bit in the DIS register.

# 3.5 Telemetry Test

3.5.1 Preflight Function

The Telemetry Test routine is a commanded preflight program. This routine accepts an input word which defines the rate at which to telemeter data. The routine then telemeters data bit patterns to test the system.

There is one error message in the telemetry test (see Appendix B).

3.5.2 Error Test Organization

3.5.2.1 First Sequence

a) Command Telemetry Test and issue an input word of 0. An input word of 0 is unacceptable to the telemetry test.

3.5.2.2 Second Sequence

- a) Reset error flag.

- b) Display 'completed' message.

# 3.6 Read Input Data Subroutine

3.6.1 Preflight Function

The Read Input Data Subroutine is a preflight utility subroutine which handles ground/LVDC interface in accepting data words.

There is one error message issued from the read input data subroutine (see Appendix B).

3.6.2 Error Test Organization

3.6.2.1 First Sequence

a) Command the Telemetry Test routine. Issue an input word with the mode bit = 1. This is an error.

# 3.6.2.2 Second Sequence

- a) Reset error mode flag.

- b) Display 'completed' message.

#### 3.7 CIU Data Read Routine

#### 3.7.1 Preflight Function

The CIU Read Data routine is a preflight commanded routine. This routine requests data from the CIU by loading the CIU register with an address in the CIU. When the requested address is found in the strobe of the CIU, the data is loaded into the data register and an interrupt is generated.

There are two messages issued by the routine (see Appendix B).

3.7.2 Error Test Organization

# 3.7.2.1 First Sequence

- a) Command the CIU data read routine and issue the required input word.

- b) Do not respond to CIU data request. This will cause routine to time out and issue an error message.

#### 3.7.2.2 Second Sequence

a) As step a) above, except single step from load of CIU address bits  $(PIO 042_8)$  to the EMR read  $(PIO 023_8)$  made by the routine when the data register is read. Supply unacceptable EMR bits.

#### 3.7.2.3 Third Sequence

- a) Reset error mode flag.

- b) Display 'completed' message.

3.8 G and C Steering Routine

3.8.1 Preflight Function

The G and C Steering routine is a commanded preflight routine. This routine will call the flight program minor loop processor upon receipt of a minor loop interrupt. The routine times out, if a delay of more than 30 milliseconds occurs before receiving an interrupt.

There is one error message issued from this routine (see Appendix B).

3.8.2 Error Test Organization

# 3.8.2.1 First Sequence

- a) Command G and C Steering routine.

- b) Set the FCDD control (DST), which stops timing functions in the LVDA so no minor loop will occur.

#### 3.8.2.2 Second Sequence

- a) Reset error mode flag.

- b) Display 'completed' message.

3.9 DOM Test

3.9.1 Preflight Function

The DOM test is a commanded preflight routine. The functions of the DOM are verified by telemetering data bit patterns. One specific function of the DOM is performed when minor loop interrupt occurs. There is one error message issued by this routine (see Appendix B).

### 3.9.2.1 First Sequence

- a) Command preflight DOM test.

- b) Set FCDD control (DST) which stops timing functions in the LVDA so no minor loop interrupt will occur.

### 3.9.2.2 Second Sequence

- a) Reset error mode flag.

- b) Display 'completed' message.

#### 3.10 Ladder Error Test

## 3.10.1 Preflight Function

The Ladder Error test is a commanded preflight routine. This routine exercises the converter switching logic of the ladders. Under the specifications of the analog converters, this test verifies that the converters will or will not switch and that such a switch is recorded in the EMR bit 17 and DIS ladder bits.

3.10.2 Error Test Organization

3.10.2.1 First Sequence - Test Select Converter A in EMR Error test indicating failure by setting SCB in EMR.

- a) Command Ladder Error Test, clamp ladders to zero, and set ICR function to select converter A.

- b) Single step to first read of DIS. Advance two instructions to read of EMR where bit 17 should be zero. Put 17 into the accumulator to indicate SCB where no SCB is expected.

If the following sequences are performed as listed, the errors may be generated without commanding the ladder routine after each error.

3.10.2.2 Second Sequence

This error test indicates failure by setting SCB in the DIS.

- a) Same as a) above.

- b) Test Select Converter A in DIS Single step to set read of DIS. Indicate converter B selected by putting bits 18 and 19 in the accumulator.