DELCO ELECTRONICS DIVISION . GENERAL MOTORS CORPORATION

SYSTEM MECHANIZATION

# SITUDY B STUDY GUIDE

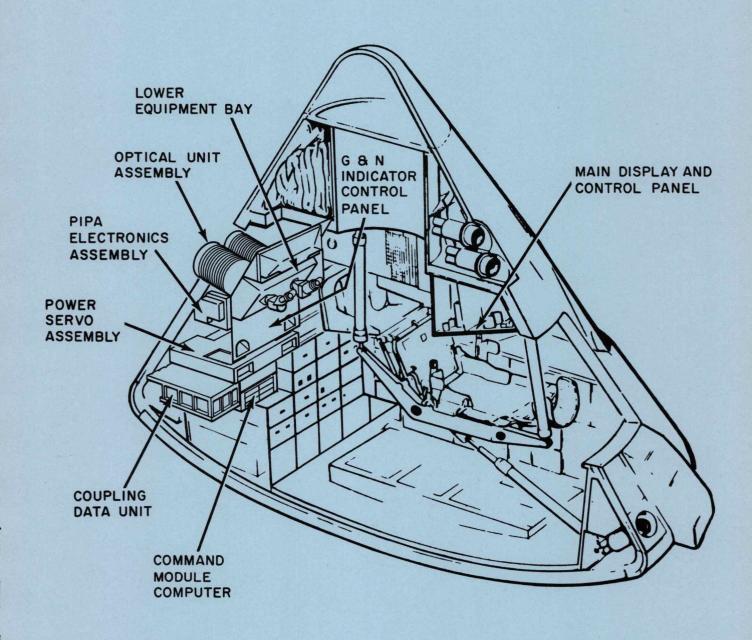

CM PRIMARY GUIDANCE NAVIGATION AND CONTROL SYSTEM

#### SKYLAB

## COMMAND MODULE

PRIMARY GUIDANCE, NAVIGATION AND CONTROL SYSTEM

STUDENT STUDY GUIDE

**PGNCS**

LEVEL III

SYSTEM MECHANIZATION COURSE SM-4100

PREPARED BY

DELCO ELECTRONICS

DIVISION OF GENERAL MOTORS

MILWAUKEE, WISCONSIN

## PREFACE

This student study guide has been prepared by Delco Electronics in response to:

Contract NAS 9-10356

for

System Assembly and Test, Inertial

Measurement Unit, Coupling Data Unit

Power and Servo Assembly - Project APOLLO

## TABLE OF CONTENTS

|            |         |                                                | Page |

|------------|---------|------------------------------------------------|------|

| Section I  | Introd  | uction to the Primary Guidance, Navigation and |      |

|            | Contro  | ol System (PGNCS)                              | 1-1  |

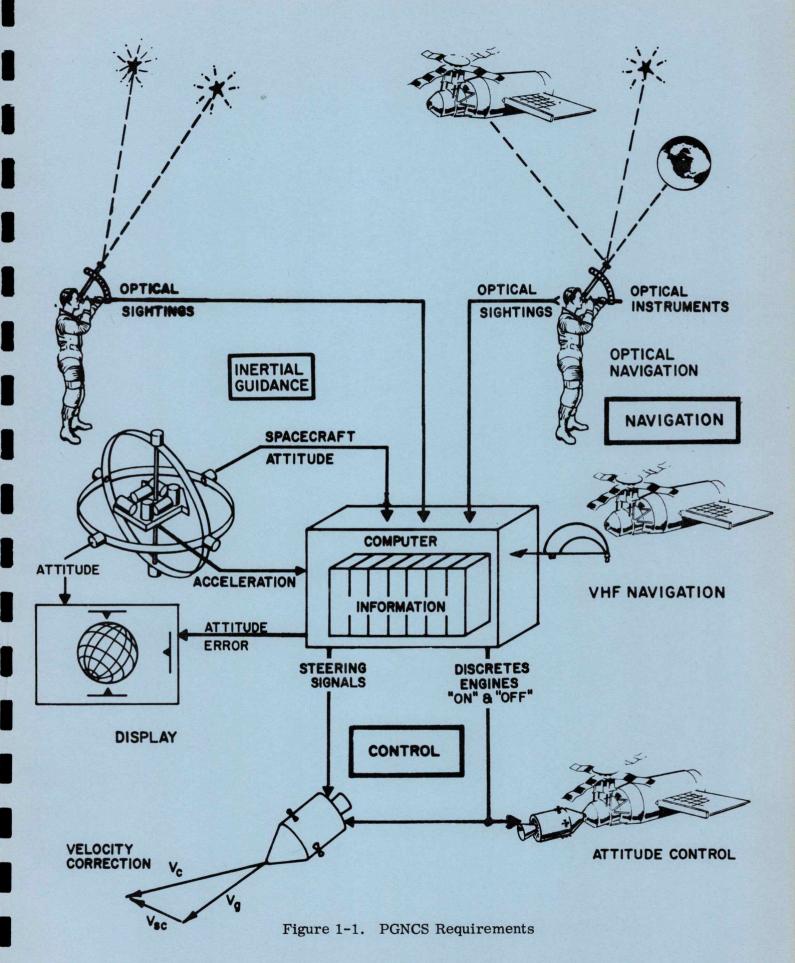

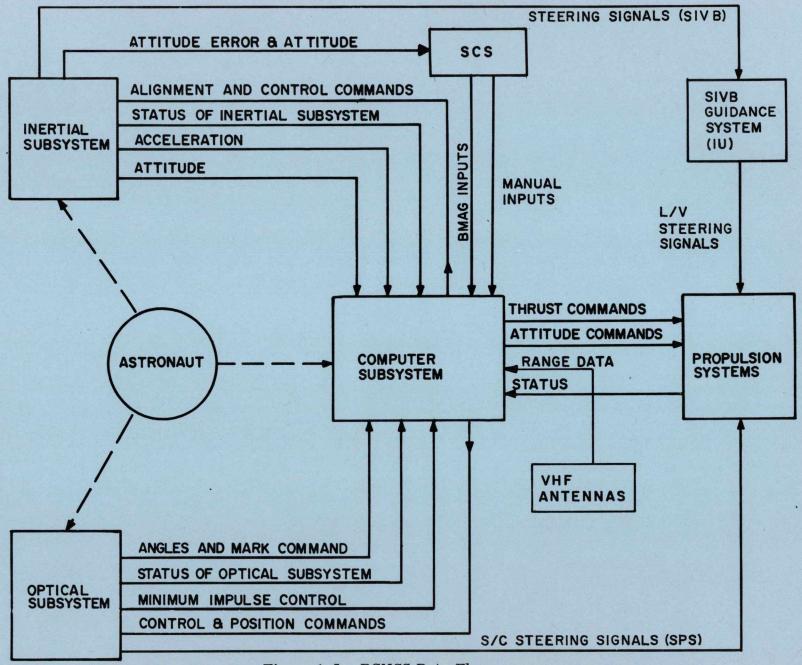

| Block 1.1  | Guida   | nce, Navigation and Control Requirements       | 1-1  |

| 1.1.       |         | Inertial Guidance                              | 1-1  |

|            | 1.1.1   | Attitude Determination                         | 1-1  |

| 1.1.       |         | Navigation                                     | 1-1  |

|            |         | Control                                        | 1-3  |

|            |         |                                                |      |

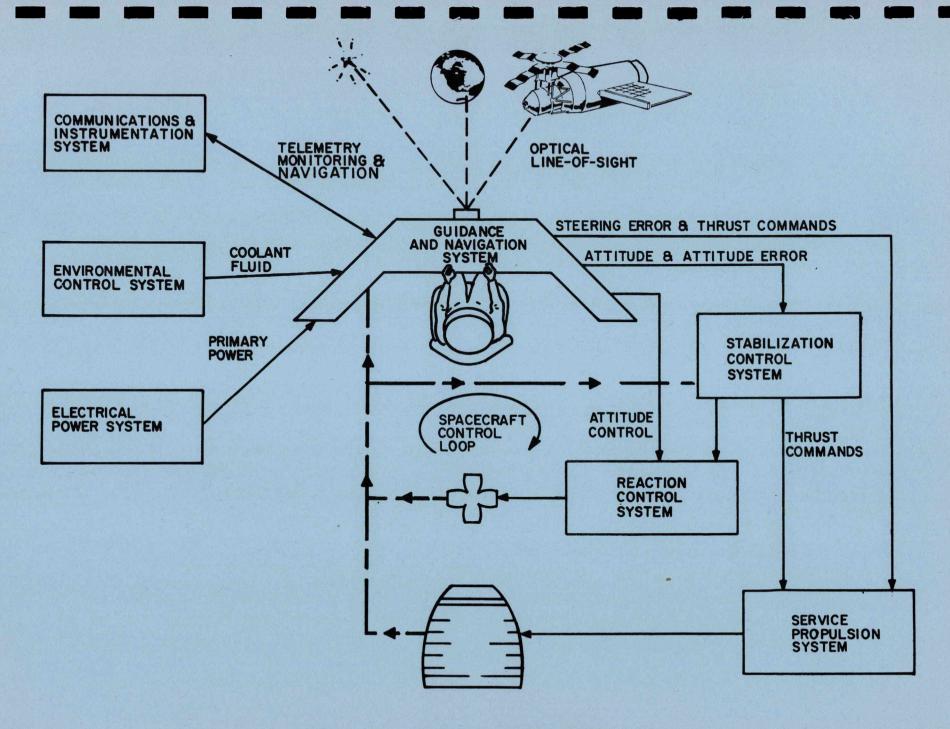

| Block 1.2  |         | S Interface                                    | 1-4  |

|            |         | Spacecraft Systems Interface                   | 1-4  |

|            | 2.1.1   |                                                | 1-4  |

|            | 2.1.2   |                                                | 1-4  |

|            | 2.1.3   |                                                | 1-4  |

|            | 2.1.4   | Electrical Power System                        | 1-6  |

| 1.         | 2.1.5   | Environmental Control System                   | 1-6  |

| 1.         | 2.1.6   | Communication and Instrumentation System       | 1-7  |

| 1.2.       | 2       | Astronaut Interfaces                           | 1-7  |

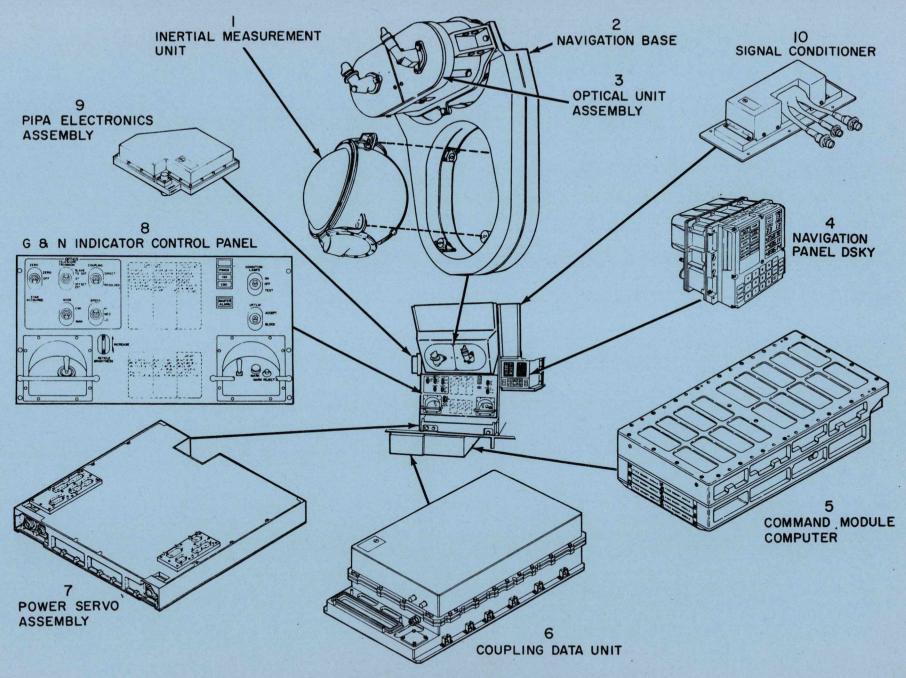

| Block 1.3  | PGNC    | S Subsystems                                   | 1-7  |

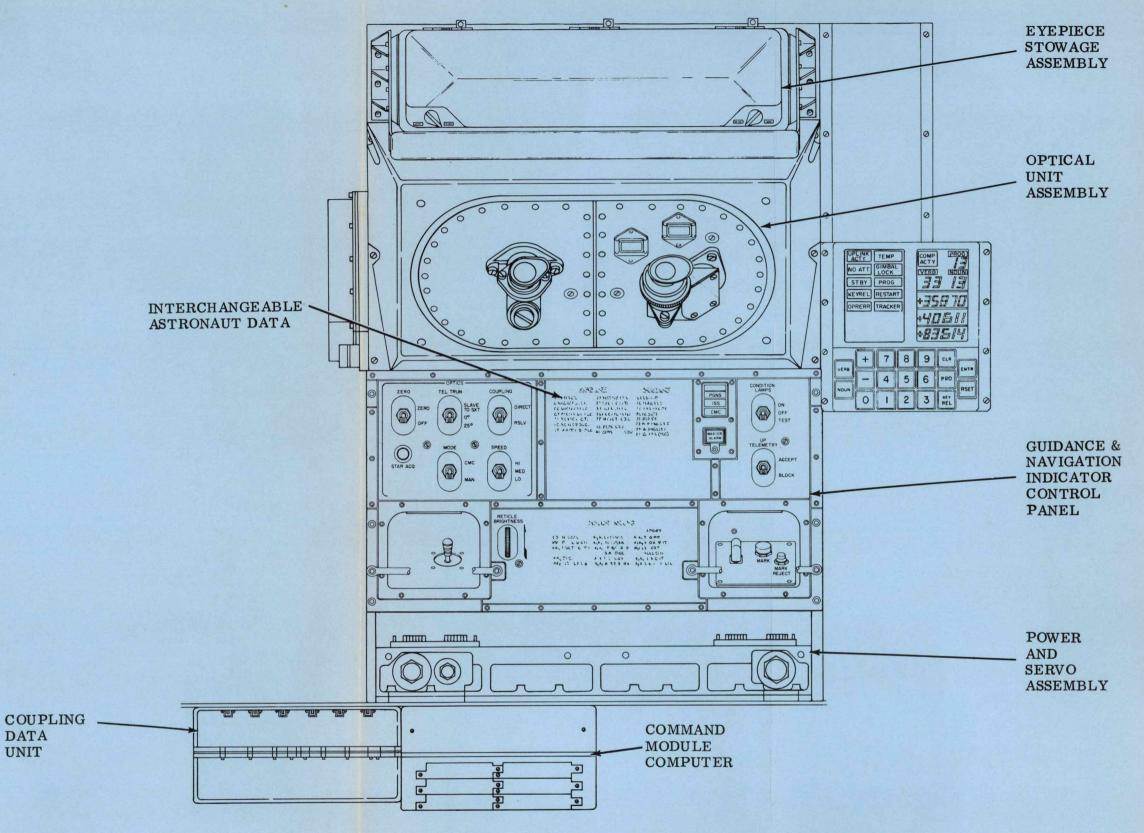

|            |         | PGNCS System Equipment                         | 1-8  |

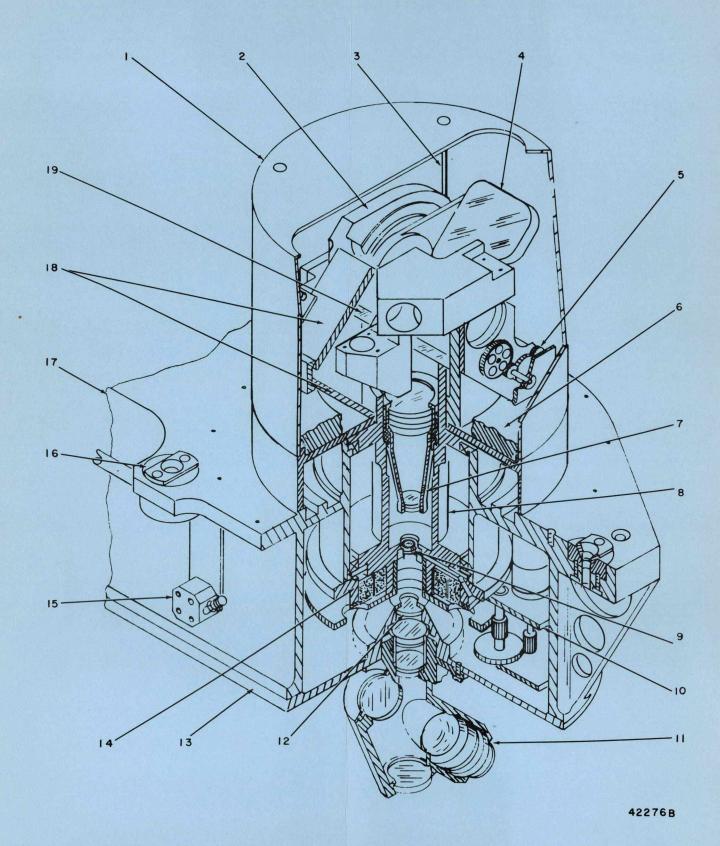

| 1.3.       |         | Inertial Subsystem                             | 1-8  |

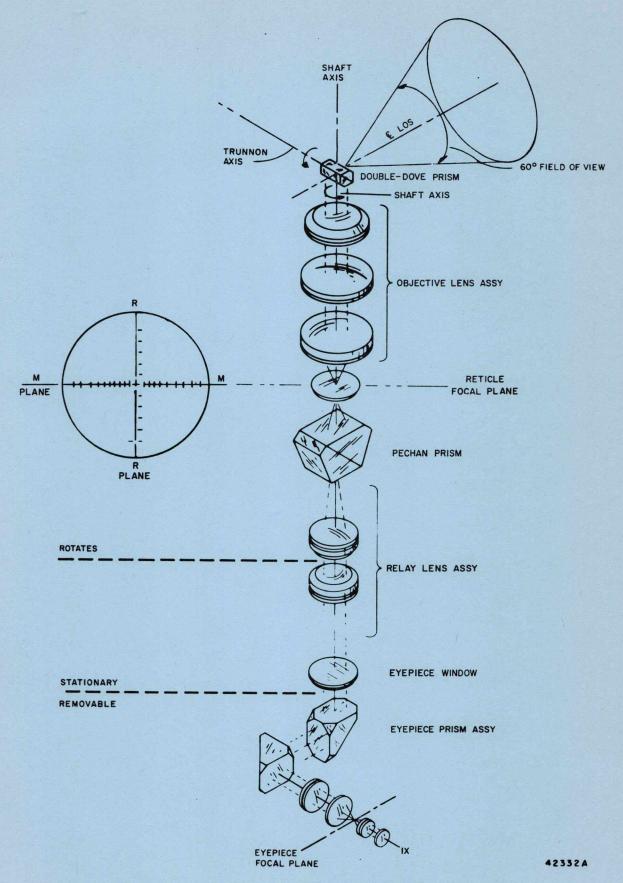

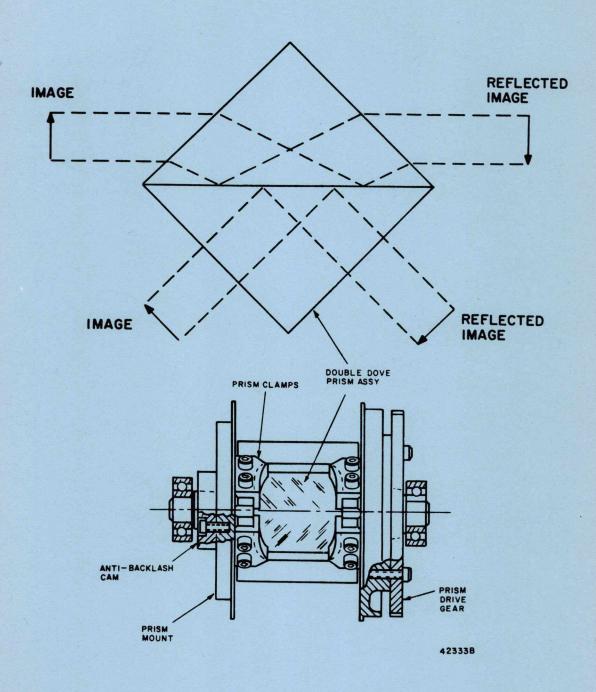

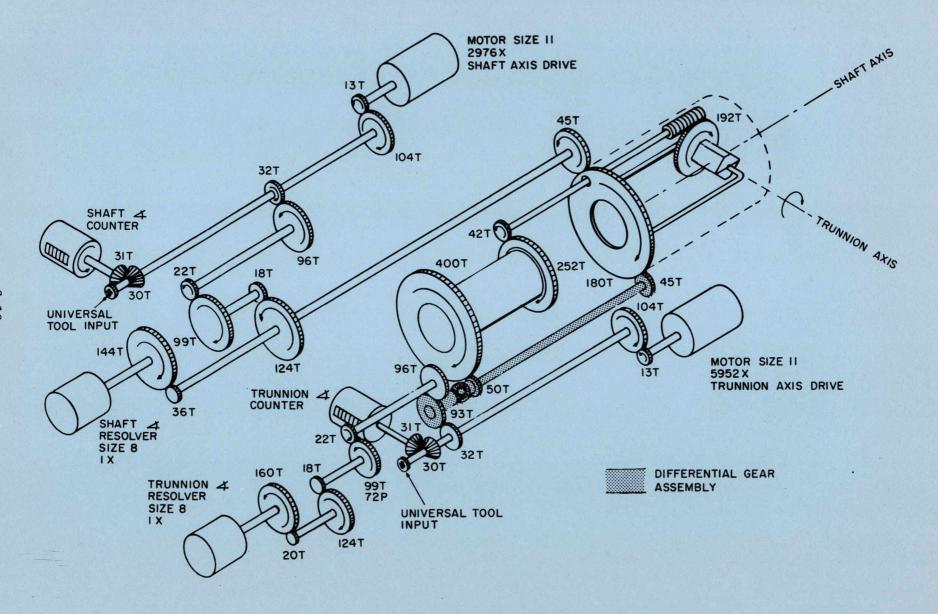

| 1.3.       |         | Optical Subsystem                              | 1-12 |

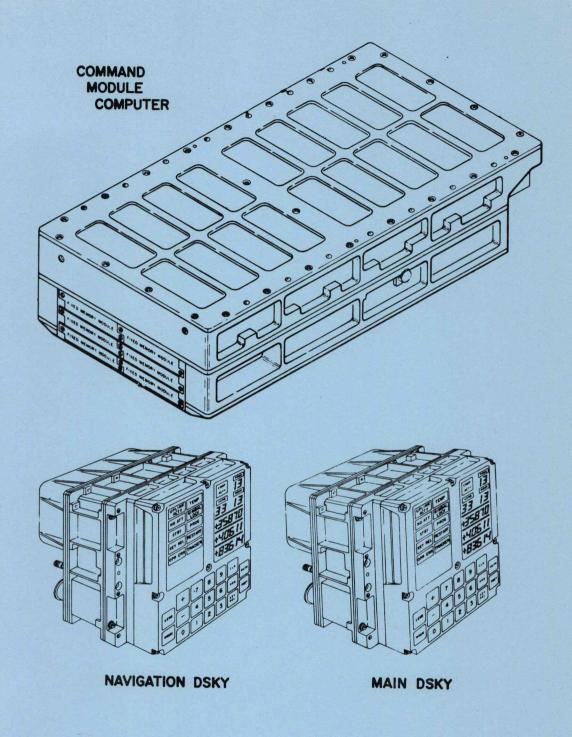

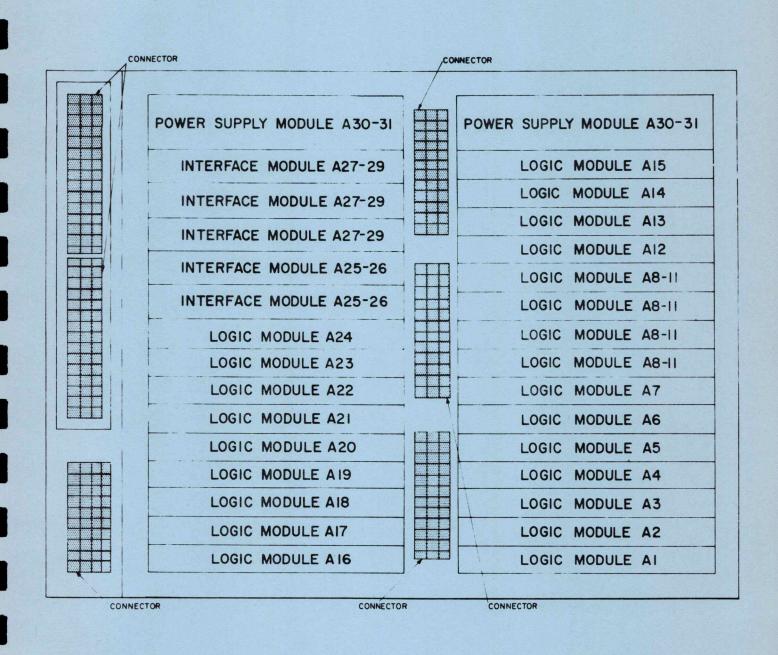

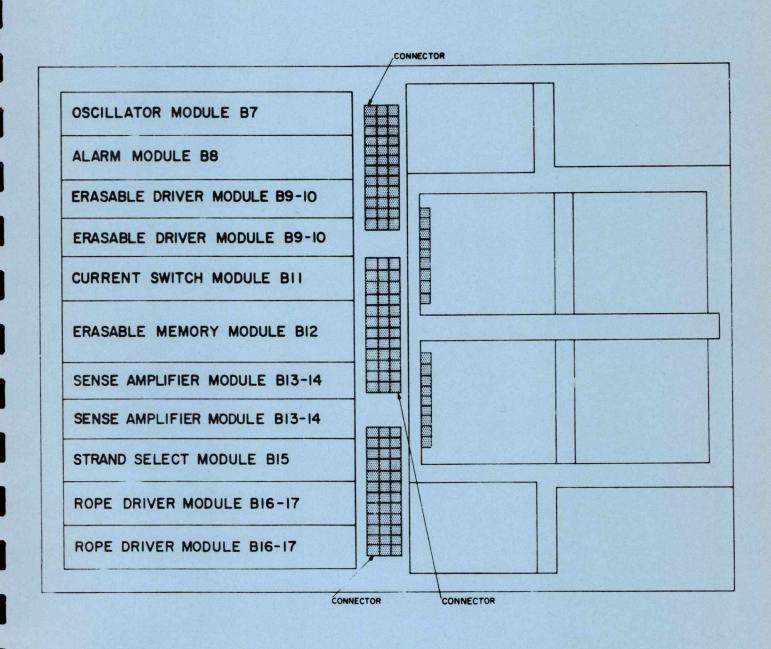

| 1.3.       |         | Computer Subsystem                             | 1-13 |

| Block 1.4  | Summ    | ary                                            | 1-14 |

|            |         |                                                |      |

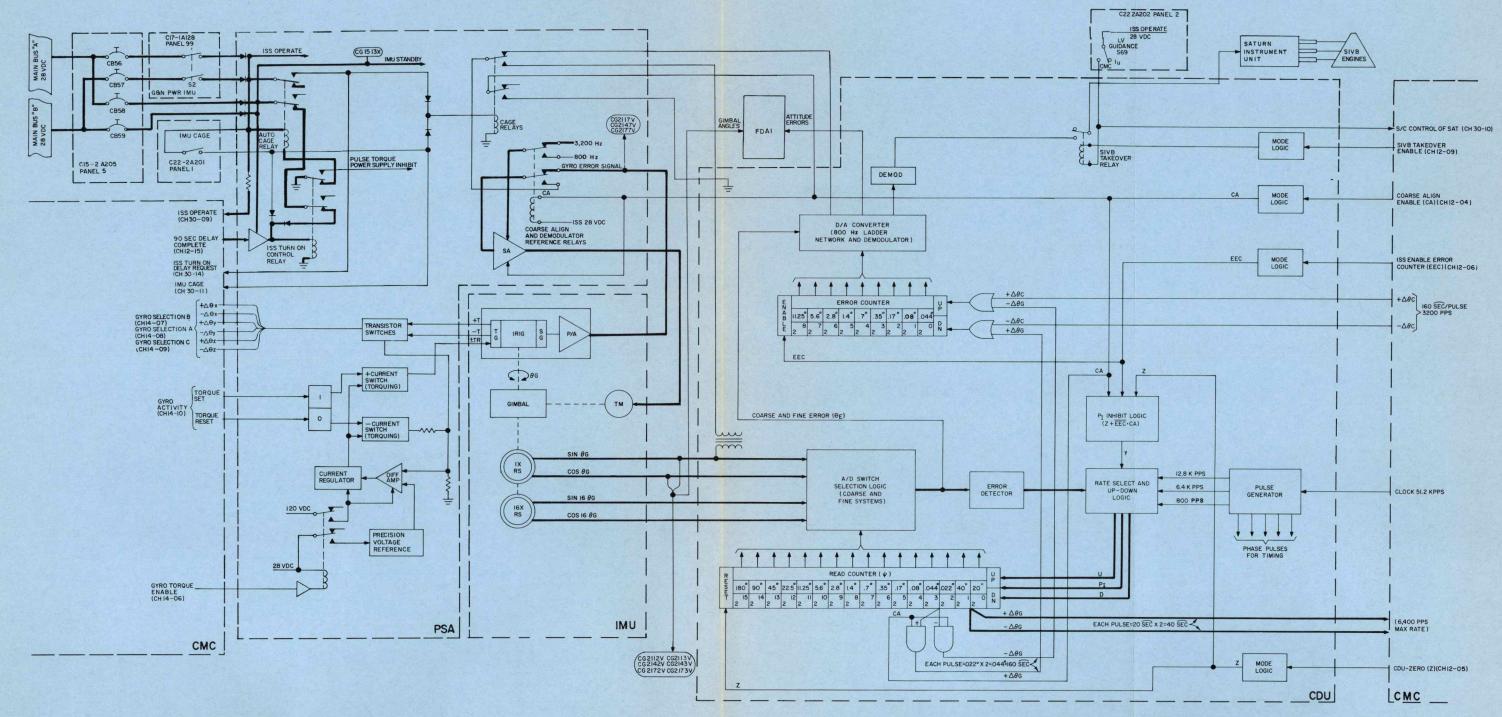

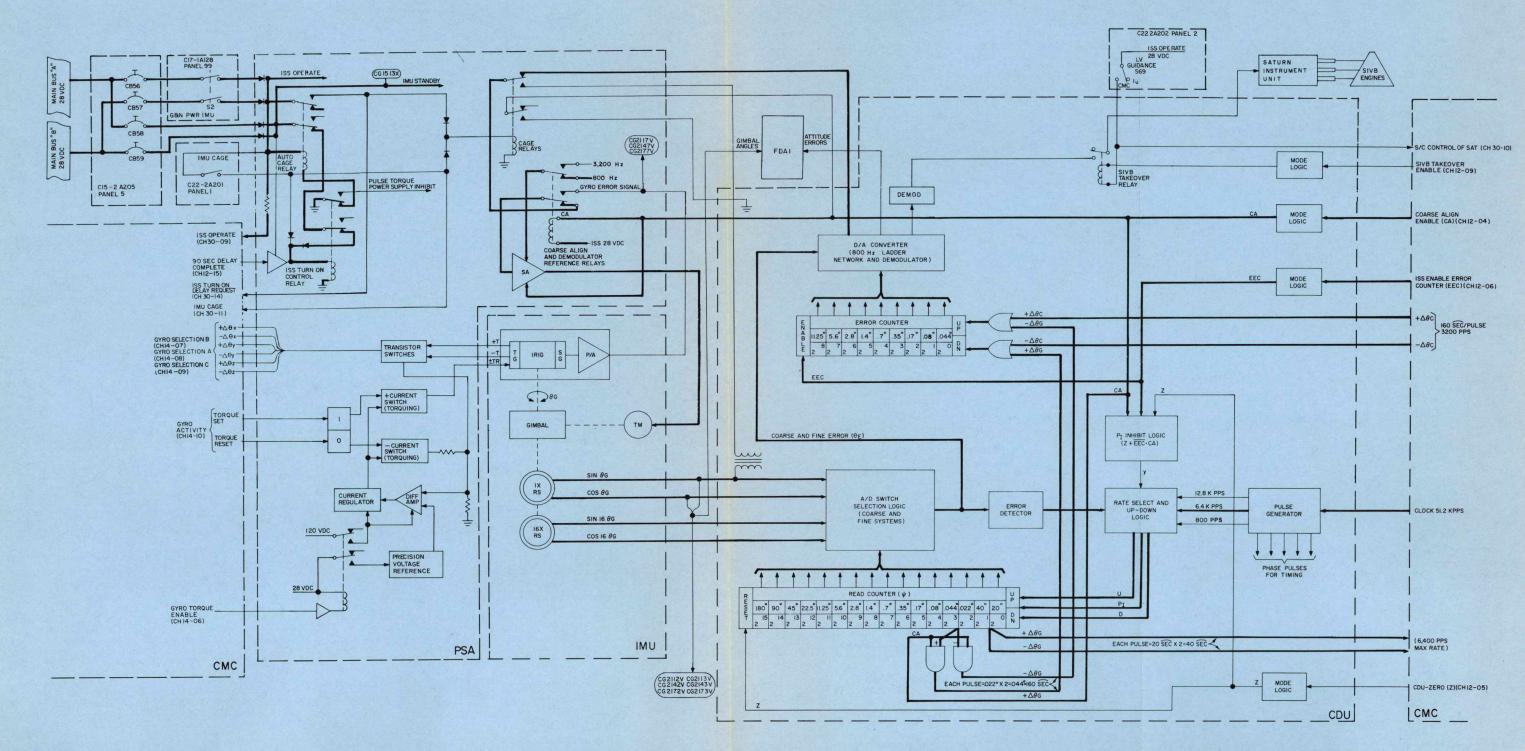

| Section II | Inertia | al Subsystem                                   | 2-1  |

| Block 2.1  | Functi  | ional Description                              | 2-1  |

| 2.1.       | 1       | ISS Alignment and Turnon                       | 2-1  |

| 2.1.       | 2       | Attitude Measurement                           | 2-1  |

| 2.1.       | 3       | Acceleration Measurement                       | 2-1  |

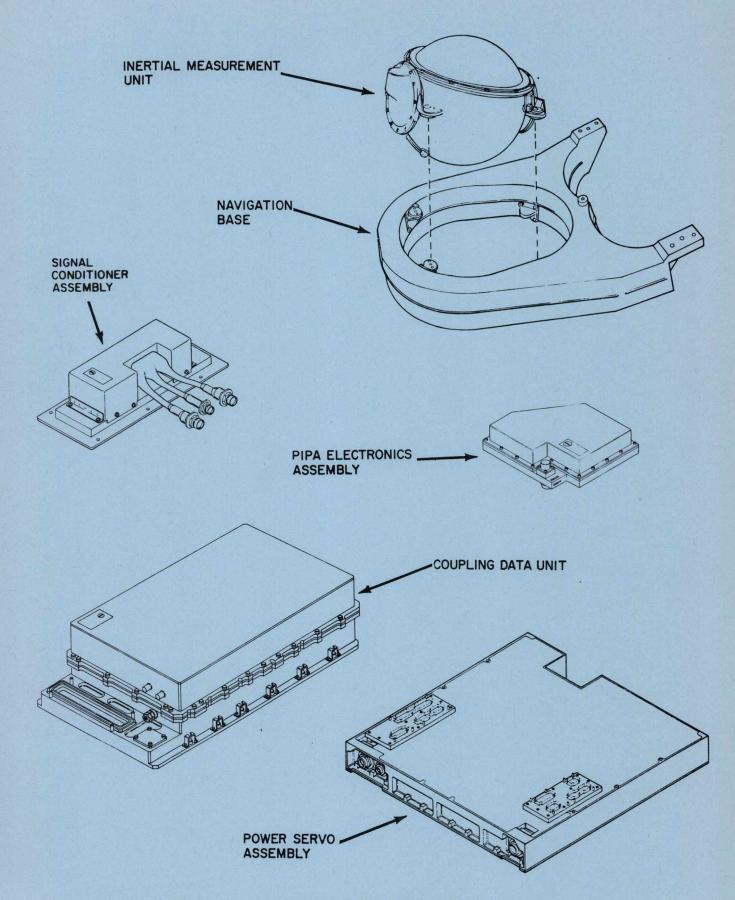

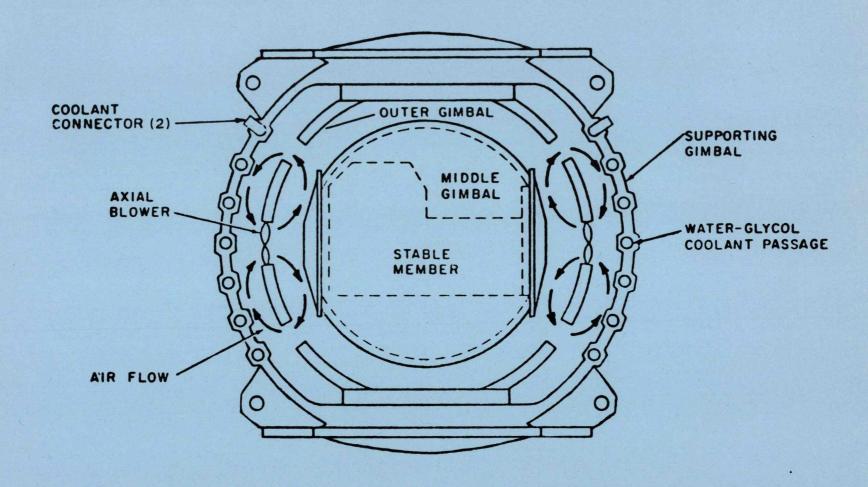

| Block 2.2  | ISS Ec  | quipment                                       | 2-2  |

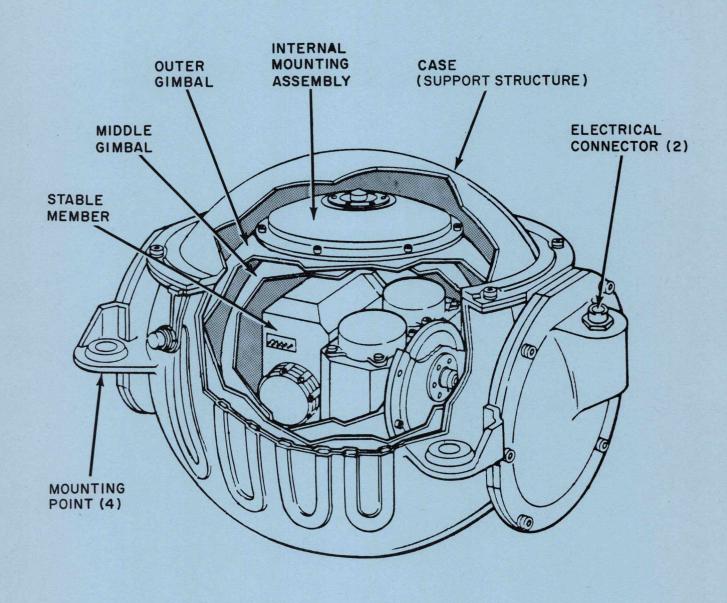

| 2.2.       |         | Inertial Measurement Unit                      | 2-2  |

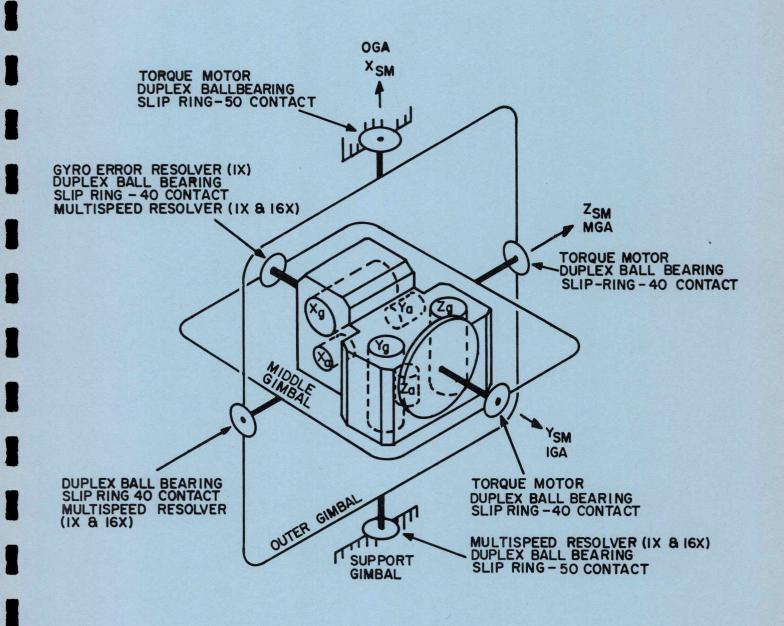

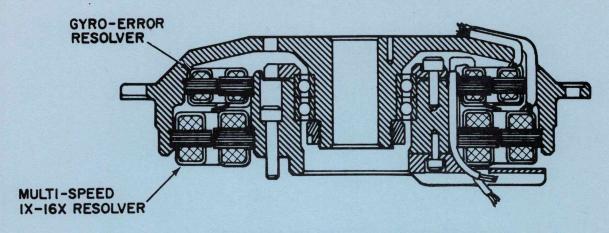

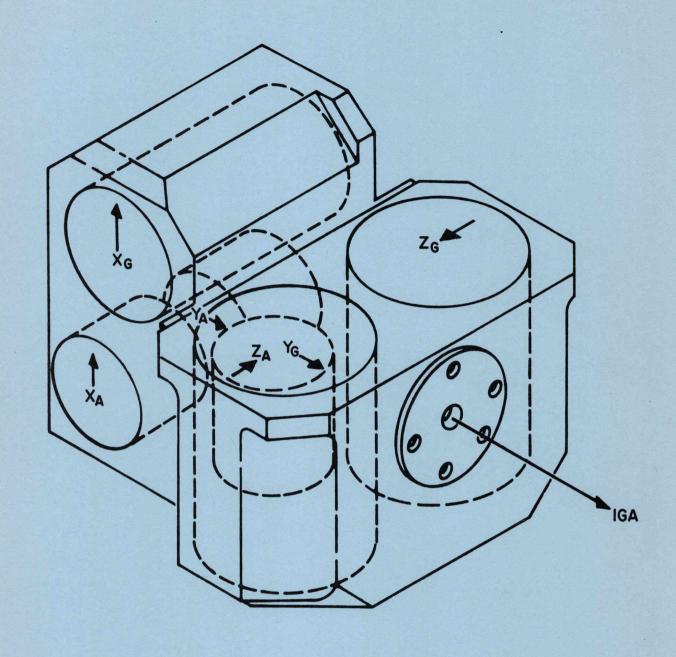

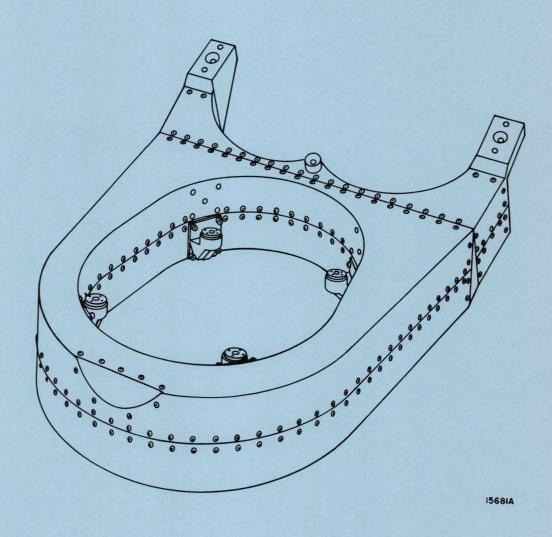

|            | 2.1.1   | Inter-gimbal Assembly                          | 2-6  |

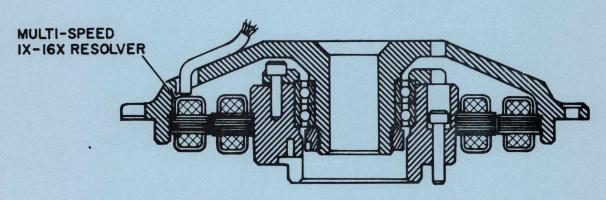

|            | 2.1.2   | Middle Gimbal                                  | 2-6  |

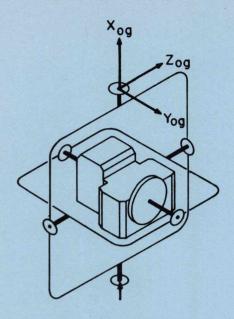

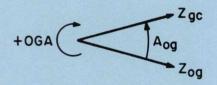

|            | 2.1.3   | Outer Gimbal                                   | 2-8  |

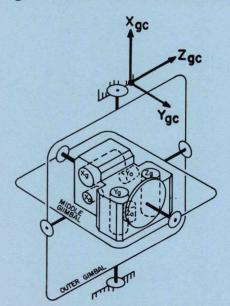

|            | 2.1.4   | Gimbal Case                                    | 2-8  |

|            | 2.1.5   | Stable Member                                  | 2-8  |

| 2.2.       |         | Navigation Base                                | 2-10 |

| 2.2.       |         | PIP Electronics Assembly                       | 2-10 |

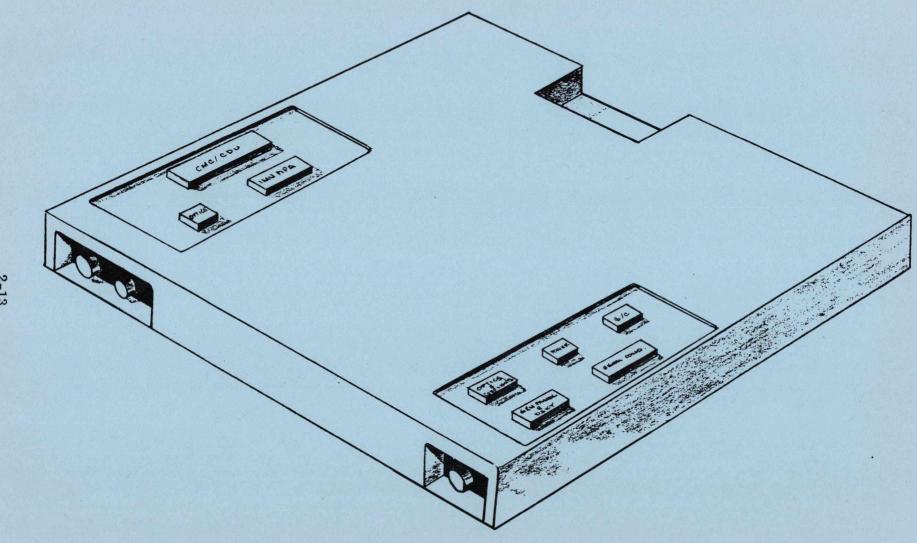

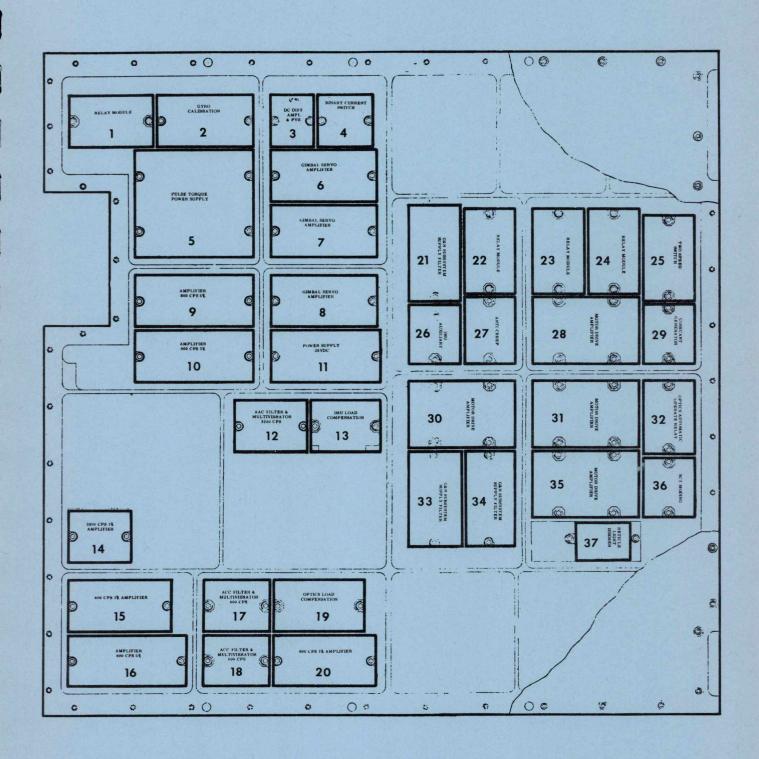

| 2.2.       |         | Power and Servo Assembly                       | 2-10 |

| 2.2.       |         | Coupling Data Unit                             | 2-10 |

| 2.2.       |         | Signal Conditioner Assembly                    | 2-10 |

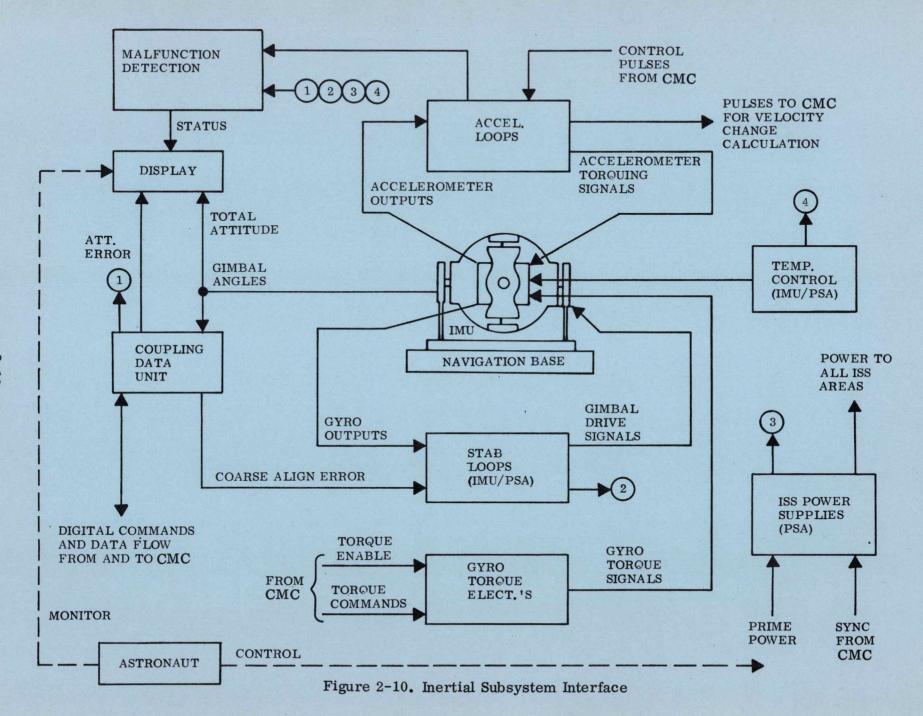

| Block 2.3 ISS F  | unctions and Interface                                                                                     | 2-10 |

|------------------|------------------------------------------------------------------------------------------------------------|------|

| 2.3.1            | Navigation Base (NB)                                                                                       | 2-18 |

| 2.3.2            | Inertial Measurement Unit (IMU)                                                                            | 2-18 |

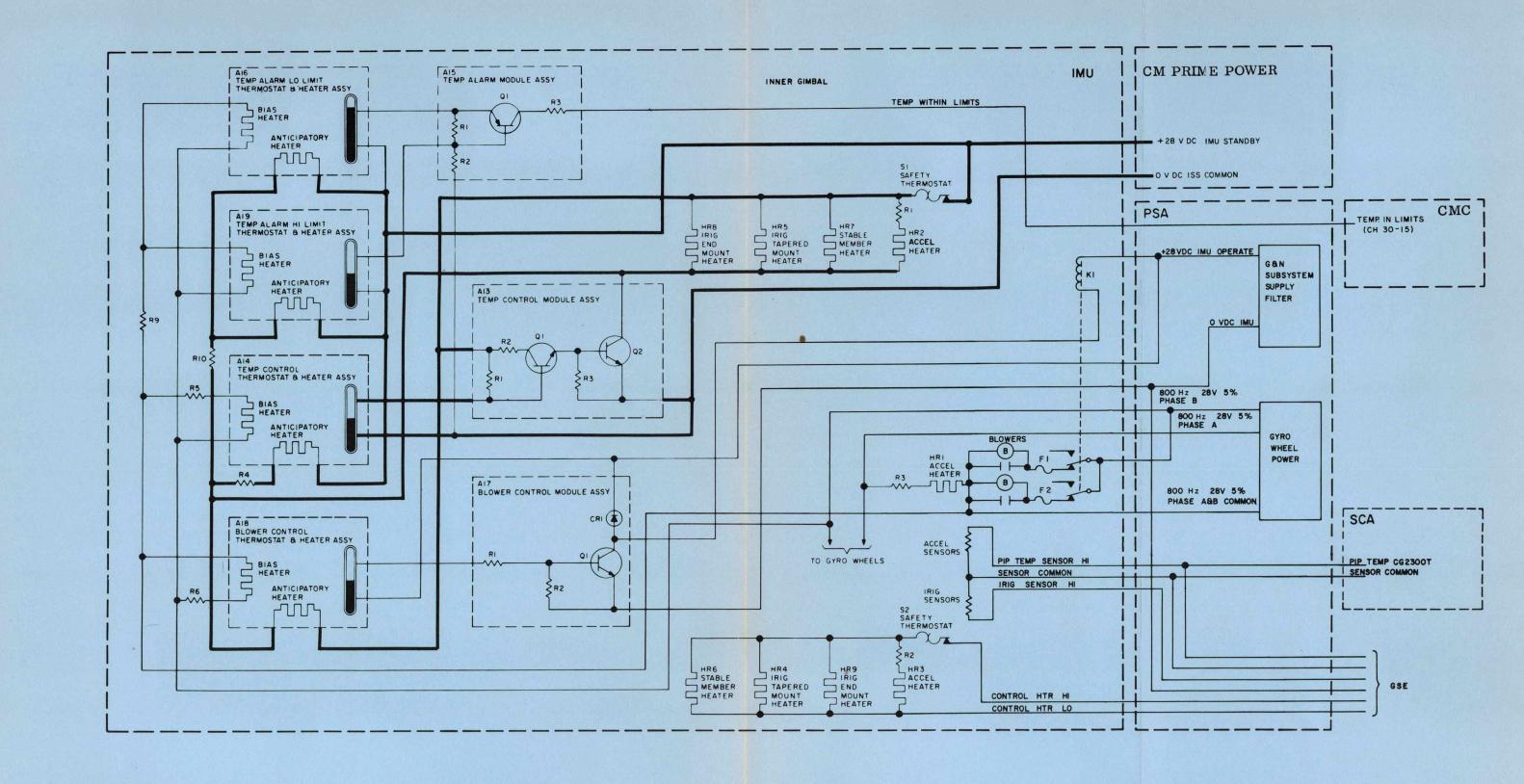

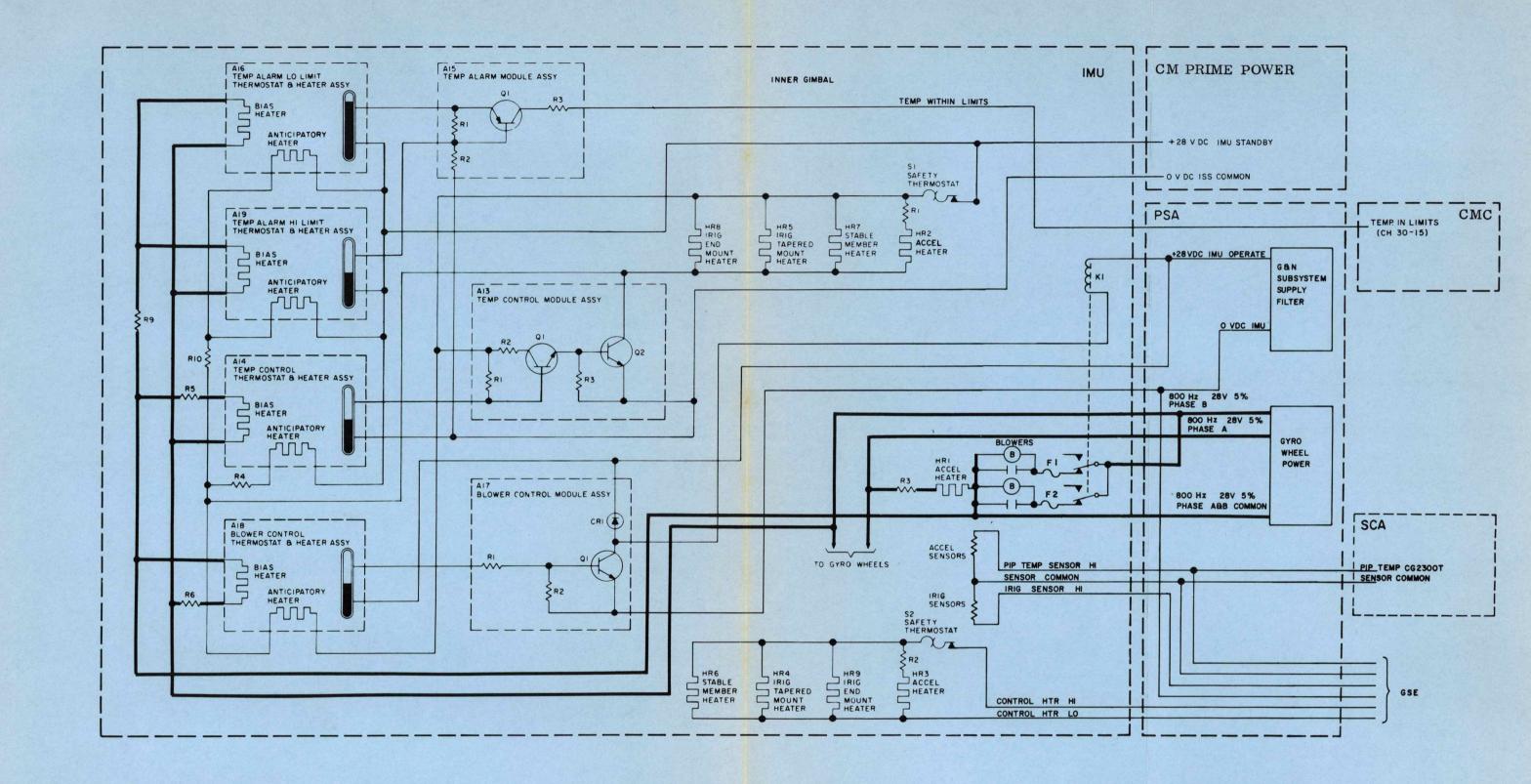

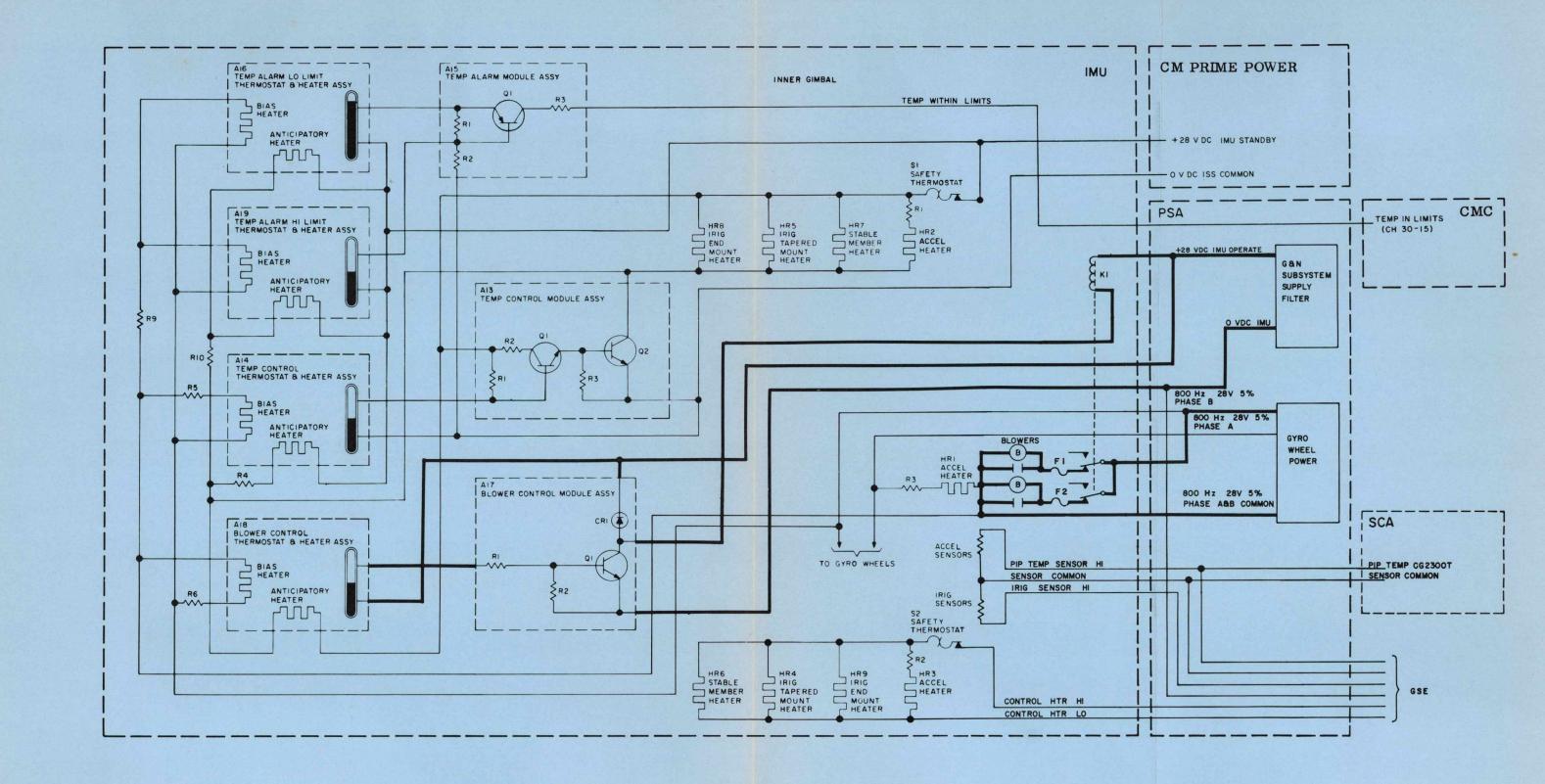

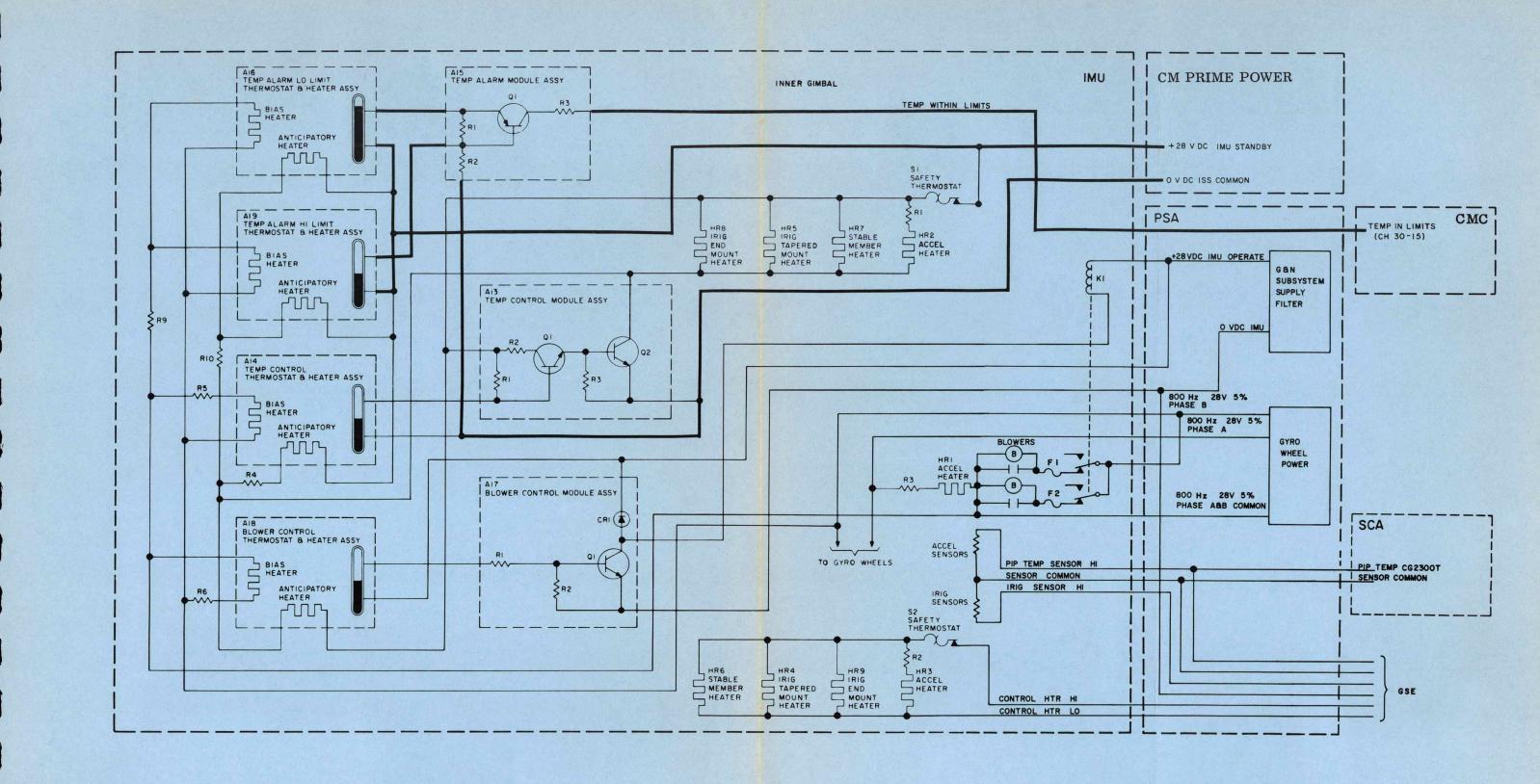

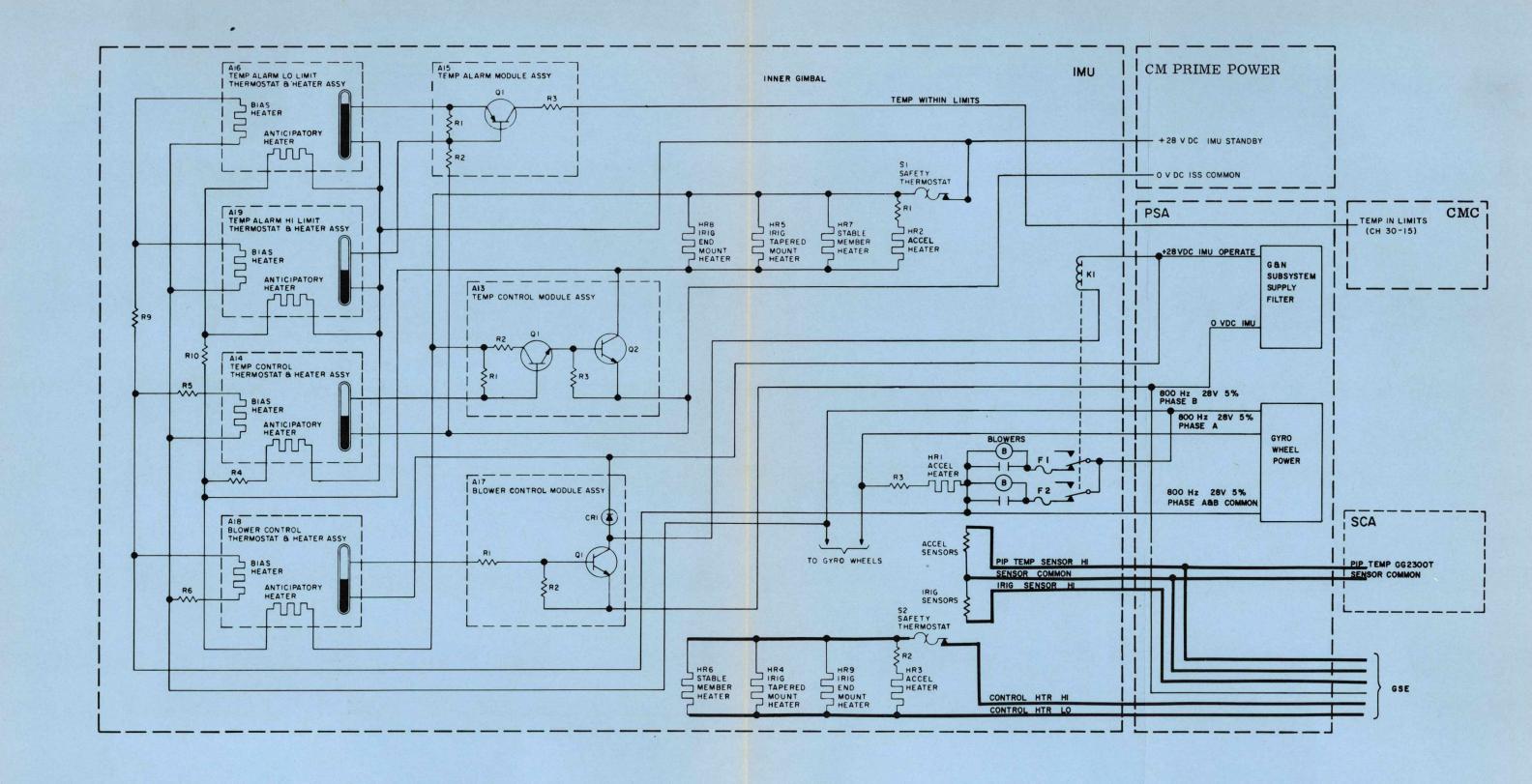

| 2.3.3            | Temperature Control System                                                                                 | 2-18 |

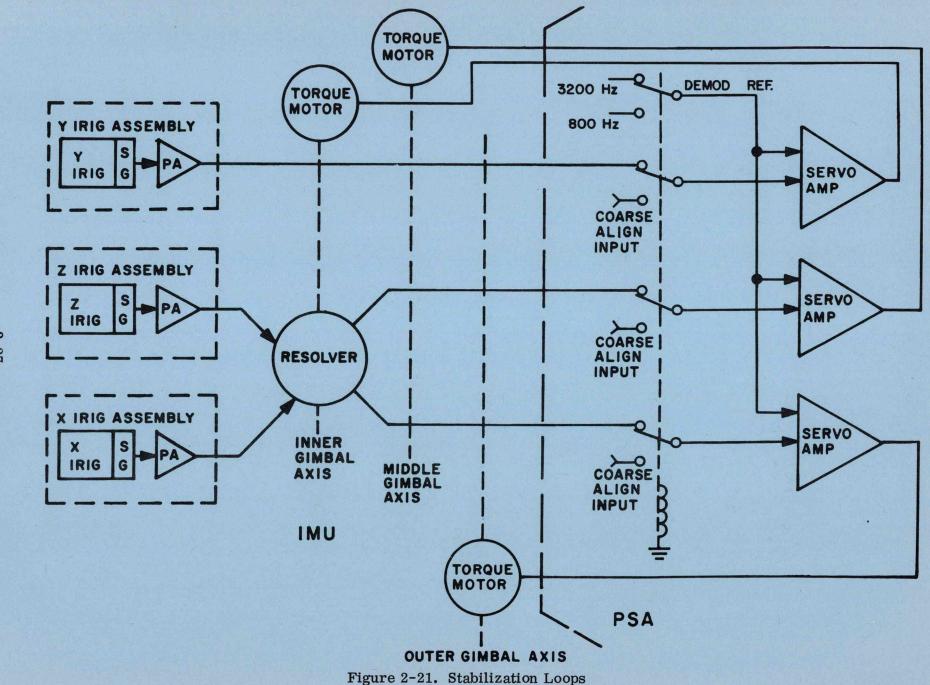

| 2.3.4            | Stabilization Loop                                                                                         | 2-20 |

| 2.3.5            | Fine Align Electronics                                                                                     | 2-20 |

| 2.3.6            |                                                                                                            | 2-20 |

| 2.3.7            | Accelerometer Loops                                                                                        | 2-21 |

|                  | Coupling Data Unit                                                                                         | 2-21 |

| 2.3.8            | Power Supplies  Molfunction Detection Circuits                                                             | 2-21 |

| 2.3.9            | Malfunction Detection Circuits                                                                             | 2-21 |

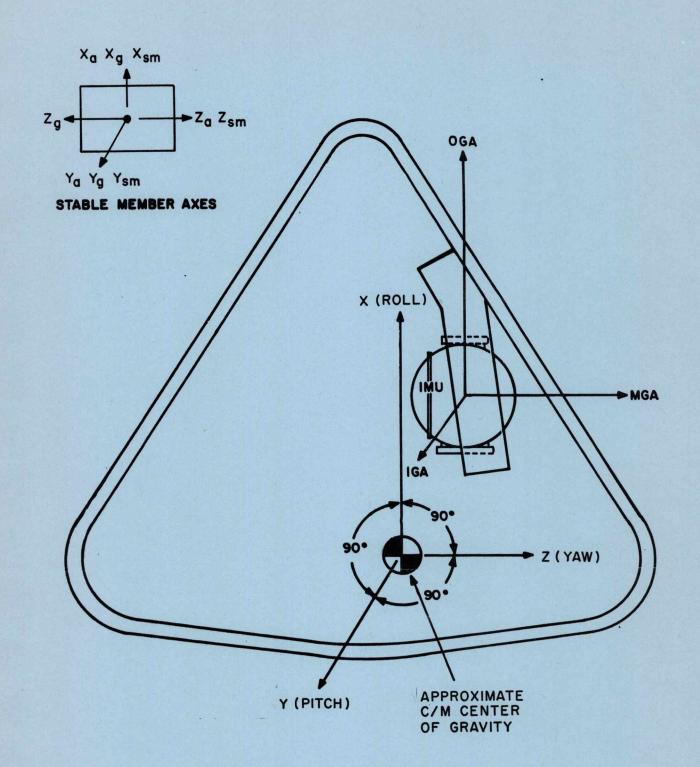

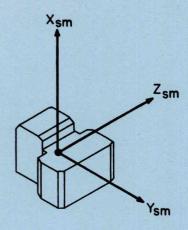

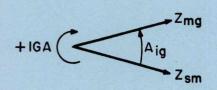

| Block 2.4 Axes   |                                                                                                            | 2-21 |

| Block 2.5 Stabi  |                                                                                                            | 2-26 |

| 2.5.1            | Stabilization Loop Operation                                                                               | 2-26 |

| 2.5.2            | Stabilization Loop Mechanization                                                                           | 2-28 |

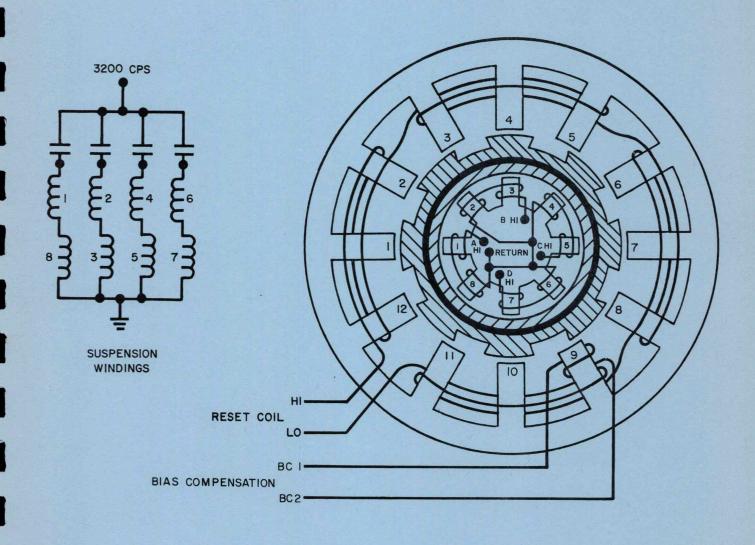

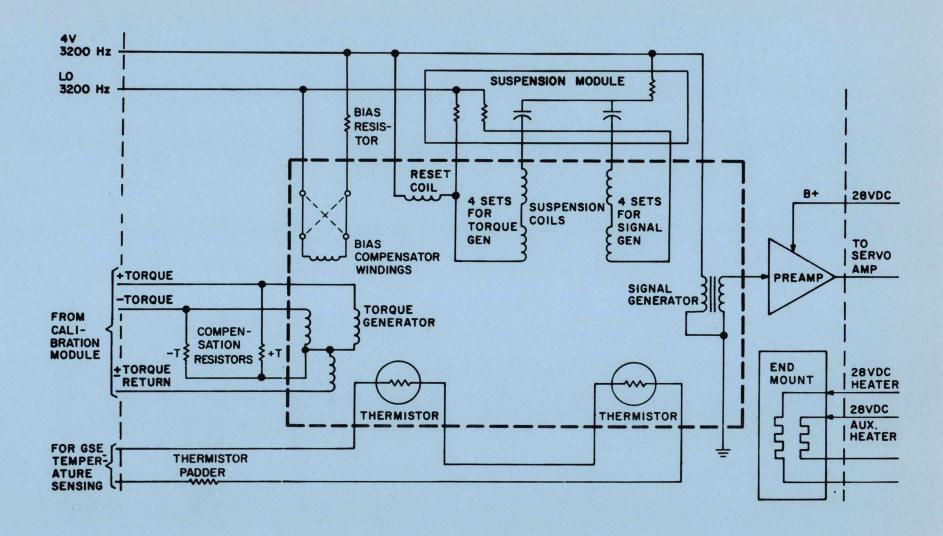

| 2.5.2.1          |                                                                                                            | 2-30 |

| 2.5.2.2          | 위한 것으로 가스스 및 CHRONO 및 NOTE 및 NOTE 및 기능적으로 가는 것으로 CHRONO 및 기능적으로 있는데, 이번 사용 전기에 바다가 되는데 가능한다고 있는데, 기능에 되었다. | 2-33 |

| 2.5.2.3          | Normalization Package                                                                                      | 2-40 |

| 2.5.2.4          | IRIG Preamplifier                                                                                          | 2-40 |

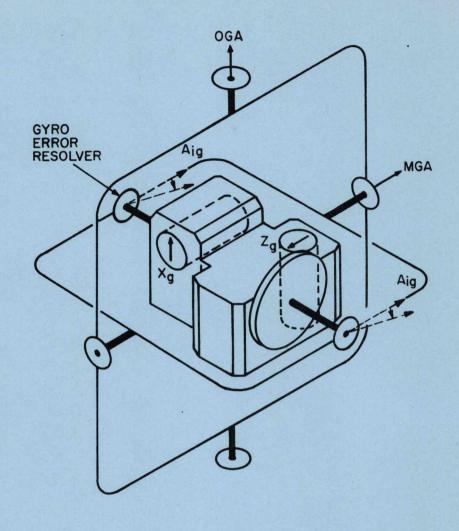

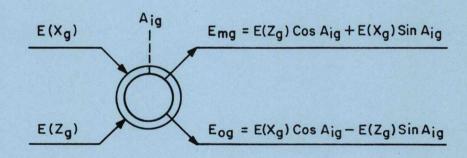

| 2.5.2.5          | Gyro Error Resolver                                                                                        | 2-40 |

| 2.5.2.6          | Gimbal Servo Amplifier (GSA)                                                                               | 2-40 |

| 2.5.2.7          | Torque Motor                                                                                               | 2-43 |

| Block 2.6 Fine   | Align Electronics                                                                                          | 2-43 |

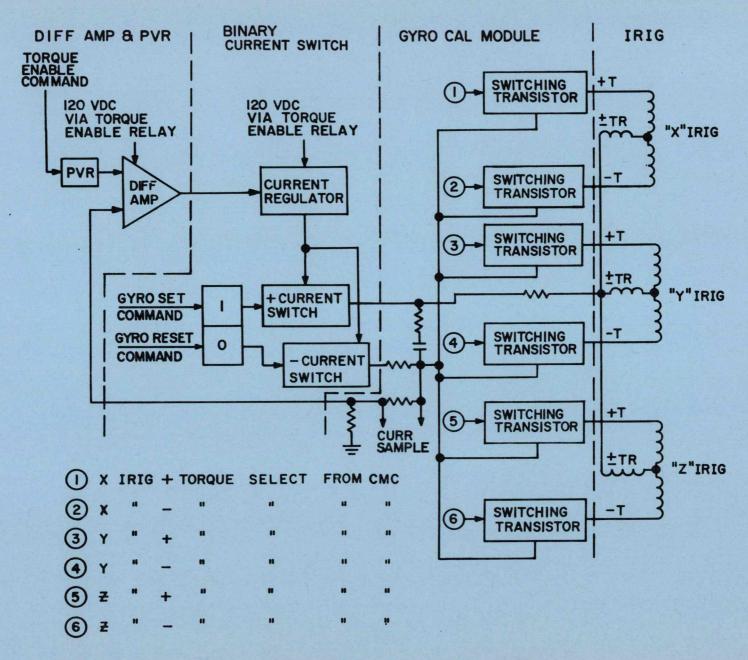

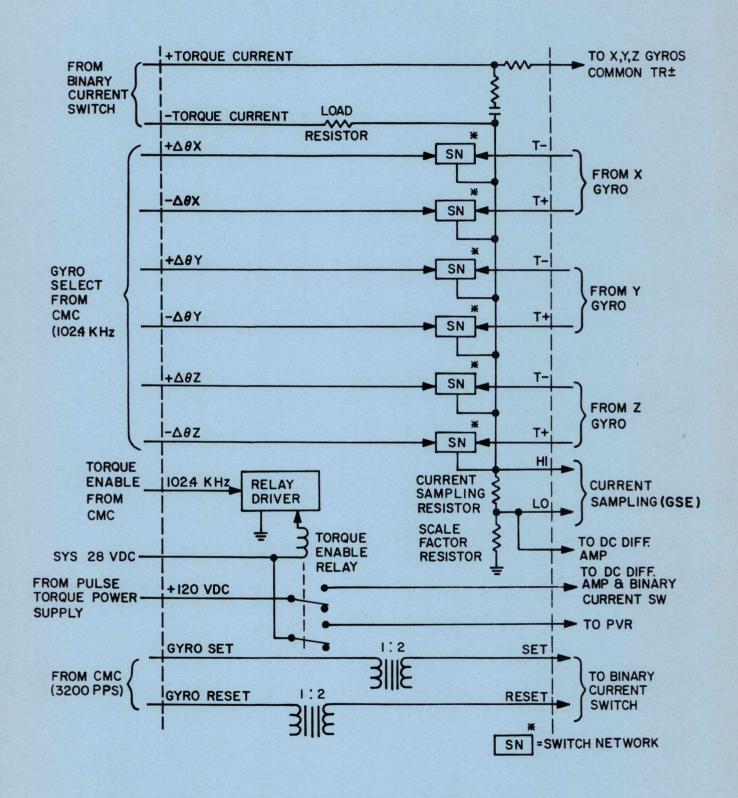

| 2.6.1            | Gyro Calibration Module                                                                                    | 2-46 |

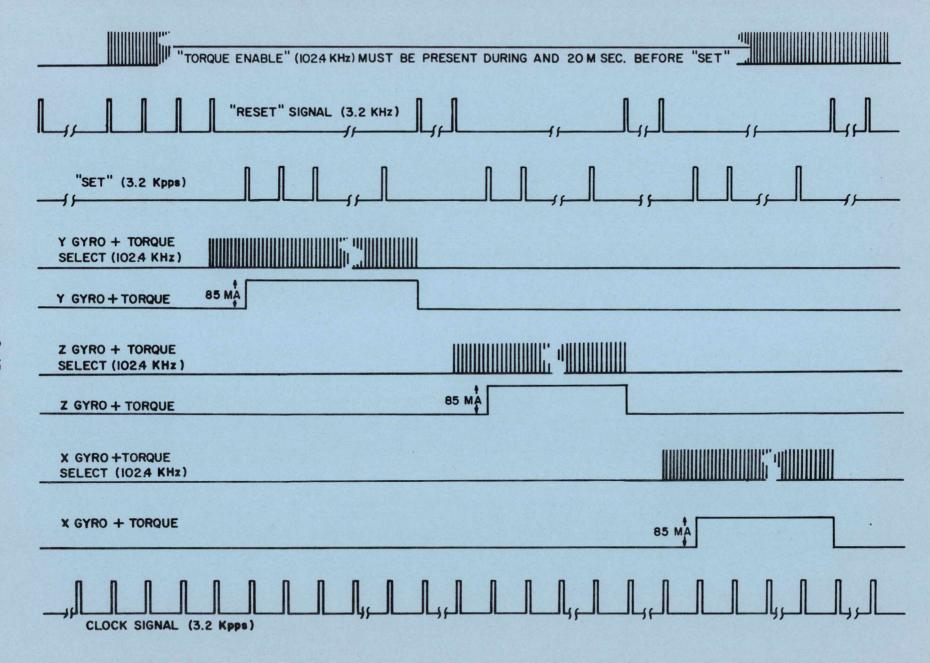

| 2.6.1.1          | Torque Enable Relay                                                                                        | 2-46 |

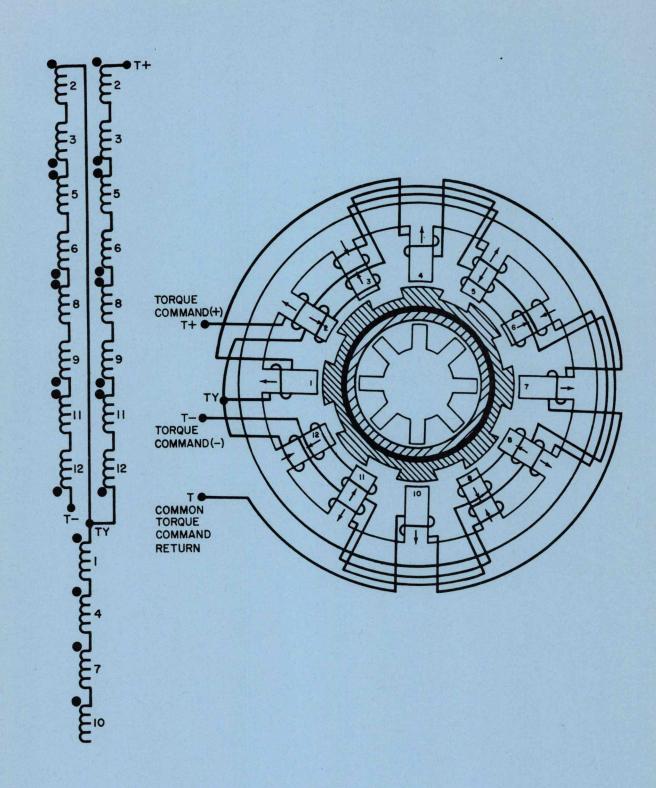

| 2.6.1.2          | Torque Winding Selection Switches                                                                          | 2-46 |

| 2.6.1.3          | Compensation and Dummy Load Resistors                                                                      | 2-46 |

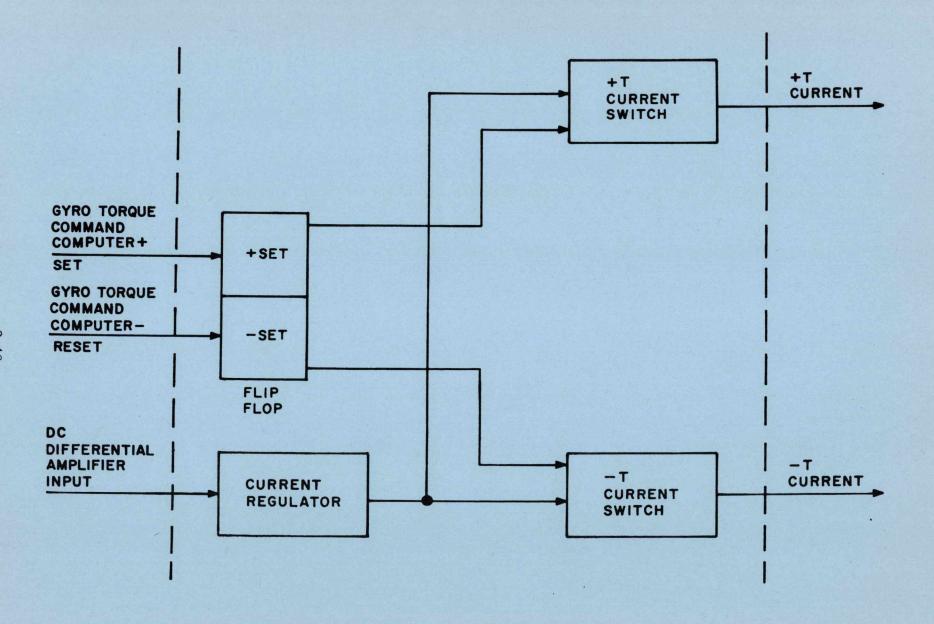

| 2.6.2            | Binary Current Switch                                                                                      | 2-46 |

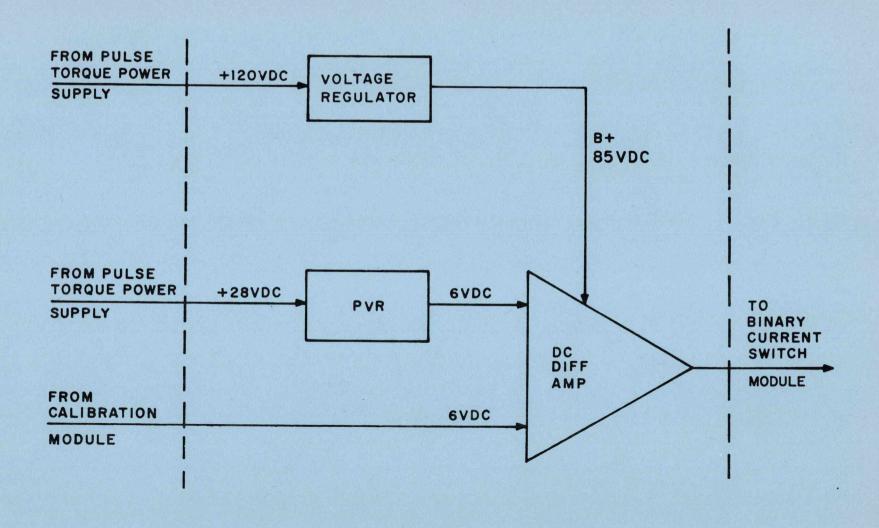

| 2.6.3            | Constant Current Supply                                                                                    | 2-46 |

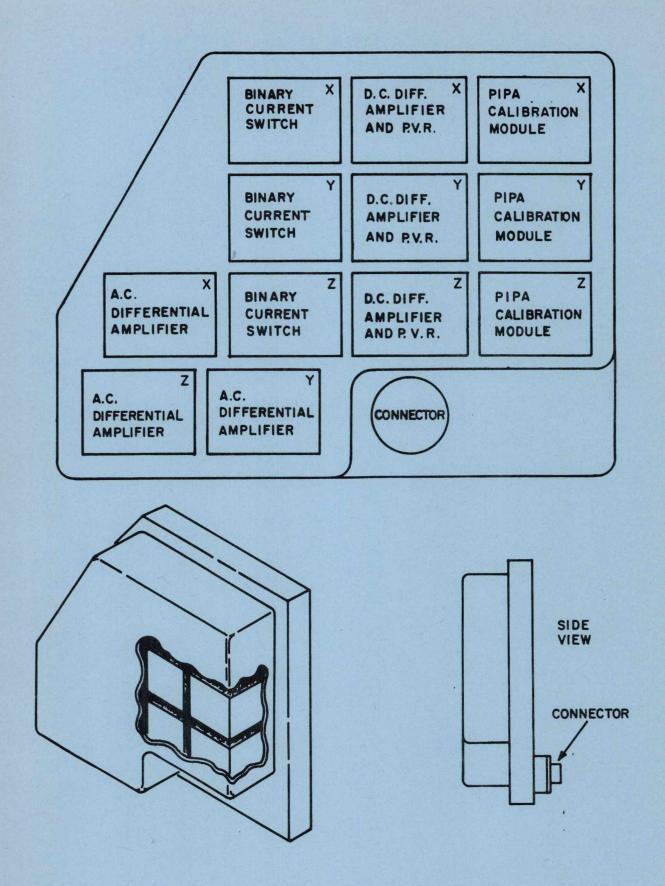

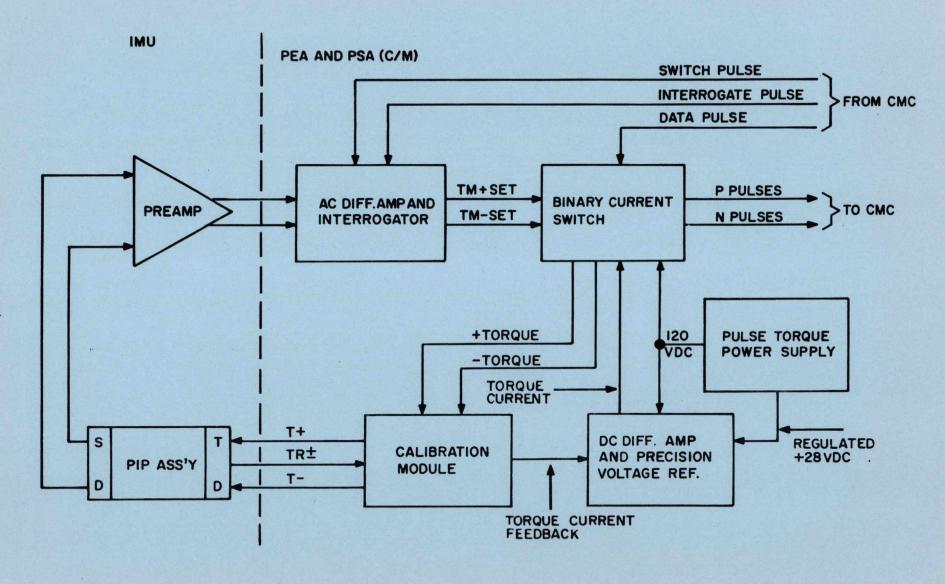

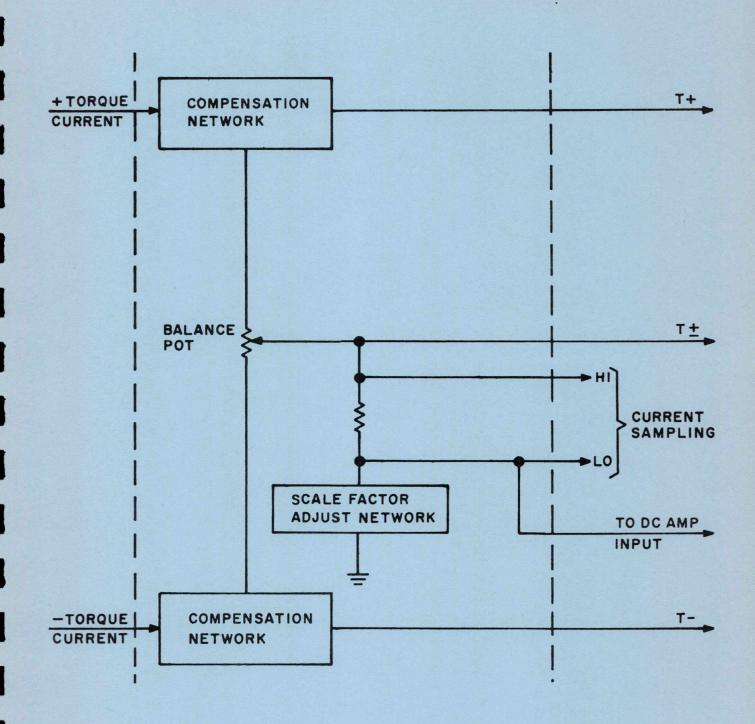

| Block 2.7 Acce   | lerometer Loop                                                                                             | 2-50 |

| 2.7.1            |                                                                                                            | 2-52 |

| 2.7.2            | Accelerometer Loop Mechanization                                                                           | 2-53 |

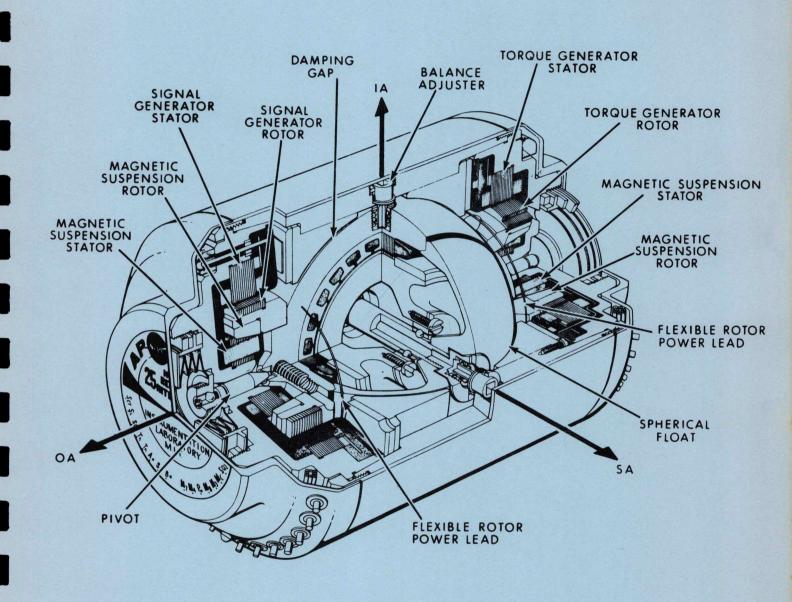

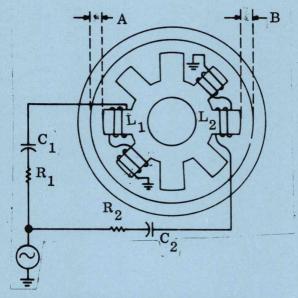

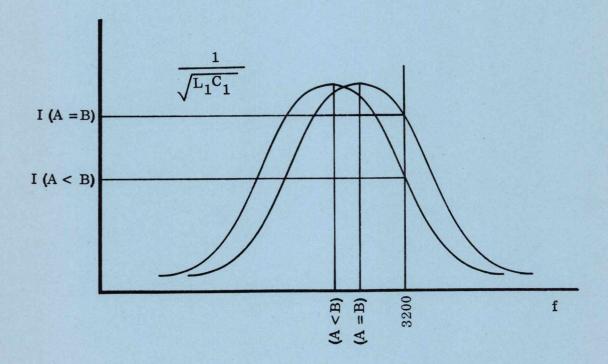

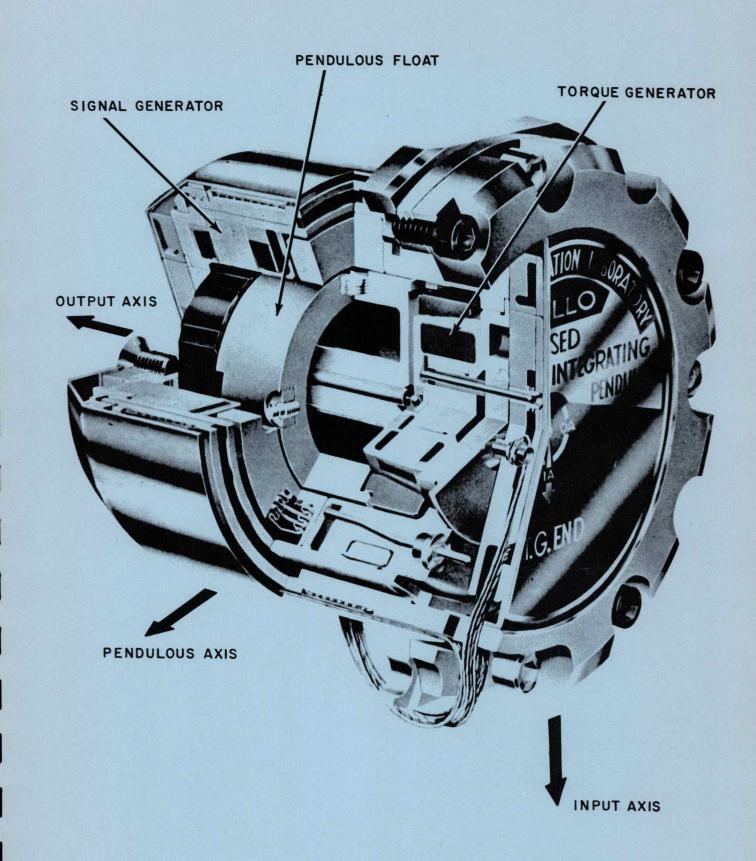

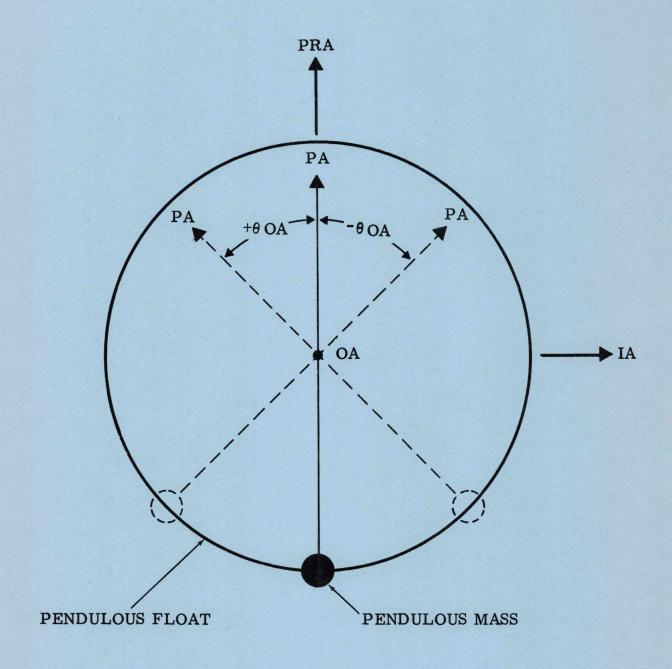

| 2.7.2.1          | Pulse Integrating Pendulum                                                                                 | 2-53 |

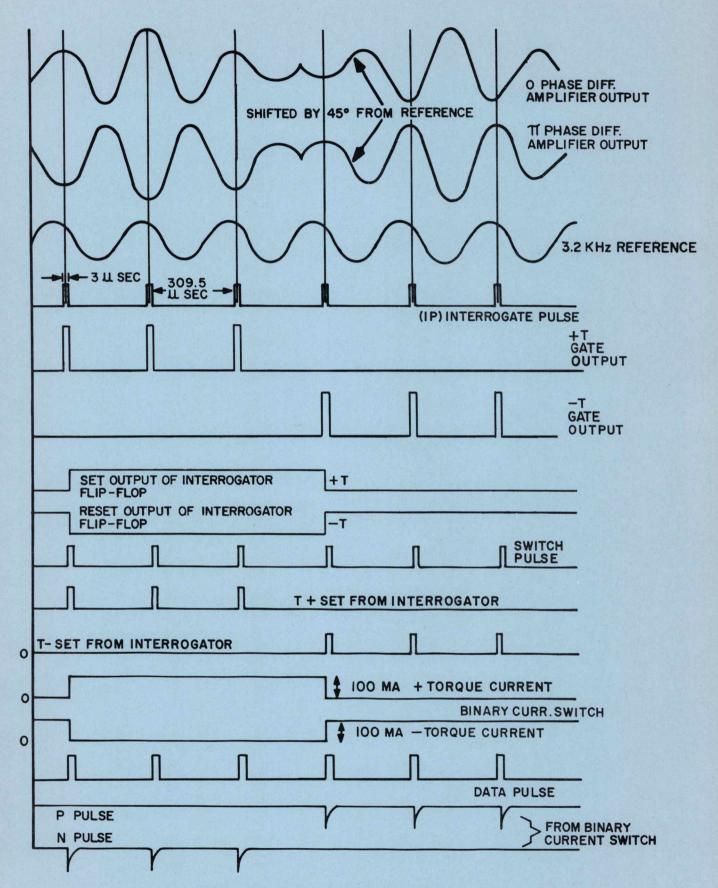

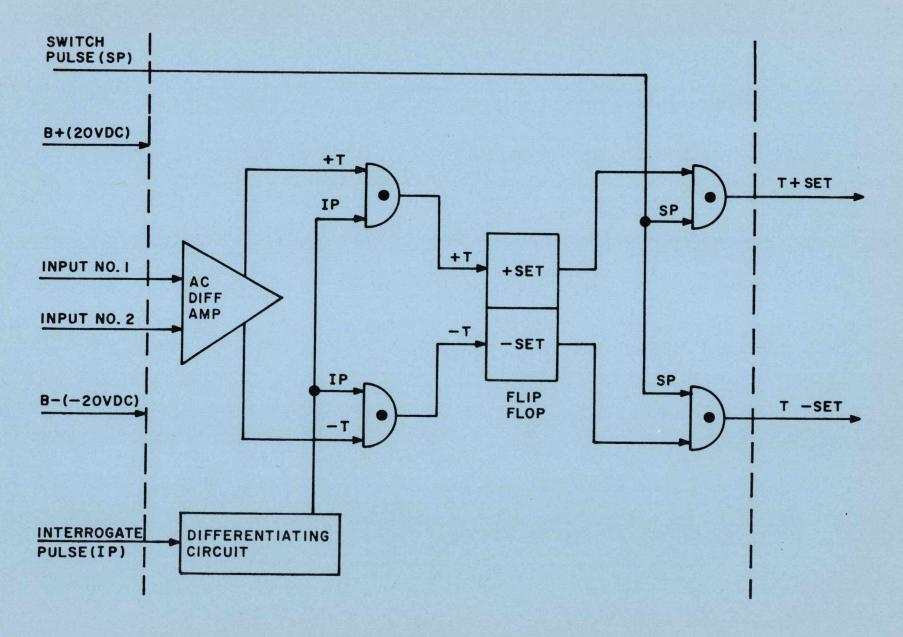

| 2.7.2.2          | AC Differential Amplifier and Interrogator Module                                                          | 2-59 |

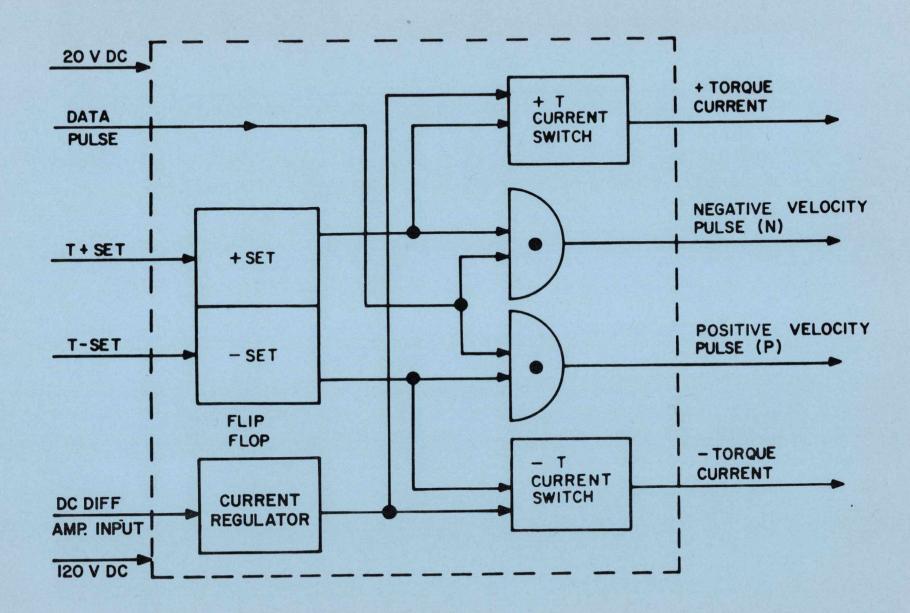

| 2.7.2.3          | Binary Current Switch                                                                                      | 2-59 |

| 2.7.2.4          | PIPA Calibration Module                                                                                    | 2-63 |

| 2.7.2.5          | Constant Current Supply                                                                                    | 2-63 |

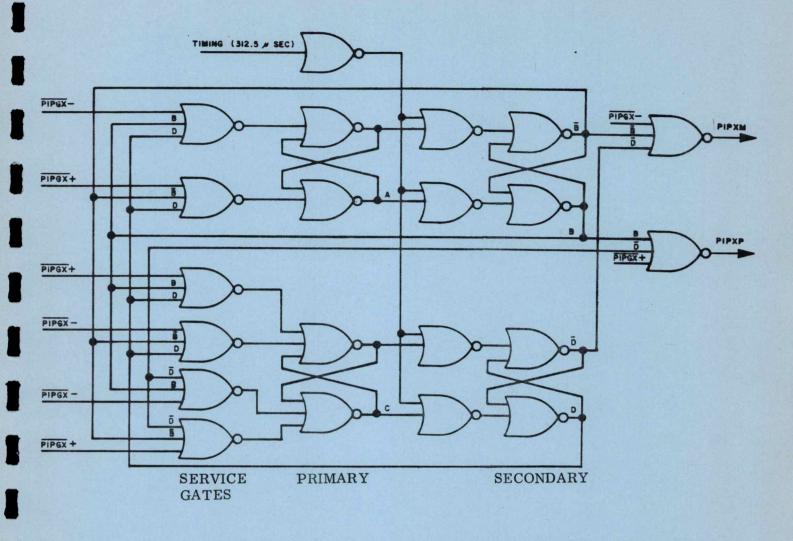

| 2.7.2.6          | Forward-Backward Counter                                                                                   | 2-63 |

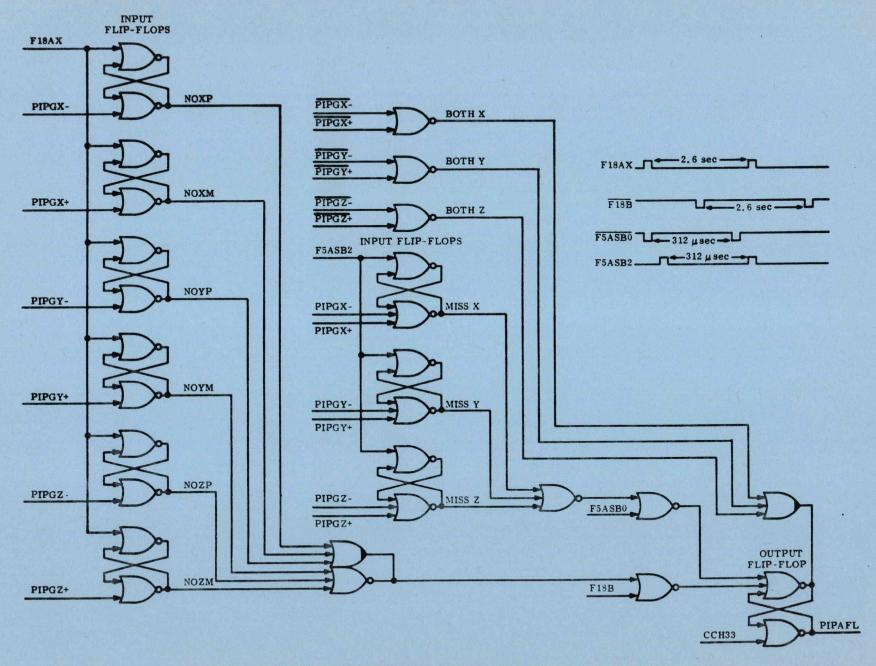

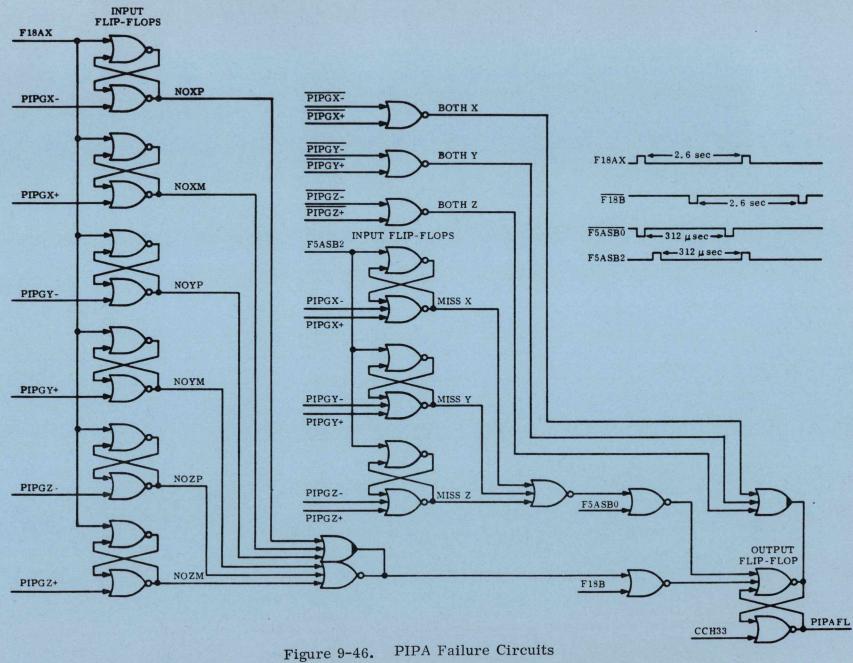

| 2.7.2.7          | PIPA Failure                                                                                               | 2-66 |

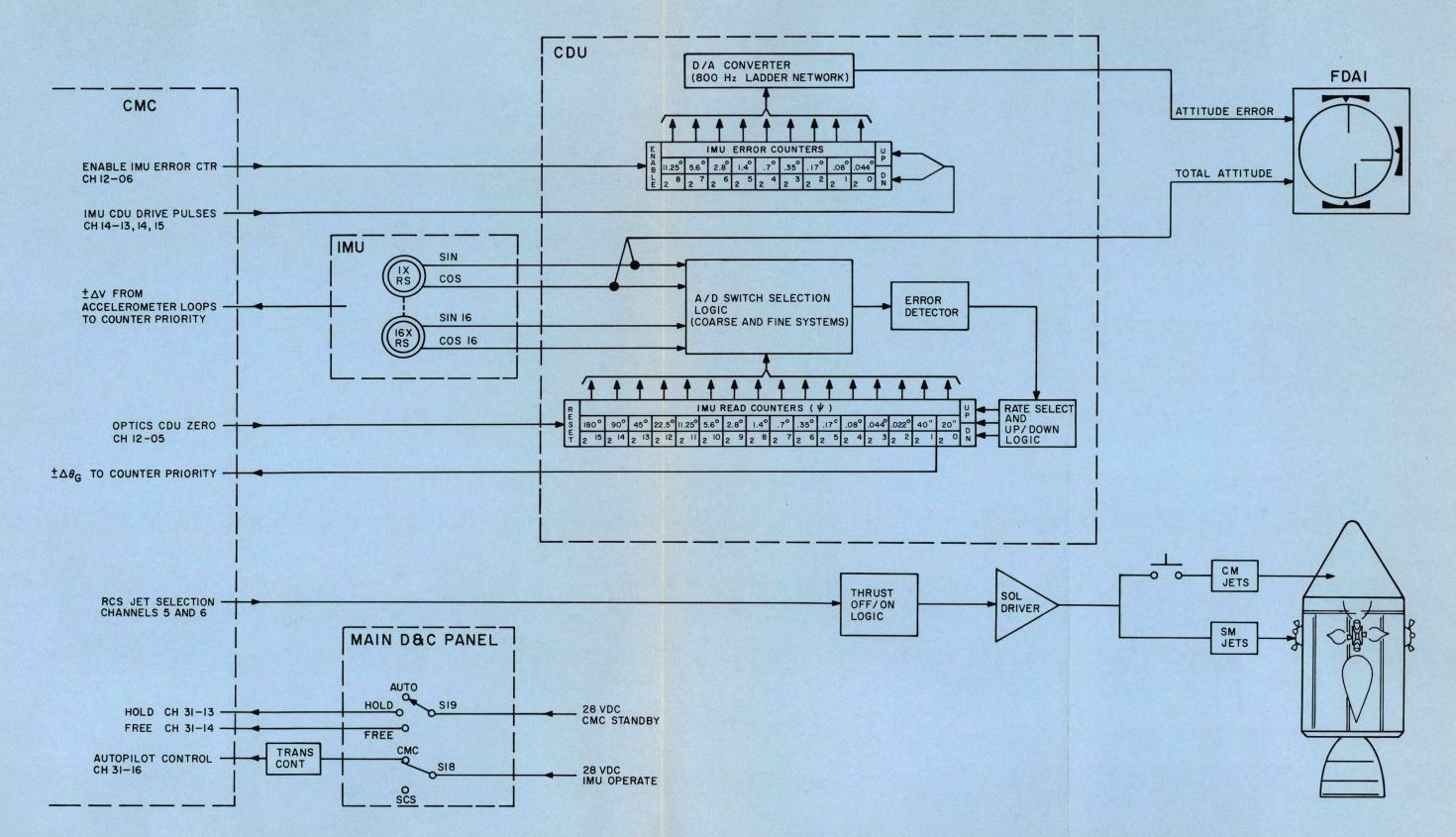

| Section III Coup | ling Data Unit                                                                                             | 3-1  |

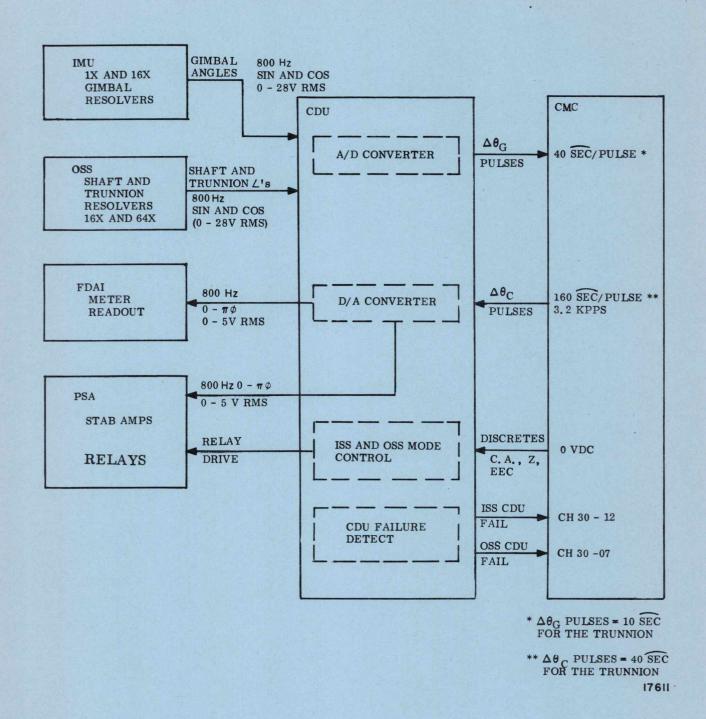

| Block 3.1 Purp   | ose of the Coupling Data Unit (CDU)                                                                        | 3-1  |

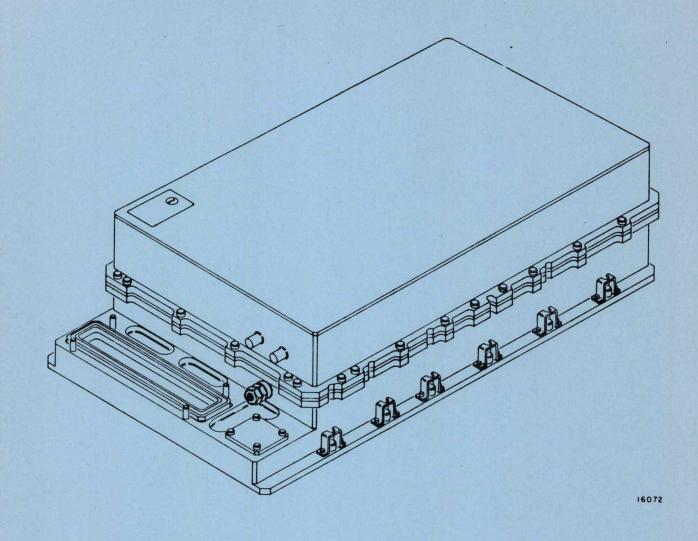

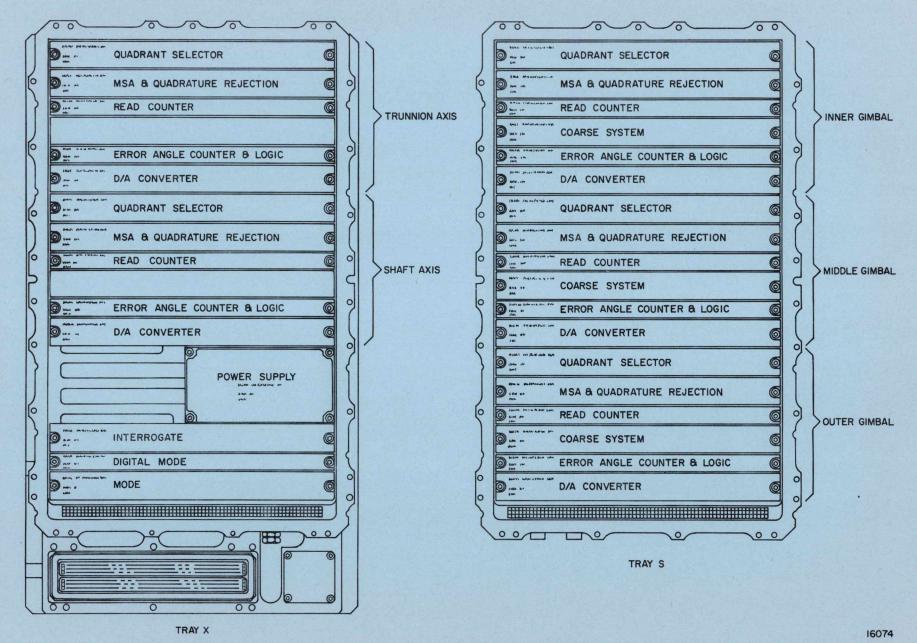

| Block 3.2 Phys   | ical Description of the CDU                                                                                | 3-1  |

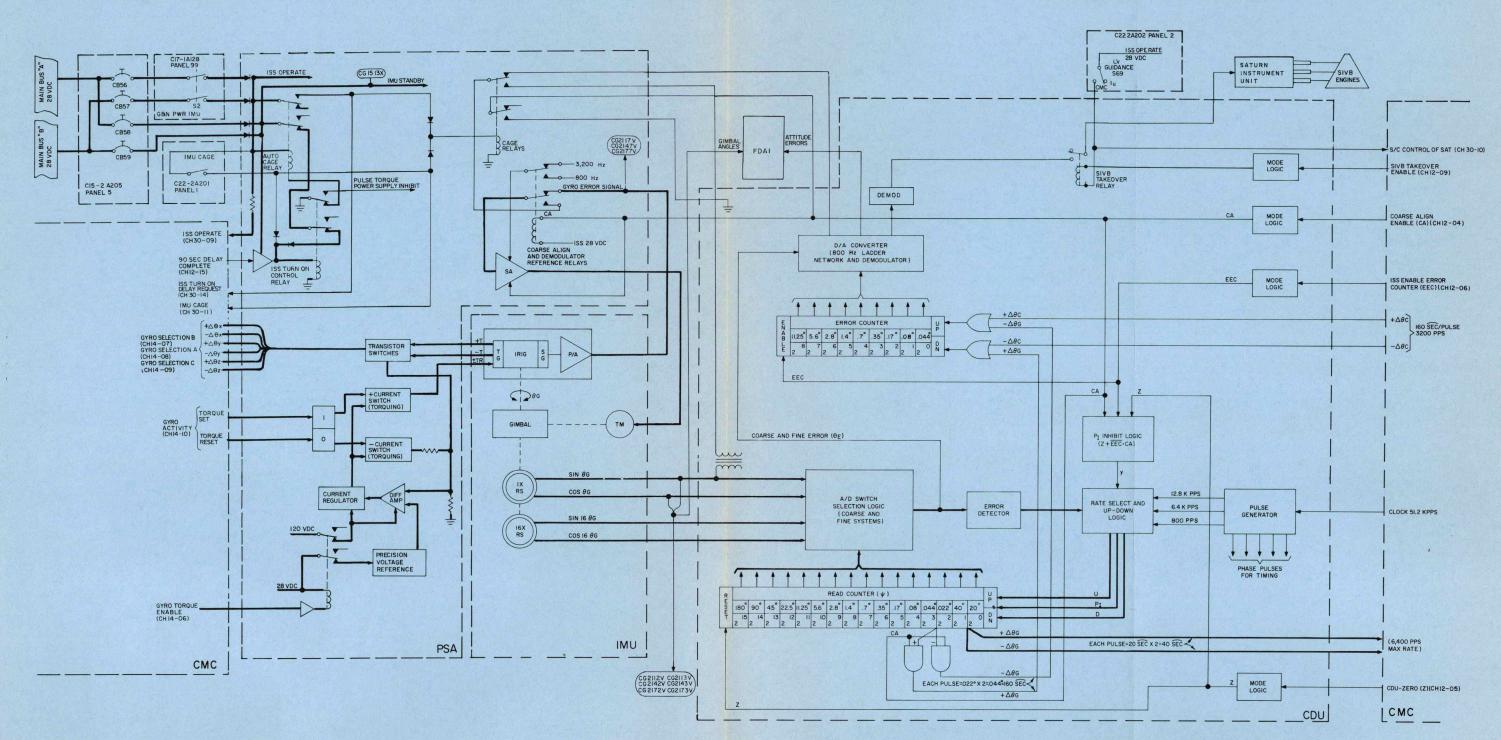

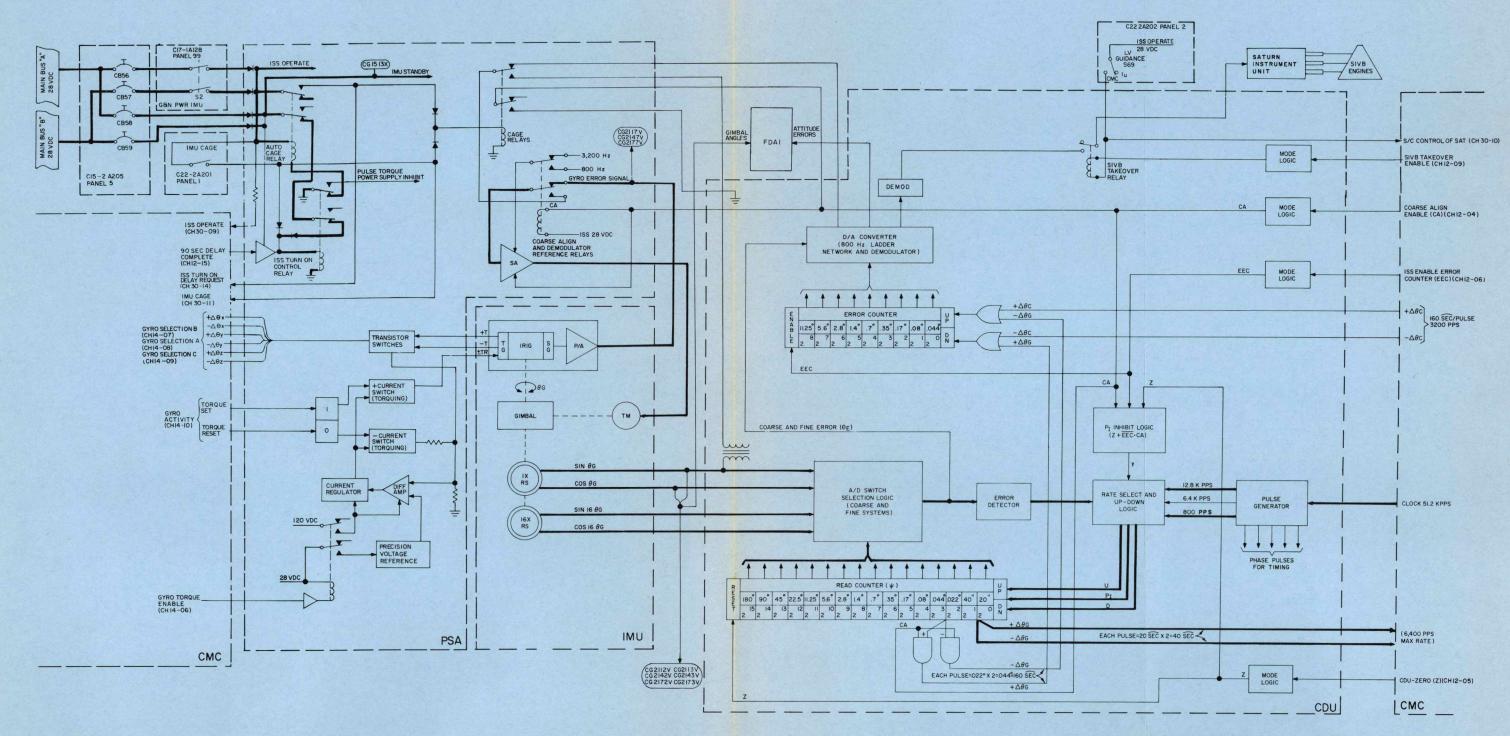

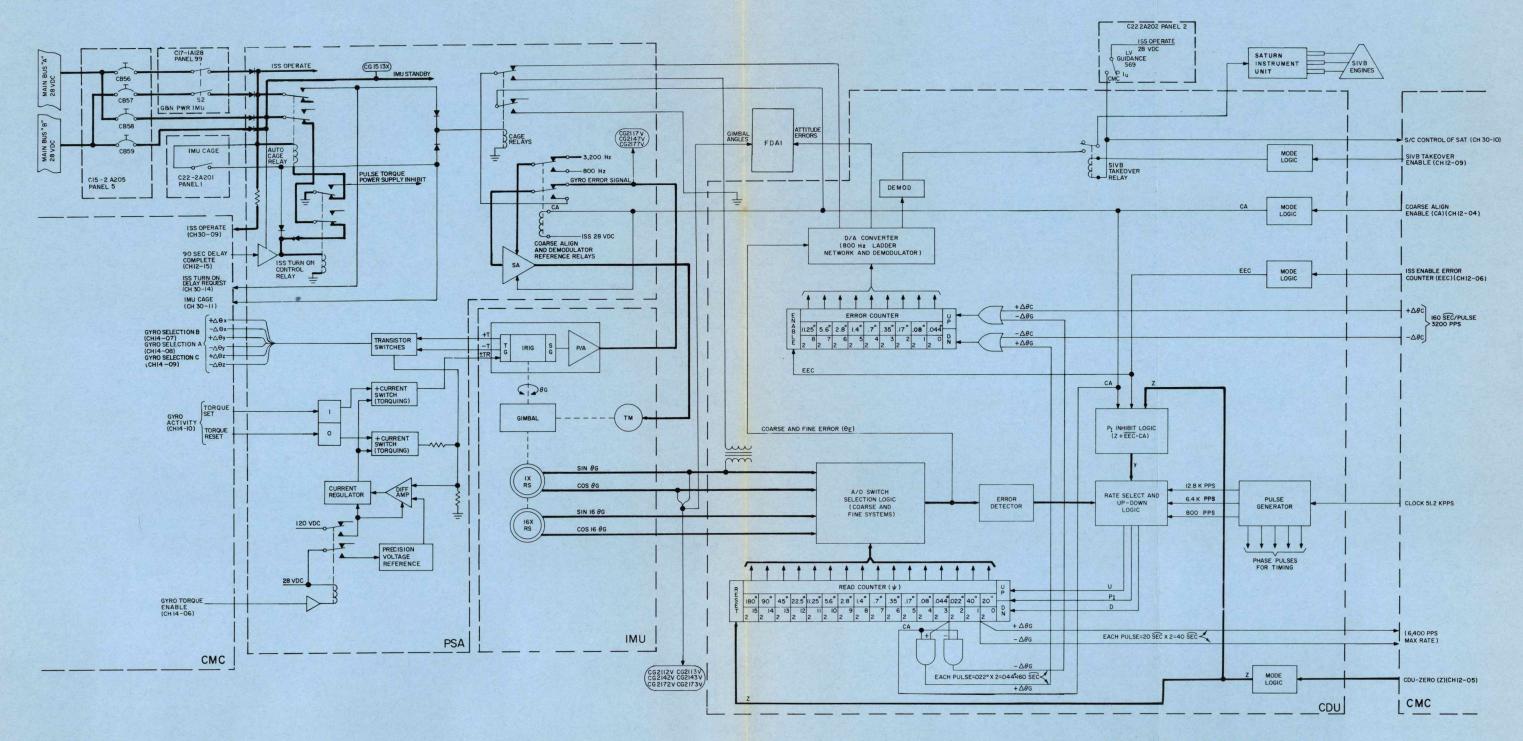

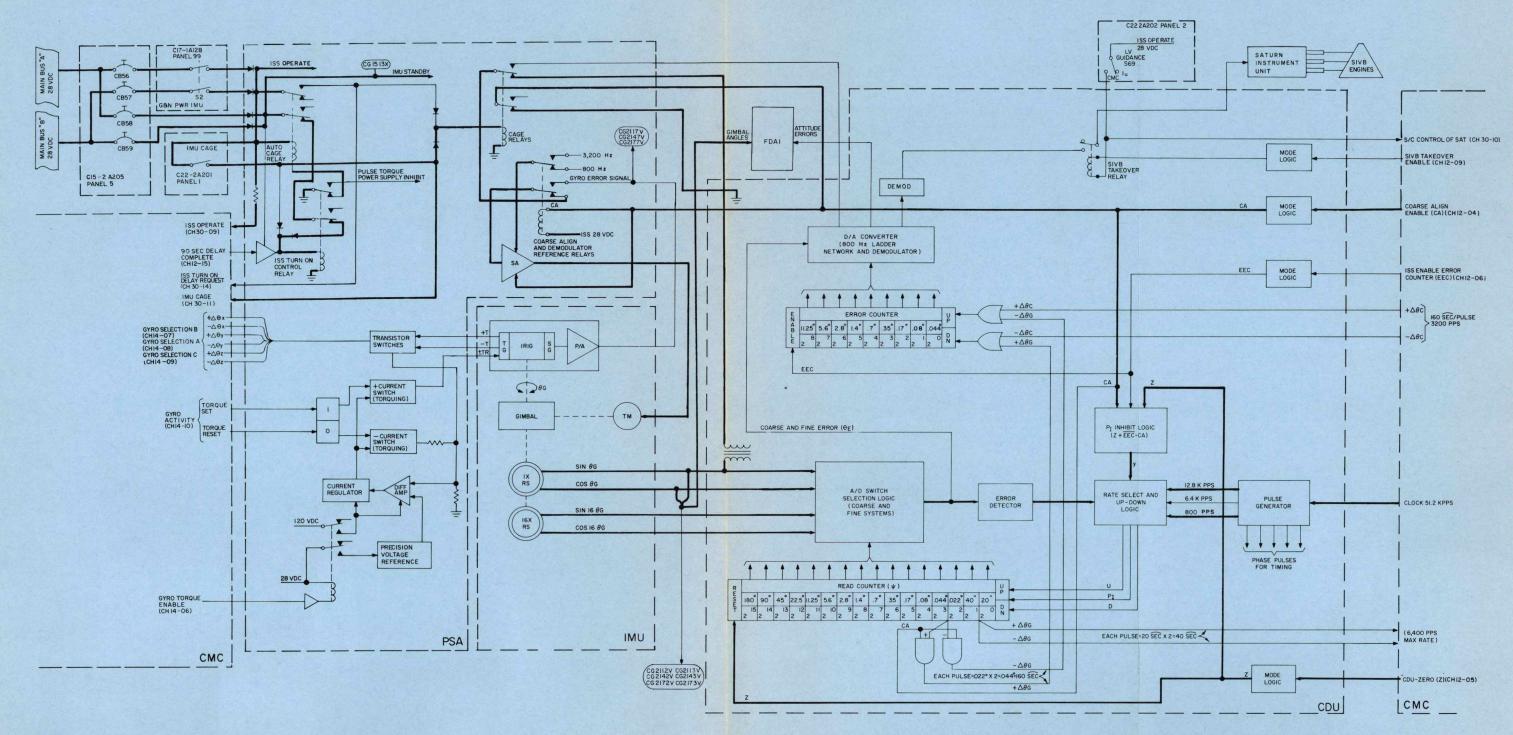

| Block 3.3 CDU    | Single Channel Functional Description                                                                      | 3-5  |

| 3.3.1            | Analog to Digital Conversion                                                                               | 3-6  |

| 3.3.2            | Digital to Analog Conversion                                                                               | 3-8  |

| 3.3.3            | ISS and OSS Mode Control                                                                                   | 3-8  |

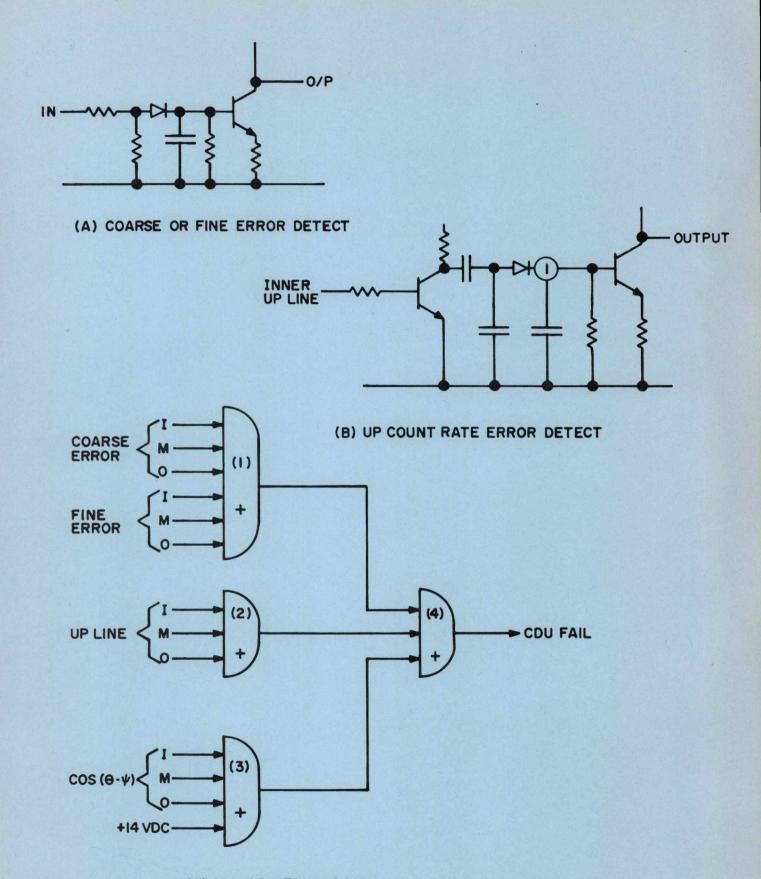

| 3 3 4            | CDIL Fail Detect                                                                                           | 3_0  |

| 있는 사용 등 등 하는 것들은 사용 보고 있는 것이 되었다. 그는 것이 없는 것은 것은 것은 것은 것을 보고 있다. 그는 것은 것은 것은 것은 것은 것은 것은 것은 것은 것을 했다. | 0.0                  |

|-------------------------------------------------------------------------------------------------------|----------------------|

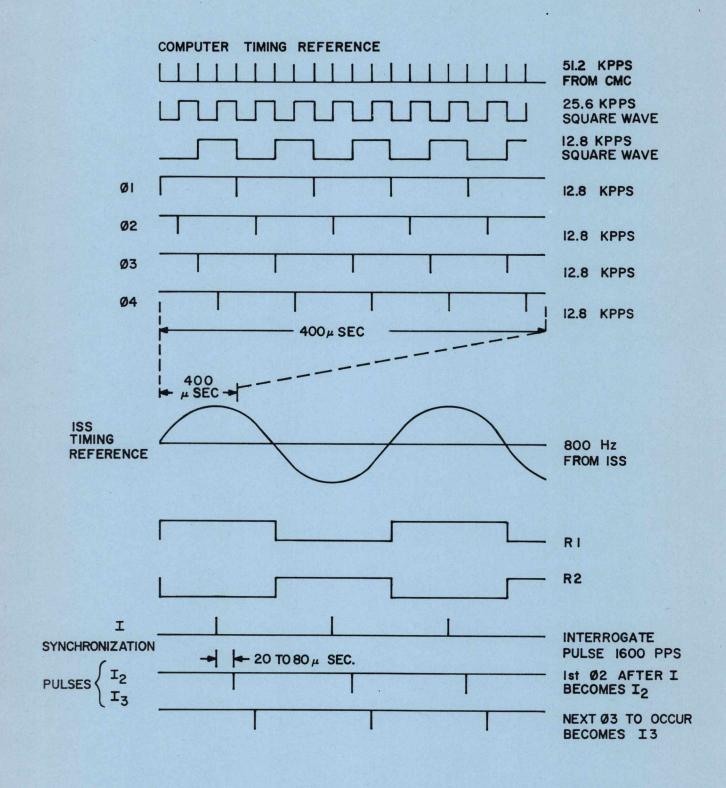

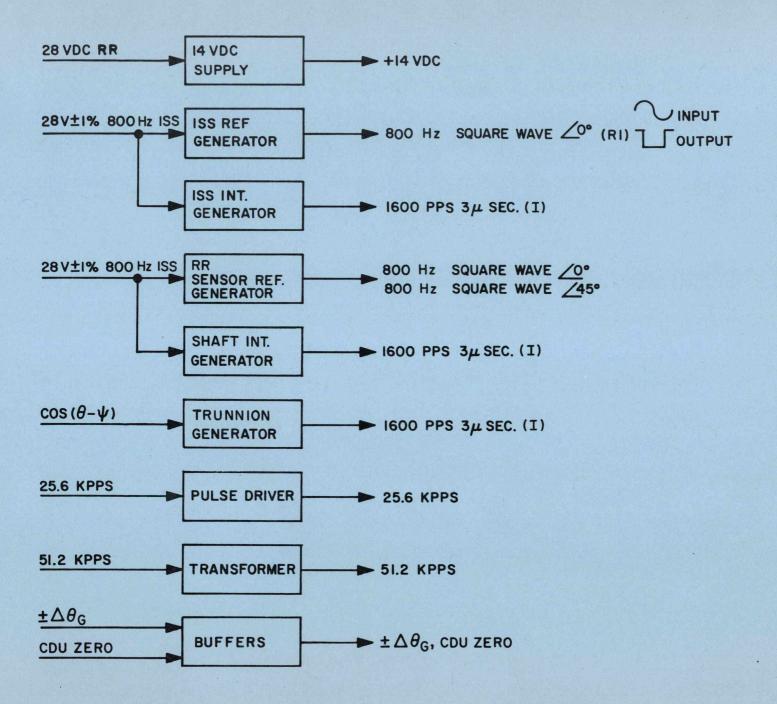

| Block 3.4 Timing Interface                                                                            | 3-9                  |

| 3.4.1 Computer Reference                                                                              | 3-9                  |

| 3.4.2 ISS Reference                                                                                   | 3-11                 |

| 3.4.2 ISS Reference<br>3.4.3 Synchronization Link                                                     | 3-12                 |

|                                                                                                       |                      |

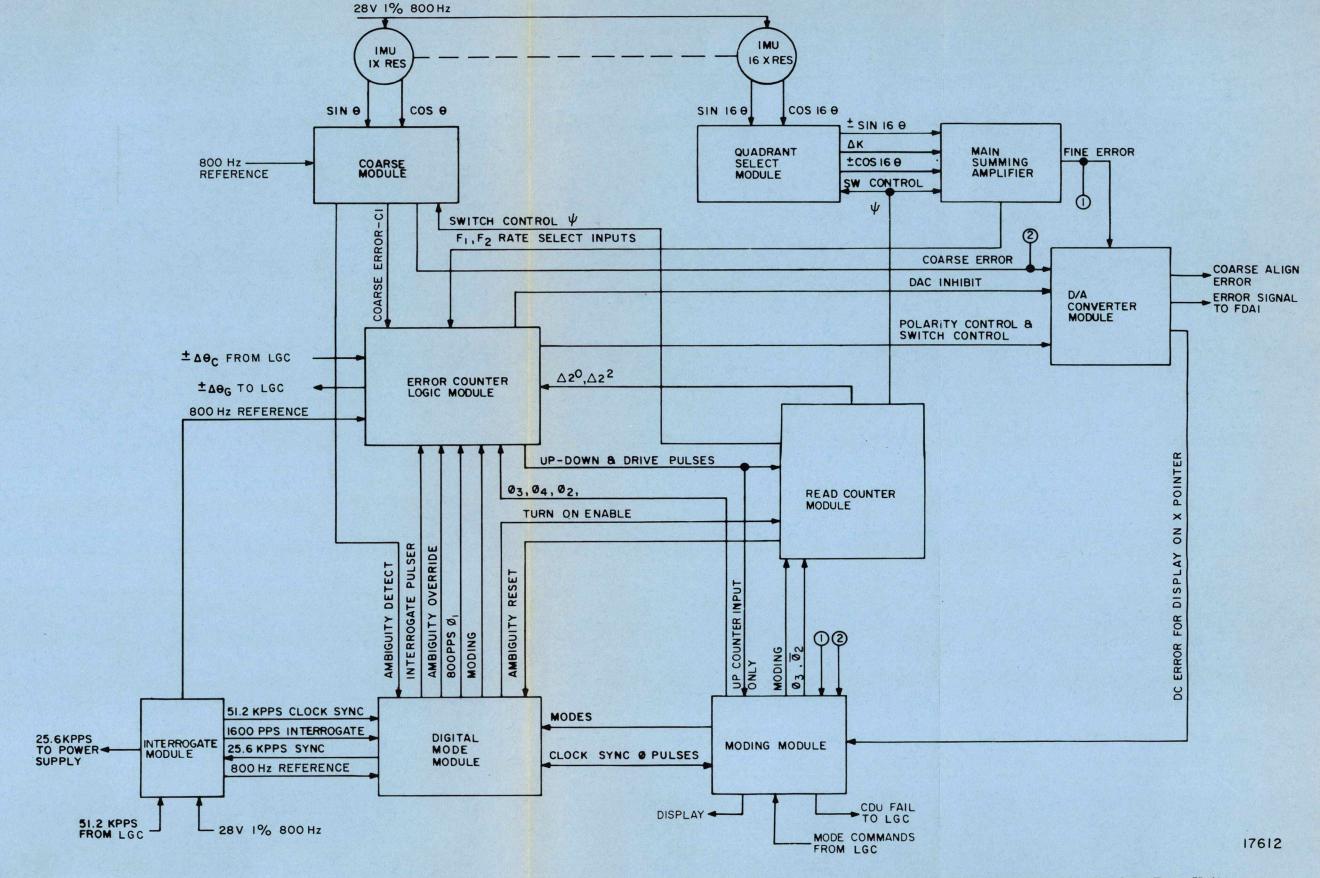

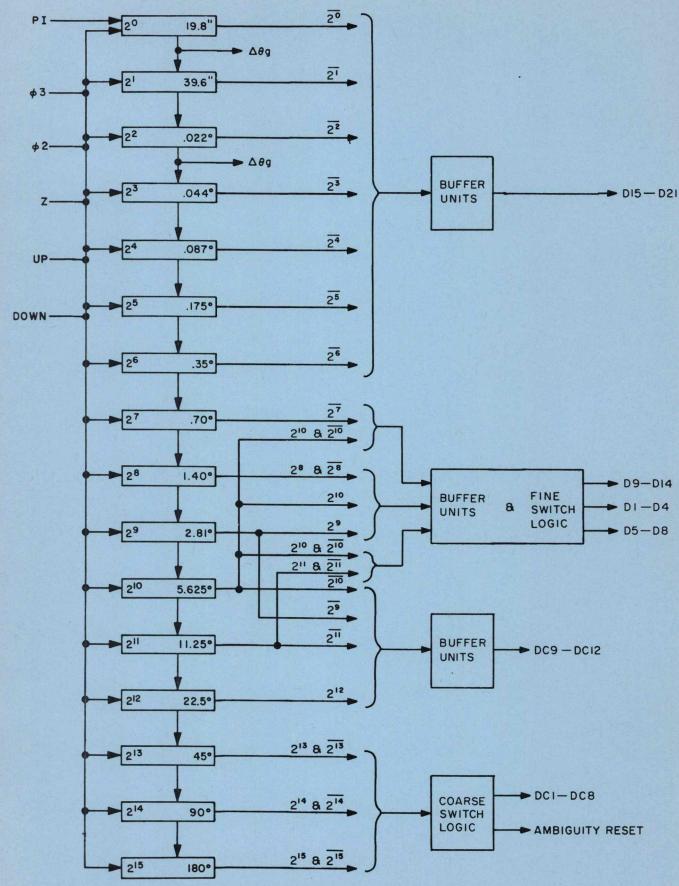

| Block 3.5 CDU Module Interconnect (Single Channel)                                                    | 3-12                 |

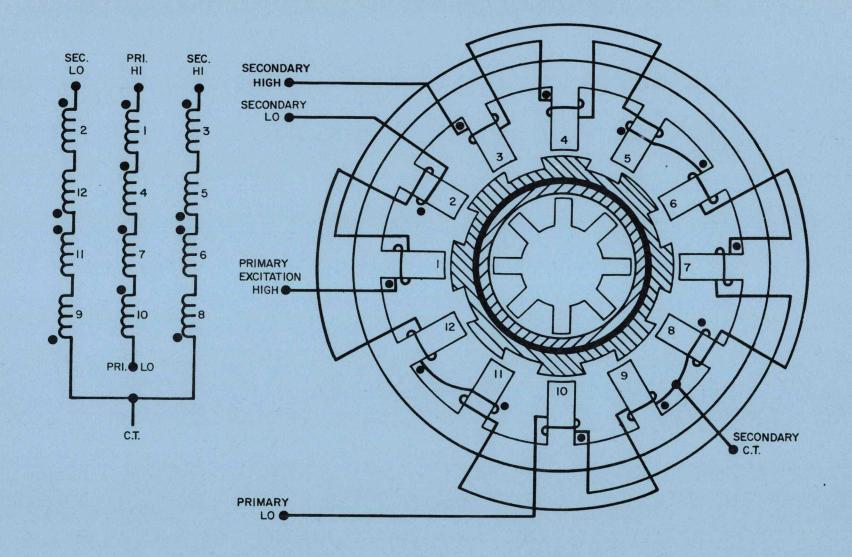

| 3.5.1 Analog to Digital Conversion                                                                    | 3-14                 |

| 3.5.2 Digital to Analog Conversion                                                                    | 3-14                 |

| 0.0.2 Digital to finalog conversion                                                                   |                      |

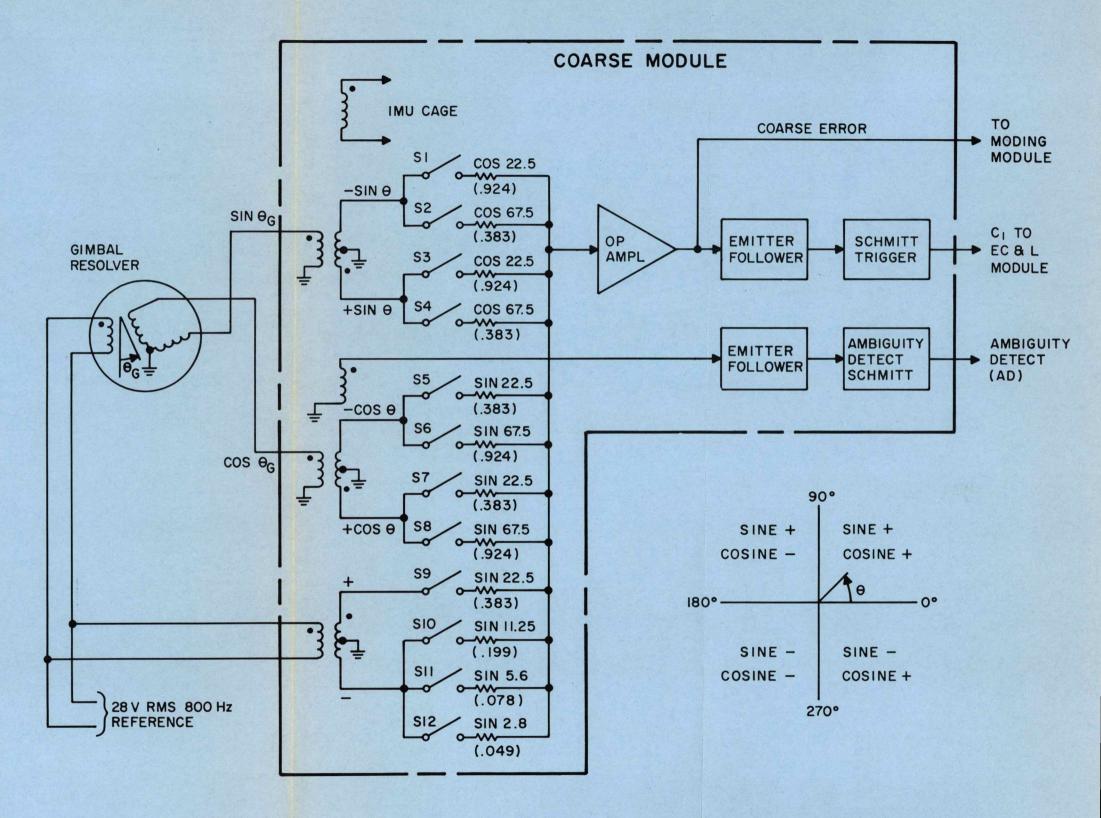

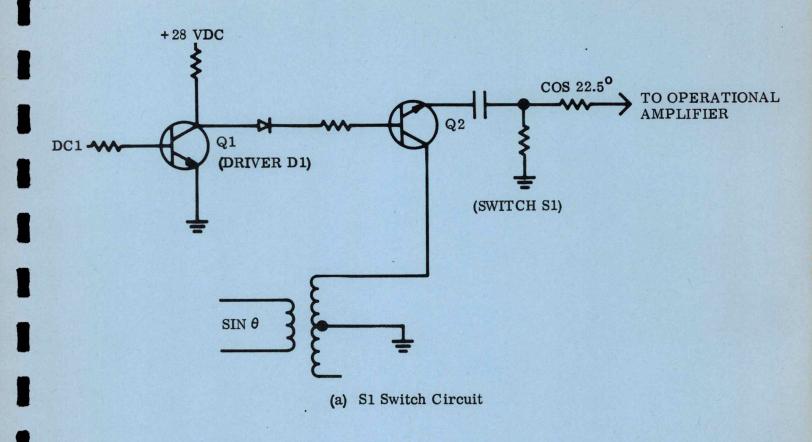

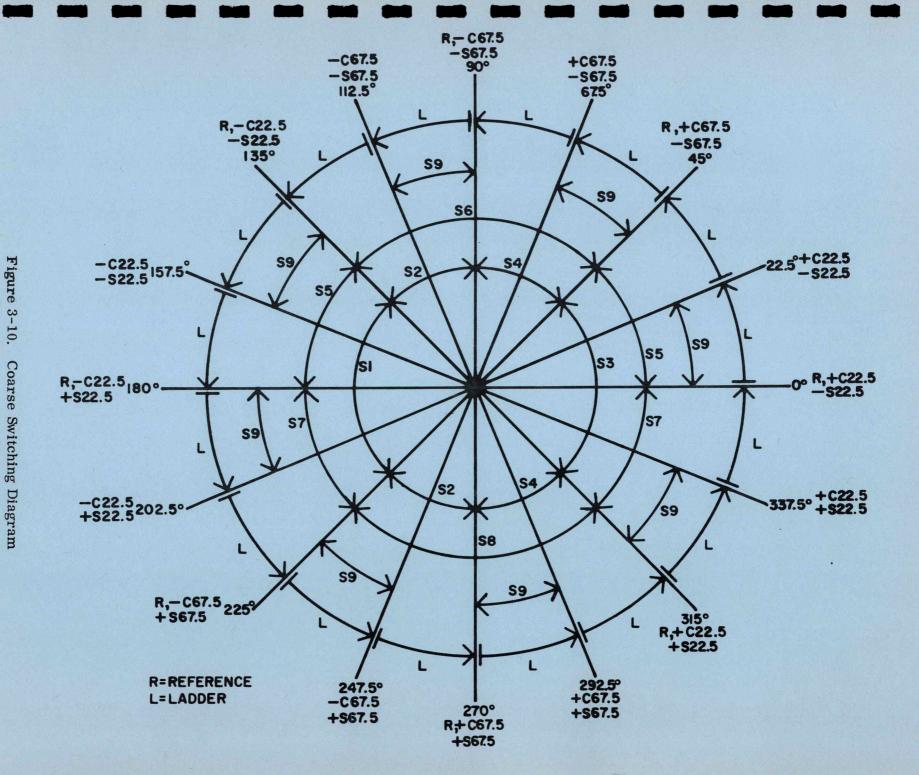

| Block 3.6 CDU Coarse Module                                                                           | 3-15                 |

| 3.6.1 Theory of Operation                                                                             | 3-15                 |

| 3.0.1 Theory of Operation                                                                             | 3 13                 |

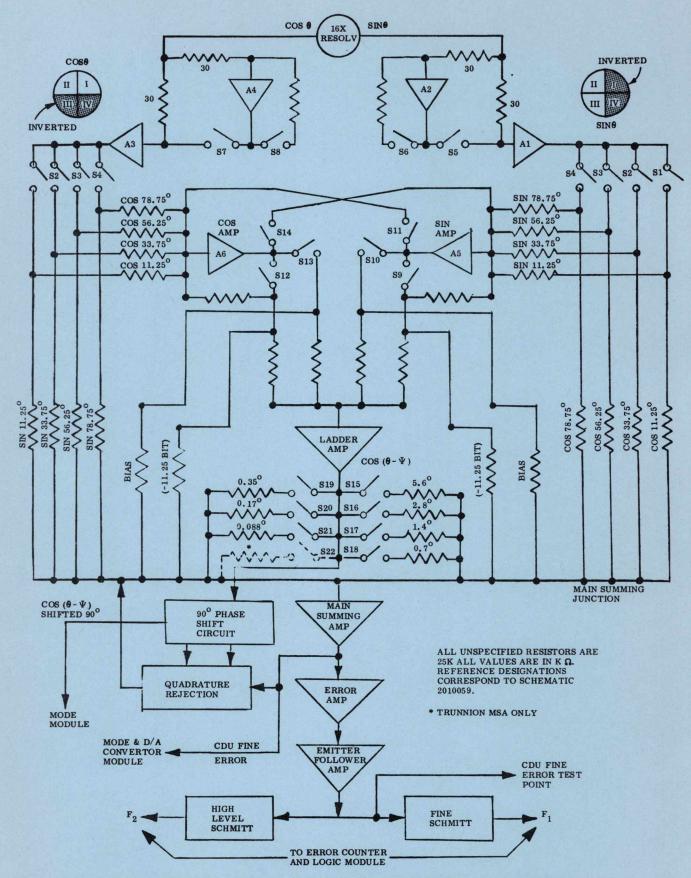

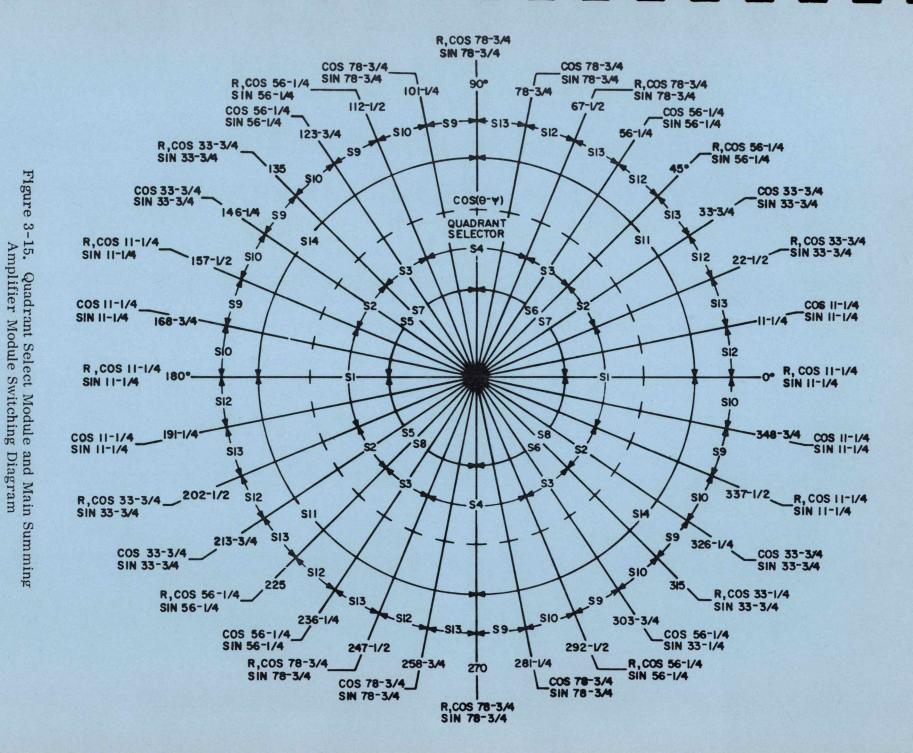

| Block 3.7 Quadrant Select Module and Main Summing Ampli                                               | fier Module 3-27     |

| 3.7.1 Quadrant Select Module                                                                          | 3-27                 |

|                                                                                                       | 3-27                 |

| 3.7.1.1 Theory of Operation                                                                           |                      |

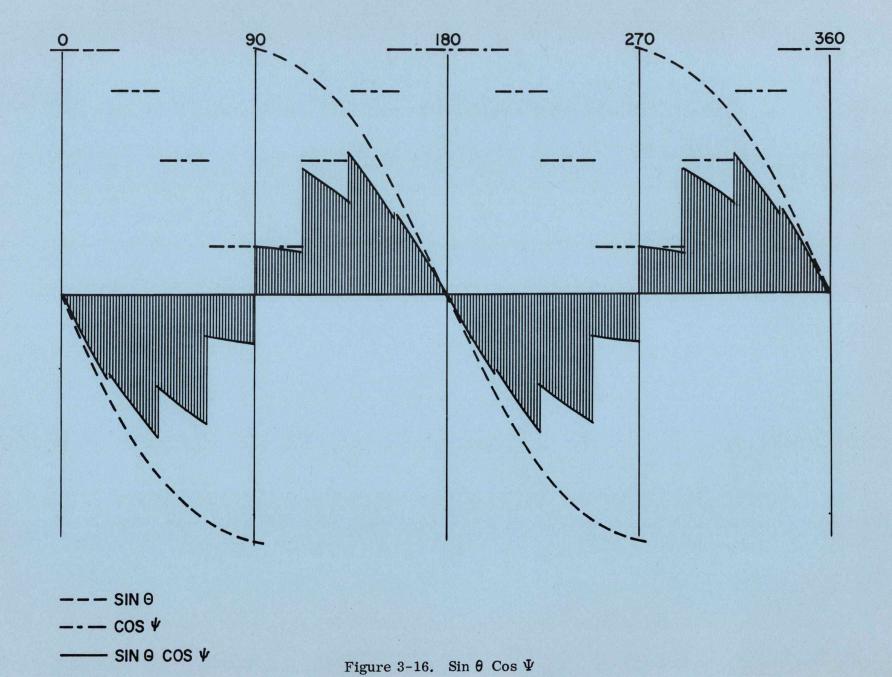

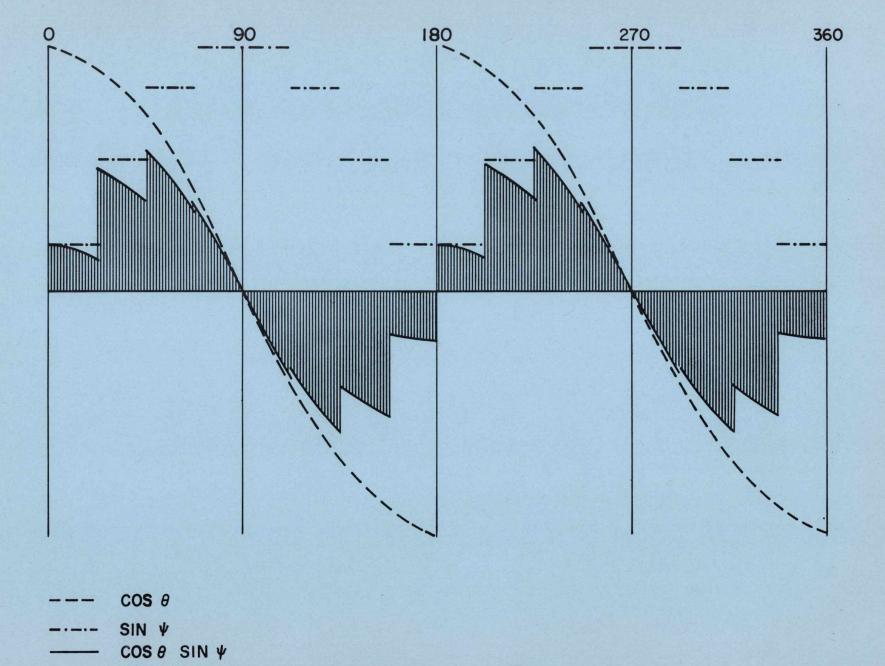

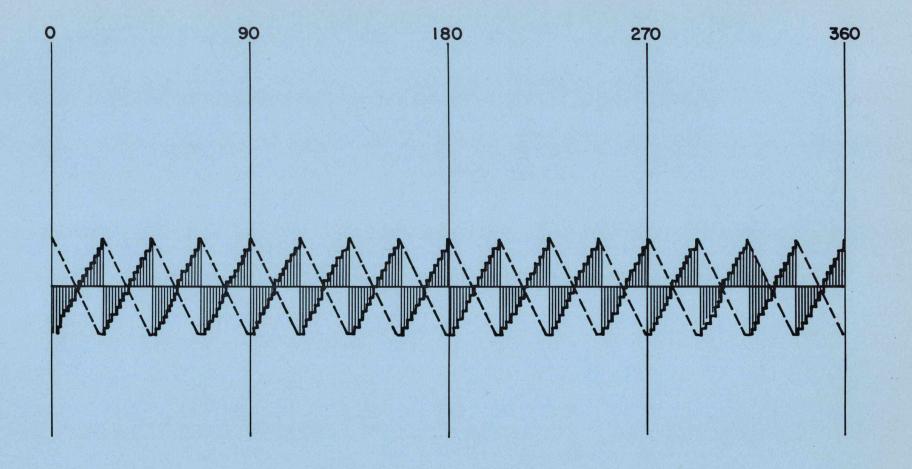

| 3.7.2 Main Summing Amplifiers and Quadrature I                                                        |                      |

| 3.7.2.1 Main Summing Amplifier Module Theor                                                           | ry of Operation 3-32 |

|                                                                                                       | 2.20                 |

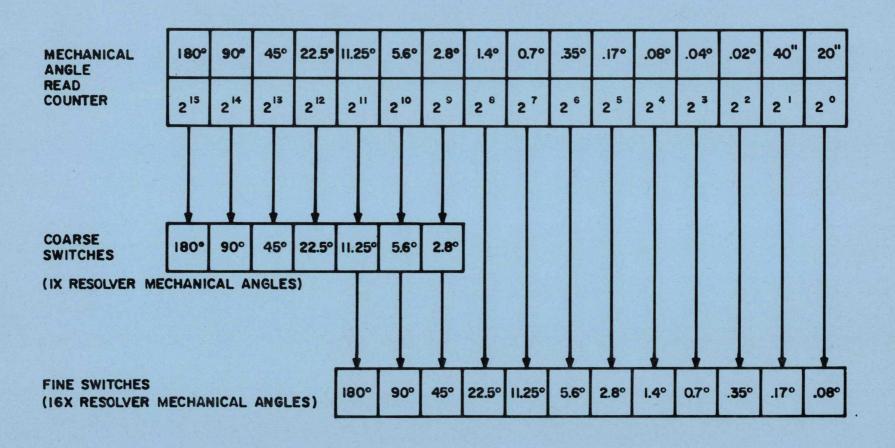

| Block 3.8 Read Counter Module                                                                         | 3-38                 |

| 3.8.1 Read Counter Theory of Operation                                                                | 3-38                 |

|                                                                                                       |                      |

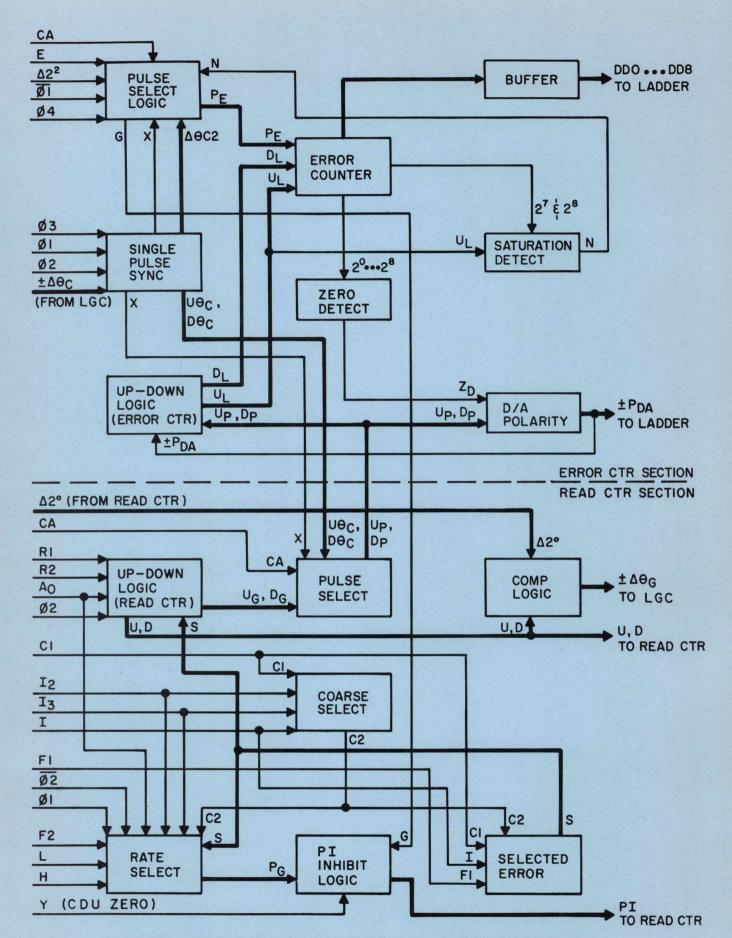

| Block 3.9 Error Counter and Logic Module                                                              | 3-40                 |

| 3.9.1 Error Counter and Logic Module Theory of                                                        |                      |

| 3.9.1.1 Error Counter Logic Circuits                                                                  | 3-46                 |

| 3.9.1.2 Error Counter Logic Circuits                                                                  | 3-48                 |

|                                                                                                       |                      |

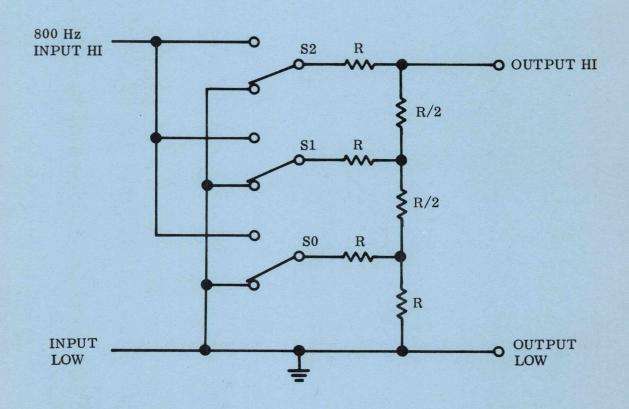

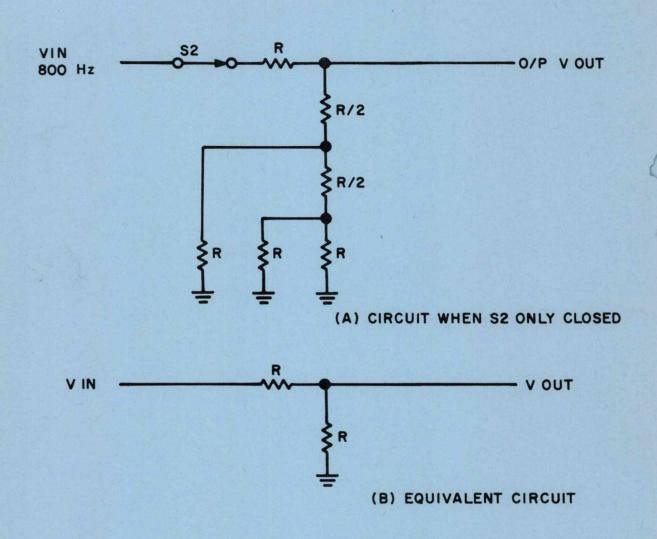

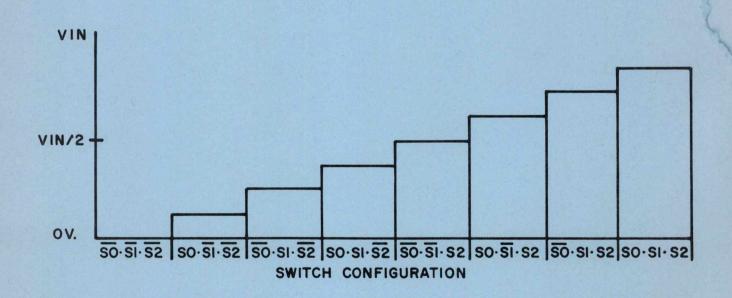

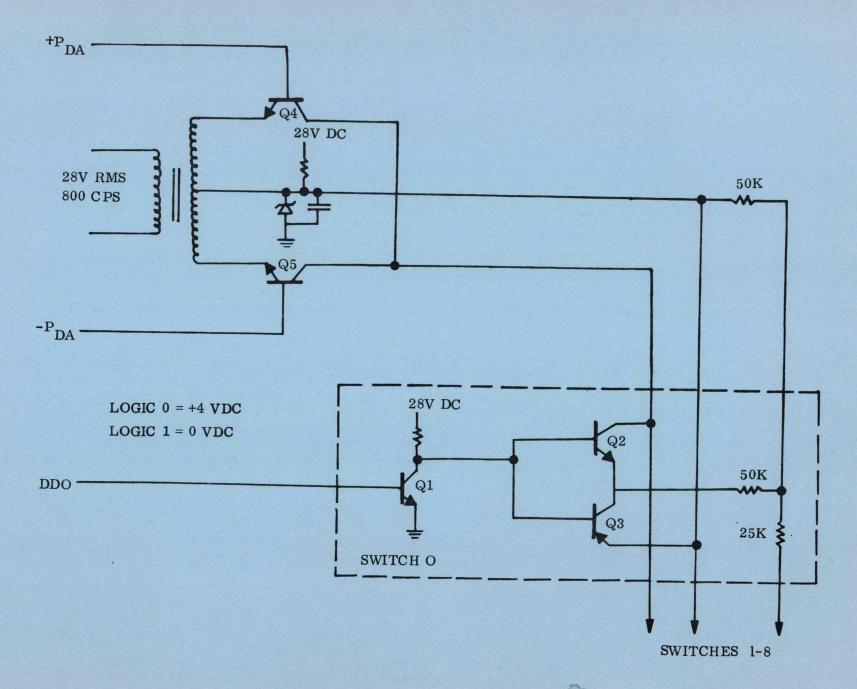

| Block 3.10 Digital to Analog Converter Module                                                         | 3-50                 |

| 3.10.1 Digital to Analog Converter Theory of Oper                                                     |                      |

| 3.10.1.1 Digital to Analog Conversion                                                                 | 3-50                 |

| 3.10.1.1 Digital to Analog Conversion 3.10.1.2 DAC Module Mixing and Output Circuit                   | s 3-57               |

|                                                                                                       |                      |

| Block 3.11 Interrogator Module                                                                        | 3-58                 |

| 3.11.1 Interrogator Module Theory of Operation                                                        | 3-58                 |

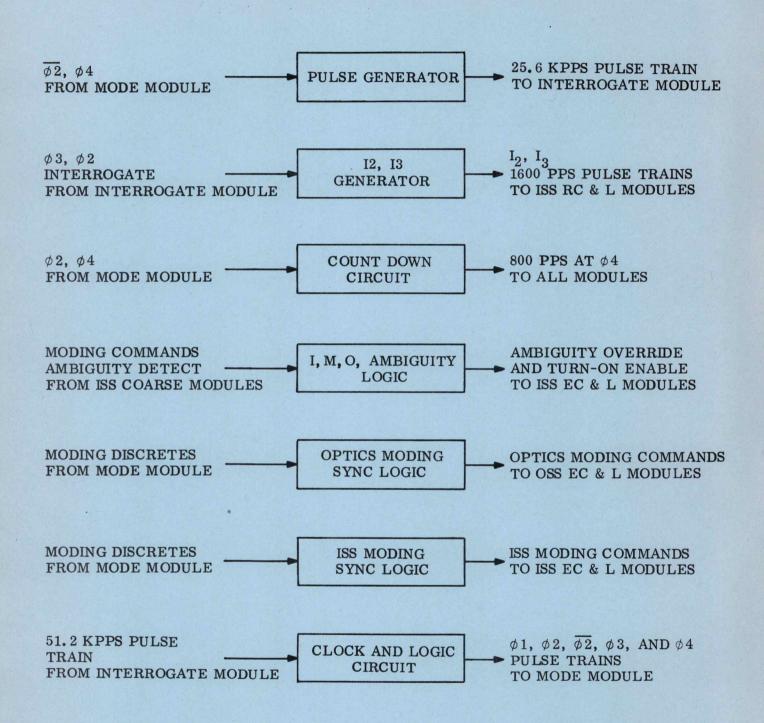

| 3.11.1 1 Timing Circuits                                                                              | 3-58                 |

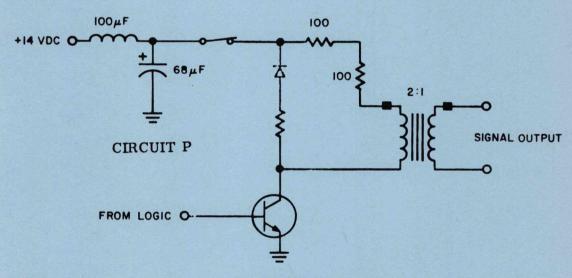

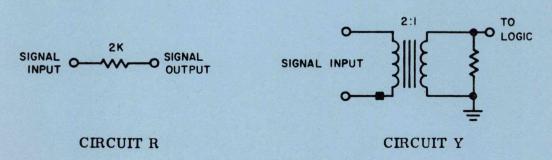

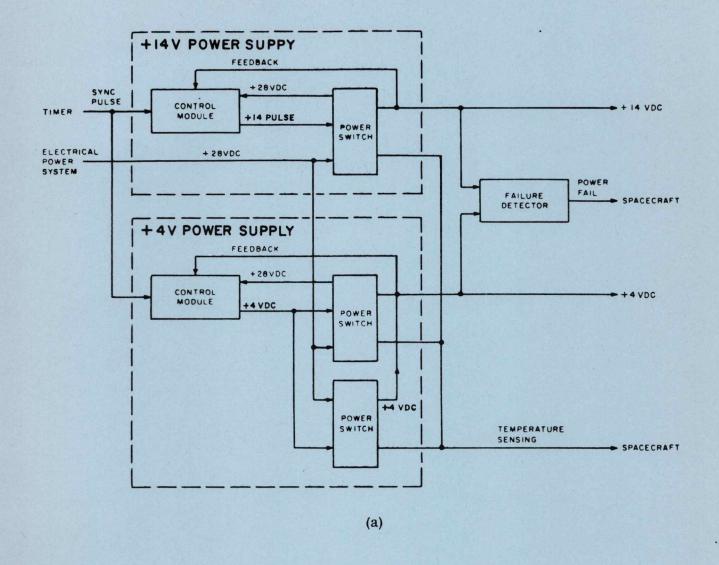

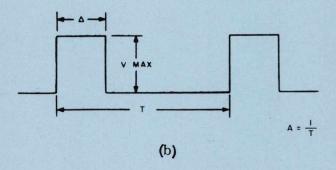

| 3.11.1.2 14 VDC Power Supply                                                                          | 3-60                 |

|                                                                                                       |                      |

| Block 3. 12 Digital Mode Module                                                                       | 3-60                 |

| 3. 12.1 Digital Mode Module Theory of Operation                                                       | 3-60                 |

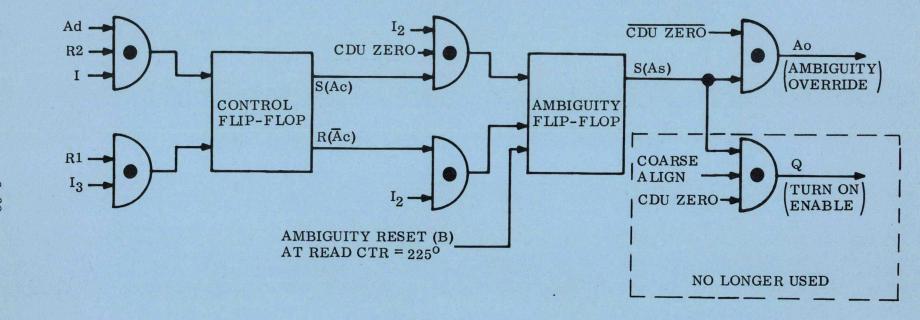

| 3.12.1.1 Ambiguity Logic                                                                              | 3-60                 |

| 3.12.1.2 ISS Moding Sync Logic                                                                        | 3-62                 |

| 3.12.1.3 OSS Moding Sync Logic                                                                        | 3-62                 |

|                                                                                                       |                      |

| Block 3.13 Mode Module                                                                                | 3-64                 |

| 3.13.1 Mode Module Theory of Operation                                                                | 3-64                 |

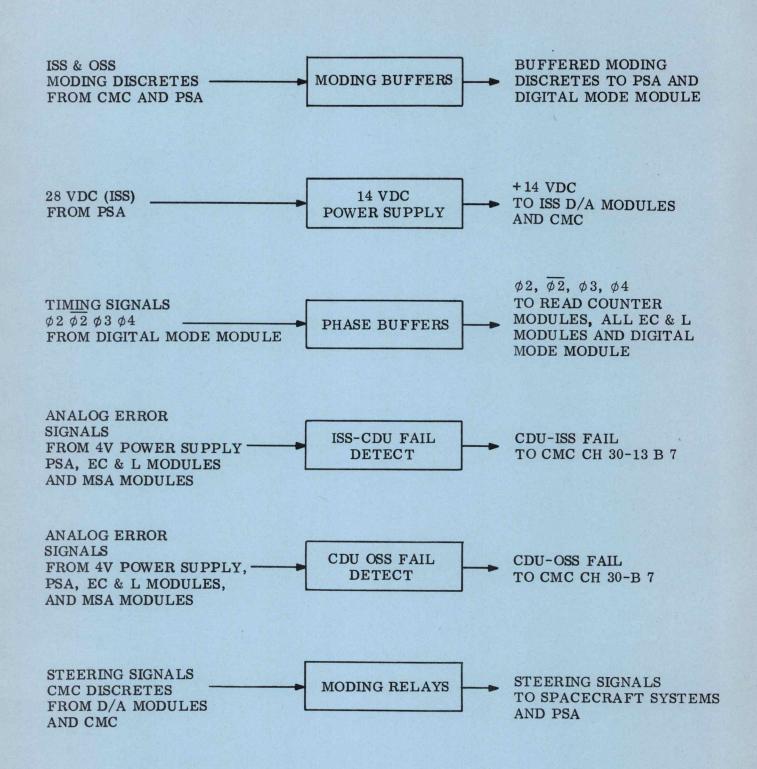

| 3.13.1.1 Moding Buffer Circuits                                                                       | 3-64                 |

| 3.13.1.2 14 VDC Power Supply                                                                          | 3-66                 |

| 3.13.1.3 Phase Buffer Circuits                                                                        | 3-66                 |

| 3. 13. 1.4 ISS CDU Fail Circuits                                                                      | 3-66                 |

| 3.13.1.5 OSS CDU Fail Circuits                                                                        | 3-68                 |

| 3 13 1 6 Moding Relays                                                                                | 3-68                 |

| A LA LU MURITO REIAVS                                                                                 |                      |

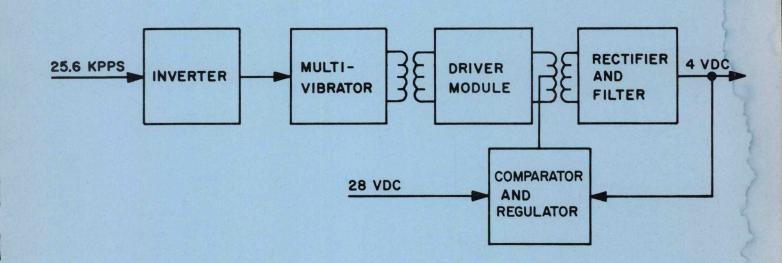

| Block 3.14<br>3.14.1 | CDU 4 VDC Power Supply Power Supply Theory of Operation | 3-68<br>3-68 |

|----------------------|---------------------------------------------------------|--------------|

| Block 3.15           | Summary                                                 | 3-71         |

| Section IV           | ISS - System Modes of Operation                         | 4-1          |

| Doctron 1,           | 222 2 Joseph Market of Operation                        |              |

| Block 4.1            | ISS Turn-on Mode                                        | 4-1          |

| 4.1.1                | Purpose                                                 | 4-1          |

| 4.1.2                | Methods of Entry                                        | 4-1          |

| 4.1.3                | Discretes                                               | 4-1          |

| 4.1.4                | Computer Routines                                       | 4-1          |

| 4.1.5                | Display and Control Indication                          | 4-1          |

| 4.1.6                | Operation                                               | 4-3          |

| Block 4.2            | ISS Coarse Align Mode                                   | 4-6          |

| 4.2.1                | Purpose                                                 | 4-6          |

| 4.2.2                | Methods of Entry                                        | 4-6          |

| 4.2.3                | Discretes                                               | 4-6          |

| 4.2.4                | Display and Control Indications                         | 4-6          |

| 4.2.5                | Operation                                               | 4-6          |

| Block 4.3            | ISS Fine Align Mode                                     | 4-9          |

| 4.3.1                | Purpose                                                 | 4-9          |

| 4.3.2                | Methods of Entry                                        | 4-9          |

| 4.3.3                | Discretes                                               | 4-9          |

| 4.3.4                | Display and Control Indications                         | 4-9          |

| 4.3.5                | Operation                                               | 4-9          |

| Block 4.4            | ISS Inertial Mode                                       | 4-11         |

| 4.4.1                | Purpose                                                 | 4-11         |

| 4.4.2                | Methods of Entry                                        | 4-11         |

| 4.4.3                | Discretes                                               | 4-11         |

| 4.4.4                | Display and Control Indications                         | 4-11         |

| 4.4.5                | Operation                                               | 4-11         |

| Block 4.5            | ISS CDU Zero Mode                                       | 4-13         |

| 4.5.1                | Purpose                                                 | 4-13         |

| 4.5.2                | Methods of Entry                                        | 4-13         |

| 4.5.3                | Discretes                                               | 4-13         |

| 4.5.4                | Display and Control Indications                         | 4-13         |

| 4.5.5                | Operation                                               | 4-13         |

| Block 4.6            | IMU Cage Mode                                           | 4-15         |

| 4.6.1                | Purpose                                                 | 4-15         |

| 4.6.2                | Methods of Entry                                        | 4-15         |

| 4.6.3                | Discretes                                               | 4-15         |

| 4.6.4                | Display and Control Indications                         | 4-15         |

| 165                  | Operation                                               | 1 15         |

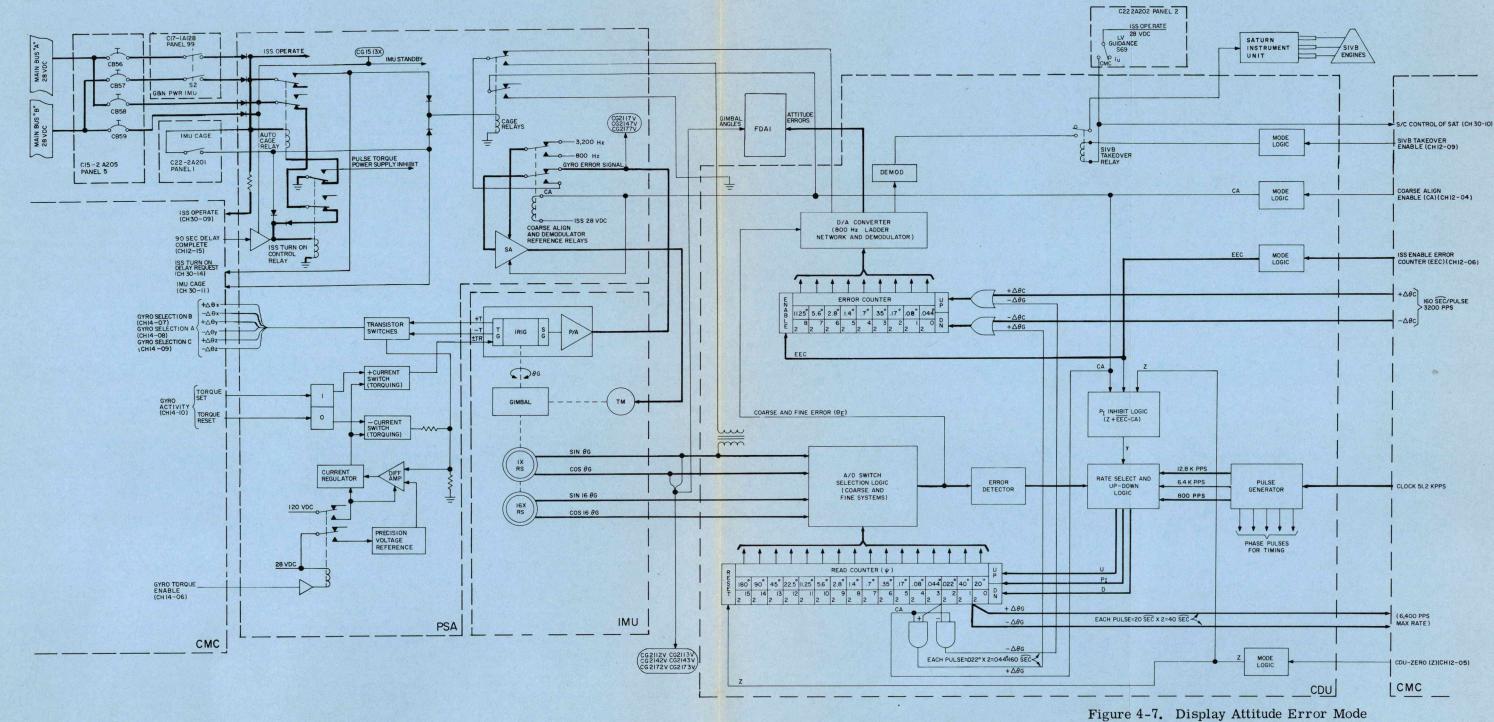

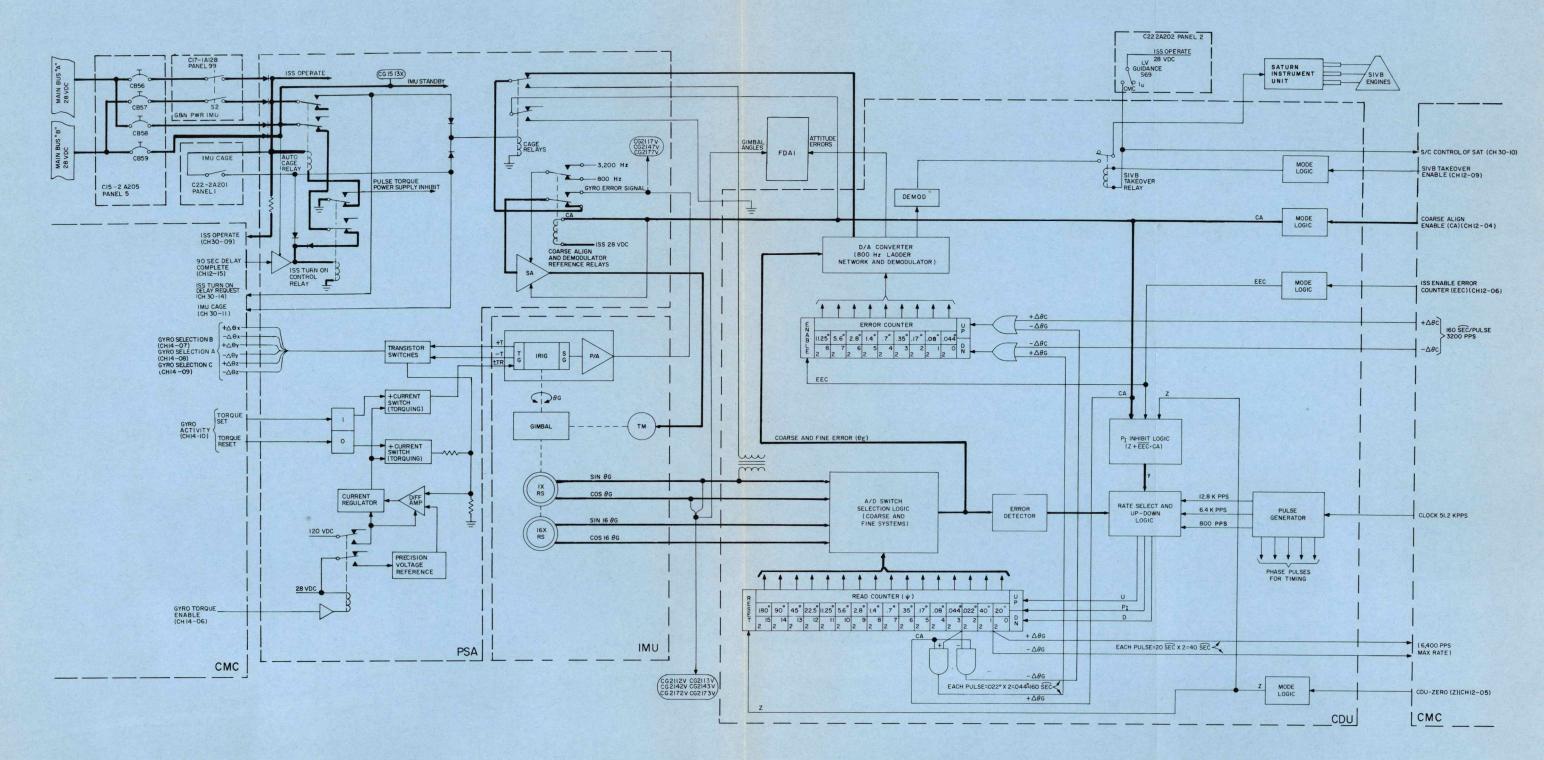

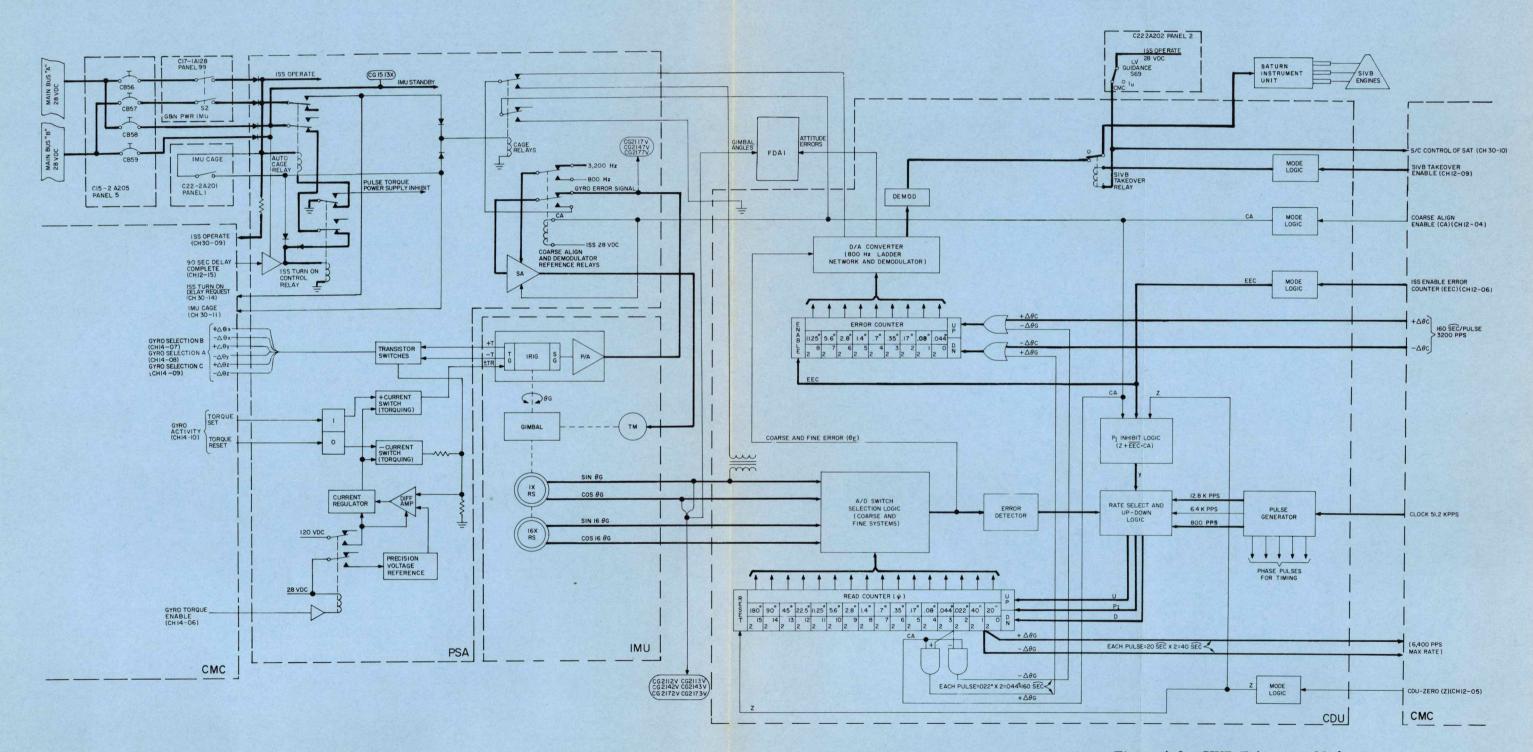

| Block 4.7   | Attitude Error Display Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-18 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.7.1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-18 |

| 4.7.2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-18 |

| 4.7.3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-18 |

| 4.7.4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-18 |

| 4.7.5       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-18 |

| Block 4.8   | Gimbal Lock Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-20 |

| 4.8.1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-20 |

| 4.8.2       | 가게 하는 그리고 사용하다는 이후 10 km, 이렇게 하는 것으로 걸려지는 이 사용이 되는 것이다. 10 km 이 사용이 되었다면 다른 것이다. 10 km, 10 k | 4-20 |

| 4.8.3       | Discretes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-20 |

| 4.8.4       | Display and Control Indications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-20 |

| 4.8.5       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-20 |

| Block 4.9   | SIVB Take-Over Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-22 |

| 4.9.1       | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-22 |

| 4.9.2       | Methods of Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-22 |

| 4.9.3       | Discretes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-22 |

| 4.9.4       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-22 |

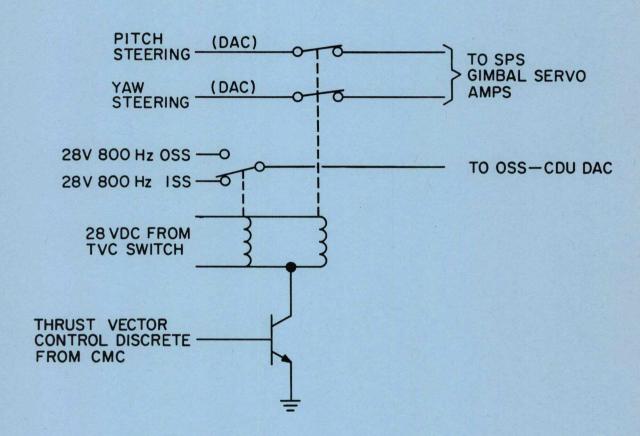

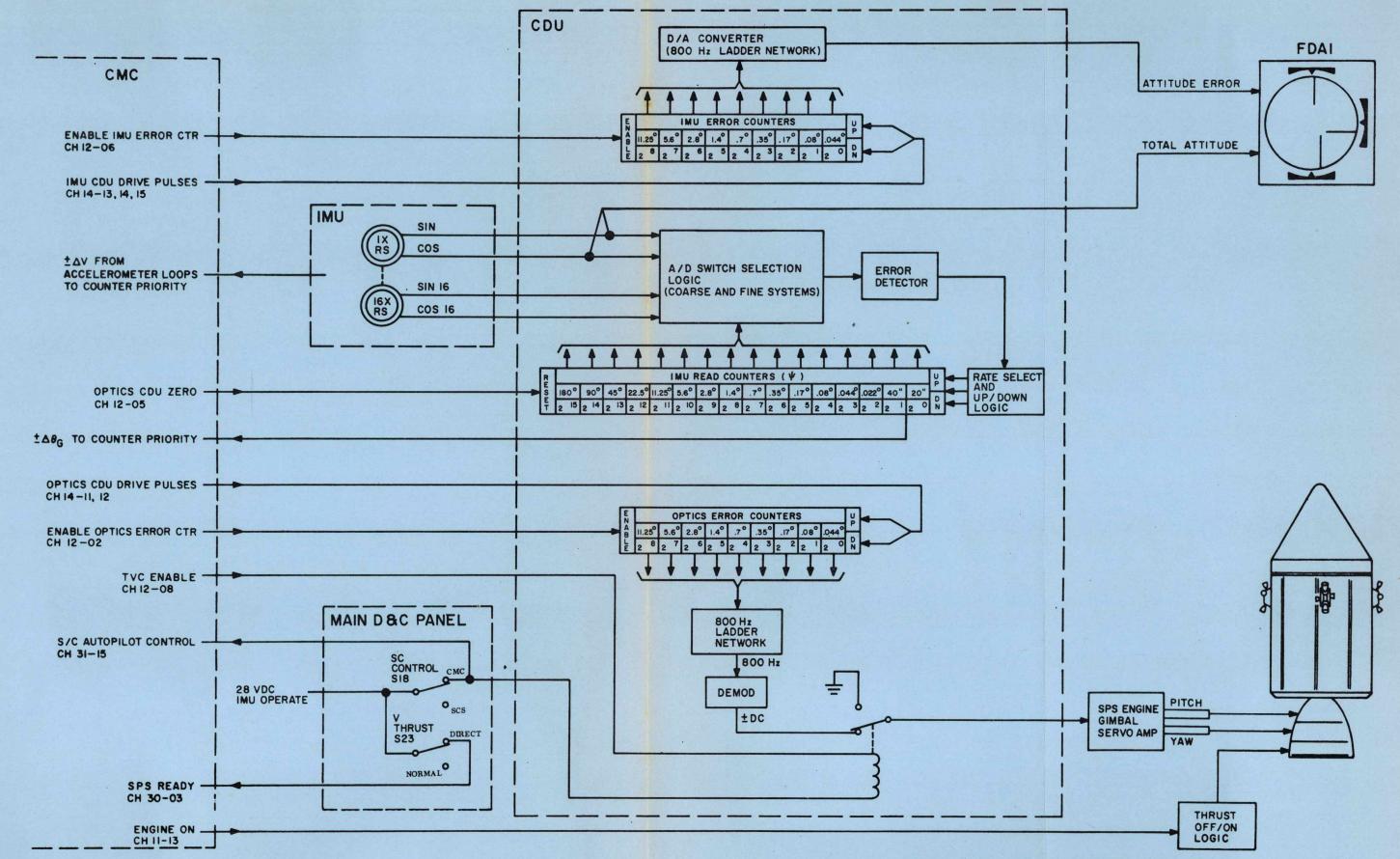

| Block 4. 10 | Thrust Vector Control Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-24 |

| 4.10.1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-24 |

| 4.10.2      | Methods of Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-24 |

| 4.10.3      | B Discretes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-24 |

| 4.10.4      | 4 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-24 |

| Block 4.11  | Attitude Control Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-26 |

| 4.11.1      | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-26 |

| 4.11.2      | 2 Methods of Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-26 |

| 4.11.3      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-26 |

| 4.11.4      | l Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-26 |