**Space Shuttle** Advanced System/4 Pi Prototype Input/Output Processor (IOP)

**Functional Description**

YUBRARIES

2

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives

# Space Shuttle Advanced System/4 Pi Prototype Input/Output Processor (IOP)

**Functional Description**

Prepared for

**Rockwell International Corporation** Space Division 12214 Lakewood Blvd. Downey, CA 90241

25 October 1974

Under Purchase Order No. MAJ7XMA-483019

IBM File No. 74-A31-016

Federal Systems Division, Owego, New York 13827

# TABLE OF CONTENTS

| Section |          |         | Madrid Milaton Brandina Crain Madrid Co. | Page         |

|---------|----------|---------|------------------------------------------|--------------|

| 1       | INTR     | ODUCTIO | DN                                       | 1-1          |

|         | 1.1      | OVERV   | ЛЕW                                      |              |

|         |          |         |                                          | 1-1          |

|         |          | 1.1.1   | Instructions                             | 1-3          |

|         |          | 1.1.2   | Data Bus Operating Modes                 | 1-3          |

|         | in water | 1.1.3   | Fault Detection                          | 1-4          |

|         |          | 1.1.4   | Packaging                                | 1-5          |

|         | 1.2      | OPERA   | TING PRINCIPLES                          | 1-5          |

| 2       | FUNC     |         | IMPLEMENTATION                           |              |

|         |          |         |                                          | 2-1          |

|         | 2.1      | INTRO   | DUCTION                                  | 2-1          |

|         |          | 2.1.1   | Time Sharing                             | 2-1          |

|         |          | 2.1.2   | Operation of Processor Elements          | 2-1          |

|         |          | 2.1.3   | Example Program Execution                | 2-5          |

|         | 2.2      | PROGR   | AM CONTROL INPUTS AND OUTPUTS            | 2-5          |

|         |          | 2.2.1   | PCI/PCO Command Word Format              | 2-5          |

|         |          | 2.2.2   | PCO Data Words                           | 2-9          |

|         |          | 2.2.3   | PCI Data Words                           | 2-13         |

|         | 2.3      | STATU   | S AND INTERRUPT REGISTERS                | 2-17         |

| kadi -  | 2.4      | MASTE   | R SEQUENCE CONTROLLER (MSC)              | 2-20         |

|         |          | 2.4.1   | MSC Programmable Registers               |              |

|         |          | 2.4.2   | MSC Operation                            | 2-21         |

|         |          | 2.4.3   | MSC Instructions                         | 2-21         |

|         |          | 2.4.4   | MSC Local Store and Status Register      | 2-24<br>2-27 |

|         | 2.5      | BUS CO  | NTROL ELEMENT                            | 9.90         |

|         |          |         |                                          | 2-28         |

|         |          | 2.5.1   | Programmable Registers                   | 2-29         |

|         |          | 2.5.2   | BCE Operation                            | 2-29         |

SM

Вох

LIBRARIES

WALESCOLOSA ON THE POST OF THE CONTRACT OF THE

# Table of Contents (cont)

| Section |      |         |                                     | Page |

|---------|------|---------|-------------------------------------|------|

|         |      | 2.5.3   | BCE Instructions                    | 2-30 |

|         |      | 2.5.4   | BCE Local Store and Status Register | 2-33 |

|         | 2.6  | FAULT   | HANDLING                            | 2-33 |

|         |      | 2.6.1   | Fault Detection                     | 2-34 |

|         |      | 2.6.2   | Fault Identification                | 2-41 |

|         |      | 2.6.3   | Reconfiguration                     | 2-41 |

|         | 2.7  | INITIAL | PROGRAM LOADING                     | 2-43 |

|         |      | 2.7.1   | GPC Mode Control                    | 2-40 |

|         |      | 2.7.2   | Computer Initial Program Load       | 2-40 |

| 3       | SYST | EM ELEM | ENTS                                | 3-1  |

|         | 3.1  | INTROD  | OUCTION                             | 3-1  |

|         | 3.2  | MIA AN  | D BUFFER                            | 3-4  |

|         |      | 3.2.1   | Serial Data Bus Modulation Scheme   | 3-5  |

|         |      | 3.2.2   | Overview of MIA Operations          | 3-6  |

|         |      | 3.2.3   | IOP/MIA Interface and Timing        | 3-9  |

|         |      | 3.2.4   | Individual Circuits                 | 3-9  |

|         |      | 3.2.5   | MIA Buffer                          | 3-16 |

|         | 3.3  |         | OL MONITOR                          | 3-17 |

|         | 3.4  | CHANNI  | EL CONTROL                          | 3-22 |

|         |      | 3.4.1   | Channel Control Elements            | 3-22 |

|         |      | 3.4.2   | PCI/PCO Sequence                    | 3-25 |

|         |      | 3.4.3   | DMA Sequence                        | 3-27 |

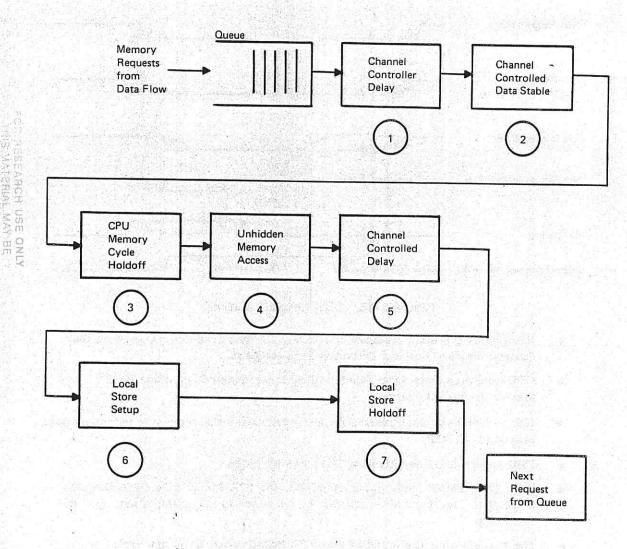

|         | 3.5  | DMA QU  | EUE                                 | 3-32 |

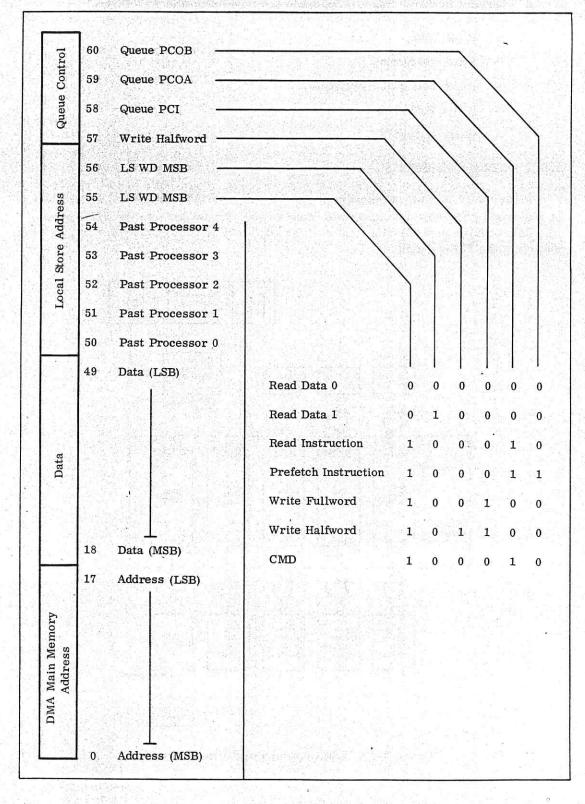

|         |      | 3.5.1   | Queue Format                        | 3-32 |

|         |      | 3.5.2   | Queue Operation                     | 3-34 |

|         |      | 3.5.3   | Queue Control Field                 | 3-35 |

|         |      | 3.5.4   | Queue Microdecode                   | 3-35 |

SM Wichita State University Libraries, Special Collections and University Archives Dr. James E. Tomayko Collection of NASA Documents 87-08 Box

Y LIBRARIES

# Table of Contents (cont)

| Secti | on    |          |                                        | Pag  |

|-------|-------|----------|----------------------------------------|------|

|       | 3.6   | PROCE    | SSOR ELEMENTS                          | 0.0  |

|       |       | 111001   | BOOK BELLEVIS                          | 3-3  |

|       |       | 3.6.1    | Microstore and Timing                  | 3-39 |

|       |       | 3.6.2    | Local Store                            | 3-44 |

|       |       | 3.6.3    | Data Flow Element                      | 3-4  |

|       | 3.7   | REDUN    | DANCY MANAGEMENT (RM) HARDWARE LOGIC   | 3-49 |

|       |       | 3.7.1    | Noncooperative Elements                | 3-49 |

|       |       | 3.7.2    | Cooperative Hardware/Firmware Elements | 3-53 |

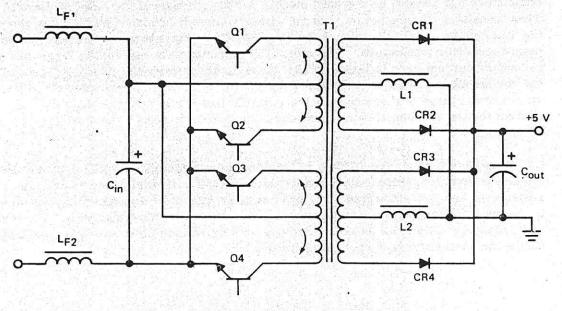

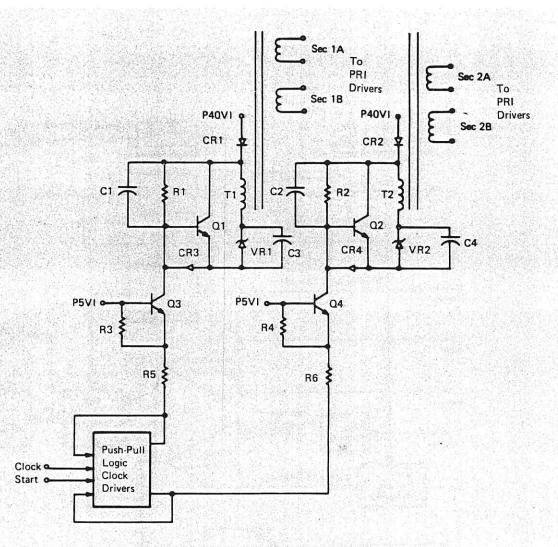

|       | 3.8   | POWER    | SUPPLIES                               | 3-58 |

|       |       | 3.8.1    | General                                | 0 5  |

|       |       | 3.8.2    | Functional Description                 | 3-55 |

|       |       | 3.8.3    | Power Supply Sequencing                | 3-57 |

|       |       |          | Power Supply Sequencing                | 3-62 |

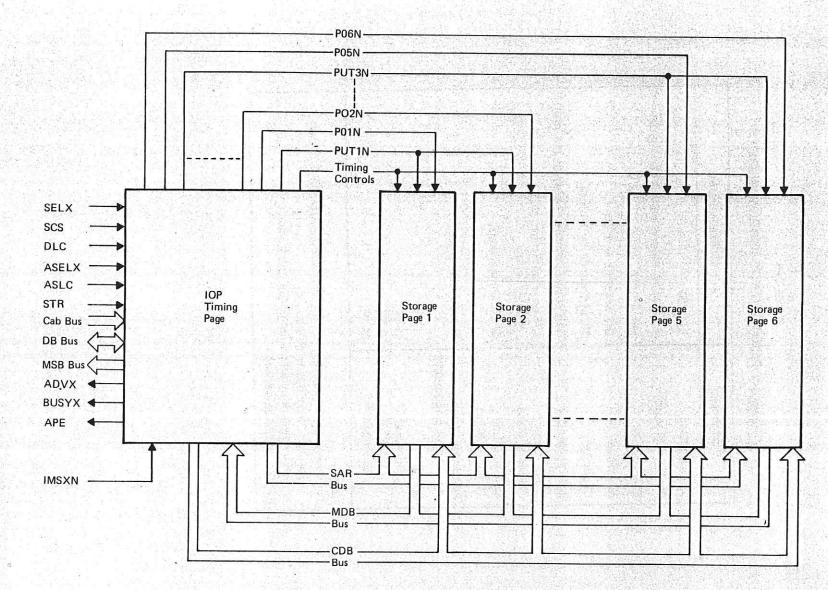

|       | 3.9   | IOP ME   | MORY                                   | 3-66 |

| 4     | IOP P | ACKAGIN  | NG (PROTOTYPE)                         | 4-1  |

|       | 4.1   | IOP HO   | USING                                  | 4-1  |

|       | 4.2   | MULTII   | LAYER INTERCONNECTION BOARDS           | 4-1  |

|       |       | 4.2.1    | Tape Cable Assembly Page               |      |

|       |       | 4.2.2    | IOP Backpanel                          | 4-3  |

|       |       | 4,2.3    | Core Storage Page                      | 4-3  |

|       |       |          |                                        | 4-4  |

|       | 4.3   | PAGE N   | IOMENCLATURE, LOCATION, AND CIRCUIT    |      |

|       |       | POPUI    | LATION                                 | 4-5  |

|       |       | A CODDAT | NA DA GWA GRAG                         |      |

|       | 4.4   | ASSEME   | BLY PACKAGING                          | 4-5  |

|       |       | 4.4.1    | IOP Assembly                           | 4-5  |

|       |       | 4.4.2    | Main Memory Assembly                   | 4-5  |

|       |       | 4.4.3    | Power Supply Assembly                  | 4-5  |

|       | 4.5   | STRUCT   | TURE DESIGN                            | 4-7  |

|       | 4.6   | IOP/CP   | U INTERCONNECTIONS                     | 4-7  |

|       |       |          |                                        | -    |

MS 87-08

Box 4

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives

WICHITA STATE UNIVERSITY LIBRARIES

SPECIAL COLLECTIONS

WATER SERVISON - WATERA VANVOTES CORES

V

# Table of Contents (cont)

| Section | on    |                                |                                         | Page         |

|---------|-------|--------------------------------|-----------------------------------------|--------------|

| 5       | IOP ' | EST EQUIPMENT                  |                                         | 5-1          |

|         | 5.1   | COMPUTER/COMPUTER TESTER       | • • • • • • • • • • • • • • • • • • • • | 5–1          |

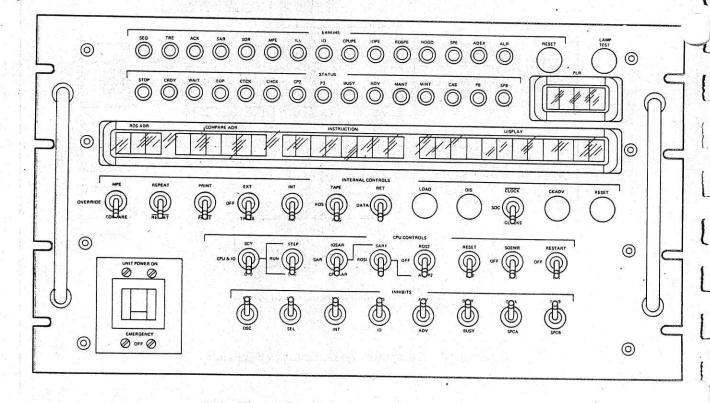

|         |       | 5.1.1 Panel Layout             |                                         | 5-7          |

|         |       | 5.1.2 Display Indicators       |                                         |              |

|         |       | 5.1.3 CPU Controls             |                                         | 5-8          |

|         |       | 5.1.4 Mode Select              |                                         | 5-9          |

|         |       | 5.1.5 Operation                |                                         |              |

| the new |       | 5.1.6 Error Indicators         |                                         | 5-11         |

|         |       | 5.1.7 Inhibit Switches         |                                         |              |

|         |       | 5.1.8 Status Indicators        |                                         | 5-11         |

|         |       | 5.1.9 Discrete Inputs          |                                         | 5-12<br>5-13 |

|         | 5.2   | IOP TESTER                     |                                         | 5-13         |

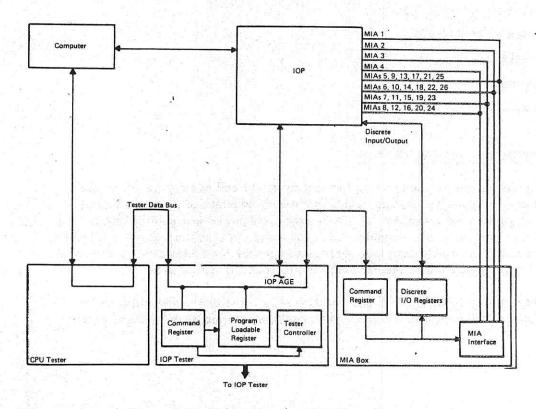

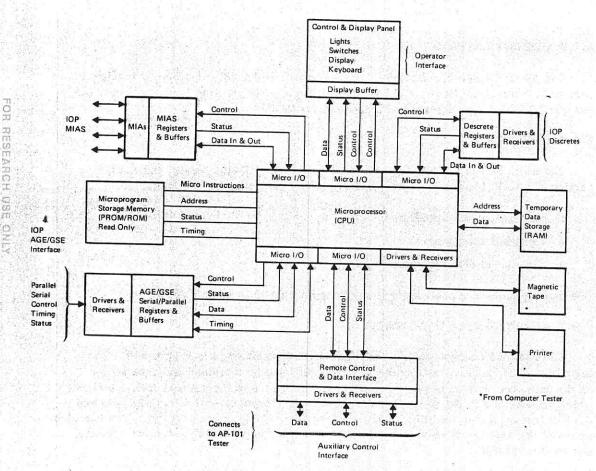

|         |       | 5.2.1 AP-101 Tester Interface  |                                         | 5-13         |

|         |       | 5.2.2 MIA Box Interface        |                                         | 0-13         |

|         |       | 5.2.3 Tester-to-IOP Interface  |                                         | 5-13         |

|         |       | 5.2.4 Tester — IOP Controls    |                                         | 5-13<br>5-17 |

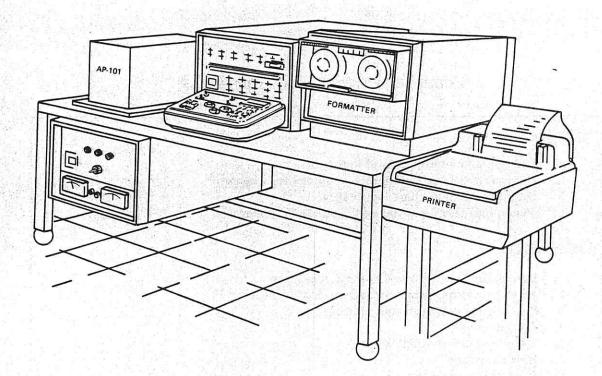

|         | 5.3   | MAGNETIC TAPE TRANSPORT        |                                         | 5-18         |

|         | 5.4   | LINE PRINTER                   |                                         | 5-18         |

| 6       | DIFF  | ERENCES BETWEEN IOP DEVELOPMEN | IT AND                                  |              |

|         | PRO   | TOTYPE MODELS                  |                                         | 6-1          |

SW 87-08

SITY LIBRARIES

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives Box 42

# LIST OF ILLUSTRATIONS

| Figure |                                                     | Page         |

|--------|-----------------------------------------------------|--------------|

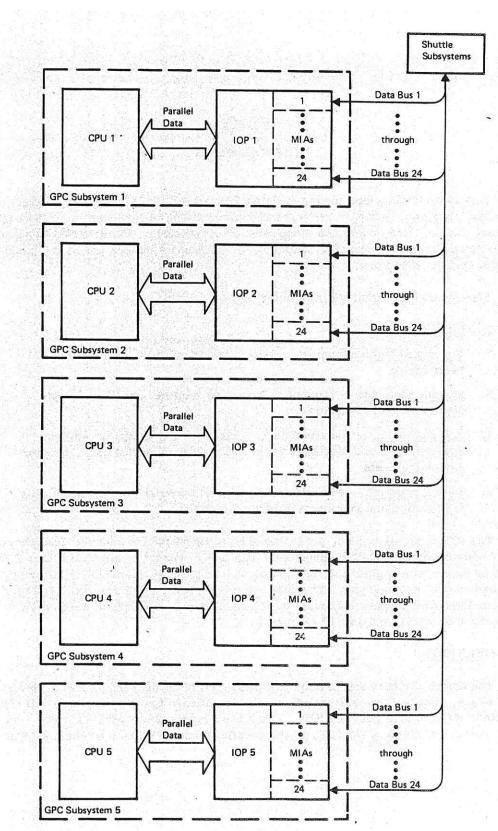

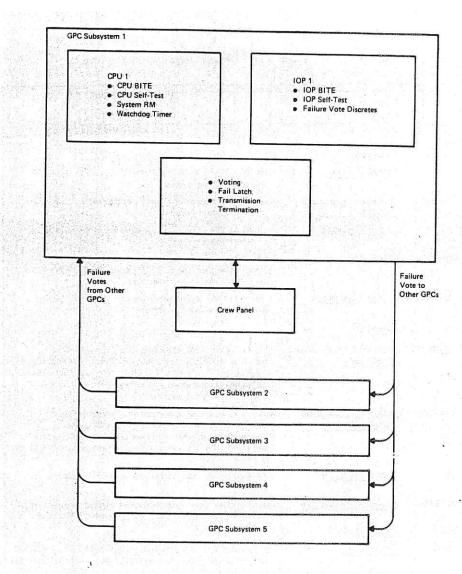

| 1-1    | Basic Five GPC Shuttle Data Processing System       | 1-2          |

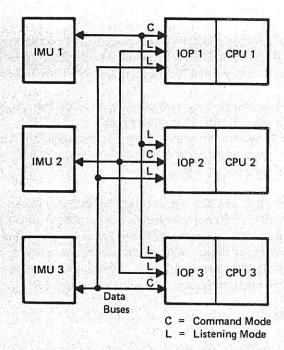

| 1-2    | Example of Command and Listen Modes                 | 1-4          |

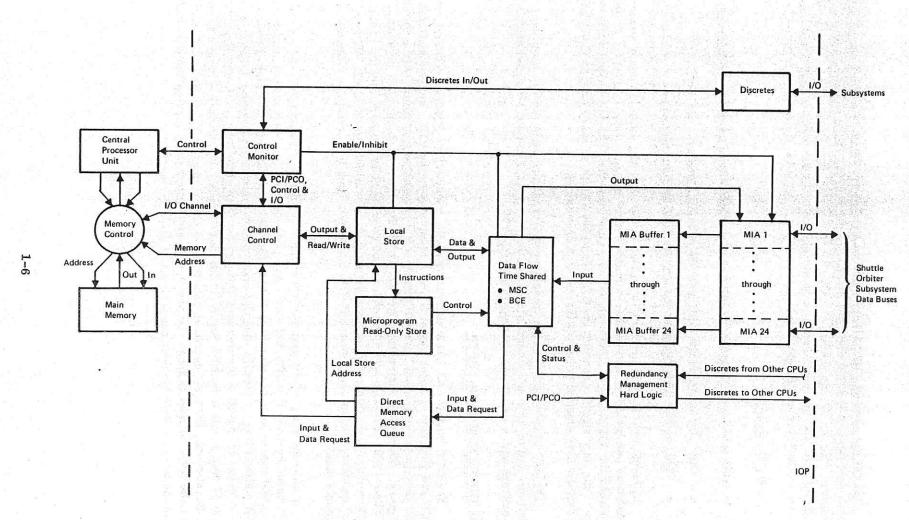

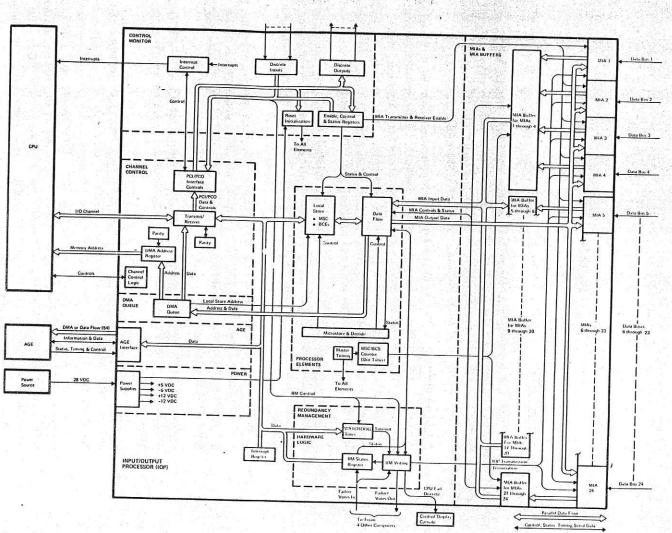

| 1-3    | Input/Output Processor Functional Block Diagram     | 1-6          |

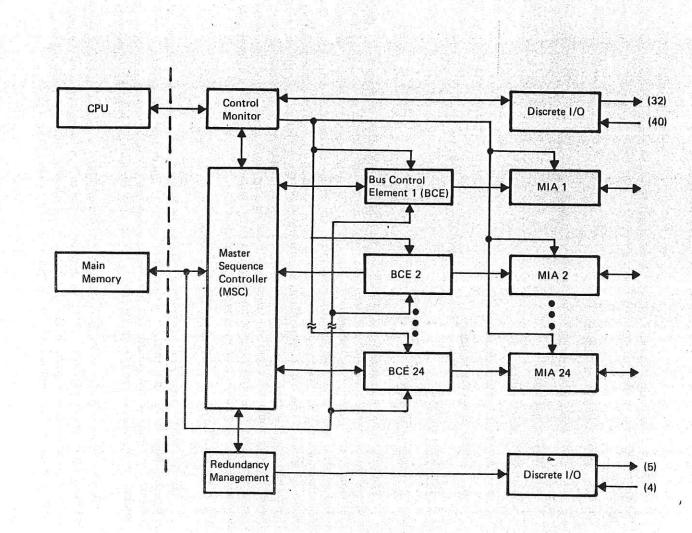

| 2-1    | IOP Functional Block Diagram                        | 2-2          |

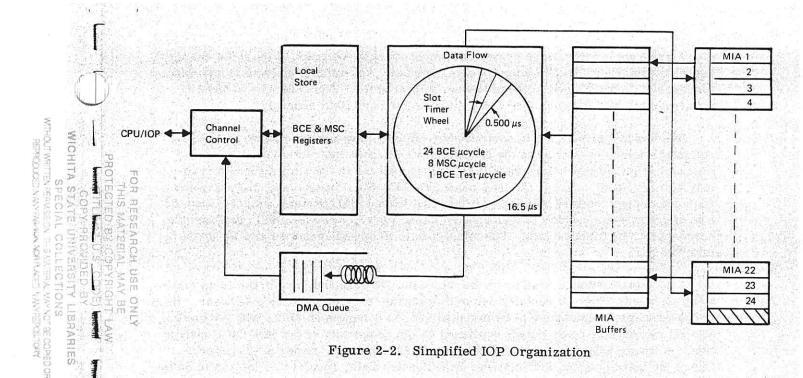

| 2-2    | Simplified IOP Organization                         | 2-3          |

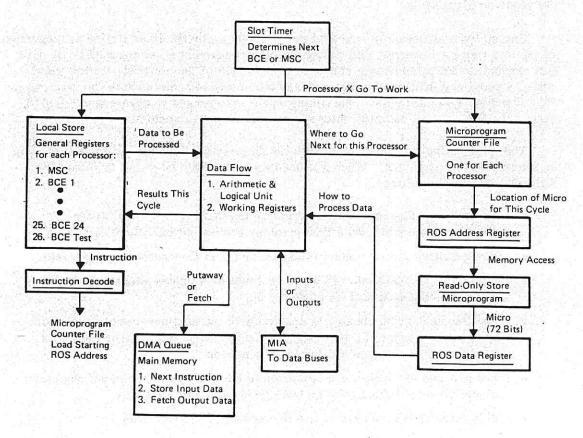

| 2-3    | Microcycle Information Flow                         | 2-3          |

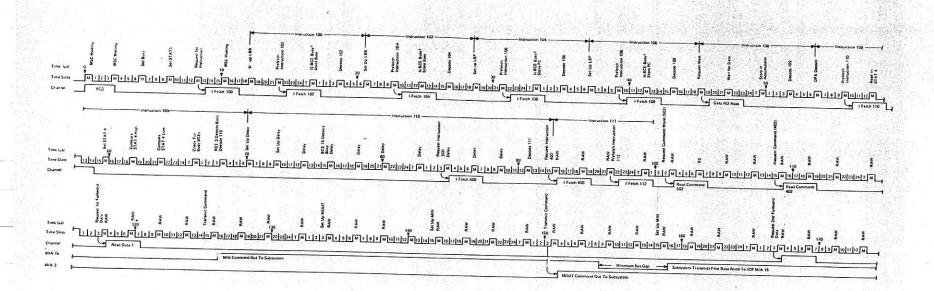

| 2-4    | Typical IOP Instruction Timing                      | 2-6          |

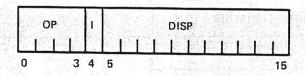

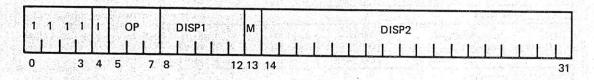

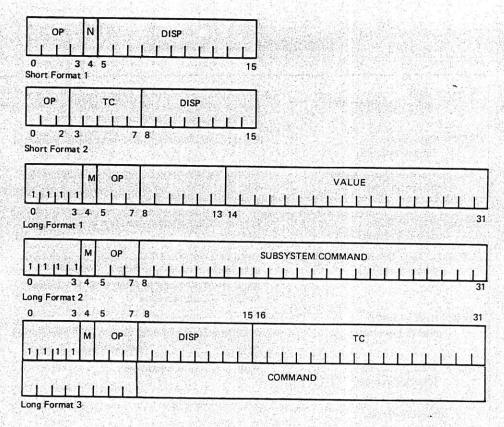

| 2-5    | Basic MSC Instructions Formats                      | 2-26         |

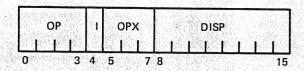

| 2-6    | BCE Instruction Formats                             | 2-31         |

| 2-7    | Functional Summary of Fault Detection               | 2-36         |

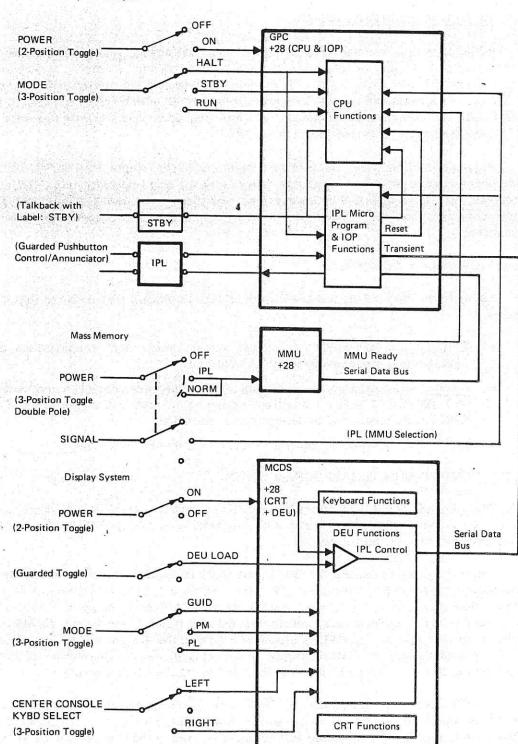

| 2-8    | Cockpit/GPC/MMU/MCDS Functional Interface Summary   | 2-44         |

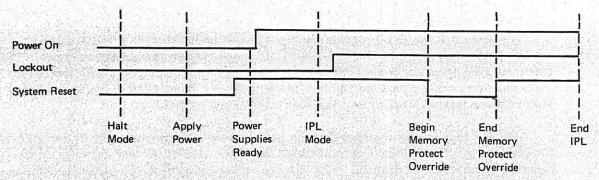

| 2-9    | IPL Power-On Sequencing                             | 2-47         |

| 3-1    | IOP Elements                                        |              |

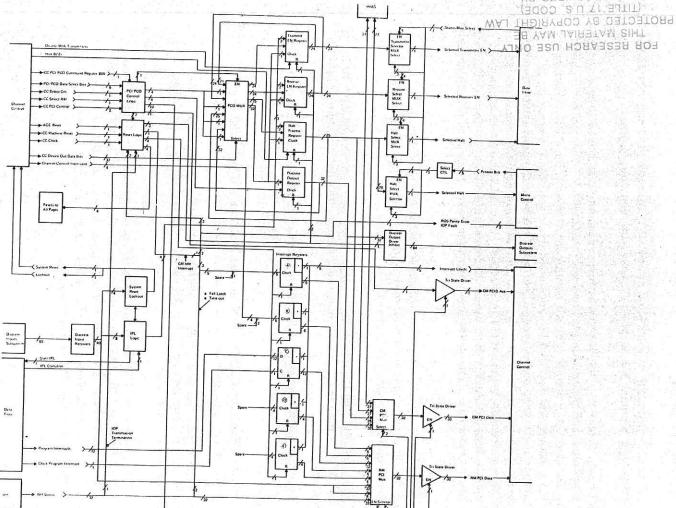

| 3-2    | Detailed System Diagram                             | 3-2          |

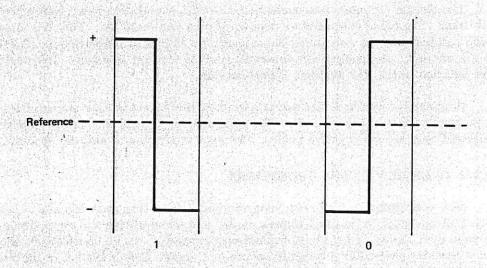

| 3-3    | Biphase-Level Manchester II Code Modulation Scheme  | 3-3          |

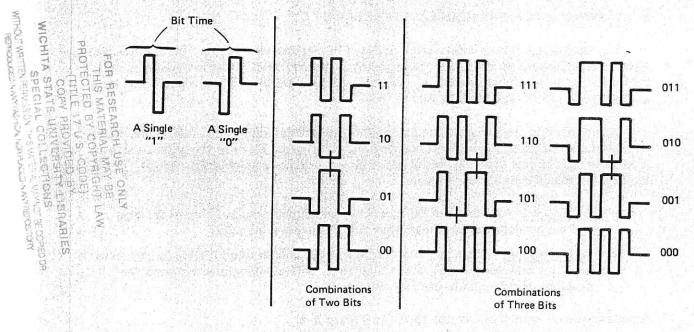

| 3-4    | Sample Manchester II Code Bit Combinations          | 3-5          |

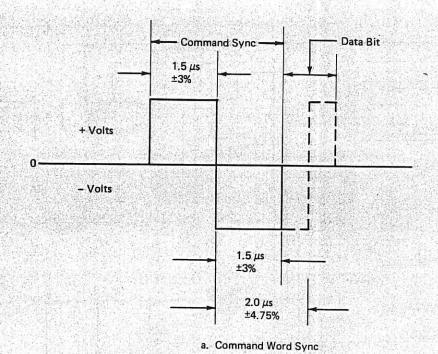

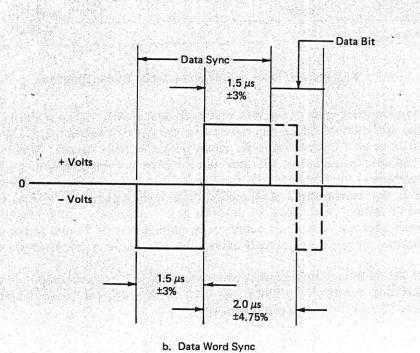

| 3-5    | Command and Data Word Sync                          | 3-6          |

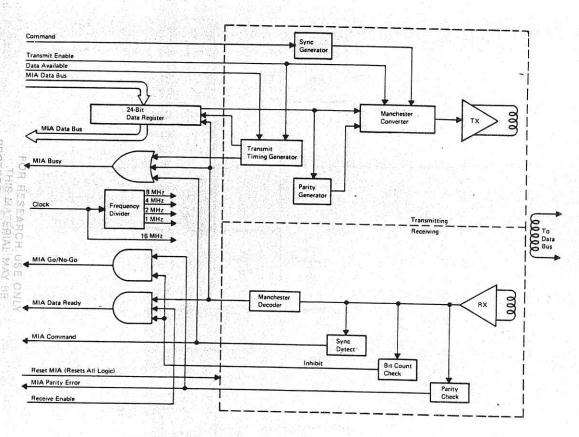

| 3-6    | MIA Block Functional Block Diagram                  | 3-7          |

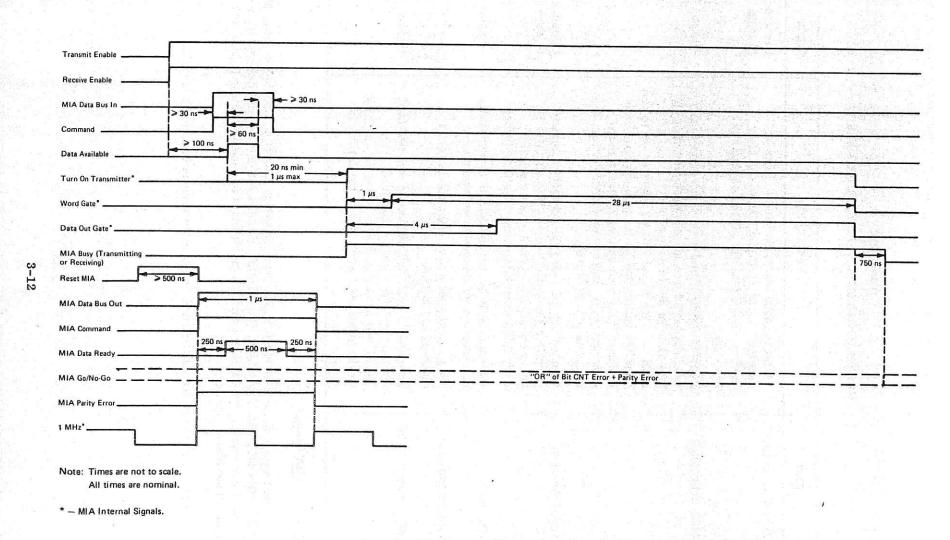

| 3-7    | IOP/MIA Interface and Timing Signals                | 3-8          |

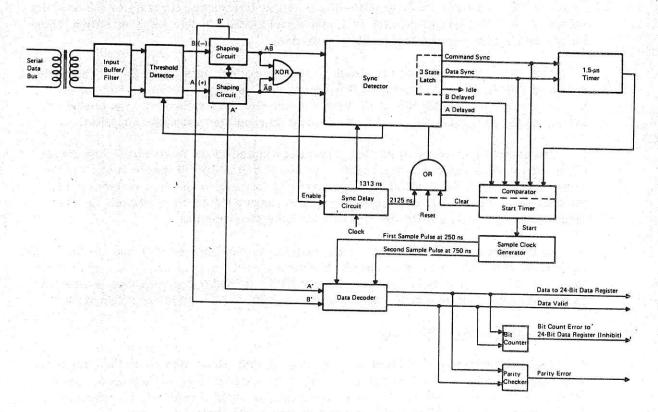

| 3-8    | MIA Receiving Circuits Functional Block Diagram     | 3-12         |

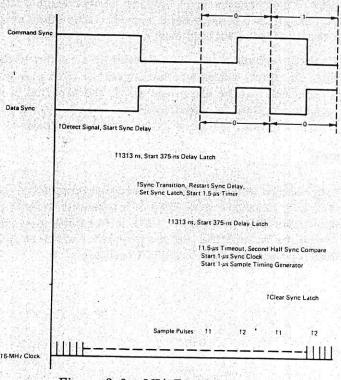

| 3-9    | MIA Receiver Timing                                 | 3-14         |

| 3-10   | MIA Buffer Functional Block Diagram                 | 3-15         |

| 3-11   | Control Monitor Element Functional Diagram          | 3-18         |

| 3-12   | Channel Control and Interfaces                      | 3-20         |

| 3-13   | PCI/PCO Sequence                                    | 3-24         |

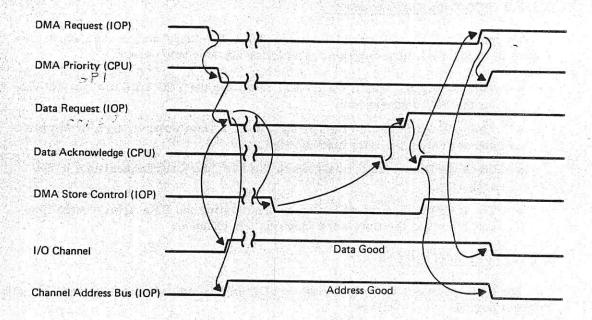

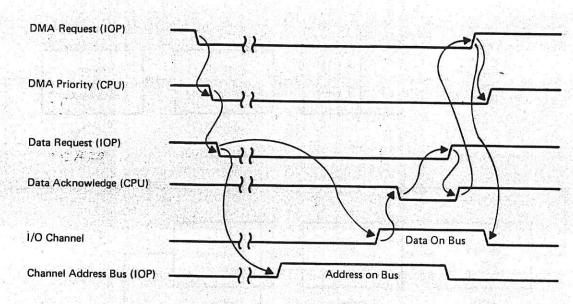

| 3-14   | DMA Input Sequence                                  | 3-26         |

| 3-15   | DMA Output Sequence                                 | 3-28         |

| 3-16   | Channel Control Timing                              | 3-29         |

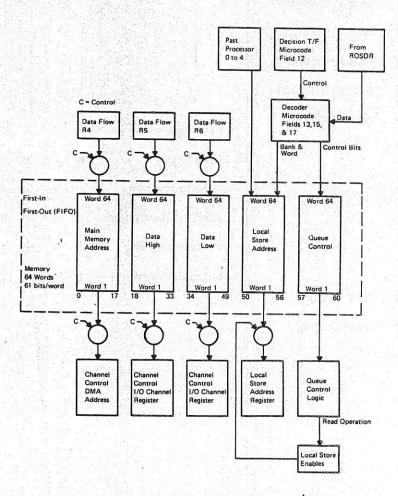

| 3-17   | DMA Queue Functional Diagram                        | 3-30         |

| 3-18   | Processor Elements Data Paths                       | 3-34         |

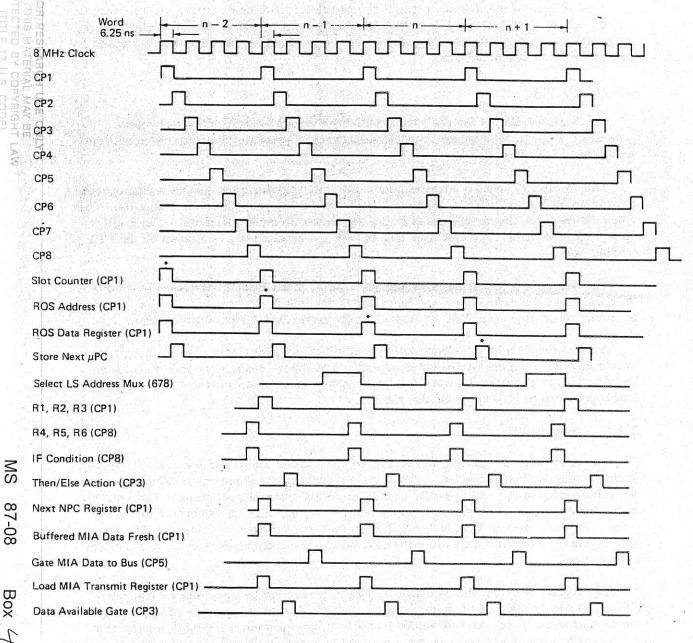

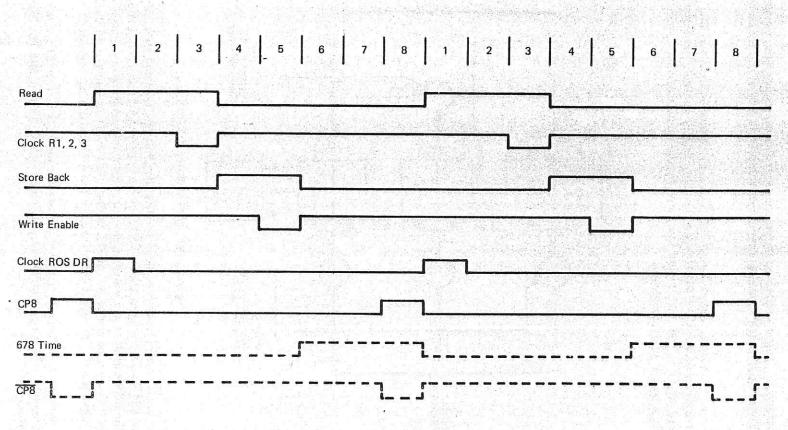

| 3-19   | IOP Timing Diagram                                  | 3-38         |

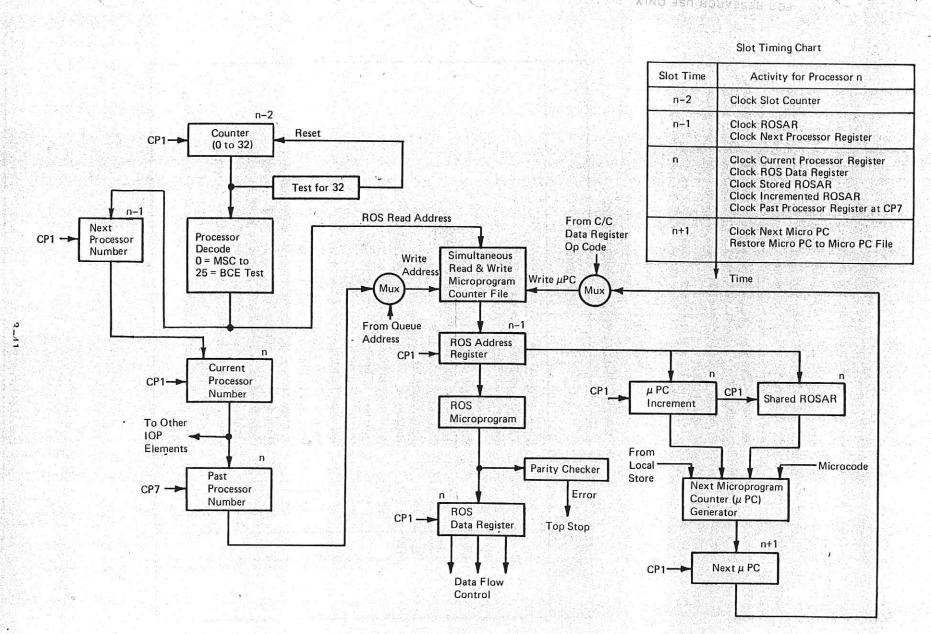

| 3-20   | Microstore and Timing                               | 3-40         |

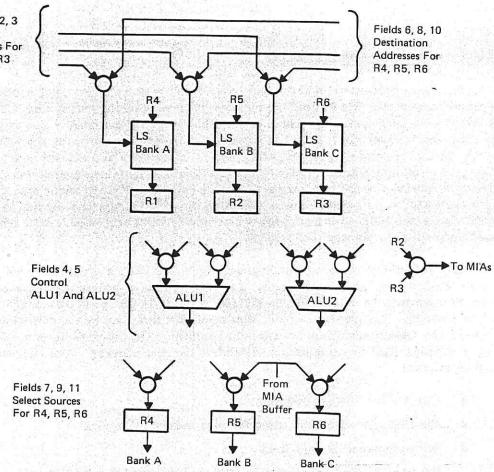

| 3-21   | Microprogram Control of Data Flow                   | 3-41         |

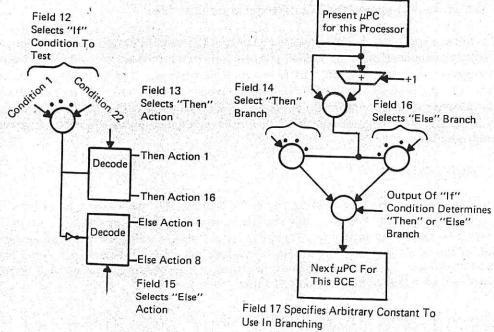

| 3-22   | Microprogram Control of Actions and Micro Branching | 3-43         |

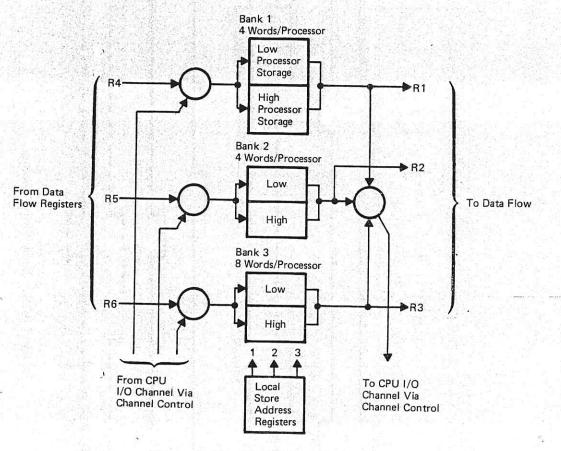

| 3-23   | Local Store Data Paths                              | 3-43<br>3-45 |

|        |                                                     |              |

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives

LIBRARIES

# List of Illustrations (cont)

| Figure |                                              | Page |

|--------|----------------------------------------------|------|

| 3-24   | Local Store Timing                           | 3-46 |

| 3-25   | Data Flow Timing                             | 3-48 |

| 3-26   | Redundancy Management Hardware Logic Diagram | 3-50 |

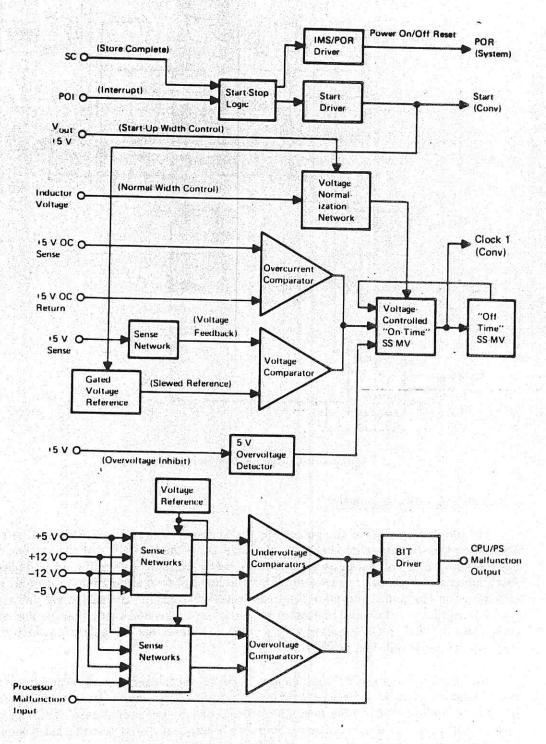

| 3-27   | IOP Power Supply Block Diagram               | 3-56 |

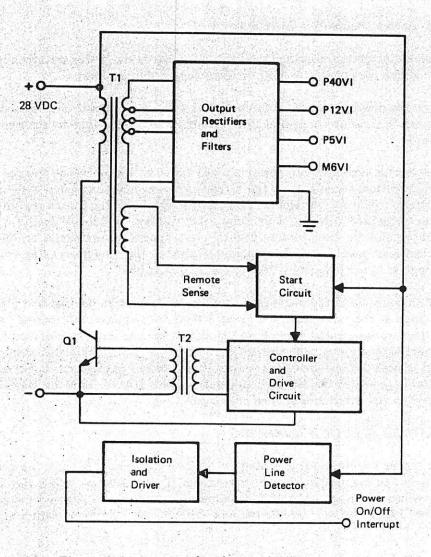

| 3-28   | Input Filter and Converter                   | 3-57 |

| 3-29   | Converter Driver Circuit                     | 3-59 |

| 3-30   | +5-V Controller Block Diagram                | 3-60 |

| 3-31   | Internal Voltage Block Diagram               | 3-61 |

| 3-32   | Power Supply On/Off Timing Diagram           | 3-63 |

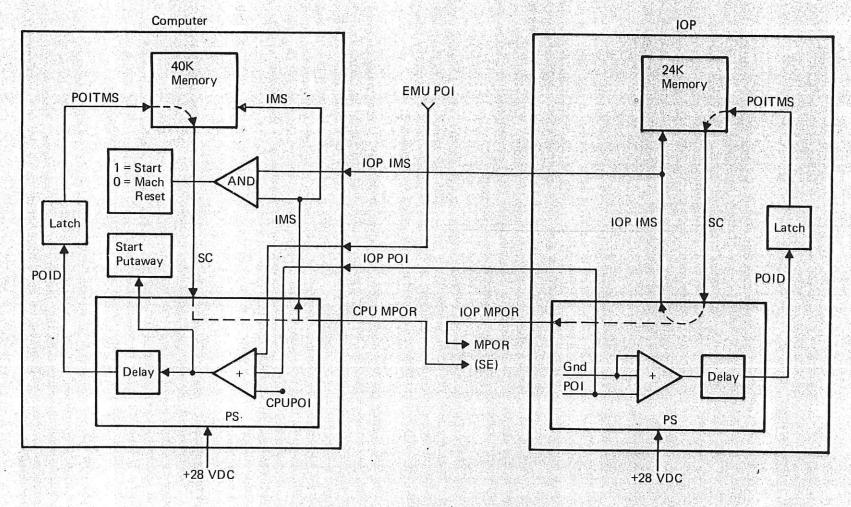

| 3-33   | Power Up/Down Controls                       | 3-65 |

| 3-34   | IOP Memory Block Diagram 24K × 36 Bits       | 3-67 |

|        |                                              | 0 0. |

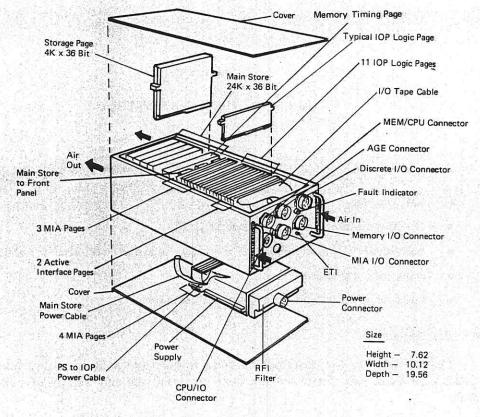

| 4-1    | Exploded View of IOP                         | 4-2  |

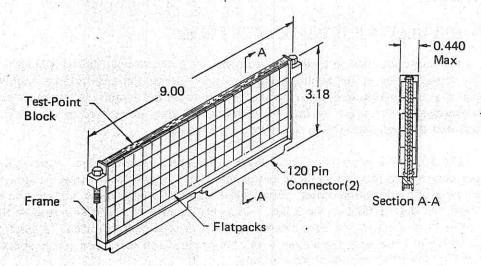

| 4-2    | Basic IOP Page                               | 4-2  |

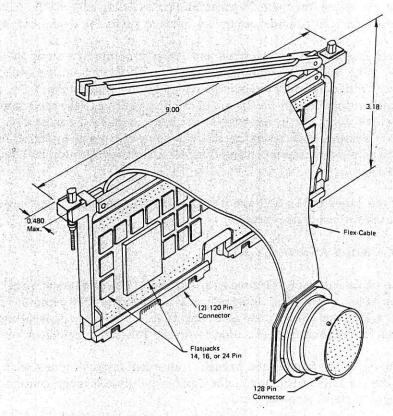

| 4-3    | Tape Cable Assembly                          | 4-4  |

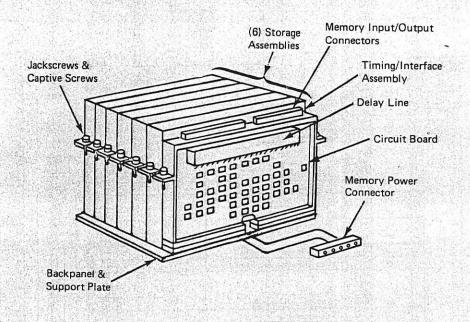

| 4-4    | Main Memory Assembly — 24K, 36-Bit           | 4-7  |

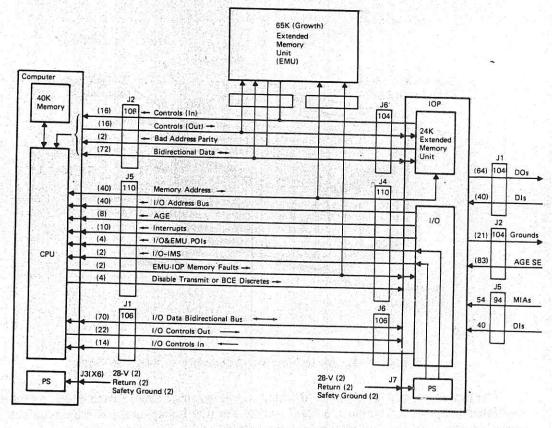

| 4-5    | GPC Prototype Model Interface Configuration  | 4-8  |

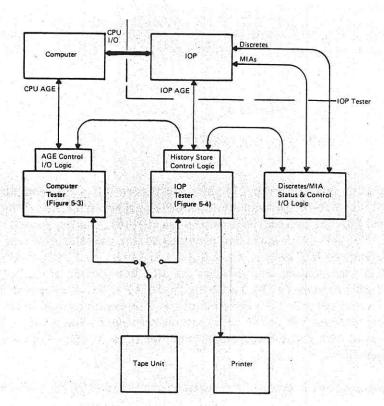

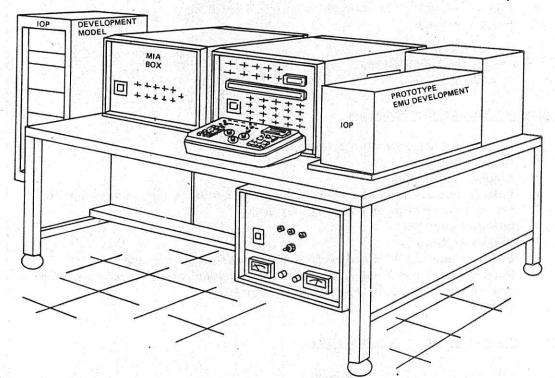

| 5–1    | IOP and Test Equipment Interface             | 5-2  |

| 5-2    | IOP Tester Interface Data Bus                | 5-2  |

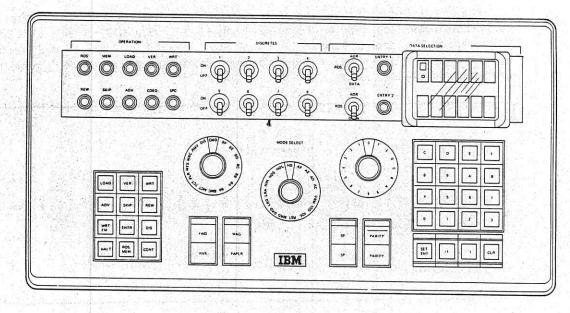

| 5-3    | AP-101 Test Set                              | 5-4  |

| 5-4    | IOP Test Set                                 | 5-4  |

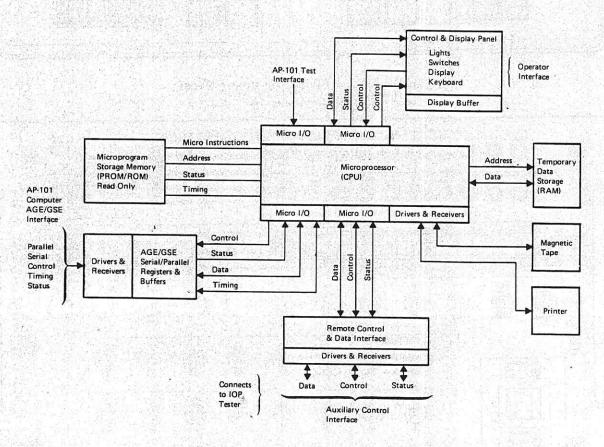

| 5-5    | Computer Tester Block Diagram                | 5-5  |

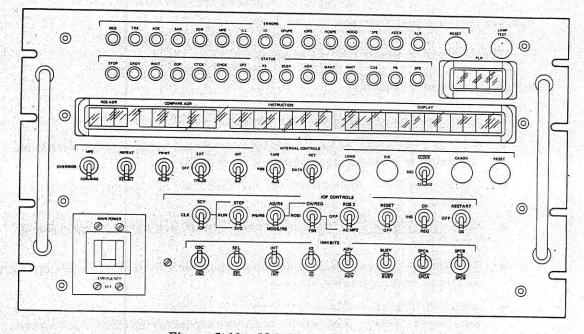

| 5-6    | CPU Tester Lower Panel                       | 5-6  |

| 5-7    | CPU Tester Upper Panel                       | 5-6  |

| 5-8    | IOP Tester Block Diagram                     | 5-14 |

| 5-9    | IOP/AGE Interface                            | 5-15 |

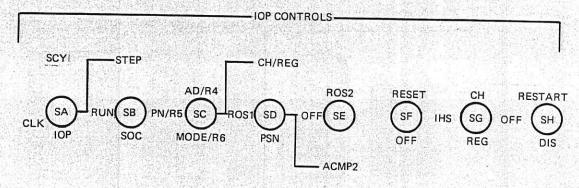

| 5-10   | IOP Controls                                 | 5-17 |

| 5-11   | IOP Tester Upper Panel                       | 5-17 |

| 5-12   | IOP Tester Lower Panel                       | 5-18 |

| 6-1    | IOP Development Model Packaging              | 6-1  |

| 6-2    | Logic Allocation for IOP Development Model   | 6-2  |

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives SM

CTI LIBRARIES

Box 42

# LIST OF TABLES

| Table |                                                    | Page |

|-------|----------------------------------------------------|------|

| 1-1   | IOP Slot Timing                                    | 1-7  |

| 2-1   | Example MSC Program                                | 2-8  |

| 2-2   | Example BCE Programs                               | 2-9  |

| 2-3   | PCI and PCO Instructions                           | 2-10 |

| 2-4   | Redundancy Management Status Register              | 2-18 |

| 2-5   | MSC Characteristics                                | 2-20 |

| 2-6   | MSC Instructions                                   | 2-25 |

| 2-7   | MSC Local Store Usage                              | 2-27 |

| 2-8   | MSC Status Register                                | 2-27 |

| 2-9   | BCE Characteristics                                | 2-28 |

| 2-10  | BCE Instruction Summary                            | 2-32 |

| 2-11  | BCE Local Store Register Allocations               | 2-34 |

| 2-12  | BCE Status Register                                | 2-35 |

| 2-13  | IOP Interrupt Detected Errors                      | 2-37 |

| 2-14  | MSC Firmware Detected Errors                       | 2-38 |

| 2-15  | BCE Firmware Detected Errors                       | 2-39 |

| 2-16  | GCP and DEU Load Procedure                         | 2-45 |

| 2-17  | IOP/IPL Microroutine Sequence                      | 2-46 |

| 3-1   | Processor Elements to MIA Signals                  | 3-10 |

| 3-2   | MIA to Processor Elements Signals                  | 3-11 |

| 3-3   | Control Monitor Reset Logic Summary                | 3-23 |

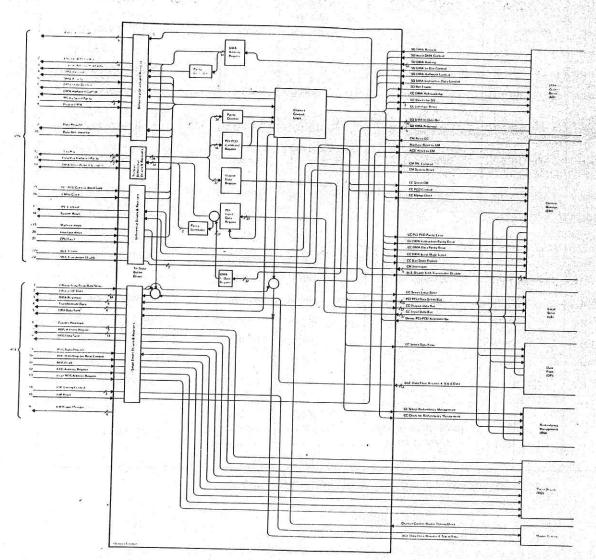

| 3-4   | IOP/CPU Interface Signal Descriptions              | 3-31 |

| 3-5   | Queue Register Format                              | 3-33 |

| 3-6   | Micro Decoding by DMA Queue                        | 3-36 |

| 3-7   | Micro Instruction Field Description                | 3-42 |

| 3-8   | IOP Memory Performance Characteristics             | 3-68 |

| 4-1   | Page Nomenclature, Location and Circuit Population | 4-6  |

| 4-2   | CPU/IOP Connector Pin Functions                    | 4-9  |

| 5–1   | Computer Tester Characteristics                    | 5-3  |

| 5-2   | Mode Select Switch Functions                       | 5-9  |

| 5-3   | Data Format for AGE Data B00-53 (54 Lines) IOP→AGE | 5-15 |

| 6-1   | Packaging Differences Between IOP Configurations   | 6-3  |

| 6-2   | Hardware Limitations of Development Model IOP      | 6-3  |

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives Box 42

MS

Y LIBRARIES

ix

| 그네 12명 [인종화 : 12명 ] 다 그리고 말했다면 바다 생각이 있다니다. |                            |

|---------------------------------------------|----------------------------|

| ACC                                         | Accumulator                |

| AGE                                         | Aerospace Ground Equipment |

| ALU                                         | Arithmetic Logical Unit    |

| BA                                          | Boundary Alignment         |

| BASE                                        | Base Register              |

| BCE                                         | Bus Control Element        |

| BITE                                        | Built-In Test Equipment    |

| BTO                                         | Block Timeout              |

| BU                                          | Branch Unconditional       |

| C                                           | Control                    |

| cc                                          | Channel Control            |

| cc                                          | Cross-Couple               |

| CCR                                         | Cross-Couple Register      |

| CM                                          | Control Monitor            |

| CMD                                         | Command                    |

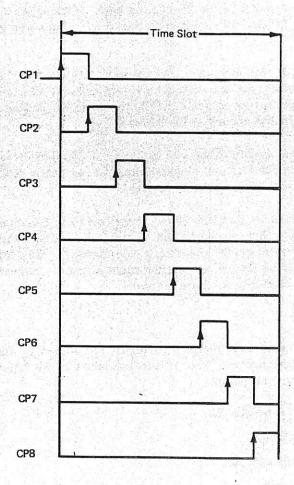

| CP                                          | Clock Pulse                |

| CPU                                         | Central Processing Unit    |

| CRT                                         | Cathode Ray Tube           |

| DC                                          | Direct Current             |

| DEU                                         | Display Electronics Unit   |

| DF                                          | Data Flow                  |

| DI                                          | Discrete Input             |

| DIN                                         | Direct-In Instruction      |

| DIP                                         | Dual In-Line Package       |

| DISP                                        | Displacement               |

| DLY                                         | Delay                      |

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives SM 87-08

WICHITA STATE UNIV

FOR RESEARCH USE

Box 42

lb

| 그 교통하다 다른 그는 이 이번에 다른 경기를 들어 하고 있다. 그리는 아이를 다른 부모를 가지 않는데 되었다. | 선지에 하다면서야근 5이 없어졌다. 네트 전에 보고 있다. 그렇게 하는데 무슨데 그 것이 보고 있다. 그 그 네트를 다 하다 하다. |

|----------------------------------------------------------------|---------------------------------------------------------------------------|

| DO                                                             | Discrete Output                                                           |

| DU                                                             | Display Unit                                                              |

| ECR                                                            | External Call Register                                                    |

| EIU                                                            | Engine Interface Unit                                                     |

| EMI                                                            | Electromagnetic Interference                                              |

| EP/MCM                                                         | Extended Performance/Modular Core Memo                                    |

| EMU                                                            | Extended Memory Unit                                                      |

| ETI                                                            | Elapsed Time Indicator                                                    |

| FCOS                                                           | Flight Control Operations System                                          |

| FIFO                                                           | First-In/First-Out                                                        |

| ft                                                             | Foot or Feet                                                              |

| FTP                                                            | Functional Test Program                                                   |

| FW                                                             | Fullword                                                                  |

| GPC                                                            | General-Purpose Computer                                                  |

| GSE                                                            |                                                                           |

| HW                                                             | Halfword                                                                  |

| IMM                                                            | Immediate                                                                 |

| IMS                                                            | Inhibit Main Store                                                        |

| IMU                                                            | Inertial Measurement Unit                                                 |

| in                                                             | Inch or Inches                                                            |

| 1/0                                                            | Input/Output                                                              |

| IOP                                                            | Input/Output Processor                                                    |

| IOPIMS                                                         | Input/Output Processor Inhibit Main Store                                 |

| IPL                                                            | Initial Program Load                                                      |

| IPLC                                                           | Initial Program Load Complete                                             |

| ITO                                                            | Initial Timeout                                                           |

| IUAR                                                           | Interface Unit Address Register                                           |

| К                                                              | 1024                                                                      |

| КВ                                                             | Keyboard                                                                  |

| - II                                                           |                                                                           |

Direct Memory Access

Pound(s)

HIS HATEMAL PROTECTED BY COR

FOR RESEARCH USE ONLY

| LBR  | Load Base Register                            |

|------|-----------------------------------------------|

| LC   | Inductor-Capacitor                            |

| LCC  | Load Cross-Couple Register                    |

| LRU  | Line-Replaceable Unit                         |

| LS   | Local Store                                   |

| LSB  | Least Significant Bit                         |

| LSI  | Large-Scale Integration                       |

| LTOR | Load Timeout Register                         |

| MA   | Micro Architecture                            |

| MAL  | Malfunction                                   |

| MCDS | Multipurpose CRD Display Subsystem            |

| MDM  | Modulator Demodulator                         |

| MHz  | MegaHertz (1 $\times$ 10 <sup>6</sup> cycles) |

| MIA  | Multiplexer Interface Adapter                 |

| MIB  | Multilayer Interconnection Board              |

| MM   | Mass Memory                                   |

| MMU  | Mass Memory Unit                              |

| MPOR | Master Power-On Reset                         |

| ms   | Millisecond(s)                                |

| MSB  | Most Significant Bit                          |

| MSC  | Master Sequence Controller                    |

| MSI  | Medium Scale Integration                      |

| MTO  | Maximum Timeout Register                      |

| MTS  | Microprogram Test System                      |

| NOP  | No Operation                                  |

| OCC  | Overcurrent Comparator                        |

| OP   | Operation                                     |

| OVC  | Overvoltage Comparator                        |

| PC   | Program Counter                               |

| PCI  | Program Control Input                         |

| PCO  | Program Control Output                        |

|      |                                               |

|      |                                               |

87

Box

BRARIES

xiii

RSITY LIBRARIES

| VVICNITA                                 | Dr. Jar                      | MS    |

|------------------------------------------|------------------------------|-------|

| vvichita State University Libraries, Spe | Dr. James E. Tomayko Co      | 87-08 |

| ty Libraries, Sp                         | o Collection of              | Box 4 |

| Special Collections and University       | Collection of NASA Documents | かれて   |

| ions and Univ                            | nents                        | 11111 |

| ersity Archiv                            | ~                            | 7     |

| /es                                      |                              |       |

Ch xoi

| 마트의 조지 그림 나는 의료 개발 중에 일반한 사회의 가입하는 남이 되었다. 그는 해 때 부모님들에서 목표하고 내려왔다. 그리고 하였다. |                              |

|------------------------------------------------------------------------------|------------------------------|

| svc                                                                          | Supervisor Call              |

| TDL                                                                          | Transmit Data Long (Format)  |

| TDS                                                                          | Transmit Data Short (Format) |

| T/F                                                                          | True/False                   |

| TO                                                                           | Timeout                      |

| T/R                                                                          | Transmit/Receive             |

| TTL                                                                          | Transistor-Transistor Logic  |

| v                                                                            | Volt(s)                      |

| w                                                                            | Watt(s)                      |

| WAT                                                                          | Wait                         |

| WR                                                                           | Working Register             |

| XMT                                                                          | Transmitter                  |

| Ω                                                                            | Ohm(s)                       |

| . 전 1일, 그런 1일                            |                              |

xiv

Section 1

INTRODUCTION

SM 87-08

WICHITA STATE UNIVERSI

SPECIAL COLLEC

SPECIAL COLLEC

SPECIAL COLLEC

SPECIAL COLLEC

SPECIAL COLLEC

THIS MATERIAL MAY BE THIS MATERIAL MAY BE LAW

Box 42

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives

#### Section 1

### INTRODUCTION

This manual describes the Input/Output Processor (IOP) Subsystem design. It provides functional hardware and software information. A programmer reference manual entitled 'IOP Principles of Operation' is available. The IOP and Central Processing Unit (CPU) use IBM System/4 Pi components manufactured and packaged at IBM Owego, New York.

This manual is organized in five sections as follows:

- 1. Introduction

- System Elements Describes hardware, timing, and signal flow details of the IOP design

- IOP Packaging Provides line-replaceable unit (LRU) packaging descriptions, and identifies replaceable subassemblies and connector pin assignments

- Test Equipment Provides interface and test and checkout capability information and summarizes test procedures

The IOP is an all-digital, programmable, time-shared processor that transmits and receives Shuttle Orbiter subsystems data under control of the CPU. The CPU processing functions are guidance, navigation and control, performance monitoring, and payload control management. The data processing involved is accomplished by five identical general-purpose computer (GPC) subsystems. Each GPC subsystem is comprised of a CPU and an IOP (Figure 1-1).

### 1.1 OVERVIEW

The Shuttle Orbiter subsystems are connected to the IOP by 24 serial, 1-MHz data buses. Data bus-to-IOP interface is accomplished by 24 multiplexer interface adapters (MIA) located in each IOP. The MIAs convert Manchester II coded serial data words, received by the IOP, to the parallel format required by the CPU/IOP.

MS

87-08

WICHITA STA

UNIVERSITY LIBRARIES

VAN NOT BE COPIED OR NAVPREPOSITORY

THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW

FOR RESEARCH USE ONLY

Figure 1-1. Basic Five GPC Shuttle Data Processing System

87

W

Conversely, the MIAs convert the CPU/IOP parallel word format (to be transmitted over the data buses) to the Manchester II coded serial data format. Also, the MIAs generate and check data parity used for transmission error detection.

The IOP handles the processing required to service the 24 data buses. An IOP buffers and controls input/output (I/O) operations for the CPU. The IOP is timeshared by the 24 data buses as determined by a fixed sequence timer. Data processing programs for the IOP (stored in main memory) are independent of CPU programs and have their own unique instruction set.

Functionally, the CPU and IOP share main memory. After an IOP program has been initiated by the CPU, a direct memory access (DMA) channel between the IOP and main memory is used to obtain the IOP program instructions required to fetch the output data or put away input data. This DMA technique provides common data storage to eliminate CPU-to-IOP I/O data transfers. However, the DMA technique produces CPU/IOP contention for main memory, thereby reducing CPU processing capacity.

### 1.1.1 INSTRUCTIONS

IOP and CPU instructions are defined by microcoding techniques. A read-only storage (ROS) is employed for controlling a fixed sequence of operations and internal data paths to be executed for each instruction. This provides an efficient and flexible technique to define the exact processing requirements for each IOP instruction.

## 1.1.2 DATA BUS OPERATING MODES

IOP data bus channel operating modes are

- Command

- Listen

In the Command mode, I/O data (to or from an interfacing Shuttle subsystem) will be processed. In the Listen mode, only input data will be processed. A Master Sequence Controller (MSC) is used to control all of the Bus Control Elements (BCEs) and to route data from one MIA channel to another through the IOP. Each MIA channel is controlled by its BCE.

Use of typical Command and Listen modes are illustrated in Figure 1-2. Note that avionics functions are triple redundant; i.e., three completely independent subsystems are designated. For example, redundant information received from each of three inertial measuring units (IMU) by each GPC should be the same. IMU 1 is assigned to and controlled by GPC 1; IMU 2 with GPC 2, etc. GPC 1 provides all command functions on the data bus associated with IMU 1, while GPC 2 and 3 monitor (listen).

Wichita State University Libraries, Special Collections and University Archives

Figure 1-2. Example of Command and Listen Modes

GPCs 2 and 3 are connected in a similar manner with their respective systems. A malfunction in one system will be detected by the other two, and corrective action will be taken to eliminate the faulty unit from control:

#### 1.1.3 FAULT DETECTION

Fault detection in the IOP is achieved by redundancy management (RM) software. programmed self-test, and built-in test equipment (BITE). These methods provide fail-safe data transfers on the MIA data channels. Since all critical functions are at least triple redundant at the subsystem level, an individual IOP failure will not affect the operation of the Shuttle Orbiter systems.

A Watchdog timer (BITE functional) is located in the RM hard logic. This timer is set and reset under program control. Should program control be lost, the Watchdog timer will time out, producing an IOP transmission termination, thereby failsafing the GPC subsystem. RM hard logic contains voting logic, so that good computers can force recognition of a failed computer. RM hard logic in each IOP receives four individual votes from the other computers while transmitting up to four votes of its own. An IOP RM hard logic that receives two or more votes, indicating that its operation is incorrect, actuates a failure latch, and any further MIA transmission is terminated. All transmission termination is under CPM software control via the termination control latches.

An IOP Self-Test program may be executed along with the background data processing program to detect IOP failures. Corrective action is taken by the program as required. Crew notification and Watchdog timer Time-Out are possible program actions.

POR RESEARCH USE ON THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT COPY PROVIDED BY COPE AND COPYRIGHT COPY PROVIDED BY COPYRIGHT COPY PROVIDED BY COPYRIGHT COPY PROVIDED BY COPYRIGHT COPYR

One of the principle BITE techniques used is parity. Data transfers on the data buses and between the IOP and CPU use parity protection. Main memory and microprogram memory words contain an extra bit to provide parity protection. Each data transmission and memory access is parity checked. Other forms of BITE are contained in the MIAs and power supplies.

#### 1.1.4 PACKAGING

A GPC subsystem is packaged in two line replaceable units (LRU) as follows:

- One LRU contains the CPU and 40K of main memory.

- The second LRU contains the IOP and 24K of main memory.

Although 24K of main memory is located in the IOP, the total 64K main memory is treated as one memory, and neither portion of main memory (40K or 24K) is dedicated to either the IOP or CPU. Both the IOP and CPU view the total 64K as one main memory. The only significance that the IOP has to the 24K of memory located in its LRU is that the IOP supplies power to that portion of memory.

The IOP is constructed using transistor-to-transistor logic (TTL). Low-power, medium- and large-scale integration circuits are used. The GPC has been designed to operate with a total power consumption of 640 W.

## 1.2 OPERATING PRINCIPLES

The CPU initiates all I/O actions through the execution of Program Control Input (PCI) and Program Control Output (PCO) instructions to the IOP. Independent of the CPU (except for initiation), the IOP executes its own programs, which reside in main memory. These IOP instructions are accessed through a DMA channel, as shown in Figure 1-3. Detailed I/O functions are accomplished by the IOP, and the resultant system data, stored in common main memory, are available to the CPU. With this arrangement, a minimum amount of CPU processor time is required to transfer systems data.

A bidirectional, 36-bit parallel I/O channel is used to transfer PCI, PCO, and data words between the CPU and IOP. When the IOP requires instruction, input data, or output data from main memory, it specifies the location in main memory over the DMA address lines. If more than one main memory access is pending in the IOP, a Burst mode of operation is requested through the DMA interface. The IOP may allow up to 64 data words to be transferred in the Burst mode. When the IOP operates in the Burst mode, the CPU cannot access main memory, and its processing will stop until the DMA channel is free. To prevent a DMA failure from locking the CPU out of main memory, a DMA timeout check is maintained by the CPU.

Box 43

80-78 SM

MITTE TO SO DED

OOFY PROVIDED BY

WICHITA STATE UNIVERSITY LIBRARIES

SPECIAL COLLECTIONS

WITHOUTWAITER STATES ALL SONEDOR

WITHOUTWAITER STATES ALL SONEDOR

PROVIDE COLLECTIONS

WITHOUTWAITER STATES ALL SONEDOR

PROVIDE COLLECTIONS

WITHOUT ALL SONEDOR

PROVIDE COLLECTIONS

WITHOUT ALL SONEDOR

PROVIDE COLLECTION

WITHOUT ALL SONEDOR

PROVIDE COLLECTION

PROVID

PROTECTED BY COPYRIGHT LAW

THIS MATERIAL MAY BE

THIS MATERIAL MAY BE

THUS MATERIAL LAW

Figure 1-3. Input/Output Processor Block Diagram

MS

A single processor element is contained in the IOP. Except for local storage the IOP hardware is time-shared and functionally provides the 24 data bus control elements (BCE) and the master sequence controller (MSC). The MSC and BCE execute programs located in main memory to perform the desired I/O operations. (MSC and BCE instruction sets are summarized in Section 2.) The MSC controls the BCE, which in turn controls one of the 24 data buses. Time sharing of the IOP processor element is defined by the slot timer as defined in Table 1-1. Slot timing sequence for one IOP processor element is BCE test, MSC, BCE 1, BCE 2, BCE 3 MSC . . . . BCE 22, BCE 23, BCE 24 and repeat. The BCE test slot initiates individual self-test programs, which verify that the processor and BCE data flow are operating correctly.

Table 1-1

IOP SLOT TIMING

| Design Restriction         | 1 MSC every 3 slots preceded by odd BCE slo |

|----------------------------|---------------------------------------------|

| • Slot Layout              | 24 BCE 1 BCE Test 8 MSC 33 Total            |

| • Slot Time                | 0.500 μs                                    |

| • Cycle Time               | $33 \times 0.500 = 16.5 \ \mu s$            |

| • MIA Word Transfer        | 28 bits at 1 MHz = 28 μs                    |

| • Interword Gap            | 5 μs                                        |

| MIA Slaved to 1-MHz Timing |                                             |

Figure 1-3, a simplified functional diagram of the IOP, shows the I/O data flow and major system elements. The primary functions of the major IOP elements are as follows:

- Control Monitor Interfaces with the CPU to provide power on/off, master reset functions, MIA enable/inhibit, decode the PCI and PCO commands, control the I/O channel interface, handle system discretes, IOP interrupt to CPU, and controls the initial program load (IPL) sequence.

- Channel Control Receives and transmits data over the main I/O channel

- <u>Local Store</u> Contains the general registers associated with the MSC and with each BCE

ATRO ONLY

Wichita State University Libraries, Special Collections and University Archives

- Microprogram Storage A ROS containing the microcoded instructions required to control the IOP data flow and the basic IOP operations

- Direct Memory Access Queue A first-in/first-out (FIFO) type memory device designed to handle instructions and data requests from main storage. In addition, the queue passes input data from an MIA to main storage. The queue will hold a maximum of 64 DMA requests and determines when the burst DMA mode is required.

- Data Flow Performs the arithmetic and logical functions, contains the necessary working registers to process and control data flow, and is timeshared to perform the MSC and each of the 24 BCE functions

- MIA Receives and transmits data over the 1-MHz, serial, digital data buses; converts serial to parallel data when receiving, and parallel to serial data when transmitting; and checks and maintains data word parity

- MIA Buffers Provides a one data word buffer per MIA channel to prevent data overrun when multiple data word input streams are being processed

- Discretes Receives and transmits discrete inputs and outputs, which are single control or status lines that interface with other orbiter subsystems

- Redundancy Management Hard Logic Performs RM functions for the IOP. and provides a means of indicating GPC failures and transmitting/receiving failure rate discretes to/from other GPCs in the system.

- Status Registers Provides a register for the MSC and each BCE for the Busy, Go, and Indicators.

The following example of IOP operation is a simplified description of how the IOP functions for an input data request from the CPU. This example uses MIA input processor BCE 1 with its transmitter and receiver enabled.

- CPU issues a PCO instruction to the program counter in the MSC local store. This instruction contains the starting address of the MSC program in main memory.

- CPU issues a PCO instruction to start the MSC. From this point, the remainder of the input sequence is performed by the IOP.

- MSC accesses main memory through the DMA queue to obtain its first and subsequent instructions.

- MSC program loads BCE 1's local store base register with the main memory address where the input data will be stored.

- MSC program loads BCE 1's local store program counter with a main memory address. This address is the BCE program starting address.

- MSC program starts BCE 1 and executes a repeat until instruction. 6.

- 7. BCE 1 accesses main memory through the DMA queue to obtain its first and subsequent instructions.

- 8. BCE 1 executes first instruction, which commands a system device to supply a data word over the MIA 1 data bus.

- 9. BCE 1's next instruction from main memory is to receive the data word. If more than one data word was required, the word count is part of the receive instruction.

- 10. MIA signals BCE 1 that data have been received.

- 11. BCE loads data in the main memory address specified in Step 4.

- 12. BCE 1's next instruction is to store its status register in main memory and enter the Wait state. Any error conditions are resolved by MSC and CPU programming.

- 13. MSC detects BCE Program completion and checks for errors. If no errors are present, the CPU is informed via MSC specified interrupt.

- 14. CPU accepts interrupt and processor input data.

Section 2

FUNCTIONAL IMPLEMENTATION

This section delineates the IOP system capabilities and describes the relationship between IOP system design and I/O programming. The topics covered in this section are: IOP program execution

- CPU control of the IOP by PCI/PCO commands

- MSC processor

- BCE processors

- IOP fault-detection capabilities

- Initial program loading.

### 2.1 INTRODUCTION

## 2.1.1 TIME SHARING

The functional components comprising the IOP are shown in Figure 2-1. Basic IOP operation centers around a fixed time sequence of operations determined by the slot timer, or "wheel," as shown in Figure 2-2. All BCEs and the MSC have dedicated general registers assigned in local store and share a common data flow. The MIA channels and the MSC are serviced in a very methodical fixed sequence using the local store. The IOP communicates with the CPU main memory (to fetch instructions and transfer data) in a completely asynchronous manner. The BCEs or MSC issue memory requests required from data flow during their slot times. These requests are stacked in DMA queue and are serviced in sequence by the channel control independent of the basic IOP processing operation.

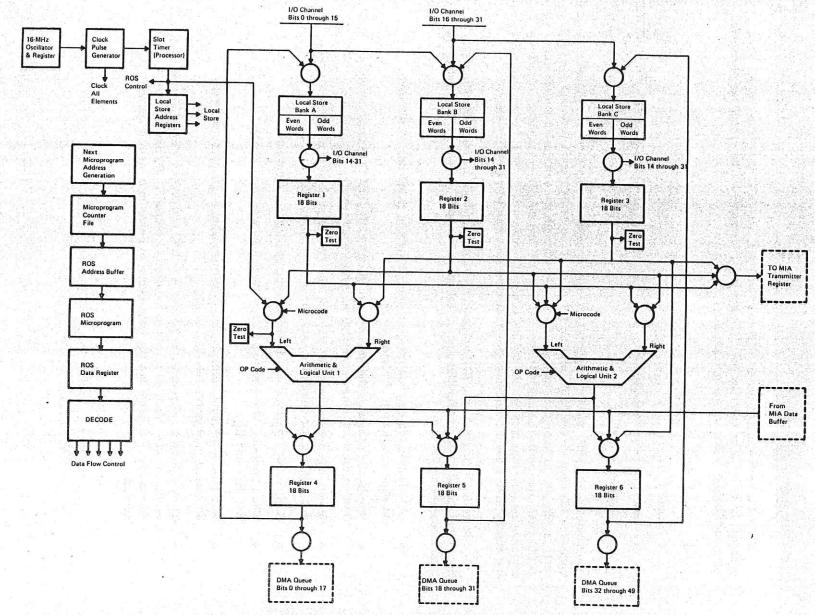

## 2.1.2 OPERATION OF PROCESSOR ELEMENTS

The major IOP processor elements, shown in Figure 2-3, are local store, microprogram, data flow, and timing. A standard phrase, "processor elements," will be used in reference to the actual IOP hardware elements to distinguish them from the general term, "processor," which refers to the MSC or a BCE program execution.

A processor's (MSC or BCE) operation is controlled by a series of instructions executed from main memory. A set of general registers in local store is maintained for each processor. A basic IOP instruction cycle consists of extracting an instruction from main memory, performing the instruction, and storing the results.

BRARIES

$S_{S}$

87

WICHITA STATE UNIVERSITY LIBRARIES

SPECIAL COLLECTIONS

WITHOUT WRITTEN PERSONS THIS WAS THE WAYNOT BE COPRED OR

REPRODUCED IN MINISTER AS THE WAYNOT BE COPRED OR

COBY PROVIDED BY

FOR RESEARCH USE ONLY

THIS MATERIAL MAY BE

PROTECTED BY COPYHIGHT LAW

TH 33 CH XOB 80-18 SW

Figure 2-1. IOP Functional Block Diagram

Figure 2-3. Microcycle Information Flow

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

MS

Wichita State University Libraries, Special Collections and University Archives

A program counter in the processor's local store keeps track of the main memory address from where the program is being executed. Any related main memory address for I/O data is maintained in the processor's local store. The instructions and I/O data transfers are accomplished using the main memory DMA channel.

Internal IOP processing is controlled by micros (micro instructions). The execution of a micro is similar to the execution of MSC/BCE instructions in that a microprogram counter keeps track of the micro address in the microprogram readonly storage (ROS). During the first phase of a MSC/BCE instruction, the operation code determines the ROS starting address to be loaded into the microprogram counter. The microprogram counter is then updated as the micros are executed to perform the desired MSC/BCE instruction. The microcode is fixed and cannot be altered by the programmer.

A hardware register resides on the micro decode page and is referred to as microprogram counter file. It contains one microprogram counter for each processor. Each micro requires one slot time to be executed and, to complete an MSC/BCE instruction, several micros will be executed, depending on the complexity of the MSC/BCE instruction. A simple MSC instruction, such as Store Accumulator, requires five micros. One of the more complex instructions, BCE Receive Data, requires 60 micros to define the required processing.

One micro instruction is executed every 0.500 \(mu\)s by the fixed timing arrangement of the slot timer. However, the timing wheel arrangement gives each BCE (or data bus channel) a dedicated timing slot once every cycle of the complete timing wheel. Thus, a dedicated BCE can be serviced and one micro associated with this dedicated BCE executed every 16.5  $\mu$ s. The timing wheel is arranged to devote every fourth slot to the MSC so that one MSC micro instruction can be executed every 2.0 us.

The information flow associated with the processor elements for one microcycle is illustrated in Figure 2-3. When a processor's slot time becomes current, the following microcyle occurs:

- A Read-Only Storage Address register (ROSAR) is loaded from the microprogram file, and a ROS memory access obtains the micro.

- The resulting micro controls the data and data flow paths for this cycle.

- The micro is executed. Each micro contains a processing step, and a test for a condition may be made.

- The microprogram counter is updated with the next sequential micro, or a branch can occur if a test condition is specified and met, or the same micro may be repeated waiting for a condition.

- The processing results can be stored in the processor's general registers (Local Store), written into the DMA queue, or sent to a MIA.

- This completes a slot time, and the next micro is executed.

MSC/BCE instructions are defined by a microprogram and are defined in the Microprogram Principles of Operation manual. MSC and BCE instruction lists can be found in Subsections 2.4 and 2.5, respectively.

## 2.1.3 EXAMPLE PROGRAM EXECUTION

The timing chart shown in Figure 2-4 is the sequence of micros needed to implement example MSC and BCE programs. The MSC program is listed in Table 2-1, and the BCE programs are listed in Table 2-2. This example shows the relationship between slot timing, I/O channel use, and MIA activity and briefly describes what occurs during a microcycle (one slot time). The MSC micro labeled RAW (repeat until all BCEs are waiting) is continually testing the status of BCE 3 and 15 in the example to determine when they have finished. The remarks column in Tables 2-1 and 2-2 briefly describe each instruction.

MSC programs are initiated by the CPU; the MSC starting sequence follows:

- PCI to test MSC status. If MSC is in the Wait state, proceed.

- PCO to load MSC program counter (100 in this example).

- PCO to place MSC in the Busy state.

# 2.2 PROGRAM CONTROL INPUTS AND OUTPUTS

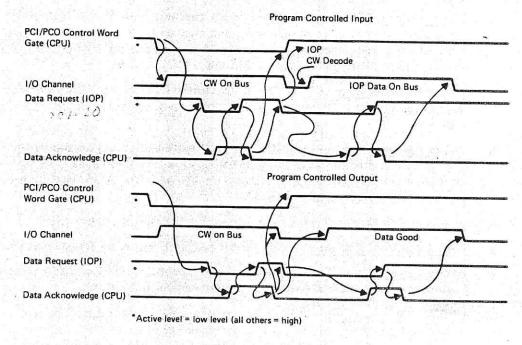

The CPU controls the IOP by PCI and PCO instructions issued over the I/O channel data bus. PCI and PCO instruction formats are summarized in Table 2-3. PCI/PCO transmissions involve a PCI/PCO command word immediately followed by a data word. For a PCO instruction, both a command word and a data word are issued by the CPU. For a PCI instruction, the CPU issues the command word, and the IOP responds with the data word. The CPU maintains a timeout check on IOP response to PCI/PCO commands. For timeout check details, see Subsection 3.4.

## 2.2.1 PCI/PCO COMMAND WORD FORMAT

The 5-bit Device-Select field must contain only the bit specified in the format description for the desired device selected. Additional bits will cause the PCI/PCO data word to be written to all the devices designated, with associated loss of IOP control. No attempts to use the hardware configuration should be made, since driving circuits are not sized to drive multiple loads and will not operate reliably.

Handshaking for a PCI/PCO is required for several operations to allow the device selected to complete an operation before the PCI/PCO command function is implemented. The handshaking operation prevents loss of control of the IOP software because of possible configuration changes during the PCI/PCO implementation.

CH XOB

80-78 SM

WICHITA STATE UMIVERSON TO SHED OF WAYNOT TO SHED OF WHICH THE STATE OF THE STATE O

FOR RESEARCH USE ONLY

PROTECTED BY COPYRIGHT LAW

CHILE IZ US CODE)

Figure 2-4. Typical IOP

Instruction Timing

| Main<br>Memory<br>Location | OP<br>Code | Operand            | Remarks  BCE 15 load base                                                                                                        |  |  |  |  |  |  |

|----------------------------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 100                        | LBB        | 15,300             |                                                                                                                                  |  |  |  |  |  |  |

| 102                        | LBB        | 3,200              | BCE 3 load base                                                                                                                  |  |  |  |  |  |  |

| 104                        | LBP        | 15,400             | Set BCE 15 to start at 400                                                                                                       |  |  |  |  |  |  |

| 106                        | LBP        | 3,500              | Set BCE 3 to start at 500                                                                                                        |  |  |  |  |  |  |

| 108                        | L          | 10                 | Get mask to start BCE 3 & 15 (from cell 108 + 10 = 118)  Start BCEs  Wait one wheel revolution to get BCES started (8 MSC slots) |  |  |  |  |  |  |

| 109                        | SIO        |                    |                                                                                                                                  |  |  |  |  |  |  |

| 110                        | DLY        | 8                  |                                                                                                                                  |  |  |  |  |  |  |

| 111                        | RAW        | 10                 | Now wait until BCEs are done                                                                                                     |  |  |  |  |  |  |

| 112                        | вс         | TIMEOUT            | If this instruction is executed, one of the BCEs did not turn off                                                                |  |  |  |  |  |  |

| 113                        | LAR        | 3                  | At this point, both BCEs have completed. Will now check if there were errors                                                     |  |  |  |  |  |  |

| 114                        | N          | 4                  | And error register (STAT1) with BCE mask. If result is nonzero, an error occurred.                                               |  |  |  |  |  |  |

| 115                        | BC         | NOT ZERO,<br>ERROR |                                                                                                                                  |  |  |  |  |  |  |

| 116                        | INT        |                    | Interrupt the GPC with an "All Operations<br>Completed Successfully" interrupt                                                   |  |  |  |  |  |  |

| 117                        | WAT        |                    | [마일 기계 전 역시 기계의 중요한 경기 등 경기 (2012년 )<br>1882년 - 1882년 - 1882년 기계                             |  |  |  |  |  |  |

| 118                        | 000100     | 000000000100       | 0 BCE mask. 1 in positions 3 & 15                                                                                                |  |  |  |  |  |  |

| Main<br>Memory<br>Location | OP<br>Code | Operand    | Remarks                                                                                                                      |  |  |  |  |  |

|----------------------------|------------|------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 400                        | MIN        | 2*, 2, CMD | Transmit command to subsystem device telling it to transmit 3 words. Receive data word count = 3, displacement from base = 2 |  |  |  |  |  |

| 404                        | WAT        |            | Enter Wait state                                                                                                             |  |  |  |  |  |

| BCE 3 - T                  | ransmit :  | 3 Words    |                                                                                                                              |  |  |  |  |  |

| 500                        | MOUT       | 2*, 0, CMD | Similar to receive program, transmit 3 words with displacement of data from base = 0                                         |  |  |  |  |  |

| 504                        | WAT        | <u> -</u>  | Enter Wait state                                                                                                             |  |  |  |  |  |

#### 2.2.2 PCO DATA WORDS

The following data present the information contained in the data words associated with each of the PCO instructions. These 32-bit data words may be correlated with the command words through the title and/or the octal or hexadecimal bit configuration. The positions within the data word are referenced by bit positions 0 through 31. Further details are available in the PCI/PCO Prinicipal of Operation. The PCO data word descriptions follow:

DMA Burst Inhibit 60002000000(8) C0040000(H) Enable 60202000000(8) C1040000(H)

The data word transferred with this command contains no information and is ignored.

WICHITA STATE LAWERS TY LIBRARIES

| 0,0                 | , ( | 1  | 02          | 0     | 3         | 04        | 0,                    | , 0                  | 6                 | 0,     | 0                               | , 0                   | 9                | 10   | 1     | 1   | 1 <sub>2</sub> 1 <sub>3</sub> 1 <sub>4</sub> 1 | 16       | 1, 31                                                                                                                                                                         |

|---------------------|-----|----|-------------|-------|-----------|-----------|-----------------------|----------------------|-------------------|--------|---------------------------------|-----------------------|------------------|------|-------|-----|------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | = 1 | cc | O C         | om    | ma<br>nar | nd        | 1                     | Co                   | mr                |        |                                 | D F                   |                  | 81.7 |       |     |                                                |          |                                                                                                                                                                               |

| 0<br>0<br>0<br>1    | 1   | 0  | 1<br>0<br>0 | 0 0 0 |           | ļ         |                       | RM<br>DF<br>LS<br>CC | $\left. \right\}$ |        |                                 | ce S                  |                  |      |       | əld |                                                | iak      |                                                                                                                                                                               |

|                     |     |    |             |       |           |           |                       |                      |                   |        |                                 | ith<br>Dev            |                  |      | • )   |     | Handshake Co                                   | ntrol    | Field                                                                                                                                                                         |

| 3                   |     |    | y k         |       |           |           | 0                     | 1                    | 2                 | 3      | 4                               | 5                     | 6                | 7    | 8     | 9   | Data Select                                    | Field    |                                                                                                                                                                               |

| 1                   | 1   | 0  | 0           | 0     | 0         | 0         | 0<br>1<br>1           | 0                    |                   | 1      | 1                               | 0                     | 1                | 0    | 0     | 0   | Load                                           | cc       | Disable Burst DMA Mode Enable Burst DMA Mode Enable Bad Parity MIA Add Disable Bad Parity Data In Enable Bad Parity Data In Disable Bad Parity Add Disable Bad Parity DMA Add |

| 1                   | 0   | 0  | 0           | 0     | 1         | 0         | 0                     | 0                    | 0                 | 0      |                                 | 0                     | 1                | 0    | 0     | 0   | Load                                           | <b>↓</b> | Disable Bad Parity Data In  Disable MIA Transmitter                                                                                                                           |

|                     |     |    |             |       |           | 1         | 1<br>0<br>1<br>0<br>1 |                      |                   | 1      | 1<br>1                          | 1                     | 1                |      |       |     |                                                |          | Enable MIA Transmitter Disable MIA Receiver Enable MIA Receiver Reset Discrete Output Set Discrete Output Halt Processor                                                      |

| 0 1                 |     | 0  | -           | 0     |           | ļ         |                       | 0 0 0                | 0                 | 0 0    |                                 | 0<br>1                | 1<br>0           | 0    | 0 0 0 | 0   | Read                                           |          | Enable Processor MIA Transmitter Enable Regi MIA Receiver Enable Register Discrete Output Register Halt Register (Stat 5)                                                     |

| 1                   |     | 0  | -           | 1     |           | 0         |                       | 0                    | -                 | 210.00 | 0                               | 0                     | 1                | -    | 0     |     | Load                                           | RM       | Master Reset Watchdog Timer                                                                                                                                                   |

|                     | 0   | 0  | Î           | 1     | 0         |           | 0                     | 0                    | 0                 | 0      | 0<br>1<br>0<br>1                | 0 0                   | 0<br>0<br>1<br>1 | 0    | 0     | 0   |                                                |          | Termination Control Latches<br>Voter Test Register<br>Watchdog Timer for Test<br>No Test All Interrupts                                                                       |

| 0                   | 0   | 0  |             | 1     | 0         |           | 0                     | 0                    | 0                 | 0      | 1<br>0<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>0 | 1                | 0    | 0     | 0   | Read                                           | RM       | Test All Interrupts Interrupt Register A Interrupt Register B Interrupt Register C Interrupt Register D Interrupt Register E Status Register Discrete Input A (High 32)       |

| 1                   | 0   | 0  | 1           | 0     | 0         | 1         | 0                     | 0                    | 0                 | 0      |                                 | 0                     | 0                | 0    | 0     | 0   | Load                                           | DF       | Discrete Input B (Low 8) Stat 1 (Reset)                                                                                                                                       |

| <b>♦</b> 0 <b>♦</b> | 0   | 0  | 1           | 0     | 0         | <b>♦०</b> | 0                     | 0                    | 0                 | 0      | 0                               | 0                     | 1<br>0<br>1      | 0    | 0     | 0   | ₩<br>Read<br>₩                                 | DF       | Stat 4 (Set MSC to Busy)<br>Stat 1<br>Stat 4                                                                                                                                  |

| 1 0                 |     |    |             | 0     |           | 1         | 0                     | 0                    | 0 0 :             | 0      |                                 |                       |                  |      |       |     | Load<br>Read<br>MSC Region<br>BCE 1            | LS<br>LS |                                                                                                                                                                               |

|                     |     |    |             |       |           |           | 1<br>1                | 1                    | 0                 | 0      | 0<br>1                          |                       | 0 1 0            |      |       | 180 | BCE 24 Proc 25 (Self Bank A Bank B Bank C      | f–Test   |                                                                                                                                                                               |

|                     |     |    | 1           |       |           |           | A .                   |                      |                   |        |                                 |                       |                  | 0    | 0     | 0   | Location 0                                     |          |                                                                                                                                                                               |

Wichita State University Libraries, Special Collections and University Archives Dr. James E. Tomayko Collection of NASA Documents Box 42

MIA Transmitter Disable 41002000000(8) 84040000(H) Enable 41202000000(8) 85040000(H)

Positions 0, 28, 29, 30, 31 = not used and should be "0"s.

Positions 1 through 27 = channels 1 through 27 of MIA transmitters, respectively.

If "0" = no change of status.

If "I" = Enable or Disable, depending on command word.

MIA Receiver Disable 41004000000(8) 84080000(H) Enable 41204000000(8) 85090000(H)

Positions 0, 28, 29, 30, 31 = not used and should be "0"s.

Positions 1 through 27 = channel 1 through 27 of MIA transmitters, respectively.

If "0" = no change of status.

If "1" = Enable or Disable, depending on command word.

Discrete Output Reset 41010000000(8) 84100000(H) Set 85100000(H) 41210000000(8)

Positions 1 through 31 = Discrete Outputs (DO) 1 through 31, respectively. If "0" = no change of status.

If "1" = set or reset the DO, depending on command word.

Processor 41020000000(8) Halt 8,4200000(H) Enable 41220000000(8) 85200000(H)

Positions 0, 28, 29, 30, 31 = not used and should be "0"s.

Position 0 = MSC.

Position 1 through 27 = BCE processors 1 through 27, respectively.

If "0" = no change of status.

If "1" = Processor Halt or Enable, depending on command word.

Reset 41040000000(8) The data word transferred with this command word is ignored.

Wichita State University Libraries, Special Collections and University Archives

```

Go/No-Go

Load

Timer

42002000000(8)

88040000(H)

Go/No-Go

Timer Test 42002200000(8)

88048000(H)

```

Positions 0 through 19 = not used and should be "0"s.

Positions 20 through 31 = weighted binary data representing the value to be loaded.

Position 20 = MSB.

Position 31 = LSB = 0.768 ms.

Termination Latch Control 42004000000(8) 88080000(H)

Positions 0 through 29 = not used and should be "0"s.

Position 30 = Timeout Termination latch.

Position 31 = Voter Termination Latch.

If "0" = reset.

If "1" = set.

Load Test Register 42010000000(8) 88100000(H)

Positions 0 through 26 = not used and should be "0"s.

Position 27 = voter test control.

If "0" = permit normal RM operation.

If "1" = inhibit normal RM operation to perform test.

Positions 28 through 31 = voter inputs 1 through 4 for test inputs.

If "0" = simulation of nonfail case.

If "1" = simulation of failed input.

Reset Program Exception 44400000000(8) 92000000(H)

Positions 28, 29, 30, 31 = not used and should be "0"s.

Position 0 = MSC.

Positions 1 through 27 = BCE numbers 1 through 27, respectively.

If "0" = do not alter Go or No-Go status as presented.

If "1" = reset the position to a normal or Go status.

Load MSC Busy

44402000000(8)

92020000(H)

The data word associated with the transfer of this command word is not used. The command word will force the MSC to the Busy state.

Load Local Store (Command word specifies address.)

Positions 0 through 13 = not used and should be "0"s.

Positions 14 through 31 = positions 0 through 17 of the specified Local Store word.

#### 2.2.3 PCI DATA WORDS

The PCI data word descriptions follow:

MIA Transmitter Status

0100000000(8)

04000000(H)

Receiver Status

01002000000(8)

04020000(H)

Positions 0 through 26 = MIA channels 1 through 27, respectively.

If "0" = transmitter (or receiver) disabled.

If "1" = transmitter (or receiver) enabled.

Positions 27 through 31 = not used and should be "0"s.

Read Discrete Outputs

01004000000(8)

04080000(H)

Positions 0 through 31 = DOs 1 through 32, respectively.

If "0" = DO is off.

If "1" = DO is on.

Processor Halt Status

0100600000(8)

040C0000(H)

Position 0 = MSC.

Positions 1 through 27 = BCEs 1 through 27, respectively.

If "0" = processor is disabled.

If "1" = processor is enabled.

Positions 28 through 31 = not used and should be "0"s.

Read Interrupt Register 1

02000000000(8)

08000000(H)

Position 0 = Watchdog timer.

If "0" = timer has not timed out.

If "1" = timer has timed out.

Position 1 = IOP Fail latch.

If "0" = not failed.

If "1" = IOP failed.

```

Position 2 = CM IDCE.

```

If "0" = control monitor logic is operating.

If "1" = control monitor is in Idle mode and is available.

Position 3 = ROS parity error.

If "0" = no error.

If "1" = parity error for IOP ROS has been detected.

Position 4 = IOP fault.

If "0" = no fault detected.

If "1" = IOP oscillator has stopped.

Position 5 = spare.

Positions 6 through 31 = not used and should be "0"s.

# Interrupt Register 2

02002000000(8)

08040000(H)

Position 0 = PCI/PCO parity error.

If ''0'' = no error.

on intertoc c If "1" = parity error detected during PCI/PCO transfer on one of the words data or command.

Position 1 = DMA instruction parity error.

If "0" = no errors. If "1" = parity error on instruction word during DMA operation.

Position 2 = DMA data parity error.

If "0" = no errors. This can be a thing If "1" = parity error detected during data word transfer during DMA operation.

Position 3 = Burst DMA error.

If "0" = no errors.

If "1" = more than 63 (10) words have been transferred in sequence.

Position 4 = DMA Queue Full indicator.

Position 5 = spares.

Positions 6 through 31 = not used and should be "0"s.

# Interrupt Register 3

6H)

02004000000(8)

08080000(H)

Positions 0 through 11 = MSC program interrupts 1 through 12, respectively.

If ''0'' = no interrupt.

If "1" = interrupt received.

Positions 12 through 31 = not used and should be "0"s.

Interrupt Register 4

02010000000(8)

08100000(H)

Positions 0 through 3 = spares.

Positions 4 through 31 are not used and should be "0"s.

• / Interrupt Register E

02010000000(8)

08100000(H)

Positions 0 through 3 = spares.

Positions 4 through 31 = not used and should be "0"s.

• RM Status Register

02010000000(8)

08100000(H)

Position 0 = Fail or Timeout latch.

If "0" = no failure.

If "1" = IOP failure or simulated failure if in Self-Test mode.

Position 1 = PCO Inhibit Fail Vote inputs for test.

If "9" = RM voter configured for normal operations.

If "I" = RM voter configured for self-test; normal operations inhibited.

Position 2 = MSC inhibit Fail Vote outputs for test.

If "0" = normal operation.

If "I" = RM Vote output inhibit for self-testing.

Positions 3 through 6 = Failure Vote inputs 1 through 4.

If "0" = no failures.

If "1" = Failure Votes being received from other IOPs.

Positions 7 through 10 = Failure Vote outputs 1 through 4.

If "0" = no failure detected (good vote).

If "1" = Failure Vote to other IOPs.

Positions 11 through 14 = Test Failure Vote inputs 1 through 4.

If "0" = no failures simulated.

If "1" = failures simulated for self-testing.

Position 15 = Voter Fail latch.

If "0" = no failure indicated.

If "1" = failure indicated for Normal or Test modes.

Position 16 = Timeout latch.

If "0" = no Go/No-Go timeout indicated.

If "I" = Go/No-Go time out reached.

Position 17 = Voter Termination Control latch.

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

```

Position 18 = Timer Termination Control latch.

```

If "0" = latch is reset indicating Go.

If "1" = latch is set indicating No-Go.

Position 19 = IOP transmission termination.

If "0" = normal operation, Go.

If "1" = terminate operations, No-Go.

Positions 20 through 31 = Go/No-Go timer data value in weighted binary.