R-276 DESIGN PRINCIPLES FOR A GENERAL CONTROL COMPUTER

by

R. Alonso J. H. Laning, Jr.

April 1960

INSTRUMENTATION LABORATORY MASSACHUSETTS INSTITUTE OF TECHNOLOGY CAMBRIDGE 39, MASSACHUSETTS

Approved: R. B. Woodbury

Associate Director

## ACKNOWLEDGMENT

Part of the work presented in this report was done by Dr. Richard H. Battin and Mr Robert E. Oleksiak. Dr , Battin took part in the discussions on order codes, and authored the final refined version of the "representative" order code. Mr, Oleksiak had a major part in the electrical design of both the fixed and erasable memory systems constructed and operated to date, designed the specialized and necessary Z and P registers, and contributed to the invention of the priority circuit.

This report was prepared under Project DSR 52-156 sponsored by the Ballistic Missile Division of the Air Research and Development Command through USAF Contract AF 04(647)-303 and Project DSR 53-138, Division of Sponsored Research, Massachusetts Institute of Technology, sponsored by the Bureau of Ordnance, Department of the Navy, under Contract NOrd 17366.

This document has been reprinted January , 1962 under National Space & Aeronautics Authority Contract NAS 9-153.

|    | RECEIVED |      |        |

|----|----------|------|--------|

|    | JUL      | 26   | 1972   |

| М, | I. T     | LIBF | RARIES |

### ABSTRACT

A set of techniques is described which permits the design of computers particularly well suited for outer space and other airborne control applications. These techniques are unified by reference to a representative computer.

Some of the properties of the computer are: variable speed, power consumption proportional to speed, relatively few transistors, relatively large storage for program and constants, and parallel transfer of words. Certain features of the input system permit automatic incrementing of counters and automatic interruption of normal computer processes upon receipt of inputs.

The program and constants are stored in a wired-in form of memory which permits unusually high bit densities.

# TABLEOFCONTENTS

|               | Page                                          |

|---------------|-----------------------------------------------|

| Introduction. |                                               |

| Chapter I     | General Organization of Storage               |

| А.            | The <i>Core</i> Rope (Wired-in Memory) . 11   |

| В             | Erasable Storage Registers ,                  |

| C.            | The Erasable Storage System , 11, 23          |

| D.            | The Complete Memory System , 126              |

| Chapter II    | Execution of Computer Instructions            |

| А,            | Central Registers and Overall                 |

|               | Organization                                  |

| B.            | The Sequence Generator , , 39                 |

| C.            | Representative Order Code System . 43         |

| D.            | Addition and Multiplication                   |

| Chapter III   | Input- Output Systems , , , , , , , , , , 67  |

| А.            | Introduction , , , , 67                       |

| B.            | The Priority Circuit , , , , , , , 68         |

| C.            | The Automatic Interrupt , , , , , , 75        |

| D.            | State Inputs, 76                              |

| E.            | Counter Inputs , , , , , , , , , , , , , , 80 |

| F.            | Output Devices 88                             |

| Chapter IV    | General Remarks                               |

| А             | Sizes and Weights 97                          |

| B.            | Reliability Problems.                         |

| С.            | Practical Experience to Date 1, , 103         |

| D.            | Power and Speed, , , , , , , 104              |

.

# LIST OF ILLUSTRATIONS

| Figure | Page                                                                                     |

|--------|------------------------------------------------------------------------------------------|

| 1-1    | 256 word core rope, . , , , , , , , . , , . , , 12                                       |

| 1-2    | Selection of a core in a core rope . , , , , $14$                                        |

| 1-3    | Timing of inhibiting, set and clear currents 15                                          |

| 1 - 4  | Sensing wires on a core rope , , , 16                                                    |

| l-5    | Symbolic erasable register , . , . , . , . , ,                                           |

| 1-6    | Erasable register , ,                                                                    |

| l-7    | Erasable storage system , , 22                                                           |

| l-8    | System of ten erasable storage registers . , , $24$                                      |

| 1-9    | Erasable storage selection system , ,                                                    |

| l-10   | Complete memory system . , , , , , 28                                                    |

| 2-l    | Over-all organization of the representative computer ,                                   |

| 2-2    | Sequence generator , , , , , , . , . , . ,                                               |

| 2-3    | Control pulse generation by sequence generator, 40                                       |

| 2-4    | Representative central register system , , , , , 44                                      |

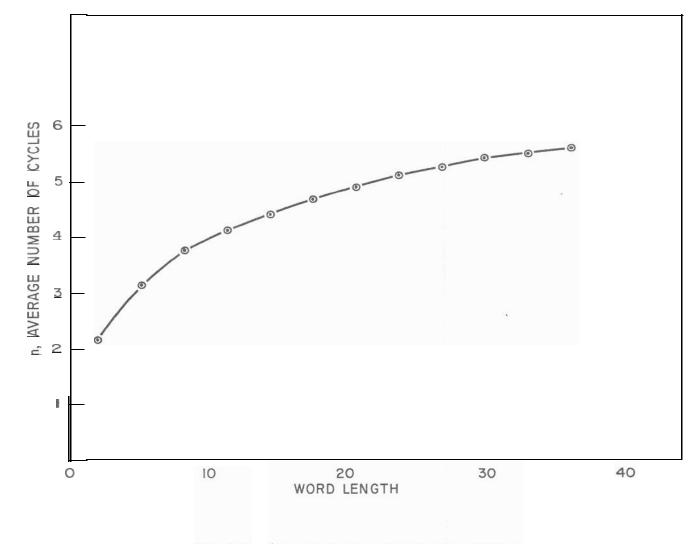

| 2-5    | Average number of cycles for addition.                                                   |

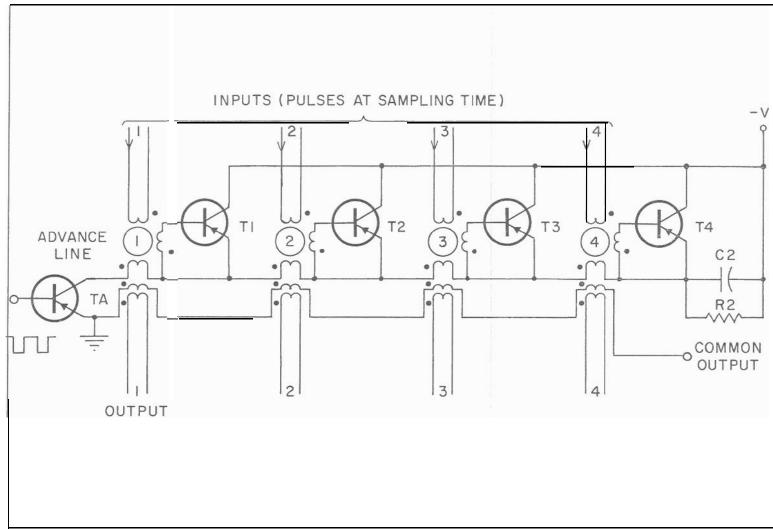

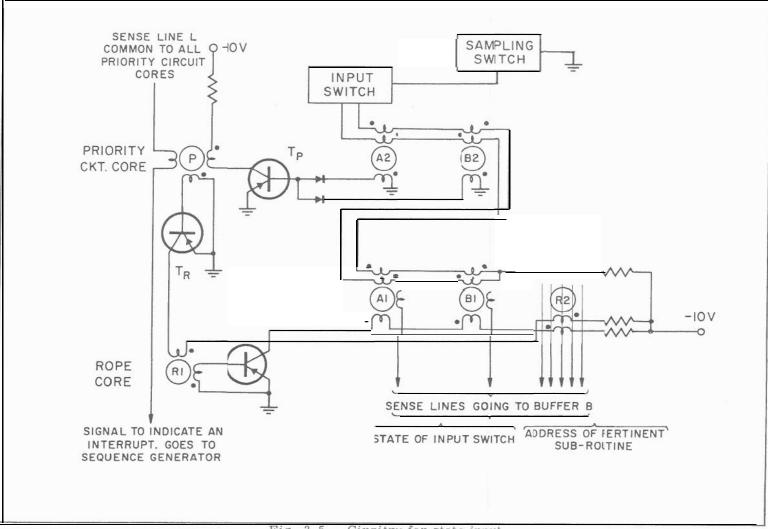

| 3-l    | Priority circuit . ,                                                                     |

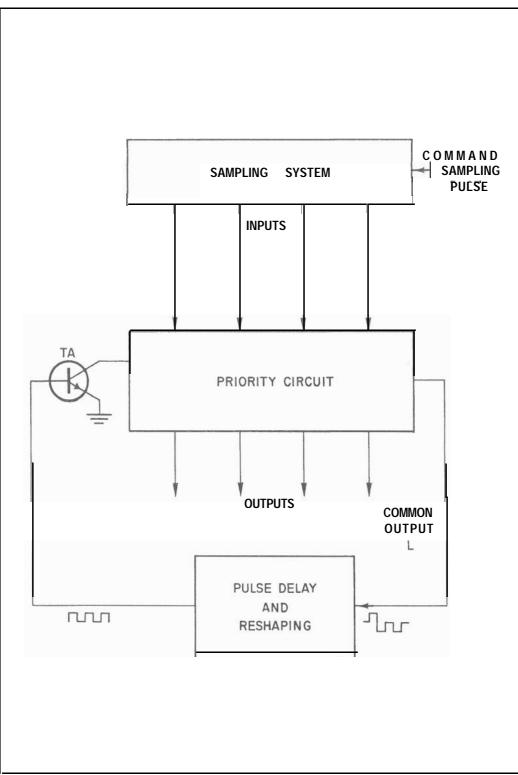

| 3-2    | Priority circuit system , , , , , ,                                                      |

| 3-3    | Input circuits for priority circuit system , 72                                          |

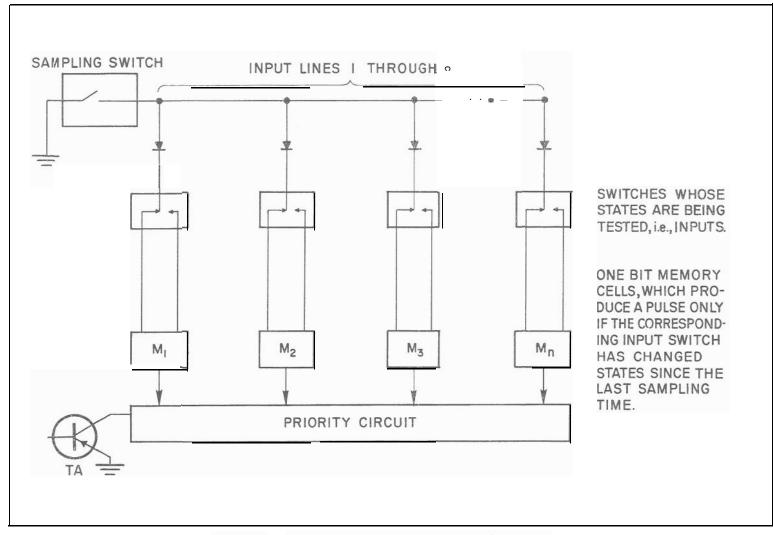

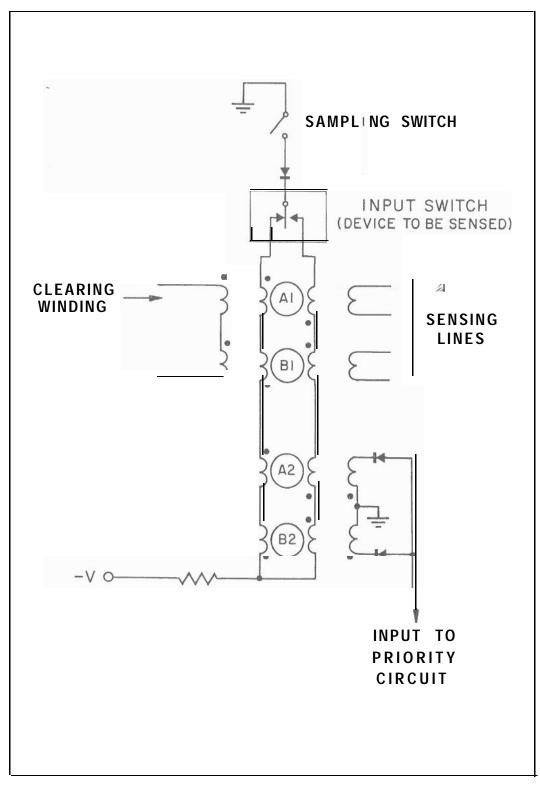

| 3-4    | Unit M for input to priority circuit , ,                                                 |

| 3-5    | Circuitry for state input , , ,                                                          |

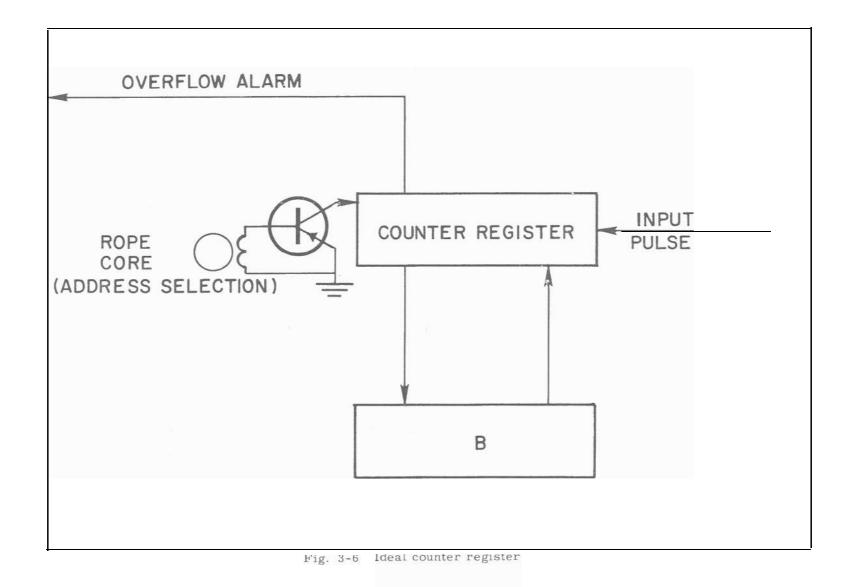

| 3-6    | Ideal counter register , , , , ,                                                         |

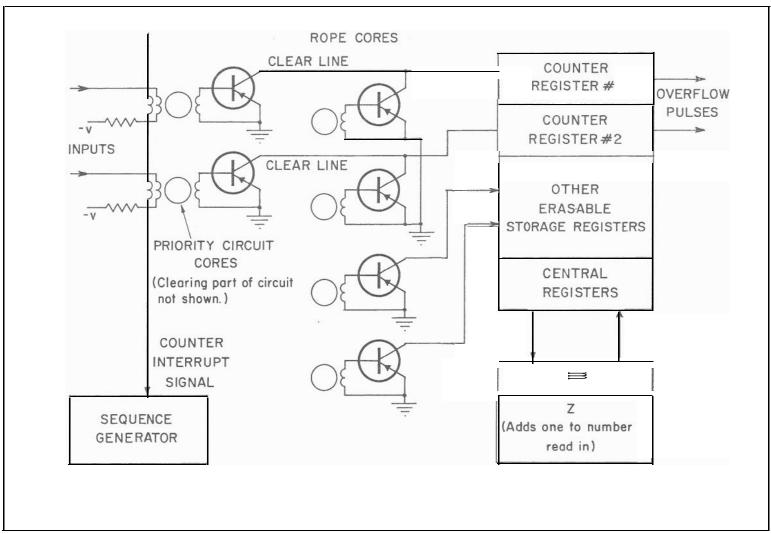

| 3-7    | System for counter inputs                                                                |

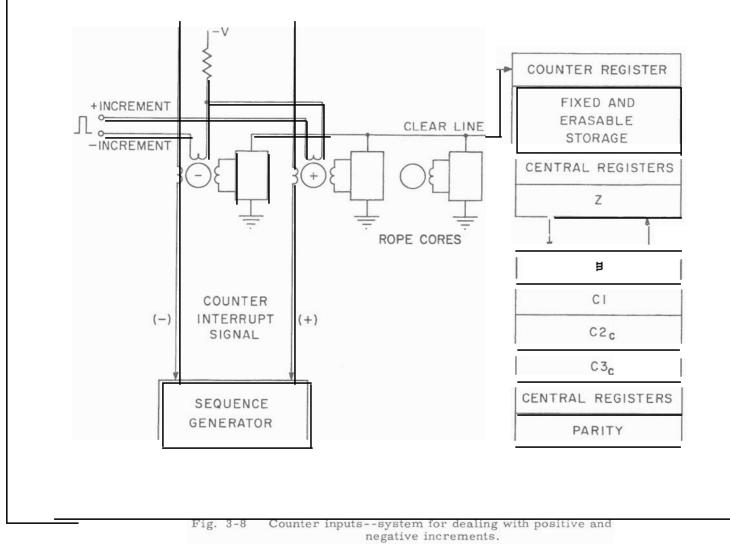

| 3-8    | Counter inputs system for dealing with positive<br>and negative increments . , , , , . , |

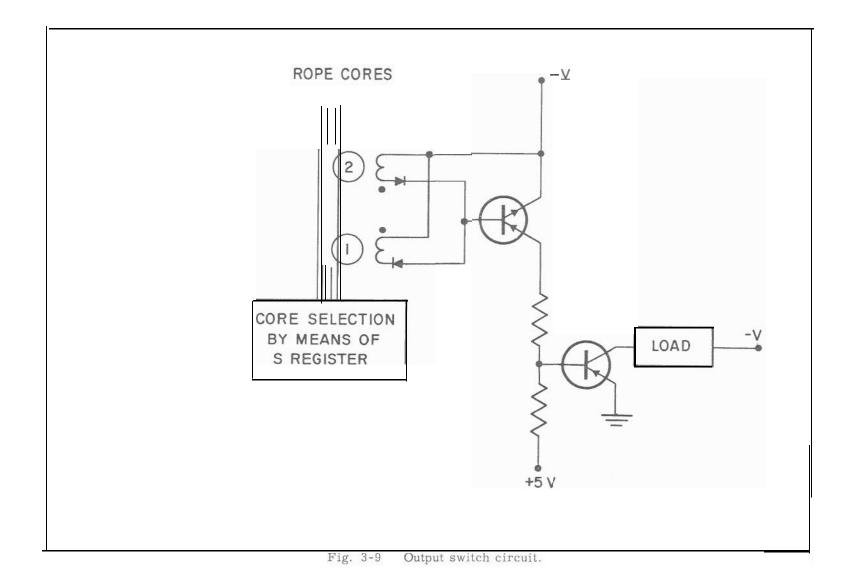

| 3-9    | Output switch circuit                                                                    |

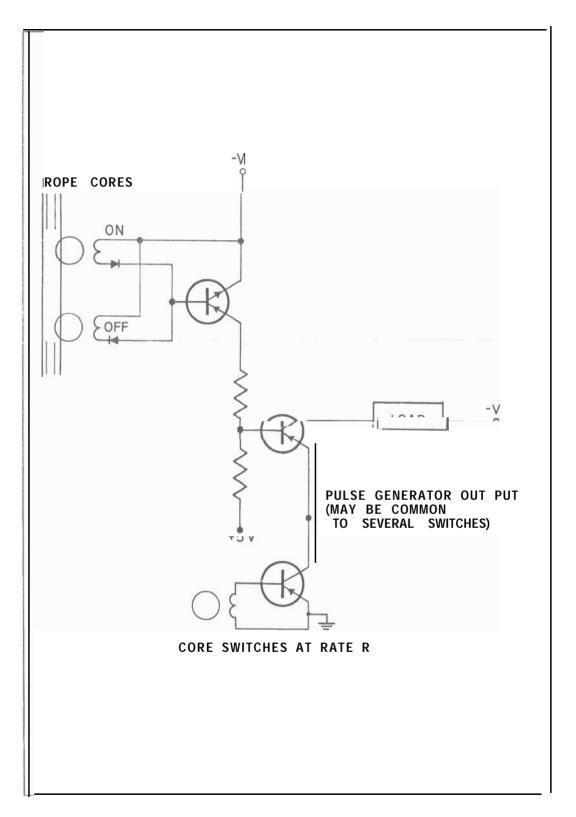

| 3-10   | Gating of a pulse generator by an output switch . , 90                                   |

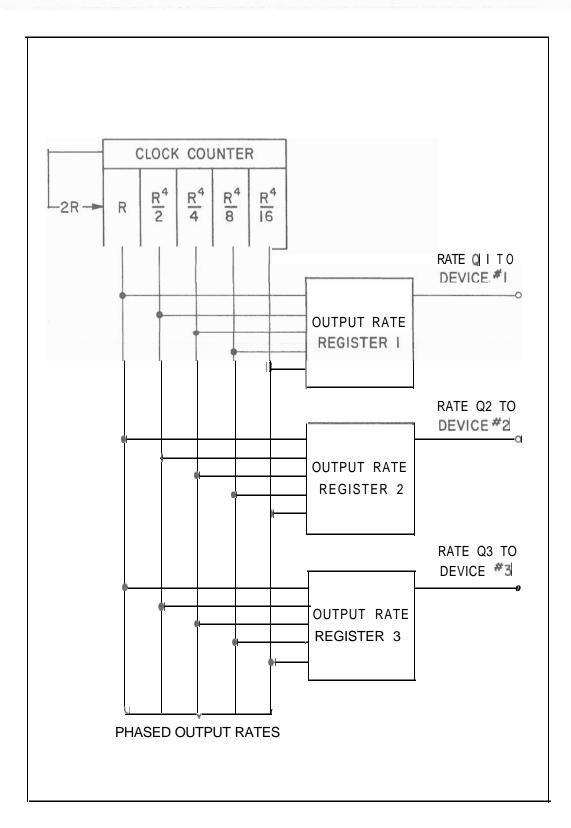

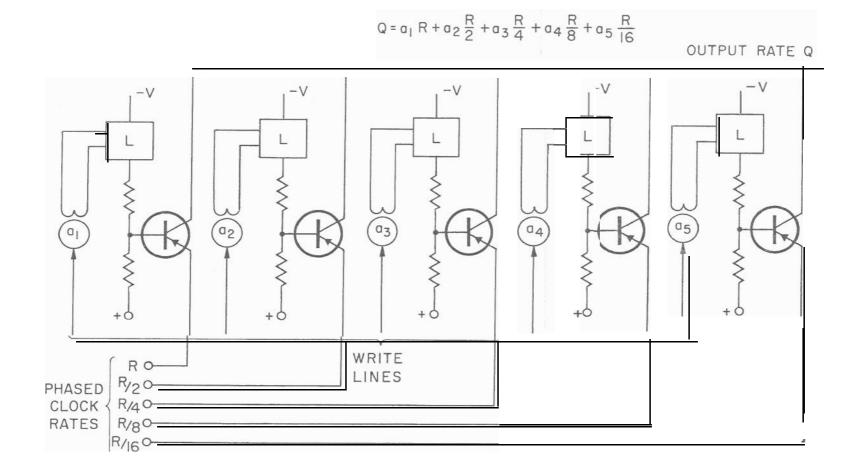

| 3-11   | Generator of several pulse rates, ,                                                      |

| Figure |                                        | Page |

|--------|----------------------------------------|------|

| 3-12   | Details of an output rate register     | 93   |

| 3-13   | Pulse rate generation and examples     | 95   |

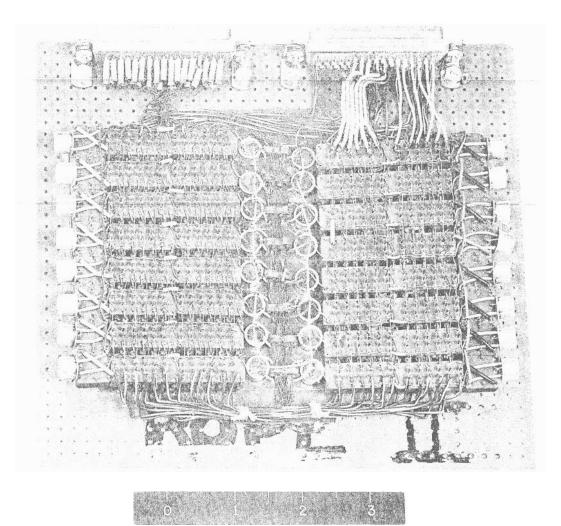

| 4-l    | Sixteen word erasable storage system   | 99   |

| 4-2    | Physical characteristics of components | 101  |

## DESIGN PRINCIPLES FOR A GENERAL CONTROL COMPUTER

## INTRODUCTION

The subject of this report is a medium-speed, general – purpose digital computer designed to serve as a controlling element for a deep space probe or other complex airborne system; it is a continuation of the work presented in Report R-235:". Major features of the design are the small size and weight of this computer, its rugged construction, low power consumption, and a combination of circuits and logical organization which allows many sophisticated operations to be accomplished quite simply. All of this can be achieved by circuits composed of magnetic cores, diodes, and transistors, with the latter being few in number relative to comparable existing computers.

The computer is not presented in the context of a specific application, but rather as a collection of useful techniques and approaches, especially with regard to inputs and outputs. To assist the reader in visualizing reasonable areas of potential uses, sizes and speeds for a representative machine are nonetheless discussed These would vary with the control application, but are meaningful in indicating the kinds of problems the computer can best solve. The remainder of this Introduction summarizes the principal characteristics of this machine.

Chapter 10, Vol III, A Recoverable Interplanetary Space Probe MIT Instrumentation Laboratory Report R-235, July 1959.

Computer memory consists of a wired-in section for program and constants plus a smaller volatile memory for variable items. Both are random access in nature, with all transfers occurring in parallel. The wired-in memory provides for storage of information at a density between ten and one hundred times that achieved with the volatile type of memory (see Chap. 4, Section A of this report). As a result, the proposed computer is well suited for the solution of a large class of airborne and spaceborne control problems which require the versatility afforded by long and intricate logical or arithmetic programs, or require the storage of many constants, but which use relatively few variables. The representative machine possesses about 4000 words of wired-in storage and 128 words of volatile storage, all words being of the order of 23 bits in length, plus a parity bit. Estimates of a representative computer's size and weight are 0. 37 ft<sup>3</sup> and 20 lb.

Various input-handling techniques are presented which assist efficient computer utilization. The input lines are not scanned; when an input line becomes active, the computer interrupts its present activity to tend to that input, returning to its former task after the input has been dealt with. This mode of operation is particularly advantageous in the case in which there are many slowly varying inputs. (A scanning system requires that computer speed be increased with an increase in the number of input lines. | However, the computer is also well equipped for the counting of rapid trains of input pulses; each such pulse costs only two clock cycles  $\stackrel{\scriptscriptstyle{(4)}}{\longrightarrow}$  on the part of the computer for its These techniques employ the efficient time Sharing processing. of a small amount of common equipment and thereby permit a relatively complex control situation to be handled by a small computer.

<sup>&</sup>lt;sup>TA</sup> clock cycle is composed of two clock pulses,  $\alpha$  and  $\beta$ .

The order code for the representative computer is of the single address type and is one in which 3 to 5 clock cycles are required for the operations involving transfer of information from one point to another or for logical operations. Addition and multiplication, however, require an average of about 27 and 750 clock cycles respectively; in fact, multiplication| is accomplished by a subroutine. At a nominal 100 KC clock rate, multiplication requires 7. 5 ms, addition 0. 27 ms, and many other operations only 0. 04 ms1

Computer speed is variable, and can be controlled both by external events and by the computer program itself. When functioning at full speed, the computer will consume power on the order of 20 watts, exclusive of input and output equipment. The electrical design, however, permits the computer to function at any clock cycle rate from a nominal maximum of 100 KC to zero cps, with a power consumption proportional to speed. Hence it is possible to take advantage of long periods during which the computer need not operate very rapidly, and save While in this semi-dormant status, the ability of the power. computer to process input information instantly on demand is in no way impaired; thus the effective operation speed can be exactly that dictated by the input requirement. This property is clearly useful in the case of a deep space probe.

The computer is expected to be long-lived, in the sense of no catastrophic failures. This is because the number of active components is low (of the order of 1500 transistors), and the power dissipated in each of these is well within the components' ratings. The possible sophistication and length of the computer program can be used for checking computations and to provide alternative actions in the case of failures of parts of the controlled system. Thus the survival capabilities of the controlled system could be increased significantly, especially in the case of temporary malfunctions. The remaining chapters in this report discuss in some detail the logic and circuits for this computer. An effort is made to lead the reader progressively from the simple and separate elements of which the machine is composed, taward the complexities of the overall logical organization; the report is therefore best read in sequence. Many details are passed over in the process; the first rudimentary version of the machine is just now being assembled, and many changes are certain to be made. The overall organization and logic, however, appear to be sufficiently unique and promising in their possible applications to justify a report at this time.

## CHAPTER 1

## GENERAL ORGANIZATION OF STORAGE

### A. The Core Rope (Wired-In Memory)

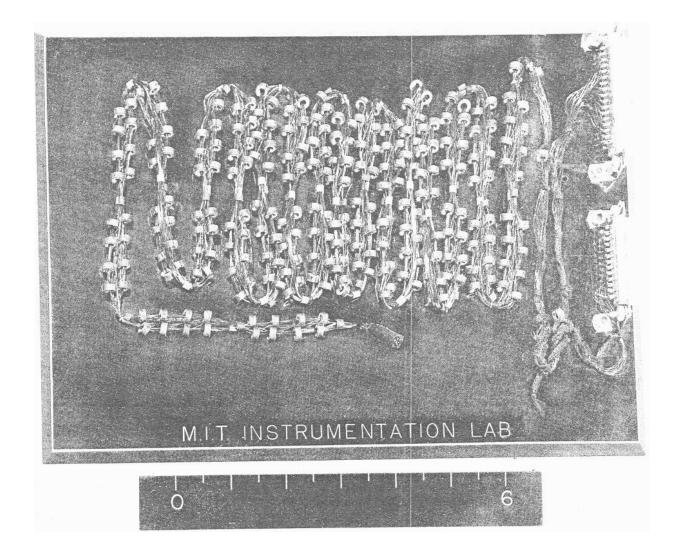

The term "core rope" is used to denote the device used as the wired-in or "fixed" storage for this computer and as the selection switch controlling operation of the volatile or "erasable" storage. The term is derived from the physical appearance of the array of cores and wiring; a rope of 256 cores is shown in Fig. 1-11 By means of the rope wiring pattern, an arbitary binary address can be translated into the switching of a single corresponding rope core, which may in turn cause other actions such as read-out of an associated erasable (volatile) storage register. Additional sensing-wiring through the core permits the read-out of a wired-in binary number upon resetting the core, providing a medium for fixed storage.

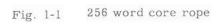

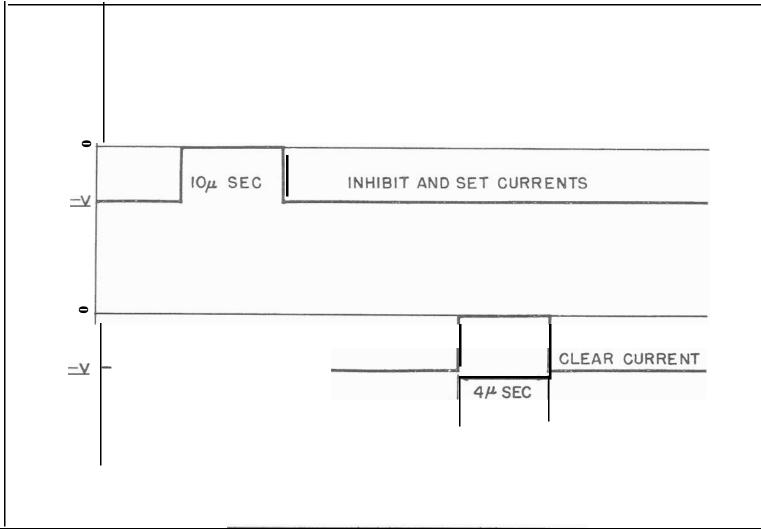

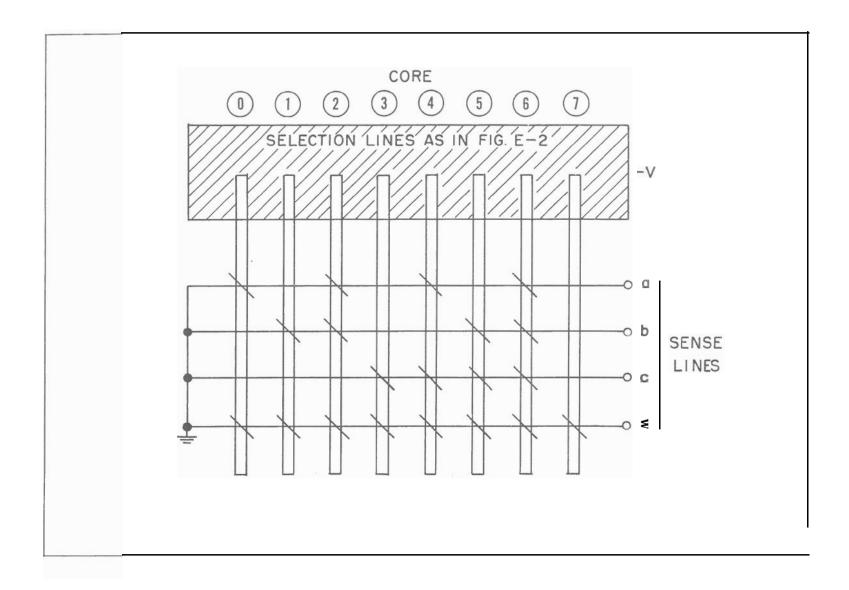

The core rope, which was invented by Olsen of Lincoln Laboratory, and which is also known as the Diamond Switch, the Rajchman Selection Switch, and the Linear Selection Switch, makes use of cores as saturable pulse transformers. The cores are small permalloy ribbon cores, with a fairly square hysteresis loop. A small 8-core rope is shown in schematic form in Fig. 14 2. There are two pulse generators, one providing a ground at point (1) at TIME 1, and the other providing a ground at point (2) The duration and timing of these grounds are shown at TIME 2. in Fig. 1-3. The lines marked A,  $\overline{A}$ , B,  $\overline{B}$ , C, and C are called Inhibitors. The slanted line at the intersection of a core and a wire shows that the wire in question threads that core. The

direction of the slant relative to the current in the wire indicates the direction of threading.

All eight cores shown in Fig. 1-2 are initially in state ZERO. The Set line puts a current through all the cores in a sense that drives all cores toward state ONE. A current-carrying Inhibit or, on the other hand, prevents those cores which it threads from switching from ZERO to ONE. If it does not carry current, i. e. if it is not connected to point (1) by virtue of the position of the appropriate switch", then it has no effect on any core. Each pair of Inhibitors in Fig. 1-2 may be regarded as one binary digit position in a 3-digit address; one and only one Inhibitor from a pair is active at any time. It is easy to verify from the wiring pattern shown that each of the eight possible combinations of inhibitors connected to the pulse source corresponds to a single core being switched from ZERO to ONE by a current through the Set line, all other cores being inhibited by at least one inhibiting current.

The Clear line, which carries current at TIME 2, tends to drive all the cores toward state ZERO. However, there is oulyone core to switch, the core that is in state ONE at that time.

Thus far we have considered how a core is selected, but not how information is stored in that core. This is accomplished by means of an additional set of windings on the cores of the **rope**, as shown in Fig. 1-4. As before, a threaded core is shown by means of a slanted line at the intersection of core and wire. For example, core number (7) is threaded only by Sense line d; core (6) is threaded by all Sense lines. Upon selecting and switching a core (say (4)), all Sense lines which thread it will

<sup>&</sup>lt;sup>°</sup>Symbolized in Fig. l-2 as a relay contact, but electronic in practice.

Fig. 1-2 of a core in a core rope.

Fig. 1-3 Timing of inhibiting, set and clear currents.

have an emf induced on them, and the remaining lines will not. Thus a pattern of ONE's and ZERO's in the resultant word can be specified by prescribing which lines do and do not thread the corresponding core.

In practice, the signals are observed at Clear time rather than at Set time, because the interference or noise induced by the currents in the many Inhibit lines masks the signals induced by the Set current. Nevertheless, the engineering problems of eliminating or minimizing the various sources of interference of this nature have provided one of the main obstacles that was necessary to overcome in the course of developing this computer. The situation is felt to be well under control for the memory sizes presently considered, but might constitute a problem in extending this technique to memories of significantly larger size.

Clearly, the size of the word stored per core is arbitrary, depending merely on the number of Sense lines. As a last remark, the whole core rope system may be thought of as a coding switch, with a correspondence between inputs (inhibiting currents) and outputs (emf's on Sense lines), rather than as a "memory" in the traditional computer sense. It is noted that the above method for selecting a core and making it switch is very economical, for it requires the logical minimum of 2N Inhibitors for selecting one out of  $2^{N}$  cores.

### B. Erasable Storage Registers

Each core of the rope just described may be regarded as a register, since it stores a word. However, that word cannot be erased and a new one put in its place because of the wired – in nature of the information, and hence these are known as "fixed registers". In order to store variables, it is necessary to have registers such that their contents may be changed; these will be called "erasable registers". The two kinds of memories will

Fig. 1-5 Symbolic erasable register.

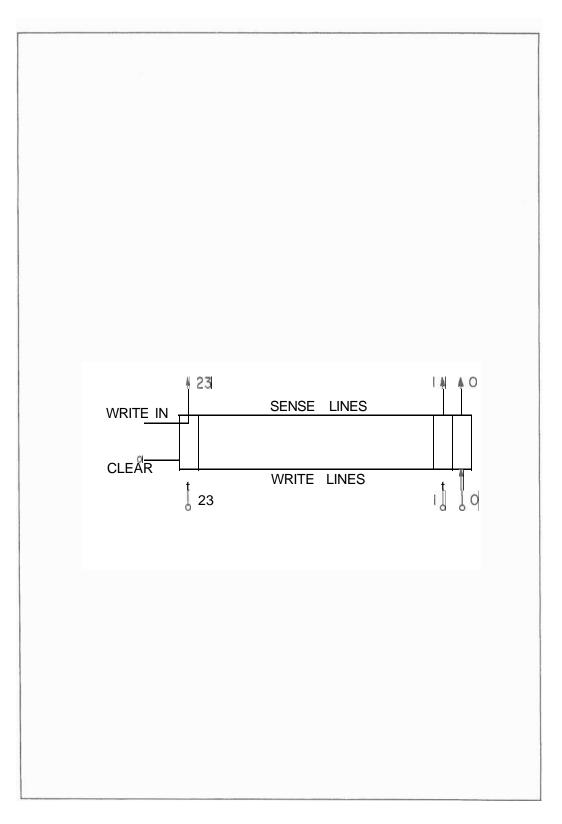

be referred to as the F memory and the E memory, or often simply as F or E. An operational description of an erasable register is shown in Fig. 1-5. Transfer of a word into and out of a register is done in parallel, i. e. , at one pulse time. In an erasable register, a separate core is required for each binary digit to be stored, in contrast to the fixed register (rope core) which stores many digits per core.

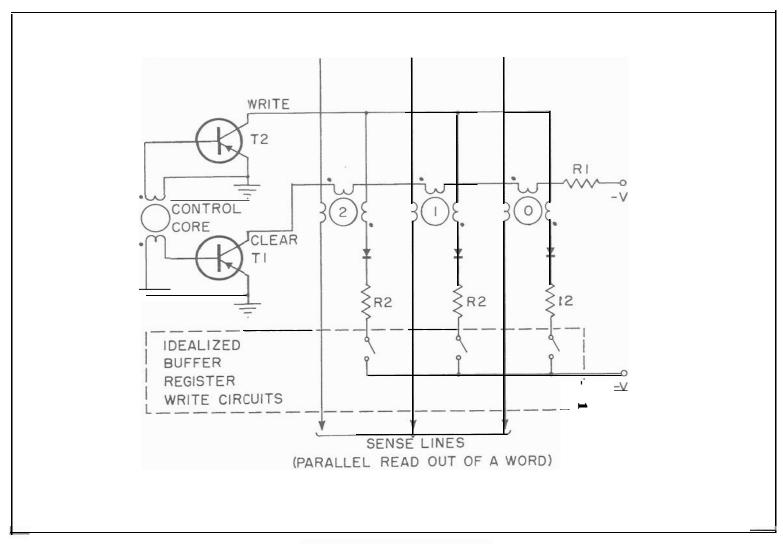

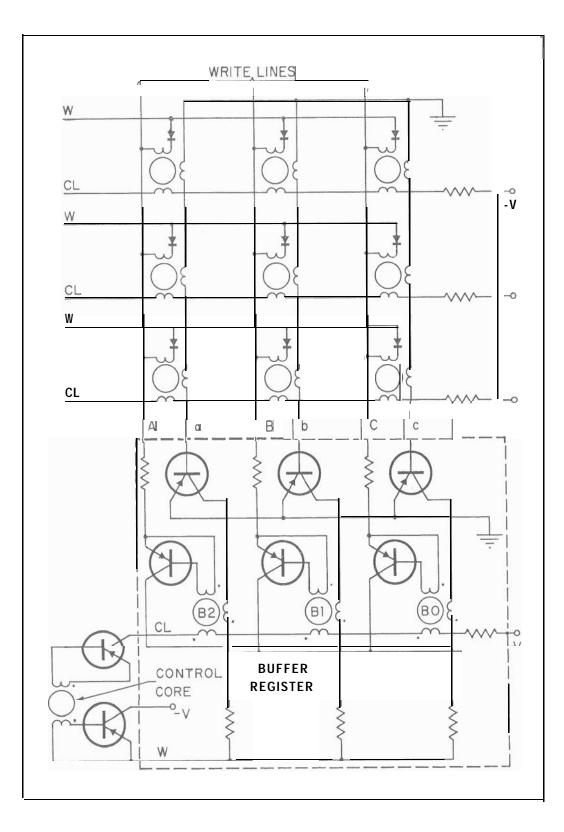

Shown in Fig. 1-6 is a three-bit erasable register. When the control core is made to switch from a ZERO to ONE, transistor TI saturates, and cores (0), (1), and (2) are cleared to ZERO. Those cores which are at ONE will induce an emf in the corresponding Sensing lines in the process of being cleared; ideally, those which are already at ZERO will not. Thus the contents of the register may be read out; e. g., to the special buffer register shown in the figure. Note that the process of reading out from an erasable register leaves all its cores at ZERO. If the original contents are to be preserved they must be written back into the register by a subsequent operation.

To write <sup>44</sup> a word into an erasable register it is necessary to provide a current source on those writing lines for which a ONE is desired. This is indicated in idealized form by a set of relay contacts in the buffer in Fig. l-6. Writing occurs when the control core is switched from ONE back to ZERO. At this time transistor T2 acts as a gate to permit current to flow from ground to the point marked (-V) A ONE is therefore placed in those cores which correspond to closed switches in the buffer register. The diodes of the Write lines prevent interactions between different registers.

A system of three erasable registers of three bits each,

<sup>&</sup>lt;sup>\*</sup>To write into a register is physically the same as to set all the register's cores; the convention used here is that whole registers are written into, while individual cores are set. Both are cleared.

Fig. 1-6 Erasable register.

together with a buffer register, is shown in Fig. 1-7] It is seen that the buffer itself is simply another erasable register, separated from the other three by suitable sensing and writing amplifiers. In order to transfer a word from a register to the buffer, it is necessary to have time coincidence between a pulse on the Clear line of the register and a pulse on the Write line of the buffer. To transfer a word from buffer to register, the process must be reversed; i. e., the Clear line of the buffer and the Write line of the register are pulsed at the same time. The active elements in the Clear and Write lines of each register in Fig. 14 7 are the respective transistors T1 and T2 in Fig. 1-6; thus each erasable register is composed of an array of cores and diodes plus two transistors.

The results of pulsing a register's Clear line without simultaneously pulsing the buffer's Write line will be to leave all the cores of the cleared register at ZERO, and the cores of the buffer unaffected. If the buffer is cleared and the register Write line is pulsed, without having previously cleared the register, then the contents of that register will be the "logical sum" or bit by bit meet of ONE!sfrom the word previously in that register (word A), and the word just cleared from the buffer (word B). In other words, the register will contain a ONE in those positions in which either word A or word B (or both) had a ONE.

Another possibility is that of transferring information between the buffer and two or more registers at the same time. If, at the time the buffer is cleared, the Write lines of the several registers are impulsed, the contents of the buffer will be transferred into each register (assuming them to have been cleared previously). Correspondingly, if two or more registers are cleared at once, the resultant information written into the buffer will be the logical sum of the contents of those registers.

Fig. 1-7 Erasable storage system.

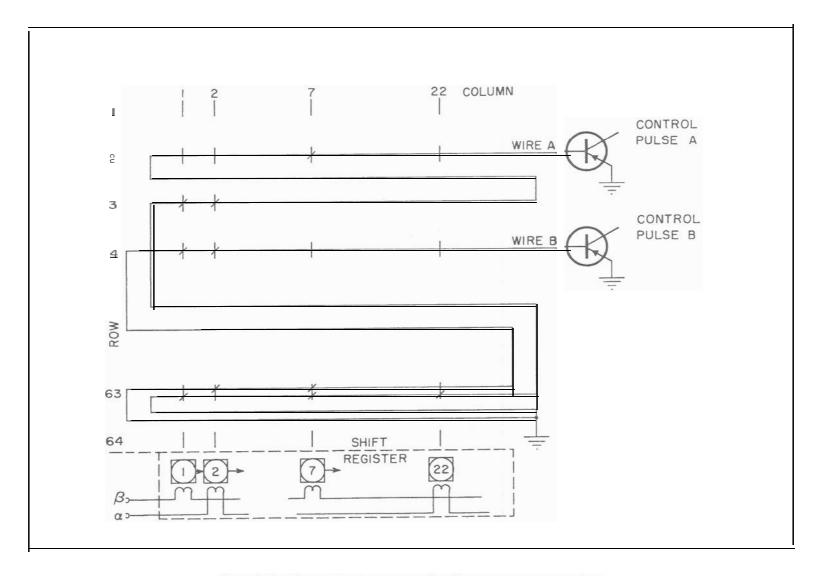

### C. The Erasable Storage System

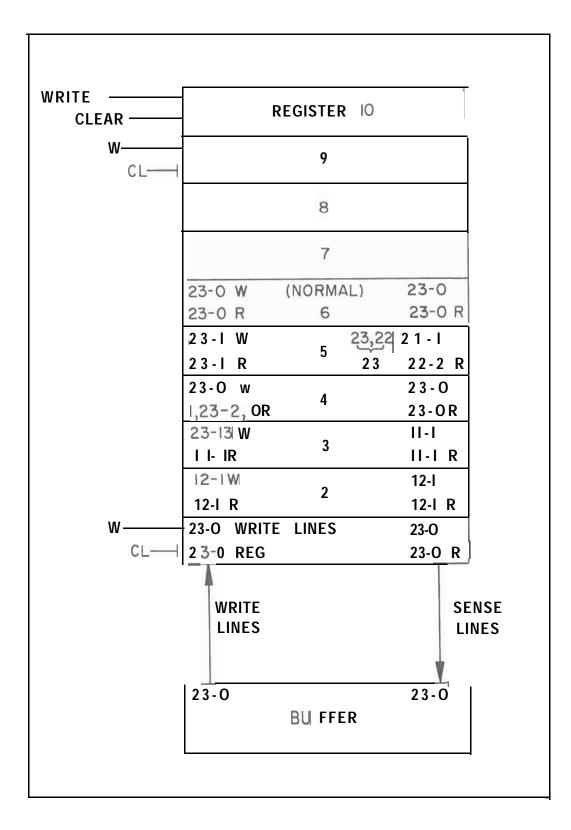

Shown in Fig. 14 8 is a ten-register erasable storage system, identical in operation to the small system of Fig. 1-7, but with additional useful notations illustrated. Examples are provided of several operations which can be performed on a word by use of a register with special rearrangements of the Write and Sense lines. For the sake of definiteness, the number of digits and the structure of the computer word are taken to be those for the representative machine. Each normal word has 24 binary digit positions numbered from 0 (low order bit) to 23 (high order bit). Digit 0 is customarily the parity bit (see Chap. 2, Section A) and, for numerical quantities, digit 23 is the sign bit.

The Write lines in Fig. 1-8 are represented by the arrow at the left, and directly over the arrowhead is, for each register, the list of Write lines (W) versus the bit positions of the register (R). Similarly the right hand numbers S and R refer to the Sense lines which thread the registers, and to their correspondence. For example, Register 1 has lines 23 through 0 connected to bit positions 23 through 0, on both the Write and Sense lines. This is of course the normal configuration; the wiring rearrangements in Registers 2 to 5 are the exception. Unless a register has markings to indicate the contrary, it should be assumed that it is a normal register (e. g., Registers 6 through 10).

Registers 2 and 3 illustrate how wiring can be used to break a word into separate parts for manipulation by the computer. Transfer of a word from the buffer simultaneously into these two registers places digits 12-l in Register 2 and digits 23-13 in Register 3. When Register 2 is subsequently transferred back into the buffer, only the low order digit portion of the original word will be involved; Sense lines 23-13 pass through no cores in Register 2, and will hence carry no pulses (i. e. , ZERO's) to the sensing amplifiers. The clearing of Register 3 will cause digits 23-13 of the original word to appear on Sense lines 11-1, with the

Fig. 1-8 System of ten erasable storage registers.

result that these digits are effectively shifted twelve positions to the right by the wiring of this register. Note that the parity bit (0) is omitted from the wiring of these registers, as it would lose its significance here.

As a further example of wiring rearrangements, Write line 23 is connected to bit position 1 in Register 4, Write lines 22-1 are connected to bit positions 23-2 respectively, and digit 0 is left invariant. The net result of writing a word into Register 4 is to shift it left one bit, with end-around carry, preserving the parity bit in the process. Further transformations may be obtained by manipulation of the Sense lines versus the register bit positions, as in Register 5. Here, Sense lines 23 and 22 both are impulsed by the clearing of core 23; Sense lines 21-1 are connected to bits 22-2. The result is to shift the word right by one digit, with the new digit position 22 being filled with a ZERO if the word is positive (digit 23 ZERO), or with a ONE if the word is negative.

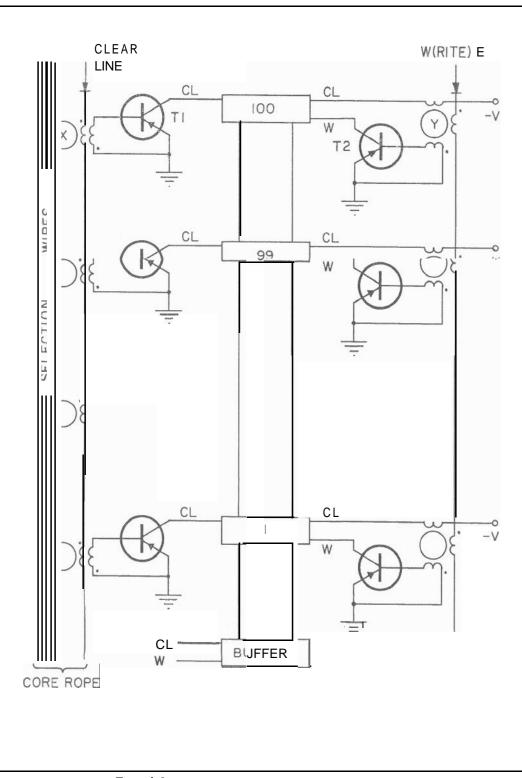

The method for selecting a register is shown in Fig. 1-9. The figure shows a more complicated arrangement of the clearing and writing operations than is illustrated in Fig. 1-6. The added complexity provides greater flexibility and is further made necessary by timing considerations which are discussed in Chap. 1, Section D.

An erasable register is selected by means of a core rope, such as the one described in Chap. 1, Section A, where each core of the rope corresponds to a register. As before, all rope cores start at state ZERO. Selecting a core results in a single core (say core x of Fig. 1-9) being set to a ONE; nothing else happens at this time. When the rope core is reset by a pulse on the CL E line (for Clear E] and previously called the rope Clear line), core x is switched back to ZERO, which causes transistor T1 to fire. The firing of T1 in turn clears the erasable storage Register 100 (hence the name CL E), and sets core y to

ONE. All the cores in the same vertical column as core y (the writing cores of the E registers), started at ZERO; hence after CL E only core y from among the writing cores is at ONE. The subsequent pulse on line W E ( for Write E) drives core y from ONE to ZERO, causing transistor T2 to switch, and allowing the contents of the concurrently cleared buffer to be written into Register 100. As can be seen, writing into a register controlled in this fashion implies having cleared it previously.

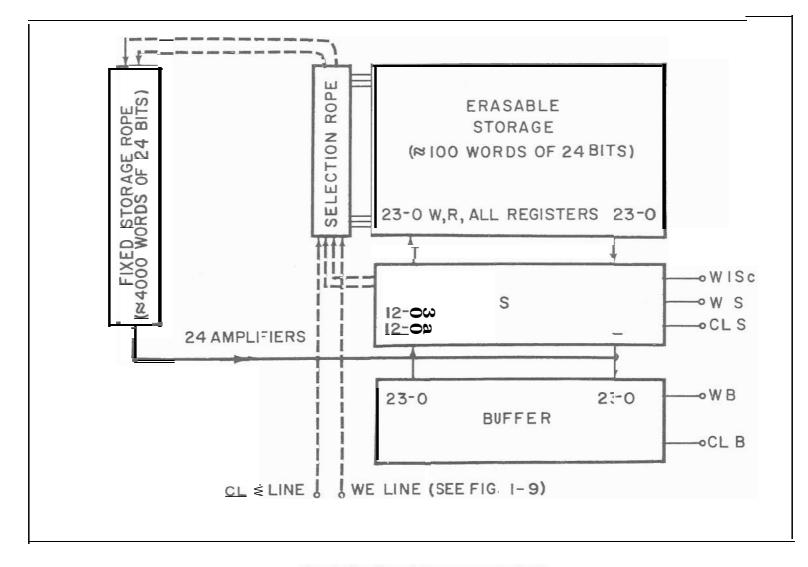

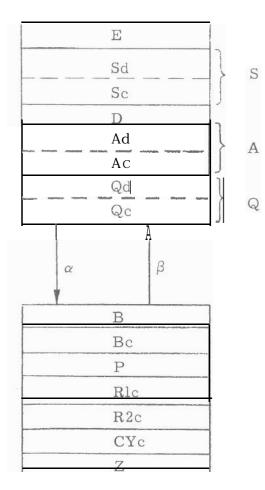

#### D The Complete Memory System

The memory system for this computer consists of fixed storage (F) erasable storage (E)] and a special register (S) called the address register, by means of which storage is addressed. There are, in addition, other special registers of the erasable type called "central registers ", which are used under direct control of the computer logic to execute the various instructions; the buffer B is an example". These are discussed separately in Chap. 2.] Section A; the "memory system" will be defined as the collection of registers which are controlled through the address register S.

The address register consists of two parts, denoted by the symbols Sd and Sc, which stand for the "direct" and "complement" parts of S. Each part is itself an erasable register of a length (12 bits) for the representative computer) sufficient for storing addresses of all computer words. The direct part of S stores the pertinent address. whereas Sc stores the ONE's complement of this address. The clearing of register S (il e. , the simultaneous clearing of Sd and Sc) by the control pulse CL SJ causes the establishment of currents in the Inhibitor and Set lines (Fig, 1-2) required for switching a rope core associated

To be quite accurate, S should properly be called a central register rather than part of the memory system.

Fig. l-9 Erasable storage selection system.

Fig. 1-10 Complete memory system.

with the address placed in S. These selecting currents are represented by the dotted lines of Fig. l-10, and are seen to be common to the fixed storage rope and the erasable storage selection rope. The two ropes thus differ only in their purpose and name, and not in the method used for addressing or selecting a core.

Each bit of Sd and Sc has a current generating circuit connected to it, which drives a corresponding rope Inhibit line. The control pulse CL S clears all cores of both Sd and Sc to ZERO, generating thereby a current pulse in each Inhibit line for which the corresponding core contained a ONE. The pulse CL S itself initiates the current through the Set line. Each pair of corresponding cores in Sd and Sc is associated with a pair of Inhibit lines. The fact that the contents of Sd and Sc are complements thus ensures that exactly one of each Inhibit pair is active.

Register *S* has several peculiarities. It is not connected to the Sense lines, and hence CL *S* does not result in the transfer of a word from S to the buffer. Furthermore, S requires a special control pulse WISc, which results in all the cores in SC being driven to ONE. This pulse is applied before transferring the address from the buffer to *S*, which is done by the pulse WS (and CL B, of course). The latter is the gating pulse which permits writing into both Sd and Sc. The Write lines are connected to Sd in the normal fashion for an erasable register. For Sc, however, the sense of the windings is reversed from the normal direction for writing, so that a current (i e., a ONE on the Write line) causes the core to be driven from ONE to ZERO. Thus any digit position on the Write lines which contains a ONE

By suitable rearrangements of the inhibit wires, it would be possible to have the addresses for erasable registers distributed amongst those for fixed storage in any manner whatever, if this were desirable, even though the erasable registers were themselves physically grouped together.

causes that digit in Sd to be set to ONE and in Sc to ZERO; conversely, a ZERO (no current) leaves Sd and Sc unchanged, i. e. , at ZERO and ONE.

It is now possible to list the sequence of pulses involved in reading from and writing into the complete storage system, and in so doing to explain the timing associated with Fig. 1-9. Each computer clock cycle is divided into two equal intervals called  $\alpha$  time and  $\beta$  time. The computer runs on a two-beat system which, at  $\alpha$  time, information flows into (or towards) the buffer and, at  $\beta$  time, towards erasable storage. Most control pulses have associated with them a specific time, either  $\alpha$  or  $\beta$ , during which they may occur; they may not occur at the other time. For example, CL B can occur only at  $\beta$ , and WB at  $\alpha_1$ A more accurate statement would be that CL B <u>may not</u> occur at  $\alpha_1$  and WB may not occur at  $\beta_1$  for it is not true that a pulse CL B occurs every  $\beta$  time or a pulse WB every  $\alpha$  time.

Assuming an initial address to be in register  $S_{\perp}$  then the following sequence of control pulses will result in a word being read out to the buffer from the register with that address, placed back where it came from if it came from erasable storage, and also placed in  $S_{\perp}$  Each line shows the time,  $\alpha$  or  $\beta$ , associated with these pulses.

| Time       | Pulses            | Comments                   |

|------------|-------------------|----------------------------|

| <i>C</i> 4 | CL S              |                            |

| β          | (wait)            | No control pulse occurs    |

| C/1        | CL E, WB,<br>WlSd | Reset rope, ONE into<br>SC |

| β          | CL B, WS<br>WE    |                            |

Although it may not seem so at first sight, this four -

pulse sequence takes care of both possible cases of reading from fixed or erasable storage. CL S selects a core in the rope regardless of whether it belongs to F or E, driving it to a ONE. CL E resets that core to a ZERO. If the core is associated with a register in E, then that register is cleared, its contents admitted to the buffer by virtue of the pulse WB, and the corresponding writing core (e| g., core y of Fig. 1-9) is set to ONE. When the buffer is cleared at the next  $\beta$  time, the pulse WE resets the writing core to ZERO, permitting the contents of B to be written back into the E register from which it came. The word is also admitted into S by the pulse WS; it is noted that Sd and Sc have been set to ZERO and ONE by the successive pulses CL S and WISc prior to the pulse WS.

If the core switched by CL S belongs to F, then the subsequent CL E and WB causes a wired-in word to be read into the buffer through a set of amplifiers" (Fig. l-10). The last row of pulses again causes the buffer to be cleared and S written into. WE here has no effect, for no writing core has been set to a ONE; hence none of the E registers is affected.

The sequence for replacing the word in an E register by a word previously stored in B is very similar, namely:

$\alpha_1 CL s$   $\beta_1 (wait)$   $\alpha_1 CL E, WlSd$  $\beta_1 CL B, WS, WE$

The only difference is the absence of WB from the second  $\alpha$  pulse. If this pulse is absent, the word cleared from the E

The main electrical distinction. between F and E signals is that those from F are weak and occur in the midst of noise, while signals from E are strong and free from interference. Hence the amplifiers.

register is lost. The pulses occurring at the following  $\beta$  time will cause the word previously placed in B to be transferred into the E register. It was assumed that the address originally in S was an E address, but the wired-in nature of F is such that nothing would happen if the address were an F address.

The control pulse sequences illustrated in this section accomplish quite elementary and restricted objectives, and are introduced primarily to discuss principles of communication with the computer memory. In the next chapter, after a discussion of central registers, **consideration** is given to the formation of control pulse sequences into computer orders in the accepted sense. In particular, an order code is given in more or less complete form for the representative computer, and possible variants are also presented.

### CHAPTER 2

#### EXECUTION OF COMPUTER INSTRUCTIONS

#### A. Central Registers and Overall Organization

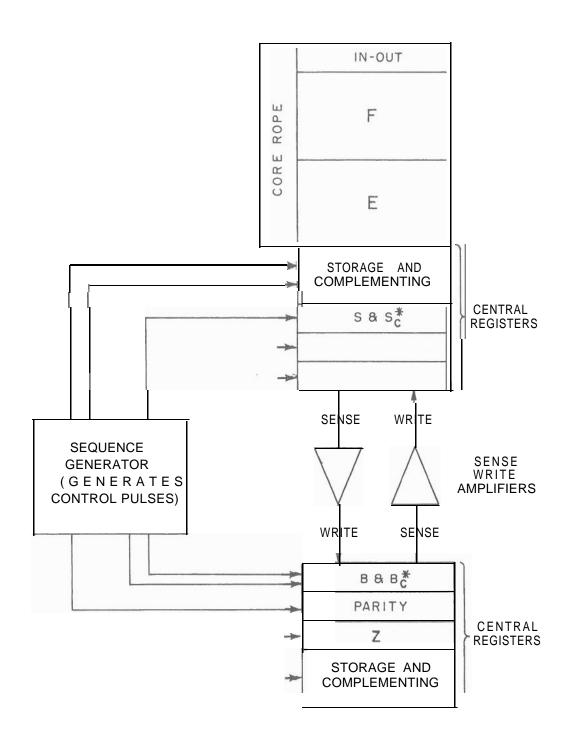

The overall organization of the computer, shown in Fig. 2-1, includes storage, discussed in Chapter 1, input-output equipment, discussed in the next chapter, together with the sequence generator and central registers which comprise the main logic for executing computer instructions. In this chapter the central registers and sequence generator are discussed, first in terms of generalities, and subsequently in somewhat more specific form in relation to the order code for the representative computer. In spite of the latter discussion, however, it should be emphasized that we are here concerned with a diverse class of possible machines rather than primarily with the specific computer selected as "representative"; this should be evident from the number of alternatives which are presented from time to time.

Central registers are, by definition, all those registers which are not addressed by means of the address register S, but whose control pulses are provided directly by the sequence generator. Registers S and B, for example, have previously been described as central registers; the pulses CL B, WS, etc., are provided by the sequence generator, as are the others listed in Chap. 1 Section D as necessary for reading from memory. The outputs from the sequence generator are, at pulse times  $\[mathbf{address}$  and  $\[mathbb{\beta}]$ pulses which bear names like CL B, CL E | WE, WS, W1Sc, etc.

Fig. 2-1 Over-all organization of the representative computer.

Most of these control pulses go the central registers; however,al few like CL E have other purposes. What follows is a brief description of the various kinds of central registers and a possible central register organization.

The overall computer organization is shown in Fig. 2-1. There are two sets of Sense and Write lines, one for the transfer of words from the core rope side to the B side, and one for the transfer of words from the B side to the rope side. Central registers may be on either side of the Sense- Write amplifiers and are of three kinds: special-purpose registers which have extra circuitry, complementing registers, and ordinary storage registers. The special-purpose registers are the address register S discussed previously, the **Z** register, the parity register P, and the buffer B. These are discussed separately in subsequent paragraphs. As in E storage, ordinary storage registers may occur with rearranged wiring to secure various special effects.

The "rope side" of the Sense- Write amplifiers is henceforth called the <u>o</u> side of the register system; i. e., the side on which registers are <u>cleared</u> at <u>a</u> time. The "B side" is correspondingly called the  $\underline{\beta}$  side. The division of the computer into an <u>a</u> side and a <u> $\beta$ </u> side, together with the electrical properties of the erasable storage scheme, helps explain the working of the computer on a two-beat system and why each control pulse has a particular time (<u>a</u> or <u> $\beta$ </u>) at which it occurs.

At  $\alpha$  time information flows from the  $\alpha$  side to the  $\beta$ side and at  $\beta$  time from the  $\beta$  side back toward the  $\alpha$  side. It would appear that both actions could take place simultaneously, because separate sets of Sense-Write amplifiers are used. Consider, however, the signals from the sensing windings on the  $\alpha$ side. These result from certain cores on the  $\alpha$  side being cleared from ONE to ZERO at  $\alpha$  time. If other cores on the  $\alpha$  side are being driven from ZERO to ONE by a simultaneous writing operation, a reverse emf is induced in the corresponding sense lines

which cancels the desired signals where overlapping occurs. As a **result**, there is a significant coupling from the write side of one set of amplifiers to the sense side of the other set which prevents them from being active at the same time. Various electrical schemes could eliminate or avoid this restriction; however, the present arrangement appears to offer a simple and reliable system.

The  $\mathbb{Z}$  register is a special-purpose register that adds "one" to a number read into it, so that a transfer into and out of  $\mathbb{Z}$  converts the number N into N t 1. It is used, on the one hand, to store and increment the address of successive computer instructions when these occur in sequence. On the other hand, it is used on a time-shared basis to increment the various program or input counter registers (see Chap. 2, Section C and Chap. 3, Section E respectively). The electrical nature of the  $\mathbb{Z}$  register is fairly well established; however, at the moment of writing, there are one or more unsettled questions concerning its logical integration with the rest of the computer. These relate to the treatment of input situations in which pulses to be counted may be either plus or minus, and to the length of the  $\mathbb{Z}$  register,

The parity register, P<sub>1</sub> accepts inputs on all 24 Sense lines and computes whether the number of ONE's in the word being read into it is even or odd. Its output is one bit long and occupies digit position 0; if the number of ONE's in the word is even, then the parity bit will hold a ONE. A parity system is employed in which the total number of ONE's in a word including its parity bit, must be odd to pass the parity test. When such a word is read into P<sub>1</sub> the contents of the parity bit will be zero, so that an alarm will not be triggered when P is subsequently cleared and tested. If, on the other hand, a 23-digit word is read into P with its parity bit missing, the parity register computes and stores the correct value in digit position 0. Thus the parity may be transferred to E storage along with digits 1-23 by clearing P at the same time the remainder of the word is stored.

The buffer register B is a special central register used as an ordinary register in communicating with storage and also used in the decoding of computer instructions. It is composed of two parts, Bd and Bc, as is the address register S. The direct part, Bd, is a full-length register; however, the complement part, Bc, occupies only the digit positions used by the order code (digits 13-18 for the representative computer). The latter bit positions of both Bd and Bc are wired to generate Inhibit pulses in a special short core rope, for selecting a sequence in the sequence generator. They operate in the same way as Sd and Sc, being cleared by the special pulse CL Bc. The pulse called CL B actually should be entitled "CL Bd" since it leaves the complement portion of B untouched. Also, the pulse CL Bc clears corresponding digits in both Bc and Bd and further provides a gate to permit the Inhibit currents to flow. The latter is necessary since Bd is used for other purposes.

Central storage registers are identical to ordinary erasable storage registers. They each require two control pulses, CL register and W register(for| "Clear" and "Write"). Complementing registers are similar to storage registers but with one extra common winding added. This winding is used to set all the cores in the register to ONE, and is pulsed by a control pulse Wl Register(for| "Write Ones"). The polarity of the windings which connect each core of a complementing register to a Write line is reversed relative to the polarity of a storage register. Thus if a word is written into a complementing register which has been set to all ONE's, the register will then hold the bit by bit complement of the word.

The number and arrangement of central registers of the storage and complementing types is a function of the order code desired, and of the way in which the order is translated into a sequence to be generated by the sequence generator. In

Fig. 2-2 Sequence generator.

general, the more powerful the order code, the larger the number of such central registers. These registers are in themselves no more expensive than those in erasable storage, but addressing them must be done through the sequence generator which is a costlier process than addressing through a rope. Later in this report specific arrangements of central-registers will be discussed in order to illustrate how certain things can be done and what alternatives there might be. This discussion is necessarily tied to a discussion of the order code and of the sequence generator. The address register S, the "add one" register Z, the parity register P, and the buffer B are common to all computers under discussion.

# B. The Sequence Generator

The sequence generator forms what is commonly called the "logic" of a computer. Other common names for it are program counter and microprogram store. The basic idea is that of associating a sequence of control pulses with each kind of order stored in F or in E. The sequence involved in transferring the contents of some register X into X and central register A, which bears the name "clear and add X" or CA X, is one such order. That involved in storing the contents of A in X, called "transfer to storage X" or TS X, is another. By means of the sequence selection circuits (mentioned above in connection with the buffer), each combination of bits in the order code digit positions of an instruction is made to correspond to the particular pulse sequence for execution of that instruction. For reasons which will become clear later, all sequences produced in the sequence generator are called "zero level sequences".

The order structure of the representative computer is such that bit 0 (numbering from low-toward high-order digits) indicates the parity of the word (cf. Chap. 2, Section A), and the next twelve bits (bits l-12) are for any address which forms

Fig. 2-3 Control pulse generation by sequence generator.

part of the instruction (e. g. , the "X" in CA X). Digits 13 to 18 form the symbol or code for an order, i. e. , the "name" of a sequence. The remaining five digits may have other optional uses which in effect, cause them to act like part of the order code.

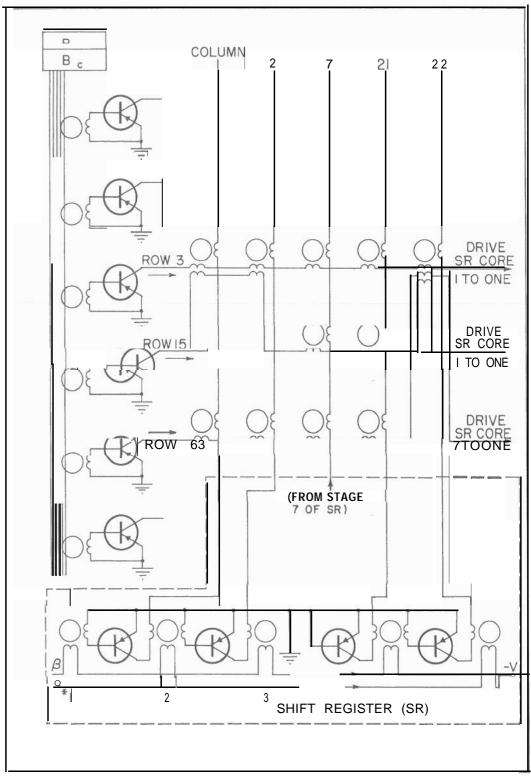

The sequence generator is a complicated device, and hence a simplified case will be discussed first. Consider a rectangular matrix, made of cores, with 64 rows and 22 columns (Fig. 2-2, 2-3). At the bottom of each column there is a core transistor circuit, symbolized in Fig. 2-3 by a square box with a number inside it, which, when fired, drives all cores of that column to ZERO and drives to a ONE the core in the next transistor- core element. These 22 elements form a shift register. All the cores in the matrix start at ZERO. Selecting a sequence means setting a row of cores to ONE's and placing a ONE in the first position of the shift register (Fig. 2-2). Hence only one core of each column may be switched to ZERO by the corresponding shift register element \*. As the shifting pulses  $\alpha$  and  $\beta$  (Fig. 2-2 and 2-3) shift the single ONE in the shift register through all positions from (1) to (22) all the matrix cores set to ONE (forming a row) are cleared to ZERO one by one. Each control pulse has a wire associated with it, which threads (or "not threads") the cores of each row. Thus when a row of cores switches in sequence, the wire has a pattern of outputs and "no outputs" impressed on it.

For example, consider control pulse A (Fig. 2-3) if the selected row is (2). The only output (i.e., the only control pulse) will occur at shift time 7, i. e., when the ONE travelling down the shift register is being transferred from position (7) to position (8). If the sequence selected had been sequence ( $\exists$  row) (3)] then there would have been outputs at time 1 and 2. Notice further

All cores of that column are driven to ZERO, but only one switches, since only one of the cores of that column was switched to ONE in the first place.

that sequence (1) involves neither pulses A nor B, while sequence (63) involves both

There are several variants of the matrix just described which enhance the flexibility of the sequence generator and permit certain economies . The particular use of these variants depends directly on the properties of the sequences, which will be discussed later: and hence the variants are presented here as "tricks" which. can be used if certain situations arise.

The most obvious variant is illustrated in Fig. 24 2 and consists in modifying the meaning of "row"] Selection of a sequence means setting to a ONE some cores of the matrix, where each column will have at most one core set to ONE. Many sequences may have common parts; for example, they must end with an identical set of control pulses, for calling forth the next instruction. Then She same core in the matrix may be set by the various sequences, as in the case of the core of row (1), column (22)] Fig. 2-2. In fact, that core is the only core present in column (22)] Also, it is possible that a sequence may require a waiting period of one or more pulses, in which case the sequence selecting wire which sets a "row" to all ONE's will simply not set any core of the pertinent columns to a ONE. For example,] sequence (15) (row 15) does not set any core of column (21).

A further "trick" consists of the use of the sequence selecting mechanism for specifying the starting point in the shift register. In Fig. 2-2, sequences (3) and (15) start at shift position (= time) 1, while sequence (63) starts at time 71 This scheme is useful in avoiding unnecessary waits and delays. Thus, the sequence CA X (clear A and add the contents of register X into A) and the sequence CA\* X, in which X is now interpreted as the location of the address of the data, are such that the set of pulses for CA X is a subset of those for CA\* X| CA X starts at time 71 CA\* X starts at time 1 and is identical to CA X from time 7 on, The wire which selects sequence CA X drives core 7 on the shift

register to ONE, thus avoiding a wait of 6 pulse times.

21

A third and final variant of the basic scheme consists of providing for branches. This is done by using a sequence to test the state of a core, e. g., the core in which the sign of the quantity presently in A is stored. This result is then used to select one of two sequences, i. e., to set to ONE's the cores of one of two "rows". This is discussed further in the next section.

### C. Representative Order Code System

For purpose of illustrating the variety of computer operations which can be accomplished by rather simple wiring and logic, a representative system of central registers and instructions, is described in this-section. The system is not completely described here; details are not sufficiently settled to make this possible. As show below, however, some relatively sophisticated operations can easily be achieved.

The central register system shown in Fig. 2-4 contains registers S (Sd, Sc), B and Bc, P, and Z which have already been discussed. In addition are shown ordinary register D, registers A and Q, each of which consist of a direct and complement part, complementing registers Rlc and R2c, together with register CYc which simultaneously complements a word and cycles it left one digit with end-around carry. Four control pulses affect register A: WAd, and WAd for writing respectively in the direct and complement portions, CL A, which clears both halves simultaneously, and WIAd to place ONE's in Ac. Register Q possesses corresponding properties. Registers Rlc, R2c, and CYc, possess three control pulses each for writing, clearing, and placing ONE's in the cores before writing.

To illustrate an entire sequence of steps comprising one relatively simple order, consider the instruction "Clear and Add  $X^{11}$ , CA X, as described previously. Control pulses for CA X are given in Table 2-1. Each instruction must bear the responsibility for calling forth fro-m storage the next instruction in

| Register | Digits |

|----------|--------|

| S        | 12-1   |

| A,Q      | 23-1   |

| B,Rlc,   | ]      |

| R2c, CYc | 23-0   |

| Z        | J      |

|          |        |

Fig. 2-4 Representative Central Register System

# TABLE 2-l

CA X, Clear and Add X, C(X) into A, 8 pulses

α CL S, CL A, CL D

β (no action)

α CL E, WB, WP, WISd

β CL Z, WS, WD

α CL S, CL D, WZ, WIR2d

β CL B, CL P, TP, WAd, WE, WIBd

α CL E, WB, WP, WR2c, WISd

β CL B, WE, WS, WD, CL Bc, CL P, TP

sequence, after its own action is complete, so that the control pulses form a never ending sequence. A convention which states at what point of the process the "new" order takes over the "old" must be adopted here. The operation CL Bc, shown in the last line of Table 2-1, sets the appropriate line of cores in the sequence generator core matrix for the new instruction; it is therefore reasonable to define the  $\alpha$  - pulse time which immediately follows as the first pulse of the next order.

To follow the actions described by the control pulses in Table 2-1] it is necessary to know that certain of the central registers are assumed to have been left with particular contents by the previous order. Line 8 in the table is the last line executed by every instruction; at the time of its execution, the next order is in B. By the action of line 8, the order is written back into E (if it came from E)] into D, and the address portion is written in S. Thus at the time of initiating CA X, in line 1 of the table, the last line of the previous instruction has placed the address X in S and the entire order in D. The effect of line 1 for CA X is to clear D, to clear the accumulator A in preparation for later receiving the contents of X, and to initiate read-out of address X through setting the corresponding rope core.

Line 3 of Table 2-1 transfers the contents of X into the buffer, B, and writes them also into the parity register P. The Z register at this point contains the address of the next instruction, N # 1; line 4 transfers this address to S as the initial step in the action of calling the next instruction forth. The number n # 1 is also saved in register D, from where it is cleared in line 5 back into Z. The result leaves N # 2 in Z as the address of the instruction after next. Neither of the actions CL S or W1R2d interfere with this transfer since S has no sense wires and since the sense wires for R2d are in use only at  $\beta$  time. The control pulses W1R2d in line 5 and WR2d in line 7 serve the purpose of saving in R2d the complement of each instruction

executed; this feature is required only in a very special situation to be discussed later. It is noted that W1R2c prepares R2d to receive a new word just as effectively as clearing an ordinary register. All cores are left at ONE's, regardless of their previous status.

In line 6 the pair of pulses CL B, CL P places on sense lines 23-O the full word, including its parity bit, that was read from storage. The parity bit comes from digit 0 of B in this instance; the contents of the single bit called register P are properly a ZERO at this time since an entire 24 digit word from storage, with presumably correct parity, was read into P in line 31 Thus the pulse on digit 0 sense line is the logical sum of a ZERO and digit 0 of B. The control pulse **labelled** TP (Test Parity) activates a test to verify that P does indeed contain a ZERO as it is cleared An alarm, as yet specified, or an error diagnosis procedure is to be initiated if this is not the case.

Line 6 writes the original word from storage back into E if required, and writes digits 23-l of the word into part Ad of the accumulator A. Thus the contents of register X have been placed in A, and X is left unaltered. The next instruction is already in the process of being called forth by the pulse CL **S** of line 5 which sets the appropriate rope core. The occurrence of the pulse WE in line 6 after the pulse CL S in line 5 may offer some confusion, until it is recalled that the write core for an erasable register is set only when the rope core is reset. Thus the rope core for the next order, i. e.  $\downarrow$  core N + 1, may be set prior to the time at which the erasable storage write core (if any) associated with register X is reset.

The pulse WlBc places ONE's in Bc to enable the complement of the order code to be obtained through the WB pulse in line 7. The fact that WlBc occurs simultaneously with CL B would at first glance appear to violate basic principles. Register

Bc contains no sense windings, however: except those connected to the logic decoding rope. Further, CL B leaves Bc unaffected; only WB is common to B and Bc.

The principal action of line 7 in Table 2-1 is to call forth the next instruction from storage, writing it directly in the buffer B (and in Bc, as well), in the parity register, and in the form of its complement into R2cl Line 8 has already been discussed briefly above; the new order is written back into E if relevant, into D, its address portion into  $S_{\parallel}$  its parity is checked, and the pulse CL Bc transforms its order code into appropriate action in the sequence generator.

Considerable detail has been brought into the analysis of the pulse by pulse action of a single elementary order, CA X, because in so doing a considerable portion of the logic of most of the rest of the orders is also presented. In the following paragraphs and tables other typical orders are presented, generally with no more than a few sentences of description attached to each. These descriptions are made somewhat more concise by use of a few simple abbreviations and conventions. The order being executed is understood to have been found in register N, and the next order is located in register N + 1 unless otherwise noted. The address portion of the order is denoted by X, as in CA X above. The contents of any register are denoted by the symbol C() with the symbol for the register inserted in the parentheses; e. g. the contents of A are written C(A). The system of arithmetic used here is that in which the negative of a word is simply its ONE's complement, denoted by following that word with a prime: -C(X) is the same as C(X)<sup>'</sup>. Finally, a register X, A, or Q is understood to be left unchanged by the action of an order, unless a change is indicated specifically.

The order TS X, to store the contents of A, has been mentioned previously. As seen from Table 2-2, it differs from CA X only in that the contents of A are transferred to B and P

in line 1, instead of being discarded, and the contents of X are discarded in line 3 instead of being transferred to B and P. Note that CL P in line 6 is here not accompanied by the parity test pulse TP as it was before. Instead, the correct parity bit for the word read into P in line 1, on digits 23-1, is supplied as the output of P on digit 0. The physical action of the parity circuit is the same in the two cases, but its function is different. Digit 0 of B is ZERO in line 6, since only positions 23-1 were filled from A in line 1.

# TABLE 2-2 TS X., Transfer to Storage X, C(A) into X, 8 Pulses 1 $\alpha$ CL S, CL A, WB, WP 2 $\beta$ (no action) 3 $\alpha$ CL E, CL D, W1Sd 4 $\beta$ CL Z, WS, WD 5 $\alpha$ CL S, CL D, WZ, W1R2e 6 $\beta$ CL B, CL P, WAd WE, W1Bd 7 a CL E, WB, WP, WR2c W1Sd 8 $\beta$ CL B, WE, WS, WD, CL Bc, CL P, TP

The instruction CS X, to clear A and place the negative of C(X) in A, is seen in Table 2-3 to differ from CA X only in the pulse W1Ac in line 2 and in the replacement of WAd by WAd in line 6.

# TABLE 2-3 <u>CS X, Clear and Subtract X, C(X)'intol A, 8 Pulses</u> 1 $\alpha$ CL S, CLA, CLD 2 $\beta$ WIAc 3 $\alpha$ CL E, WB, WP, WISd 4 $\beta$ CL Z, WS, WD 5 $\alpha$ CL S, CL D, WZ, WIR2d 6 $\beta$ CL B, CL P, TP, WAc, WE, WIBc 7 $\alpha$ CL E, WB, WP, WR2c, WISc

8  $\beta$  CL B, WE, WS, WD, CL Bc, CL P, TP

If, the first line of control pulses for CA X, the pulse CL A is omitted, the result is an order LA X as described in Table 2-4, called "Logical Add X". The effect of this order is to place in A the word which is the union or logical sum of the previous C(A) with C(X); i. e. , the word whose digits are ONE in any digit position where either or both of C(A) and C(X) contain a ONE. The application of an order of this type occurs principally in such logical processes as masking, in which only selected digits of a word are to be used in an operation. A more suitable order for this purpose is that for forming the logical product of C(X) with C(A); however, the operation LA X is so simply achieved that it is probably preferable unless a very rapid masking order is needed.

It is noted that LA X writes in the cores of Ad. If the order just preceding LA X were a clear and subtract operation, the cores of Ad would all contain ZERO's and the cores of Ac would contain the real "contents of A". It must be recognized that the pulse CL A places on the a sense lines a ONE wherever either Ad or Ac contains a ONE; i. e. , the logical sum of C(Ad) and C(Ac). Thus the effect would be the same as if it were Ad rather than Ac that contained the non-zero information. For all logical purposes, A may be regarded as a single row of cores in which a logical sum is formed as the writing takes place.

# TABLE 2-4

# LA X, Logical Add X, C(X) U C(A) into A, 8 Pulses

1 a CLS, CL D

2 to 8: The same as in Table 2-l

An operation having frequent convenience as a storage saving device in arithmetic, but which in addition has an unique logical function in the present computer, is that of exchanging

C(X) with C(A). The logical function has to do with counter All registers that receive input pulses from an external source. counting (which uses the Z register) occurs at a definite place in the sequence generator shift register at which the Z register is vacant; specifically, this is between lines 4 and 5 in the previous tables. If the contents of an externally pulsed counter register are to be examined without risk of missing a pulse in the count, it is necessary to be able to pick up the counter contents and to reset the counter to a known value simultaneously in a single order. Even the order CA X, when applied to a counter register, is not a safe way of examining the register as the order is now written, since the pulses CL E and WE are separated by the time at which counters are incremented. The order EX X, Exchange with X, described in Table 24 5 does achieve the desired result, permitting the contents of the counter to be placed in A and those of A in the counter during a time period in which no incrementing can occur.

### TABLE 2-5

### EX X, Exchange with X, C(X) exchanged with C(A), 12 Pulses

$\alpha$  CL S, CL D  $\beta$  (no action)  $\alpha$  CL E, WB, WlSd  $\beta$  CL B, WD  $\alpha$  CL A, WB, WP  $\beta$  CL B, CL P, WE  $\alpha$  CLD, WB  $\beta$  CL Z, WS, WD  $\alpha$  CL S, CL D, WZ, WlR2c  $\beta$  CL B, WAd, WlBd  $\alpha$  CL E, WB, WP, WR2c, WlSc  $\beta$  CL B, WE, WS, WD, CL Bc, CL P, TP No parity check is made on the original contents of X in the exchange order; for counters, in the present mode of operation, a parity check is not kept. An alternate counter operation method in which the  $\mathbf{Z}$  register would be on the  $\alpha$  side of storage would permit parity to be preserved.

The exchange order is the first one that has been encountered which involves other than eight pulse times for its exe cution. Its beginning is identical to that for LA X and its ending is identical to all orders considered. In the interest of economy of cores and windings in the sequence generator core matrix, the shorter orders are therefore stretched out to match the twelve columns of cores required for EX X. This operation is not done in a way so as to cause the other orders to waste four pulse times of inactivity, but requires the shorter orders to skip over several positions of the shift register. The result permits each instruction to proceed with no waste of time, and yet permits many cases of sharing of matrix cores between different orders. The numbering of the lines in the tables shown here is for convenience only, and does not correspond to core matrix columns.

The instruction "Edit by X" is perhaps unique to this particular computer, and is motivated by the fact that many of the operations such as shifting are handled by special write wiring in registers in E storage. The function of this order, in brief, is to accomplish in one order of twelve pulse times what would otherwise require the two orders TS X, CA X and sixteen pulse times. Its operation is described in the table which follows.

### TABLE 2-6

ED X, Edit by X, C(A) into X, then C(X) into A, 12 Pulses

a CL S, CL D, WB

β (no action)

α CL E, WISd

β CL B, WS

α CL S, CL A, WB, WP

β CL B, CL P, WE

α CL E, WB, WP,WISd

β CL Z, WS, WD

α CL S, CL D, WZ, WIR2d

β CL B, CL P, WAd, WE, WIBc

α CL E, WB, WP, WR2c, WISd

β CL B, WE, WS, WD,CL Bc, CL P, TP

Orders dealt with up to this point have been chiefly concerned with moving information around from one point to another. Consider now the order TC X, transfer control to X, which causes the next instruction executed to be that in register X. In the process, the next consecutive address (i. e. , the address one greater than that of the location of TC X) is left in central register Q from which it may be stored by TA X, below. This pair of orders provides convenient entry and exit procedures for closed subroutines.

| ΤA | BL | Е | 2- | 7 |

|----|----|---|----|---|

|    |    |   |    |   |

| TC X, Transfer Control to X, N + 1 into Q.  |

|---------------------------------------------|

| Next Operation from X, 6 Pulses             |

| 1 a CLQ                                     |

| 2 B CL Z, WQd                               |

| 3 a CL S, CL D, WZ, W1R2d                   |

| 4 β WlBc                                    |

| 5 α CL E, WB, WP, WR2c, WlSd                |

| 6 $\beta$ CL B, WE, WS, WD, CL Bc, CL P, TP |

It is noted that the order itself goes into the Z register in line 3, rather than merely the address, and a similar statement is true for certain branch orders considered later. This can, in turn, result in order codes being attached to the addresses which enter Q and thence are stored by the TA order. The effect of this, if recognized in programming, can cause little harm.

The transfer address order, TA X, serves an additional purpose beyond that of storing the contents of Q| This other purpose is the transfer to Q of the contents of R2c; thus two TA orders following each other will store successively the original contents of Q and of R2c. Otherwise, TA X closely resembles TS X in operation.

### TABLE 2-8

# TA X, Transfer Address to X, C(Q) into X, then C(R2c) into Q, 8 Pulses

α CL S, CL Q, WB, WP

β CL R2cJ WQ

α CL E, CL D, WlSc

β CL Z, WS, WD

α CL S, CL D, WZ, WlR2d

β CL B, CL P, WE, WlBd

α CL E, WB, WP, WR2cJ WlSd

β CL B, WE, WS, WD, CL Bc, CL P, TP

We now come to consider a group of three branching orders, that cause a transfer of control to occur or not, depending upon the outcome of a test. Representative of such orders is BNZ X, branch non-zero  $to X_j$  which tests central register A and acts as a TC X order if A contains any ONE 's. Electrical details of the branching action have been considered only in a preliminary way; however, the principles are relatively simple. The original setting of a row of cores in the sequence generator core matrix for BNZ X skips certain columns (i. e., shift register positions). These are filled in subsequently in one of two alternate ways selected by the result of the testing operation. Thus lines 3 to 7 in Table 2-9 are filled with two choices which depend upon whether C(A) are zero or not. Control pulses describing details of this action are not shown; however, the testing is done as C(A) are written into B in line 1, and the actual action of setting one of two rows of cores is indicated by the word "BRANCH" in line 2.

### TABLE 2-9

| BNZ X, Branch Non-Zero to X, | Acts as TC X if C(A)             |  |  |  |  |  |

|------------------------------|----------------------------------|--|--|--|--|--|

| are Non-Zero, Otherwi        | are Non-Zero, Otherwise Order is |  |  |  |  |  |

| Ignored, 10 Pu               | ilses                            |  |  |  |  |  |

| 1 QICLS, CLA, WI             | 3                                |  |  |  |  |  |

| 2 $\beta$ CL B, WA, BRA      | NCH                              |  |  |  |  |  |

| Active branch                | Inactive branch                  |  |  |  |  |  |

| (non- zero)                  | (zero)                           |  |  |  |  |  |

| 3 व (no action)              | 3 $\alpha$ CL E, WB, WlSd        |  |  |  |  |  |

| 4 🛱 (no action)              | 4 $\beta$ CL B, WE               |  |  |  |  |  |

| 5 & CLQ                      | 5 a CL D                         |  |  |  |  |  |

| $6$ $\beta$ CL Z, WQ         | 6 $\beta$ CL <b>Z,</b> WS, WD    |  |  |  |  |  |

| 7 a CL D, WZ,W1R2d           | 7 $\alpha$ CL S, CL D, WZ, W1R2d |  |  |  |  |  |

| 8 ß WlBc                     |                                  |  |  |  |  |  |

| 9 a CL E, WB, WP,            | WR2c, WlSd                       |  |  |  |  |  |

| 10 $\beta$ CL B, WE, WS,     | WD, CL Bc, CL P, TP              |  |  |  |  |  |

A branch order closely related to BNZ X is the order BMN X, branch minus to X, which tests the sign (digit 23) of A and acts as TC X if this bit contains a ONE denoting a negative number. The formal table of control pulses for BMN X is identical to that of Table 2-9 for BNZ X. The sole difference lies in one control pulse, not shown in the table, which determines the nature of the test. For BNZ X, all 23 bits of C(A) are tested, whereas for BMN X only the single high-order bit is involved.

A further branch order, similar to BNZ X except that the control pulses CL A, WB, CL B, WA are omitted in lines 1 and 2, is that for testing for overflow of a program counter. Certain erasable storage registers may be set aside as counters by provision of extra circuits described in Section E of Chapter 3. Those used by the program for its own bookkeeping purposes differ from those for external pulse inputs in the source of the input to be counted and in the disposition of any overflow pulses. Extra digit positions in the instruction word are so wired that a ONE in that digit causes an associated program counter to increment by one after the order is executed. For this particular class of counters, any overflow pulses are used to set an overflow core which may be tested at any later time. The "branch no overflow" instruction, BNO X, is the means for this test. This instruction acts as TC X provided than no. overflow pulse has occurred, and is otherwise ignored (except that it clears the overflow core).

One final branching order of frequent convenience is that designated as TRSP X, "test register X and skip (next order) if plus". If C(X) are negative, the next order is taken from N + 1; if C(X) are positive, the next order is taken from N + 2. Further, the absolute value of C(X) is left in Q from which it may be stored by TA.

TABLE 2-10

TRSP X, Test Register X and Skip on Plus, 10 Pulses If C(X) plus, next order from N + 2 and C(X)into Q; If C(X) negative, next order from N + 1 and C(X) into Q 1 CL S, CL Q, WIRld 2 CL Z, WD 3 CL E, WB, WP, WRlc, WlSd 4 CL B, CL P, TP, WE, BRANCH Active branch Inactive branch (negative) (positive) 5 CLD, WB 5 CL D, WZ 6 CL B, WS, WD 6 CL Z, WS, WD, WlQd 7 CL S, CL D, WZ, W1R2c 7 CL S, CL D, WZ, W1R2c 8 CL Rlc , WQd, WlBc 8 CL Rlc, WQc, WlBd 9 CL E, WB, WP, WR2c, WlSc 10 CL B, WE, WS, WD, CL Bc, CL P, TP

The order CANP X stands for "clear and add, with no parity (check)". Its purpose is to provide a way to operate with registers for which the parity bit may be incorrect or absent; e. g. , the register for shifting right one digit, described in Chap. 1, Section C, or an input register. The pulse sequence for CANP X is essentially the same as that of CA X in Table 2-1 except that the pulse WP is missing from line 3 and the pulses CL P, TP are absent from line 6.

The automatic interrupt, discussed in Chap. 3, Section C, is an interruption to the normal sequence of computer operations caused by various input circuits which require attention. It occurs, when required, just before execution of the last line in an instruction so that the next order has been called from storage but not yet transferred to the sequence generator. Instead of the next order, a special "interrupt" sequence of control

pulses is generated which, in addition to several specialized logical actions, stores away the contents of selected central registers required to permit the normal instruction sequence to resume later without any apparent discontinuity. These contents are stored in other central registers, not shown in Fig. 2-1; probably two such registers can be made to suffice.

The interrupt sequence is not itself a programmable order, however there is at present in the order code system an order RSM X, "resume" (X) is irrelevant), which provides a control pulse sequence for resuming operation after an interrupt. The effect of RSM X is, first, to test whether another interrupt request has occurred while the actions called for by the original interrupt were in progress (no more than one interrupt is processed at a time). If not, the contents of the central registers are restored and the operation of the main program is resumed.

As any programmer knows, one of the most important computer capabilities required for compact and elegant programming is that of address modification; i. e., the capability of writing an instruction whose effective address at the time of execution depends upon other actions of the program itself. In this computer the problem is solved in terms of quite simple circuits by providing the capability for so-called "indirect addressing" for every order. The effect of indirect addressing on an instruction is to replace the address mentioned in the instruction by the address contained in that location. For example, let an asterisk following an order code indicate that indirect addressing is to be applied, and let the contents of register X be the number Y. Then CA# X is essentially synonymous with CA Y. If X is an erasable register (otherwise the operation is pointless) then its contents Y may be given different values by operation of the program, and the single wired-in instruction CA<sup>\*</sup> X may thereby have a corresponding variety

### of effective addresses

When combined with the use of program counters and the previously mentioned capability of incrementing these automatically under control of selected digits in the order codethe indirect addressing capability permits some quite compact. programs For example let. if be desired to move N consecutive words in storage locations K to K + N = I to the new locations L to L + N = 1. To do this we **place** the address K in a counter C1] address L in a. counter C2] and place hhe number -(N - 1) in a counter C3. Following this preliminary operation the actual execution is accomplished with a loop of three orders.

| Address |   | $m \in CA^{\otimes}$ Cl | and increment | С3 |

|---------|---|-------------------------|---------------|----|

|         | m | $+ 1$ TS $\sim$ C2      | and increment | C1 |

|         | m | + 2: BNO m              | and increment | C2 |

The electrical details of the indirect address feature are rather simple. Of the six bits specified for the order code, four are used for the fourteen orders thus far discussed. One more is reserved for the "extended operations" to be discussed shortly, The remaining one is for indirect addressed orders. I's effect- in brief, is to precede the control. pulse sequence normal to the order in question by another of four pulses in length which replaces the contents of D and S by the word. obtained from storage in the address specified by the order, The control pulse sequence for this purpose 6s given in Table 2-11 It is necessary in addition to cause the control sequence shift register to start at a position four steps preceding the beginning point for normal orders. This is accomplished through a relatively simple wiring in the sequence generator core rope, The whole cost of providing this facility is perhaps seven or eight transistors and a few I-ores. etd

### TABLE 2-11

|    | Indire | ct | Add    | ressin | g     |         |

|----|--------|----|--------|--------|-------|---------|

| 1  | CL     | S, | CL D   | )      |       |         |

| 2  | (no    | ac | tion)  |        |       |         |

| 3  | CL     | E, | WB,    | W1S    | d     |         |

| 4  | CL     | В, | WE,    | WS,    | WD    |         |

| No | ormal  | op | eratio | n of   | order | follows |

The so- called "extended operations <sup>11</sup> form an inexpensive storage-saving device by providing means for a one-word entry into a number of subroutines. As an example, multiplication exists in most variations of the computer only as a subroutine. To multiply C(X) by C(Y), the following orders might be written:

CA X TS to standard location CA Y TC to multiply routine

The extended operation version of this would replace the last three orders by one order. The problem is that four items of information are required: (1) address X or its contents, (2) address Y or its contents, (3) the address to go to after multiplication is complete, and (4) the fact that multiplication is desired; i. e. I an address associated with this particular subroutine. A single order does not have sufficient digit positions to carry all of these data; two, however, can do so by relying on the Z and Q registers to handle the next address, provided that only a few bits are required for item 4.

The action, in brief, is that one bit in the order code causes a special control pulse sequence to become active, which holds C(Z) in Q as in the TC order, preserves the complement of the original order in R2cJ and transfers control to a specific address (e. g. J address 128) which is generated electrically. There, a short standard program is initiated which files these

data away, including the original order, and finally transfers control to an address derived from the order code portion of the original instruction. The whole operation requires approximately 50 pulse times whereas the three-order version cited previously requires about half of that. Thirty-two of these extended operations are available. By and large they will be used for a variety of instructions found in most computers which are accomplished in ours by means of subroutines, There is some appeal, though, in planning a computer for geometric computations required, say, in space navigation, which may have "vector add" as a computer instruction.

## D. Addition and Multiplication

The selection of an order code is dependent on the particular use to which the computer is put. The choices are, as usual, between speed and sophistication on the one hand and simplicity and reduced equipment on the other. Of particular interest in the present case is the method for addition, in which no use is made of an adder. Instead, in the representative computer, addition is carried out by a repetitive logical process within a loop in the sequence generator, in which all operations are conducted by the processes and registers already discussed.