# Modular Electronics Learning (ModEL) PROJECT

## SPICE Modeling of Resistor Circuits

© 2016-2024 By Tony R. Kuphaldt – under the terms and conditions of the Creative Commons Attribution 4.0 International Public License

#### Last update = 6 September 2024

This is a copyrighted work, but licensed under the Creative Commons Attribution 4.0 International Public License. A copy of this license is found in the last Appendix of this document. Alternatively, you may visit http://creativecommons.org/licenses/by/4.0/ or send a letter to Creative Commons: 171 Second Street, Suite 300, San Francisco, California, 94105, USA. The terms and conditions of this license allow for free copying, distribution, and/or modification of all licensed works by the general public.

# Contents

| 1 | Intr                   | Introduction |                                                     |    |  |  |  |  |  |

|---|------------------------|--------------|-----------------------------------------------------|----|--|--|--|--|--|

|   | 1.1                    |              | nmendations for students                            | 3  |  |  |  |  |  |

|   | 1.2                    |              | enging concepts related to SPICE circuit simulation | 5  |  |  |  |  |  |

|   | 1.3                    | Recon        | nmendations for instructors                         | 6  |  |  |  |  |  |

| 2 | $\mathbf{W}\mathbf{h}$ | at is S      | PICE?                                               | 7  |  |  |  |  |  |

| 3 | Using SPICE            |              |                                                     |    |  |  |  |  |  |

|   | 3.1                    | Summ         | nary of steps                                       | 11 |  |  |  |  |  |

|   | 3.2                    | Demo         | nstration on Microsoft Windows                      | 12 |  |  |  |  |  |

|   |                        | 3.2.1        | Invoking a text editor                              | 12 |  |  |  |  |  |

|   |                        | 3.2.2        | Saving the deck                                     | 13 |  |  |  |  |  |

|   |                        | 3.2.3        | Invoking SPICE                                      | 15 |  |  |  |  |  |

|   |                        | 3.2.4        | Viewing the SPICE analysis                          | 16 |  |  |  |  |  |

|   | 3.3                    | Demo         | nstration on Linux or CygWin                        | 17 |  |  |  |  |  |

|   |                        | 3.3.1        | Invoking a text editor                              | 17 |  |  |  |  |  |

|   |                        | 3.3.2        | Saving the deck                                     | 18 |  |  |  |  |  |

|   |                        | 3.3.3        | Invoking SPICE                                      | 19 |  |  |  |  |  |

|   |                        | 3.3.4        | Viewing the SPICE analysis                          | 20 |  |  |  |  |  |

|   | 3.4                    | Demo         | nstration of NGSPICE interactive mode               | 21 |  |  |  |  |  |

|   |                        | 3.4.1        | Creating the netlist                                | 22 |  |  |  |  |  |

|   |                        | 3.4.2        | Starting NGSPICE                                    | 22 |  |  |  |  |  |

|   |                        | 3.4.3        | Verifying the loaded netlist                        | 23 |  |  |  |  |  |

|   |                        | 3.4.4        | Running the analysis                                | 23 |  |  |  |  |  |

|   |                        | 3.4.5        | Printing a voltage                                  | 24 |  |  |  |  |  |

|   |                        | 3.4.6        | Plotting graphs using NGSPICE                       | 25 |  |  |  |  |  |

|   |                        | 3.4.7        | Issuing multiple commands in a single line          | 26 |  |  |  |  |  |

|   | 3.5                    | Idiosy       | ncrasies of SPICE                                   | 27 |  |  |  |  |  |

|   |                        | 3.5.1        | Beginning and ending cards                          | 27 |  |  |  |  |  |

|   |                        | 3.5.2        | Node zero                                           | 27 |  |  |  |  |  |

|   |                        | 3.5.3        | Current measurement                                 | 27 |  |  |  |  |  |

|   |                        | 3.5.4        | Open and short circuits                             | 28 |  |  |  |  |  |

|   |                        | 3.5.5        | Multiple sources                                    | 29 |  |  |  |  |  |

|   |                        | 3.5.6        | Multiple inductors/capacitors                       | 30 |  |  |  |  |  |

| 4 | SPI  | CE component descriptions 31                                         |

|---|------|----------------------------------------------------------------------|

|   | 4.1  | Independent voltage sources                                          |

|   |      | 4.1.1 Example: DC source                                             |

|   |      | 4.1.2 Example: "Dummy" source                                        |

|   |      | 4.1.3 Example: AC source                                             |

|   |      | 4.1.4 Example: Sinusoidal source                                     |

|   |      | 4.1.5 Example: Pulse source                                          |

|   | 4.2  | Independent current sources                                          |

|   |      | 4.2.1 Example: DC source                                             |

|   |      | 4.2.2 Example: AC source                                             |

|   | 4.3  | Resistors                                                            |

|   |      | 4.3.1 Example                                                        |

|   | 4.4  | Capacitors                                                           |

|   |      | 4.4.1 Example: Capacitor with initial charge                         |

|   |      | 4.4.2 Example: Uncharged capacitor                                   |

|   | 4.5  | Inductors                                                            |

|   |      | 4.5.1 Example: Inductor with initial charge                          |

|   |      | 4.5.2 Example: Uncharged inductor                                    |

|   | 4.6  | Transformers                                                         |

|   | 2.0  | 4.6.1 Example: 2:1 ratio step-down transformer                       |

|   | 4.7  | Transmission lines                                                   |

|   | 2    | 4.7.1 Example: 50-Ohm transmission line with 10 nanosecond delay     |

|   |      | 4.7.2 Example: half-wavelength (at 35 MHz) 300-Ohm transmission line |

|   | 4.8  | Linear dependent sources                                             |

|   | 2.0  | 4.8.1 Example: voltage-controlled voltage source                     |

|   |      | 4.8.2 Example: voltage-controlled current source                     |

|   | 4.9  | Nonlinear dependent sources                                          |

|   | 1.0  | 4.9.1 Example: multiplier                                            |

|   | 4 10 | Diodes                                                               |

|   | 4.10 | 4.10.1 Example: Generic diode                                        |

|   |      | 4.10.2 Example: 1N4001                                               |

|   | 111  | Bipolar Junction Transistors (BJTs)                                  |

|   | 4.11 | 4.11.1 Example: Generic NPN transistor                               |

|   |      | 4.11.2 Example: 2N2907                                               |

|   | 4 19 | Junction Field-Effect Transistors (JFETs)                            |

|   | 4.12 | 4.12.1 Example: Generic N-channel JFET                               |

|   | 112  | Metal-Oxide Field-Effect Transistors (MOSFETs)                       |

|   | 4.10 | 4.13.1 Example: Generic N-channel depletion-type MOSFET              |

|   |      |                                                                      |

|   |      | ı vı                                                                 |

|   |      | 4.13.3 Example: Generic P-channel depletion-type MOSFET              |

|   | 111  | 4.13.4 Example: Generic P-channel enhancement-type MOSFET            |

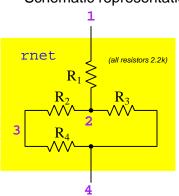

|   | 4.14 | Subcircuits                                                          |

|   |      | 4.14.1 Example: resistor subnetwork                                  |

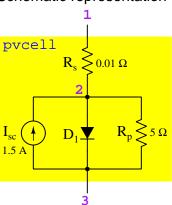

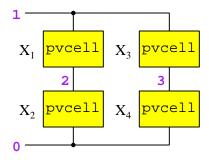

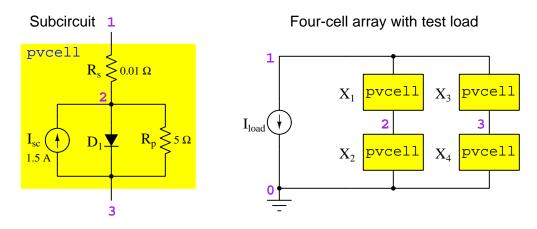

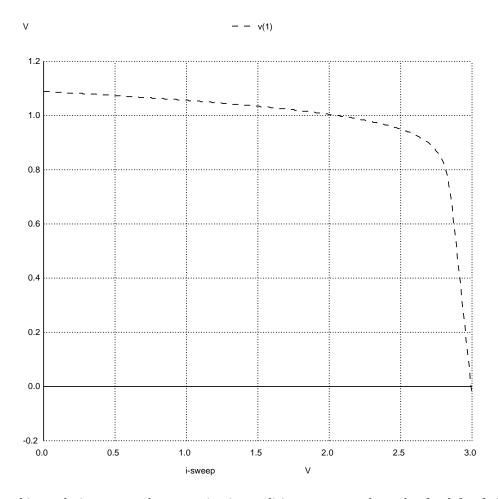

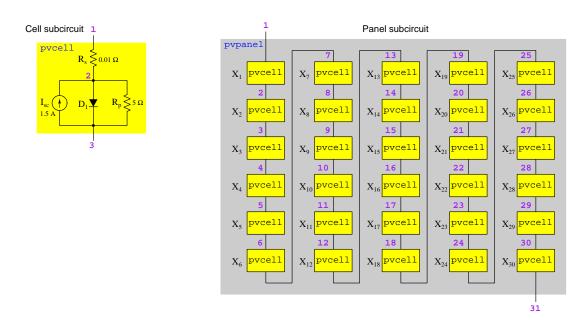

|   |      | 4.14.2 Example: solar cell array                                     |

| <b>5</b> | SPICE analysis descriptions |                                                                            |  |  |  |  |  |

|----------|-----------------------------|----------------------------------------------------------------------------|--|--|--|--|--|

|          | 5.1                         | DC voltage/current "sweep" analysis                                        |  |  |  |  |  |

|          |                             | 5.1.1 Example: sweep of voltage source                                     |  |  |  |  |  |

|          |                             | 5.1.2 Example: sweep of voltage and current sources 6                      |  |  |  |  |  |

|          | 5.2                         | AC frequency "sweep" analysis                                              |  |  |  |  |  |

|          |                             | 5.2.1 Example: linear frequency sweep                                      |  |  |  |  |  |

|          |                             | 5.2.2 Example: decade logarithmic frequency sweep                          |  |  |  |  |  |

|          |                             | 5.2.3 Example: octave logarithmic frequency sweep                          |  |  |  |  |  |

|          | 5.3                         | Transient analysis                                                         |  |  |  |  |  |

|          |                             | 5.3.1 Example: using initial conditions, beginning at time $t = 0 \dots 6$ |  |  |  |  |  |

|          |                             | 5.3.2 Example: using initial conditions, beginning at non-zero time 6      |  |  |  |  |  |

|          | 5.4                         | Fourier analysis                                                           |  |  |  |  |  |

|          |                             | 5.4.1 Example: analysis of 60 Hz waveform                                  |  |  |  |  |  |

|          | 5.5                         | Display option: print                                                      |  |  |  |  |  |

|          |                             | 5.5.1 Example: printing a DC analysis                                      |  |  |  |  |  |

|          |                             | 5.5.2 Example: printing an AC analysis                                     |  |  |  |  |  |

|          | 5.6                         | Display option: plot                                                       |  |  |  |  |  |

|          |                             | 5.6.1 Example: plotting a DC analysis                                      |  |  |  |  |  |

|          |                             | 5.6.2 Example: plotting an AC analysis                                     |  |  |  |  |  |

|          |                             | 5.6.3 Example: logarithmically plotting an AC analysis 6                   |  |  |  |  |  |

|          |                             | 5.6.4 Example: plotting a transient analysis                               |  |  |  |  |  |

|          |                             | 5.6.5 Example: plotting parametric functions                               |  |  |  |  |  |

|          | 5.7                         | Display option: width                                                      |  |  |  |  |  |

|          |                             | 5.7.1 Example                                                              |  |  |  |  |  |

| 6        | Prin                        | mitive circuit examples 6                                                  |  |  |  |  |  |

|          | 6.1                         | DC voltage source with .op analysis                                        |  |  |  |  |  |

|          | 6.2                         | DC voltage source with single-point .dc sweep analysis                     |  |  |  |  |  |

|          | 6.3                         | DC current source with single-point .dc sweep analysis                     |  |  |  |  |  |

|          | 6.4                         | DC voltage source with multi-point .dc sweep analysis                      |  |  |  |  |  |

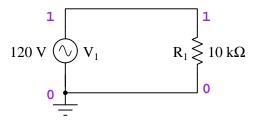

|          | 6.5                         | AC voltage source with single-point .ac sweep analysis                     |  |  |  |  |  |

|          | 6.6                         | AC voltage source with multi-point .ac sweep analysis                      |  |  |  |  |  |

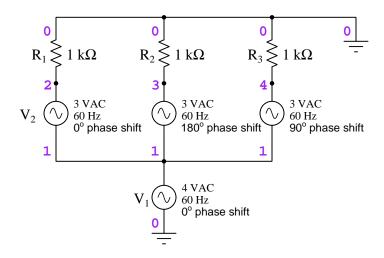

|          | 6.7                         | Additive AC voltage sources with single-point .ac sweep analysis           |  |  |  |  |  |

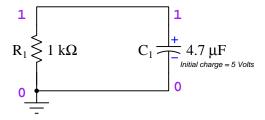

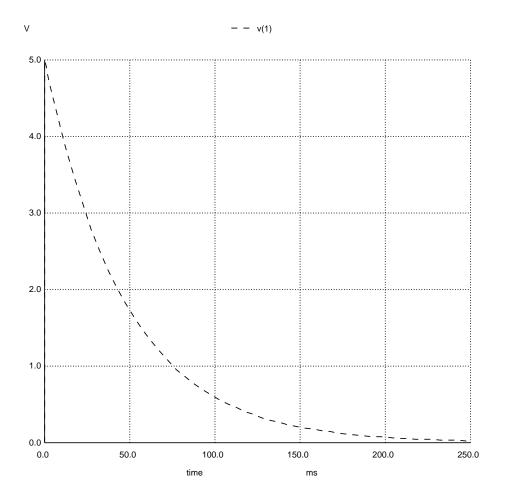

|          | 6.8                         | Transient analysis of discharging RC circuit                               |  |  |  |  |  |

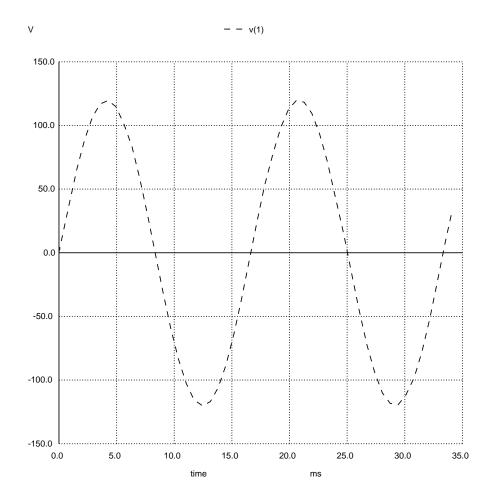

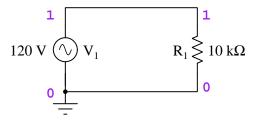

|          | 6.9                         | Transient analysis of a steady sinusoidal voltage source                   |  |  |  |  |  |

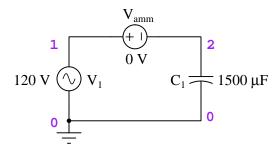

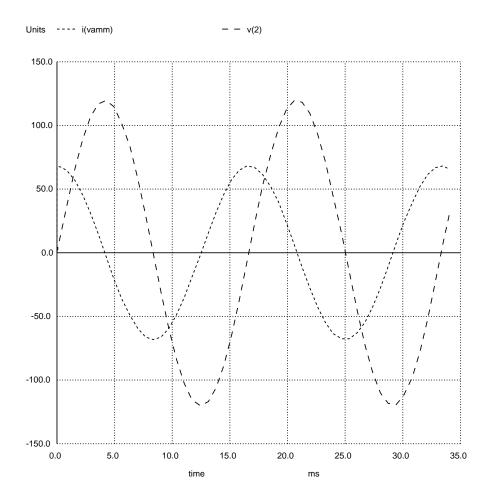

|          | 6.10                        | Transient analysis of a sinusoidal capacitive circuit                      |  |  |  |  |  |

|          |                             | Transient analysis of a damped, offset sinusoidal voltage source           |  |  |  |  |  |

|          |                             | Additive AC voltage sources with transient analysis                        |  |  |  |  |  |

|          |                             | Solar cell array simulation                                                |  |  |  |  |  |

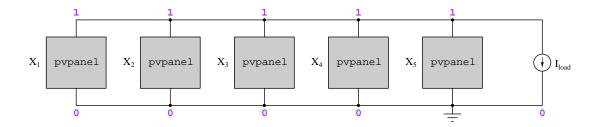

|          |                             | Solar panel array simulation                                               |  |  |  |  |  |

| 7        | Gal                         | lery 11                                                                    |  |  |  |  |  |

|          | 7.1                         | Using gallery examples for practice                                        |  |  |  |  |  |

|          | 7.2                         | Series resistor circuits                                                   |  |  |  |  |  |

|          |                             | 7.2.1 One DC current source, three resistors                               |  |  |  |  |  |

|          |                             | 7.2.2 One DC voltage source, three resistors                               |  |  |  |  |  |

|                            |            | 7.2.3   | One DC voltage source, four resistors    | 118 |  |  |  |  |  |

|----------------------------|------------|---------|------------------------------------------|-----|--|--|--|--|--|

|                            |            | 7.2.4   | One DC current source, five resistors    | 119 |  |  |  |  |  |

|                            |            | 7.2.5   | One DC voltage source, ten resistors     | 120 |  |  |  |  |  |

|                            |            | 7.2.6   | Three DC voltage sources, four resistors | 122 |  |  |  |  |  |

|                            | 7.3        | Paralle | el resistor circuits                     | 123 |  |  |  |  |  |

|                            |            | 7.3.1   | One DC voltage source, three resistors   | 124 |  |  |  |  |  |

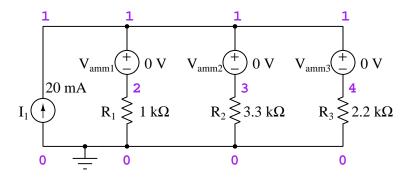

|                            |            | 7.3.2   | One DC current source, three resistors   | 125 |  |  |  |  |  |

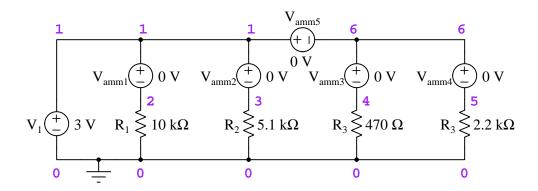

|                            |            | 7.3.3   | One DC voltage source, four resistors    | 126 |  |  |  |  |  |

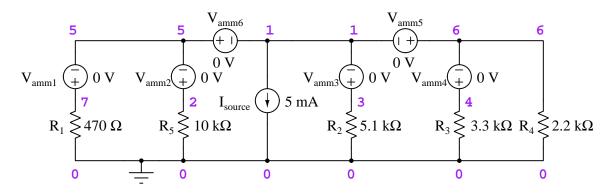

|                            |            | 7.3.4   | One DC current source, five resistors    | 128 |  |  |  |  |  |

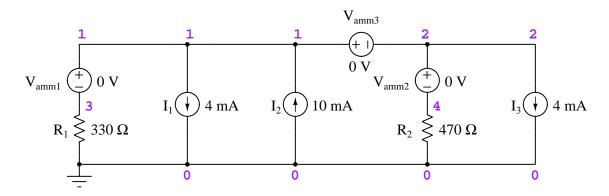

|                            |            | 7.3.5   | Three DC current sources, two resistors  | 130 |  |  |  |  |  |

|                            | 7.4        | Series- | parallel resistor circuits               | 131 |  |  |  |  |  |

|                            |            | 7.4.1   | One DC voltage source, six resistors     | 132 |  |  |  |  |  |

|                            |            | 7.4.2   | One DC current source, six resistors     | 134 |  |  |  |  |  |

|                            | 7.5        | _       | e multi-source resistor circuits         | 136 |  |  |  |  |  |

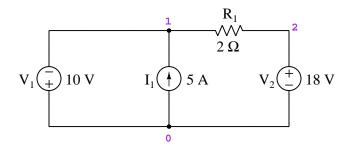

|                            |            | 7.5.1   | One voltage, one current                 | 137 |  |  |  |  |  |

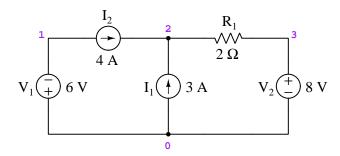

|                            |            | 7.5.2   | Two currents, one voltage                | 138 |  |  |  |  |  |

|                            |            | 7.5.3   | Two voltages, one current                | 139 |  |  |  |  |  |

|                            | <b>-</b> 0 | 7.5.4   | Two currents, two voltages               | 140 |  |  |  |  |  |

|                            | 7.6        | Resisti | ve bridge circuits                       | 141 |  |  |  |  |  |

| A                          | Pro        | blem-S  | Solving Strategies                       | 143 |  |  |  |  |  |

| В                          | Inst       | ructio  | nal philosophy                           | 145 |  |  |  |  |  |

|                            | B.1        |         | orinciples of learning                   | 146 |  |  |  |  |  |

|                            |            |         | n strategies for instructors             | 147 |  |  |  |  |  |

|                            |            |         | n strategies for students                | 149 |  |  |  |  |  |

|                            |            |         | of these learning modules                | 150 |  |  |  |  |  |

|                            |            | ls used |                                          | 153 |  |  |  |  |  |

| U                          | 100        | is used |                                          | 199 |  |  |  |  |  |

| D Creative Commons License |            |         |                                          |     |  |  |  |  |  |

| E References               |            |         |                                          |     |  |  |  |  |  |

| F Version history          |            |         |                                          |     |  |  |  |  |  |

| Index                      |            |         |                                          |     |  |  |  |  |  |

# Chapter 1

## Introduction

## 1.1 Recommendations for students

Many computer-based circuit simulation software applications exist today, most of these based on graphical "schematic capture" where one describes the circuit to the computer by drawing a diagram of it. SPICE, however, is a throwback to a much earlier era of computing when people interacted with the machine through text (and in some cases, punched paper cards!). This means SPICE is a type of programming language where you describe the circuit to be simulated by written rather than graphic means. The fact that even the most modern circuit simulation packages often use SPICE-compliant or SPICE-like instructions "behind the scenes" to specify details of circuit analysis is one reason to learn SPICE in the 21st century, but another reason is that it is a relatively simple form of coding, and all students of electronics are well-served by learning to code in multiple languages. More specifically, SPICE is what may be called a concurrent programming language whereby the instructions you write using plain-text characters are not executed in sequential order but rather serve to describe entities of a circuit and therefore may appear in any order! In this way SPICE actually shares more in common with hardware-oriented languages like Verilog or VHDL than with classic procedural languages such as assembly or C.

Important concepts related to SPICE include **netlists**, **text editing**, **cards**, **decks**, **nodes**, **dependent sources** versus **independent sources**, **passive sign convention**, component **models**, **subcircuits**, , , , , and .

One of the beautiful aspects of learning a programming language is the natural means by which you have to learn by experimentation. All you need is access to a computer with the proper software installed, and you can not only run example programs offered to you, but also modify those programs and/or even create your own to test your own growing understanding of how to "speak" the language. It is akin to learning to speak a human language and then being able to immediately apply it in conversation with someone else fluent in it as a way to test and hone your knowledge. Therefore, no reader of this module should be satisfied by merely reading what is written in these pages – instead try running SPICE on your own to see firsthand how it functions!

Here are some good questions to ask of yourself while studying this subject:

- How does a SPICE netlist instruct the computer to know which component terminals connect to which?

- How could you identify series versus parallel component connections by inspection of a netlist?

- What are some essential elements of any SPICE netlist?

- How may open-circuit conditions be simulated in SPICE without creating errors?

- How may short-circuit conditions be simulated in SPICE without creating errors?

- Where must we be careful when inserting multiple voltage sources into a netlist?

- Where must we be careful when inserting multiple current sources into a netlist?

- Where must we be careful when inserting multiple inductors into a netlist?

- Where must we be careful when inserting multiple capacitors into a netlist?

- Which node is always Ground in a netlist?

- How are voltage measurement points specified in a SPICE analysis?

- What are some different ways in which we may measure (or infer) current in a SPICE circuit simulation?

- What is a SPICE *subcircuit* and where might one be useful?

- How might you alter one of the example simulations shown in the text, and then determine the behavior of that altered circuit?

- Devise your own question based on the text, suitable for posing to someone encountering this subject for the first time.

The following active-reading strategies are advised for this module's tutorial(s);

- Limiting cases seeing opens and shorts as being limiting cases of resistance provides a means of simulating the same in a SPICE netlist, extremely large resistances simulating opens and extremely small resistances simulating shorts.

- Experiment using simulations SPICE is a programming language, and learning to program a computer is never a spectator sport. Run SPICE for yourself to see how it works!

## 1.2 Challenging concepts related to SPICE circuit simulation

The following list cites concepts related to this module's topic that are easily misunderstood, along with suggestions for properly understanding them:

- Voltage as a relative quantity this is arguably one of the most difficult concepts students first encounter when studying electricity: understanding that voltage is a difference in energy levels between two locations, and not something that can exist at any single point. In this respect, voltage is similar to distance which is always something existing between two specified points.

- Voltage versus Current these are two completely distinct things, each capable of existing without the other. *Voltage* is the amount of potential energy lost or gained by electric charge carriers as they move from one place to another, whereas *current* is the actual motion of electric charge carriers.

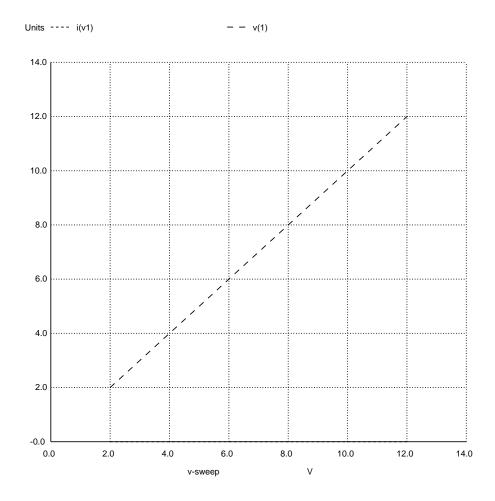

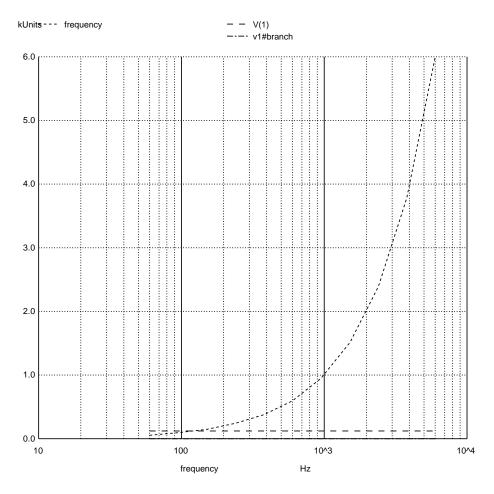

- Test sweeps SPICE excels at performing "sweep" analyses, which refers to the incrementing or decrementing of some circuit parameter, re-running the entire analysis with each new value of this parameter. Sweeping is essential for building up a graph or table of values showing trends related to that parameter.

The Gallery chapter contains many example SPICE netlists complete with analyses, which are excellent both for becoming familiar with operating SPICE (i.e. copying and pasting those given netlists in your text editor and running the simulations yourself) as well as starting points (i.e. templates) for creating your own circuit simulations.

## 1.3 Recommendations for instructors

This section lists realistic student learning outcomes supported by the content of the module as well as suggested means of assessing (measuring) student learning. The outcomes state what learners should be able to do, and the assessments are specific challenges to prove students have learned.

• Outcome – Demonstrate effective technical reading and writing

<u>Assessment</u> – Students present their outlines of this module's instructional chapters (e.g. What is SPICE?, Using SPICE, Primitive circuit examples, Gallery, etc.) ideally as an entry to a larger Journal document chronicling their learning. These outlines should exhibit good-faith effort at summarizing major concepts explained in the text.

<u>Assessment</u> – Students show how quantitative results were obtained by SPICE in the given examples, performing some of those analyses manually to compare your results with the simulations'.

• Outcome – Design a circuit, analyze it, and write a corresponding SPICE netlist

<u>Assessment</u> – Sketch a schematic diagram of a circuit and analyze all circuit parameters using the principles and equations you have learned so far.

<u>Assessment</u> – Write and run a netlist for that circuit to compare your hand-calculated results against the computer's.

#### • Outcome – Independent research

<u>Assessment</u> – Identify some circuit simulators based on schematic capture rather than typed code. Some simulators are even web-based which means you may use them by navigating an internet browser application to the appropriate website (e.g. EveryCircuit).

## Chapter 2

# What is SPICE?

SPICE is a general-purpose computer simulator for electronic circuits, with several "freeware" versions available for academic use. Although its text-based user interface may seem clumsy and archaic at first, it is quite powerful, and also neatly side-steps the many problems students tend to experience with graphic-entry ("WYSIWYG")<sup>1</sup> circuit simulators.

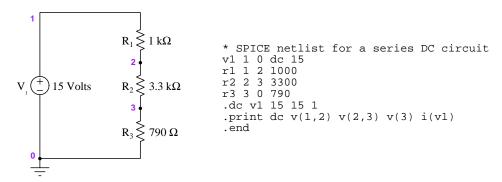

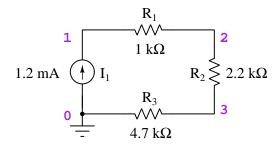

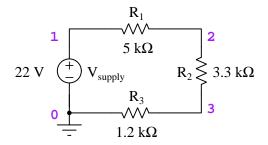

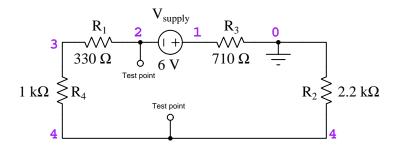

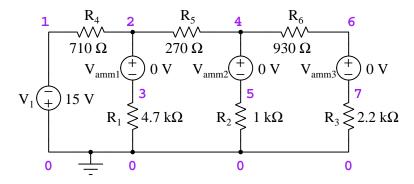

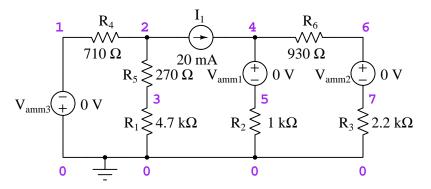

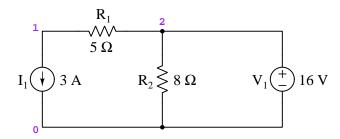

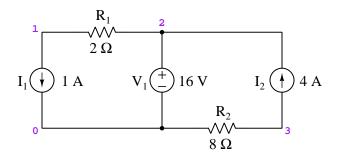

Circuits are described to SPICE in the form of a *netlist*, which is a text-based code listing of each component within the circuit, the "nodes" connecting them to each other, and the types of analyses requested of SPICE to perform on that circuit. A simple three-resistor DC circuit is shown in schematic form below, along with the netlist you would write and input to SPICE instructing it to analyze this circuit for a single source voltage value of 15 Volts and displaying the voltage drop across each resistor as well as the current through the voltage source:

The purpose of this document is to give a general introduction to the use of SPICE, and also to showcase a "gallery" of examples where SPICE is used to perform analyses on circuits containing semiconductor components. This gallery will not only help new users of SPICE learn how to format netlists and interpret analyses, but they also serve as an extensive bank of practice problems for new students of electricity and electronics to use as they build and sharpen their circuit analysis skills.

This last point deserves some elaboration. The study of electricity and electronics, like all scientific studies, is aided by the solution of practice problems. Problem-solving is a skill like any

<sup>&</sup>lt;sup>1</sup> "WYSIWYG" is an acronym meaning What You See Is What You Get.

other, and practice helps to build an arsenal of tools useful to any new problems you may encounter. Having answers provided for these problems allows students to check their work and to self-identify any misconceptions or bad problem-solving habits.

Traditional textbooks provide banks of practice problems for students to solve, and while these are useful, the availability of computer simulation software take this concept one enormous step further. Not only may the sample simulations given in this learning module serve as practice problems for students, but they will also serve as templates for creating one's own practice problems, so you will never be wanting for more practice opportunities. Like all computer simulations, SPICE rigorously applies known laws and principles of physics to predict how specific systems will behave, and as such it never makes mistakes<sup>2</sup>.

SPICE has played a pivotal role in my own self-education on the topic of circuits, being an excellent tool to check my own analytical skills and to explore the properties of certain devices (e.g. transistors, transmission lines, transformers) with relative ease. The ultimate goal of any scientific education is to equip the student with mental tools to solve problems and to continue their own learning. SPICE is a software tool that can aid in the development of these mental tools, and should be used as such.

<sup>&</sup>lt;sup>2</sup>Some simulations can and do miss certain details if they are not set up properly, but this is not the same kind of error as a human is prone to committing, and it is precisely this difference between computers and humans that makes computer simulations useful learning tools. Simply put, the computer will not repeat *your* mistakes.

## Chapter 3

# Using SPICE

SPICE is computer software designed to simulate the behavior of electric circuits. It was developed in the early days of digital computing when the dominant user interface was the *command prompt*, and the most common user file format was plain "ASCII" text. Graphic, mouse- or touchscreen-driven interfaces simply did not exist at that time except for prototype systems or highly specialized applications. Most general-purpose computing of that era occurred through the use of a keyboard and a monochrome text-based monitor, or worse yet in the form of punched paper cards and teletyped output.

This is why SPICE usage seems to resemble text-based code programming. The user (that means you) enters a description of the circuit to be analyzed and the analysis/display methods preferred by means of typed text, then the SPICE program is run and the output is viewed again in text form.

This may all seem terribly anachronistic in the 21st century, but there are some decided advantages to using SPICE with this legacy interface:

- These legacy versions of SPICE are free to use. No license fees, nothing.

- The relatively small (by modern standards) SPICE software runs very fast on modern computers.

- Circuits that are challenging to graphically draw are easy to "code"

- Errors resulting from the computer's incorrect interpretation of a diagram are eliminated

- Learning to use SPICE in this manner is an excellent orientation to simple programming

The first step in setting up SPICE to analyze a circuit is to describe that circuit using SPICE's own language, and to type this description into a plain-text file on your computer. This file is often referred to as a *deck*, with each line of text in that file called a *card*. Taken together, those lines of text (a.k.a. *cards*) comprise a *netlist* describing the circuit and the intended analysis for SPICE. The

<sup>&</sup>lt;sup>1</sup>I have struggled multiple times to get a WYSIWYG circuit analyzer program to simply analyze what I have drawn, due to "hidden" wire connections, or intended wire connections that don't exist – all "bugs" in the software stemming from the non-trivial challenge of getting a computer to recognize and correctly interpret a hand-made diagram. SPICE, with its "netlist" input and clear node-labeling protocol, neatly eliminates this whole problem.

anachronistic terms "card" and "deck" harken back to the days of punched-card input for computer systems, where each separate instruction for SPICE was a series of punched holes on its own paper card, the collection of cards representing one circuit being a "deck of cards" that would be fed into the card reader one at a time<sup>2</sup>.

Once you have typed the netlist and saved it as a text file (a.k.a. deck) to your computer, you are ready to run a SPICE analysis on it. This is done by typing the word spice on a command-line interface<sup>3</sup> followed by a less-than symbol (<) and then followed by the name of the text file "deck", and finally terminated by pressing the Enter key. Here is an example, showing a screenshot of a SPICE analysis about to happen on a "deck" file named test.cir just prior to pressing the Enter key:

After entering this command, SPICE performs its analysis and by default dumps a report as plain text to the same command-line terminal. If you desire to save SPICE's text output to another plain-text file for posterity, or to be able to paste that analysis into another document, you may "redirect" SPICE to send its plain-text analysis to another file of your choosing by using the greater-than symbol (>) in the command. Here is an example showing how to instruct SPICE to read the contents of test.cir and place all the analysis text into another file named test.out:

spice < test.cir > test.out

<sup>&</sup>lt;sup>2</sup>Interestingly, legacy versions of SPICE do not care what order these "cards" appear in the "deck" with the exception of the first line (the Title) and the last line (the .end) statement.

<sup>&</sup>lt;sup>3</sup>Microsoft Windows operating systems provide a general-purpose command line interface terminal named cmd. Unix-based systems such as Apple's OS X and Linux typically offer a variety of terminal programs suitable for this purpose.

## 3.1 Summary of steps

To summarize, using SPICE in this legacy format requires the use of a *text editor* program (such as "Notepad" on Microsoft Windows operating systems) to write the netlist, and a command-line interface on your computer to invoke SPICE to perform its analysis. The sequence of steps may be listed:

- 1. Invoke a text editor program and type the netlist (instructions) describing the circuit and the type of analysis you wish SPICE to perform

- 2. Save this netlist as a plain-text file to your computer

- 3. Type spice  $< deck_filename$  on the command-line interface and then press Enter

- 4. View the analysis in the command-line interface

Most of SPICE's "learning curve" is in becoming familiar with the syntax of the netlist: exactly which letters, numbers, and sequences must be entered in order to properly describe the circuit and the type(s) of analysis desired. A few cardinal rules must be obeyed when creating or editing netlists:

- The first line (card) of the netlist is the Title. It cannot be omitted.

- The last line (card) of the netlist is the .end command. It cannot be omitted.

- Each and every unique connection point in the circuit must be assigned a number called a *node*. This is how you describe the "shape" of the circuit to SPICE: by describing which nodes each component connects to. Components sharing common node numbers are electrically common to each other; components with differing node numbers are electrically distinct from each other. There *must* be a node 0, and this is the "Ground" node of the circuit.

## 3.2 Demonstration on Microsoft Windows

Here I will demonstrate this four-step process as a series of screenshots from a computer running SPICE version 2G6 on the Microsoft Windows version 7 operating system.

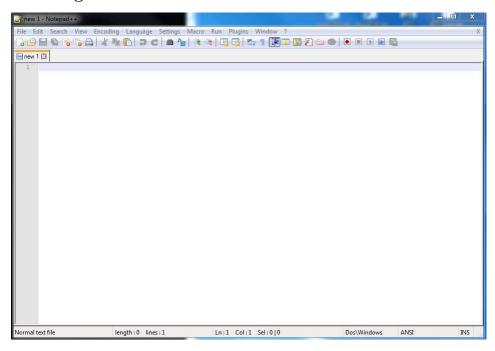

## 3.2.1 Invoking a text editor

Here, the screenshot shows an empty file, ready for me to type text. *Text editors* are similar to word processors except they lack provision for neatly formatting the text (e.g. no font selections, no paragraph formatting, etc.). Their sole purpose is to facilitate the creation and editing of plain-text files.

Text editors are the go-to application for practically all text-based computer programming. *Many* different text editors exist, each with their own features, and computer programmers tend to develop a fondness for one particular editor that best suits their programming needs. A "stock" text editor comes with every version of Microsoft Windows called notepad, but this editor is extremely limited in its capabilities, and I do not recommend it. The editor shown here (notepad++) is *vastly* superior and highly recommended.

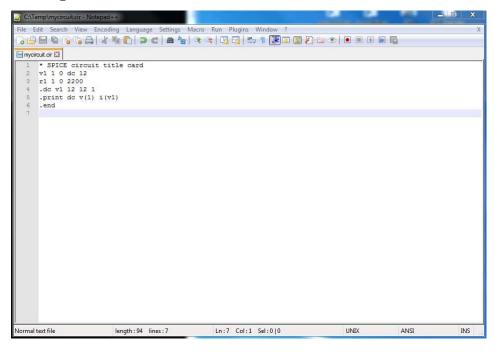

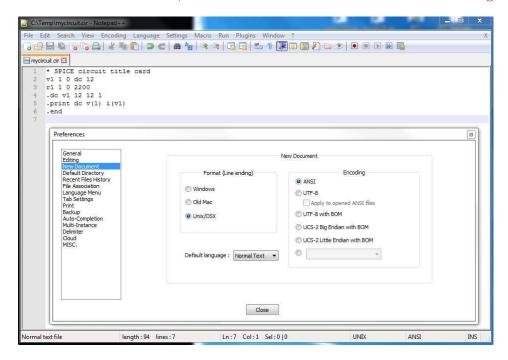

## 3.2.2 Saving the deck

Here, I have chosen the filename mycircuit.cir for the deck. Note that you do not have to end every deck filename with the suffix ".cir" – this is simply my personal choice. Any filename consistent with the naming conventions of your computer's filesystem and containing no space characters is permissible. We avoid space characters because command-line interfaces typically interpret spaces as delimiting characters designed to separate commands and filenames from each other. If you must have a "space" in your filename, use an underscore character or a dash (\_ or \_). For example, my-circuit is acceptable, but my circuit is not.

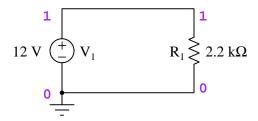

Here is a line-by-line (a.k.a. card-by-card) interpretation of the netlist:

```

* SPICE circuit title card This is the arbitrary "title" line

v1 1 0 dc 12 Defines a 12 Volt DC voltage source named "v1" between nodes 1 and 0

r1 1 0 2200 Defines a 2200 Ohm resistor between nodes 1 and 0

.dc v1 12 12 1 Requests a DC "sweep" analysis from 12 Volts to 12 Volts on source "v1"

.print dc v(1) i(v1) Measures the voltage at node 1 and current through source "v1"

.end Tells SPICE to stop

```

Note how components are "connected" to each other in the netlist by common node (connection-point) numbers. This is how SPICE is able to "picture" circuits without the use of graphical images. Each electrically distinct point in a circuit is given a unique number, and different components specified by the points they're connected to.

An idiosyncrasy of SPICE version 2G6 is that it must receive its "deck" file in Unix text format rather than Windows text format. Thankfully, notepad++ provides a means to select which text format the deck file will be written in, as shown in this screenshot of the "Preferences" dialog window:

## 3.2.3 Invoking SPICE

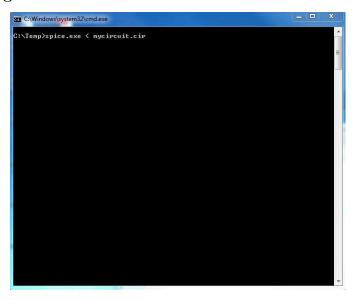

This screenshot shows the command-line interface terminal (not the text editor), with the command ready to enter. This terminal may be access on any Windows operating system by invoking the cmd command.

Note that the exact command being entered here is spice.exe < mycircuit.cir because the SPICE executable file installed on this computer is named spice.exe rather than just spice.

## 3.2.4 Viewing the SPICE analysis

As you can see, SPICE is a very "chatty" program that displays a fair amount of extraneous text on the screen following an analysis. Ignoring all the headings and labels, you can see in this display a reiteration of the original netlist (deck) followed by the requested measurements of v(1) (i.e. voltage between node 1 and ground, which is node 0) and i(v1) (current through source v1).

This concludes a *very* brief orientation on using SPICE. For more information, I refer you to the following sections on SPICE component descriptions and analysis descriptions, as well as to the "Gallery" chapter which shows you tested SPICE netlists and output results so you may learn by example.

## 3.3 Demonstration on Linux or CygWin

Now, I will show you this same four-step process using SPICE version 2G6 running under the Linux operating system. The steps shown here are virtually identical within the "CygWin" emulator which adds a Unix-like command line environment to any Microsoft Windows operating system.

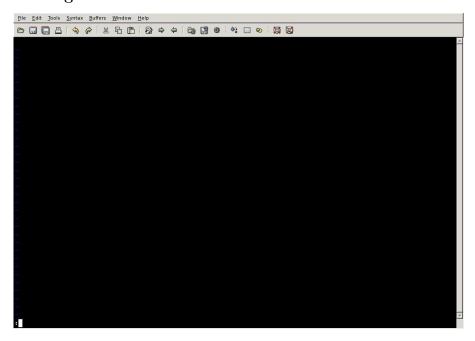

## 3.3.1 Invoking a text editor

Here, the screenshot shows an empty file, ready for me to type text. *Text editors* are similar to word processors except they lack provision for neatly formatting the text (e.g. no font selections, no paragraph formatting, etc.). Their sole purpose is to facilitate the creation and editing of plain-text files.

Text editors are the go-to application for practically all text-based computer programming. *Many* different text editors exist, each with their own features, and computer programmers tend to develop a fondness for one particular editor that best suits their programming needs. I personally prefer gvim (or vim in the CygWin emulator) and loathe Microsoft notepad, but text editors tend to be a highly personal choice.

## 3.3.2 Saving the deck

```

File Edit Jools Syntax Buffers Window Help

SPICE circuit title card

v1 1 0 da 12

r1 1 0 2200

de v1 12 12 1

.print de v(1) i(v1)

.ond

"mycircuit.cir" [New] 6L, 93c written

1,1 All

```

Here, I have chosen the filename mycircuit.cir for the deck. Note that you do not have to end every deck filename with the suffix ".cir" – this is simply my personal choice. Any filename consistent with the naming conventions of your computer's filesystem and containing no space characters is permissible. We avoid space characters because command-line interfaces typically interpret spaces as delimiting characters designed to separate commands and filenames from each other. If you must have a "space" in your filename, use an underscore character or a dash (\_ or -). For example, my-circuit is acceptable, but my circuit is not.

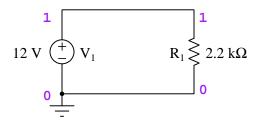

Here is a line-by-line (a.k.a. *card*-by-*card*) interpretation of the netlist:

```

* SPICE circuit title card This is the arbitrary "title" line

v1 1 0 dc 12 Defines a 12 Volt DC voltage source named "v1" between nodes 1 and 0

r1 1 0 2200 Defines a 2200 Ohm resistor between nodes 1 and 0

.dc v1 12 12 1 Requests a DC "sweep" analysis from 12 Volts to 12 Volts on source "v1"

.print dc v(1) i(v1) Measures the voltage at node 1 and current through source "v1"

.end Tells SPICE to stop

```

Note how components are "connected" to each other in the netlist by common node (connection-point) numbers. This is how SPICE is able to "picture" circuits with no graphics. Each and every electrically distinct point in a circuit is given a unique number, component placement being specified by these numbered connection points.

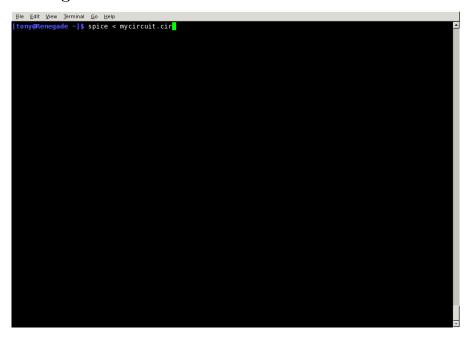

## 3.3.3 Invoking SPICE

This screenshot shows the command-line interface terminal (not the text editor), with the command ready to enter.

## 3.3.4 Viewing the SPICE analysis

As you can see, SPICE is a very "chatty" program that displays a fair amount of extraneous text on the screen following an analysis. Ignoring all the headings and labels, you can see in this display a reiteration of the original netlist (deck) followed by the requested measurements of v(1) (i.e. voltage between node 1 and ground, which is node 0) and i(v1) (current through source v1).

This concludes a *very* brief orientation on using SPICE. For more information, I refer you to the following sections on SPICE component descriptions and analysis descriptions, as well as to the "Gallery" chapter which shows you tested SPICE netlists and output results so you may learn by example.

## 3.4 Demonstration of NGSPICE interactive mode

A more modern (yet still free) version of SPICE is NGSPICE which provides all the old command-line functionality of legacy SPICE versions, plus a window-based *interactive* mode where you may call for certain analyses of a circuit without editing the netlist (deck file). This interactive display window contains a command-entry field as well as a display showing the results of those commands. The procedure for doing this, which I have tested on NGSPICE version 26 on a computer running the Microsoft Windows 7 operating system, is as follows:

- 1. Create the netlist using your favorite text editor and save it under a convenient filename in a convenient location. I will arbitrarily choose the filename test.cir for this demonstration.

- 2. Start the interactive version of NGSPICE and then enter the command source test.cir to instruct it to read the contents of that netlist file. Alternatively, instruct the Windows operating system to associate all \*.cir files with NGSPICE by right-clicking on the file's icon and choosing the "Open with..." option, selecting ngspice.exe as the application you always wish to use for opening any .cir files. From then on, all netlist files ending in .cir will appear as icons bearing the NGSPICE logo, and double-clicking on it will start NGSPICE and automatically run the source instruction. You should be able to skip this filename-association step for all future uses of NGSPICE.

- (Optional) Type listing and press Enter to execute the "listing" command. NGSPICE

will print the netlist in its display window, letting you verify that NGSPICE has loaded your

intended netlist.

- 4. Enter the run command.

- 5. Enter various display commands such as print and plot. If you choose to plot results using the plot command, for example if you are testing a circuit's response over a range of time, or of source values swept over a specified interval, NGSPICE will open up an additional graphic window showing the results in color. When in doubt, print all and plot all are good display commands to try.

If you decide to alter the circuit after having run an analysis, simply close down NGSPICE, edit the netlist file using your text editor (re-saving that file), and then re-open NGSPICE by double-clicking on the netlist file icon again. Then, just issue the run command followed by any display commands you wish.

A very nice feature of this interactive mode is the ability to recall past commands without the need to re-type them. Simply press the "up" and down "arrow" keys to recall all past typed commands from history buffer, then press Enter to re-issue that command. This will save you much time and potential for keystroke errors!

## 3.4.1 Creating the netlist

To begin our demonstration, we will first create a netlist using a text editor. In this case, the editor happens to be notepad++ which is much more capable than the stock notepad that comes with Microsoft Windows. After writing the netlist, it will be saved under the filename test.cir:

```

File Edit Search View Encoding Language Settings Macro Run Plugins Window ?

| Selection |

```

## 3.4.2 Starting NGSPICE

When NGSPICE is started with no command-line arguments (or simply started by double-clicking on the ngspice.exe filename), you will see this interactive window appear on your computer's screen. Commands are typed into the rectangular field at the bottom of the window, and after pressing Enter you will see the results of that command displayed in the upper portion of the window:

Please note that if you take the time to associate .cir files with NGSPICE in Microsoft Windows, this step (as well as the "Loading the netlist" step and "Verifying the loaded netlist" step) will be performed automatically for you whenever you double-click on the netlist file icon. You will know you have been successful in setting up this association if all files with filenames ending in .cir appear with the NGSPICE logo in their Windows icons.

## 3.4.3 Verifying the loaded netlist

Now we will verify the successful loading of our netlist by issuing the listing command. Our netlist now appears in the display window:

This step is optional, but is a good habit. If you approach SPICE as a learning tool, using it to run simulated experiments on virtual circuits to help you master certain electrical concepts, you will find yourself making many changes to your netlists and re-running analyses on those revised circuits. The listing step gives you opportunity to verify each time that your edited netlist has been loaded into NGSPICE and is ready for analysis. It also shows, as in this case, if NGSPICE inserted any statements of its own (e.g. .global gnd).

## 3.4.4 Running the analysis

Before we may request any displayed results from NGSPICE, we must issue the run command:

An interesting feature of NGSPICE is that it ignores the print command within the netlist. Running the simulation merely performs the calculations, but provides no automatic output of results. In the "interactive" version of NGSPICE, it waits for you to enter specific commands before actually displaying any results to the screen. Even with .print or .plot instructions (cards) contained in the netlist, NGSPICE's interactive mode demands you type the display command yourself after it has "run" the simulation. To print the voltage between nodes 1 and 2, for example, you would enter the command print v(1,2). NGSPICE relies on the analysis option in the netlist to discern whether this is a DC or AC analysis.

## 3.4.5 Printing a voltage

Now we are ready to make print or plot requests of NGSPICE. Here we request NGSPICE to print the voltage between nodes 2 and 3 with the print v(2,3) command:

Please note how NGSPICE does not require a preceding period symbol with the print command when it is typed at the interactive command line, nor does it require we specify dc analysis as part of the print command! In fact we could have omitted the entire .print card in the netlist, as NGSPICE's interactive mode only follows output instructions typed at the command line.

Note also how NGSPICE defaults to scientific notation, in this case the voltage displayed as 2.062500e+001 which means  $2.062500 \times 10^1$  Volts, or 20.62500 Volts.

If we issue the **print** command with the node numbers swapped, NGSPICE displays the DC voltage as though measuring with a DC voltmeter with the red test lead on node 3 and black test lead on node 2, showing a negative value instead of positive:

If we wish to see more than one voltage reported, we may specify this at the interactive command line in exactly the same manner as we would have specified within the netlist. For example, issuing the command print v(1,2) v(2) i(v1) would result in NGSPICE printing the voltage between nodes 1 and 2, followed by the voltage between nodes 2 and 0, followed by the current through voltage source v1. Alternatively, we can type print all in the NGSPICE command line and receive a report of all voltages (with reference to node 0 which is ground) rather than just the voltage(s) we specify.

#### 3.4.6 Plotting graphs using NGSPICE

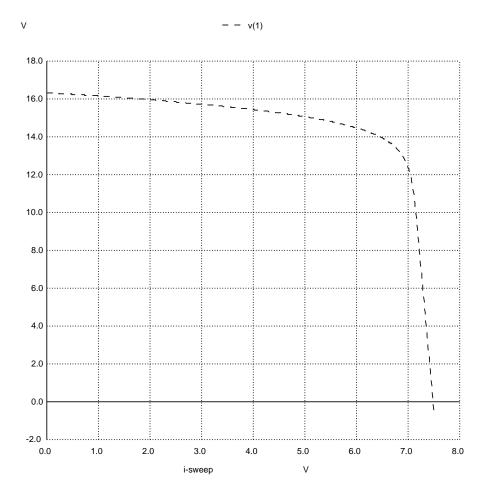

Now we will explore the graphic plotting capabilities of NGSPICE. This is much more advanced than the text-based plots of legacy SPICE versions such as 2G6. Let's begin our example with the following netlist:

```

SPICE title card

c1 1 0 47e-6 ic=24

r1 1 0 2200

.tran 10m 500m uic

.plot tran v(1)

.end

```

This particular netlist defines a simple capacitor-resistor circuit with the 47  $\mu$ F capacitor precharged to 24 Volts. The .tran card calls for a time-domain analysis from t=0 to t=500 milliseconds, in 10 millisecond steps, using the initial condition specified in the capacitor's card.

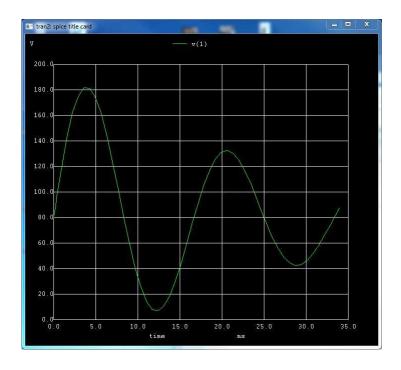

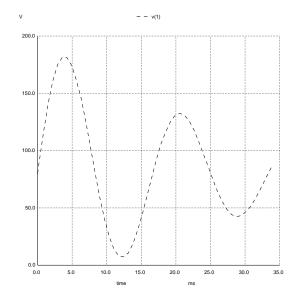

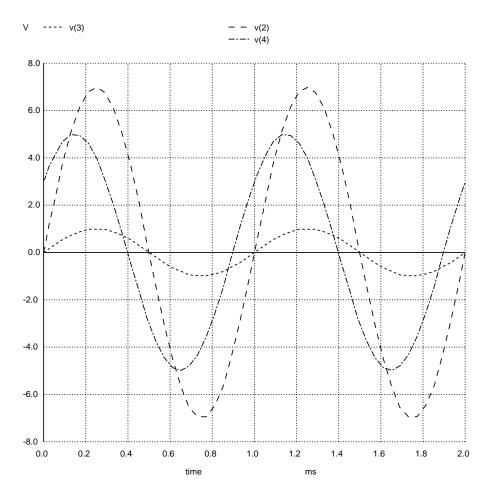

Once having loaded this netlist into NGSPICE and issuing the run command, we may type plot v(1) and get the following output in its own window. As with the previous (DC) analysis, there is no need to specify the analysis type in the plot instruction (i.e. plot v(1) rather than plot tran v(1)) because NGSPICE takes its analysis cue from the .tran card in the netlist. In fact, the .plot tran v(1) card in the netlist is entirely ignored (and could have been omitted!) when using NGSPICE in interactive mode:

As with the print command, we may issue a plot all instruction at the command line which

will prompt NGSPICE to plot *all* variables in the simulation. This may make for a cluttered result when done with complex circuits containing many nodes, but in simple cases such as this example it may be more convenient to simply enter plot all rather than specify each of the desired variables one by one.

## 3.4.7 Issuing multiple commands in a single line

A very convenient feature of NGSPICE's interactive command line is its support for multiple commands in a single typed line. This is useful if you wish to edit the netlist and re-run the simulation without re-starting NGSPICE. Instead of typing in source test.cir followed by run followed by any specific analysis commands such as print and/or plot commands, it is possible to type all these commands on a single line in the interactive window (separated by semicolons), after which the entire string of commands may be repeated by pressing the "up" arrow key followed by the "Enter" key.

Consider for example the following sequence of commands, typically entered one command at a time in the NGSPICE interactive environment to read, execute, and finally plot data from a netlist file named test.cir:

```

run

plot v(2) v(4,3)

```

These three commands may alternatively be entered at once on a single line, then recalled with a single press of the "up" arrow key, thus conserving many keystrokes and shortening the test/development cycle:

```

source test.cir; run; plot v(2) v(4,3)

```

## 3.5 Idiosyncrasies of SPICE

SPICE, particularly early versions such as 2G6, is intolerant of certain omissions and circuit topologies. Some of them are listed here.

## 3.5.1 Beginning and ending cards

Every SPICE deck must begin with a "title" line of plain text. I typically insert a comment (a line beginning with a \* character) in the first line, but a comment is not strictly necessary. The deck cannot begin with a component or analysis description.

Similarly, every SPICE deck must finish with an .end card to instruct the program to stop its analysis. There should be no lines past the .end card, not even blank lines! Similarly, the .end line should not be terminated with either a linefeed nor a carriage return character; i.e. do *not* press the Enter key when typing in this last line! SPICE version 2G6 will still process the deck properly with a terminated .end card, but it generates an annoying *missing .end card* statement anyway.

#### 3.5.2 Node zero

Every SPICE deck must contain reference to node zero (0). Node zero is not just the default "ground" reference point in a circuit, it is a *necessary* point of reference in order for SPICE to perform its mathematical analyses of the circuit. Furthermore, every other node in the circuit must have some DC path to node 0 (ground) or else SPICE will refuse to analyze the circuit, even if the specified analysis is not DC.

#### 3.5.3 Current measurement

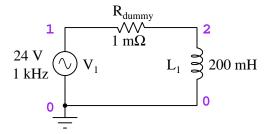

Early versions of SPICE lacked the ability to print or plot values for current through any component but a voltage source. Therefore, if you need to display the calculated current at any point in a circuit being analyzed by a legacy version of SPICE, you must insert special "dummy" voltage sources (set to zero volts each) in the circuit, and then instruct the .print or .plot analysis statements to display the current through those "dummy" sources.

Alternatively, you may insert low-valued "shunt" resistors in series with the point of interest through which you wish to measure current, and then have SPICE measure the voltage(s) across the resistor(s), just the same as you might do for any real circuit where you lack an ammeter suitable for measuring current. So long as these shunt resistor values are considerably less than the other resistances through which you need to measure current, their impact on the circuit will be negligible. Shunt resistor values of 1  $\Omega$  are common for many practical current-measurement applications in the milliAmpere range. For greater currents, shunt resistances of 1 m $\Omega$  or even 1  $\mu\Omega$  may be used.

Interestingly, the mathematical sign of the calculated current is negative when the voltage source in question is actually functioning as a source (i.e. conventional current flow out the + terminal and in the - terminal). In order to display a positive current value, current must be entering the voltage source's + terminal and exiting the - terminal, like a load.

## 3.5.4 Open and short circuits

The fundamental problem with open or shorted circuits is that either condition creates an *undefined* mathematical quantity that SPICE cannot compute. Opens create a condition of infinite (undefined) resistance. Shorts create a condition of zero resistance, which leads to infinite (undefined) current.

Since the insertion of a "short" or an "open" condition may be very useful for simulating a failed component, a common strategy in SPICE modeling is to use a resistor having a very low resistance (short) or a very high resistance (open). For example, a resistance with a value of 1e-9 Ohms is a short for all practical purposes. Similarly, a resistance with a value of 1e9 Ohms is tantamount to an open for most applications.

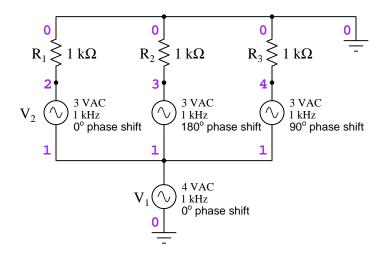

#### 3.5.5 Multiple sources

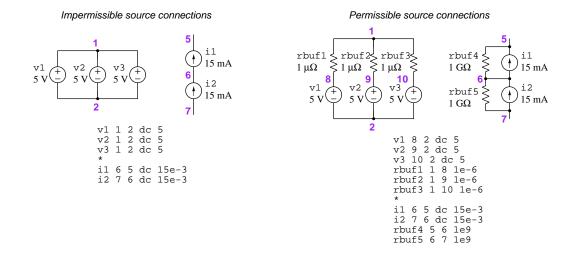

Multiple voltage and/or current sources are permitted in SPICE, but only in certain configurations. Connecting multiple voltage sources in parallel creates a *voltage source loop* error which will cause the analysis to abort, and connecting multiple current sources in series creates a *no dc path to ground* error that is similarly fatal, regardless of source values.

The problem may be understood by considering the internal impedance of each source, and how that impedance "appears" from the perspective of any other source(s). Ideal voltage sources have zero internal impedance, which is why SPICE balks at parallel-connected voltage sources: from the perspective of one voltage source, any other paralleled voltage source appears to be a direct short-circuit. Ideal current sources have infinite internal impedance, which is why SPICE balks at series-connected current sources: from the perspective of one current source, any others connected in series appear to create an open-circuit condition.

It is permissible, however, to connect multiple voltage sources in series with each other. Likewise, multiple current sources connected in parallel are also permissible.

If paralleled voltage sources and/or series-connected current sources are necessary for your circuit design, you may "break up" the offending configuration by inserting buffer components. For example, inserting resistors of extremely low value in series with each voltage source before paralleling them will allow the analysis to proceed. A resistor of extremely high value inserted in parallel with a current source will provide the dc path around the other current source that SPICE is looking for, similarly allowing the analysis to proceed.

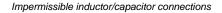

## 3.5.6 Multiple inductors/capacitors

Similar problems arise when connecting multiple inductors directly in parallel with each other, or multiple capacitors directly in series with each other. SPICE views an inductor as being a short (zero resistance) under DC conditions, and a capacitor as being an open (infinite resistance) under DC conditions. As with multiple sources, the problem may be understood by considering the DC resistance of each component as seen from the other components. Parallel-connected inductors are problematic because any attempt to analyze the behavior of one inductor is thwarted by the apparent short-circuit formed by the other inductor(s); series-connected capacitors are problematic because any attempt to analyze the behavior of one capacitor is thwarted by the apparent open-circuit formed by the other capacitor(s).

Likewise, SPICE cannot tolerate any voltage source being connected in parallel with any inductor, nor any current source being connected in series with any capacitor.

If any of these offending configurations are necessary for your circuit design, you may skirt the problem by inserting buffer components as previously described:

#### Permissible inductor/capacitor connections

## Chapter 4

# SPICE component descriptions

To review, here are some of the "cardinal rules" for writing SPICE netlists:

- The first line (card) of the netlist is the Title. It cannot be omitted.

- The last line (card) of the netlist is the .end command. It cannot be omitted.

- Each and every unique connection point in the circuit must be assigned a number called a *node*. This is how you describe the "shape" of the circuit to SPICE: by describing which nodes each component connects to. Components sharing common node numbers are connected to each other. There *must* be a node 0, and this is the "Ground" node of the circuit.

- Comment lines (cards) must begin with an asterisk symbol (\*). These are lines of text inserted into the netlist strictly for the benefit of human readers. SPICE skips over them.

Note that SPICE is case-insensitive. Any instances of capitalization in the following SPICE examples are included solely for clarity and readability, and do not matter when entered into a SPICE netlist.

# 4.1 Independent voltage sources

General format for DC and AC analyses:

[Vname] [+node\_ID] [-node\_ID] [DC/AC voltage] [AC voltage phaseangle]

The first node specified is always the positive (+) terminal of the voltage source, while the second node is always the negative (-) terminal.

# 4.1.1 Example: DC source

- Name = supply

- Polarity = + on node 5 and on node 2

- Value = 15 Volts DC

SPICE element description

Schematic representation

V<sub>supply</sub>

Vsupply 5 2 dc 15

5

$$+$$

15 V

# 4.1.2 Example: "Dummy" source

- Name = meter

- Polarity = + on node 2 and on node 1

- Value =  $\theta$  Volts

SPICE element description

Schematic representation

Vmeter 2 1 0

$$\frac{V_{meter}}{2}$$

$\frac{V_{meter}}{V_{meter}}$

"Dummy" voltage sources are useful in SPICE netlists, to serve as points of measurement for current. Legacy versions of SPICE could not display a calculated current value for any element other than a voltage source, so a "dummy" voltage source with a value of 0 Volts served the purpose quite well.

33

# 4.1.3 Example: AC source

- Name = gen

- Polarity = + on node 3 and on node 0

- Value =  $120 \text{ Volts} \angle 30 \text{ degrees}$

# SPICE element description Schematic representation $V_{gen}$ Vgen 3 0 ac 120 30 3 $^{+}\sqrt{\phantom{a}}$ 0

AC sources specified in this manner are assumed to be sinusoidal in waveform with a constant magnitude and phase shift, and the analysis performed by SPICE will be in the frequency domain.

In addition to steady-state DC and AC sources, SPICE also supports multiple types of time-dependent sources, useful for simulating waveforms and pulse trains in the time domain.

### General format for time-domain analyses:

```

[\textbf{V}\textit{name}] \ [+\text{node\_ID}] \ [-\text{node\_ID}] \ [\textit{waveform\_type}] \ ([\textit{option1} \ \textit{option2}] \ [\textit{option3} \ \cdots])

```

The first node specified is always the positive (+) terminal of the voltage source, while the second node is always the negative (-) terminal. Five different waveform types are supported, each with their own options. The waveform types are Sinusoidal (sin), Pulse (pulse), Exponential (exp), Piecewise Linear (pw1), and Frequency-Modulated Sinusoidal (sffm).

No provision for phase angle exists for AC time-domain sources. Instead, one must make creative use of the start delay time option. A positive start delay time means that the waveform's start becomes delayed, representing a negative phase shift angle. Conversely, a negative start delay time means the waveform has an "early" start, or a positive phase shift angle. Unfortunately, SPICE version 2G6 does not support negative start delay time values.

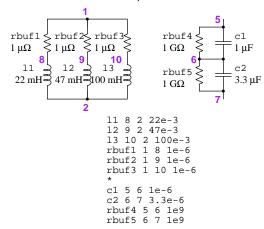

# 4.1.4 Example: Sinusoidal source

- Name = signal

- Polarity = + on node 6 and on node 2

- Wave type = sinusoidal

- DC offset = 10 Volts

- Peak amplitude =  $120 \ Volts$

- Frequency = 60 Hz

- Start delay = 8 milliseconds

- Damping factor =  $\theta$  seconds<sup>-1</sup> (i.e. an undamped waveform)

# SPICE element description

# Schematic representation

Vsignal 6 2 sin(10 120 60 8m 0)

As opposed to a simple AC voltage sources which is assumed to be sinusoidal in waveform and constant in magnitude (i.e. no growth or decay over time), this source is explicitly sinusoidal, and the analysis performed by SPICE will be in the time domain.

Note that the damping factor assumes a decaying signal with a positive value. In order to generate an exponentially growing waveform you will need to use a *negative* value for the damping factor. In other words, the damping factor is equal to  $-\sigma$ .

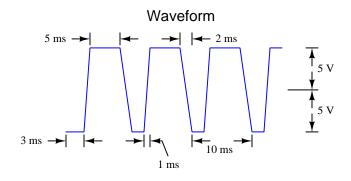

# 4.1.5 Example: Pulse source

- Name = signal

- Polarity = + on node 3 and on node 1

- Wave type = pulse

- Initial value = -5 Volts

- Pulsed value = 5 Volts

- Start delay = 3 milliseconds

- Rise time = 1 millisecond

- Fall time = 2 millisecond

- Pulse width = 5 milliseconds

- Period = 10 milliseconds

# SPICE element description

# Schematic representation

Vsignal 3 1 pulse (-5 5 3m 1m 2m 5m 10m)

Like other time-dependent sources, a pulse source requires analysis in the time domain using the .tran analysis option.

37

# 4.2 Independent current sources

General format for DC and AC analyses:

[Iname] [sink\_node\_ID] [source\_node\_ID] [DC/AC current] [AC current phaseangle]

The first node specified is always the terminal where current (conventional flow) enters the current source, while the second node is always the terminal where current exits the source.

# 4.2.1 Example: DC source

- Name = 9

- Polarity = current enters node 3 and exits node 7

- Value = 10 milliAmperes

SPICE element description

Schematic representation

# 4.2.2 Example: AC source

- Name = in

- Polarity = current enters node 2 and exits node 5

- Value =  $8 \text{ milliAmperes } \angle -20 \text{ degrees}$

SPICE element description

Iin 2 5 ac 8m -20

$$2 \xrightarrow{I_{in}}$$

$$8 \text{ mA } \angle -20$$

# 4.3 Resistors

# General format:

```

[Rname] [node_ID] [node_ID] [value]

```

As with all SPICE elements, resistor values may be specified using plain decimal notation, power-of-ten notation, or metric-prefix notation as alternatively shown in the example.

# 4.3.1 Example

- Name = limit

- Nodes = connected between nodes 2 and 8

- Value = 33 kilo-Ohms  $\Omega$

# SPICE element description

$$R_{limit}$$

2  $\longrightarrow \sim$  8

33 k $\Omega$

4.4. CAPACITORS 39

# 4.4 Capacitors

### General format:

[Cname] [+node\_ID] [-node\_ID] [value] [IC= initial\_voltage]

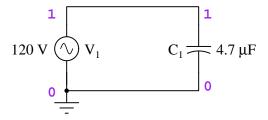

An important caveat when using capacitors in a SPICE netlist is that SPICE cannot tolerate multiple capacitors connected directly in series. If your circuit design requires this configuration, you will need to insert a "buffer" component (e.g. a resistor with an extremely high resistance value) in parallel with one or more of the capacitors so that the offending components are no longer directly in series with each other.

# 4.4.1 Example: Capacitor with initial charge

- Name = 2

- Polarity = + on node 9 and on node 3, initially charged to 3.5 Volts

- Value = 22 micro-Farads

SPICE element description Sci

Schematic representation

C2 9 3 22e-6 ic=3.5

$$9 + \frac{-3}{4}$$

# 4.4.2 Example: Uncharged capacitor

- Name = filter

- Nodes = connected between nodes 1 and 4, no initial voltage

- Value = 4700 micro-Farads

SPICE element description

Cfilter 1 4 4700e-6

$$\begin{array}{c} C_{filter} \\ 1 \longrightarrow \left( \begin{array}{c} 4 \\ 4700 \, \mu F \end{array} \right. \end{array}$$

# 4.5 Inductors

### General format:

[Lname] [sink\_node\_ID] [source\_node\_ID] [value] [IC= initial\_current]

An important caveat when using inductors in a SPICE netlist is that SPICE cannot tolerate multiple inductors connected directly in parallel, nor can it abide any voltage source connected directly in parallel with an inductor. If your circuit design requires either of these configurations, you will need to insert a "buffer" component (e.g. a resistor with a negligible resistance value) between the inductors or inductor/voltage source so that the offending components are no longer directly in parallel with each other.

# 4.5.1 Example: Inductor with initial charge

- Name = 5

- Polarity = current enters node 2 and exits node 6, initially carrying 25 milliAmperes

- Value = 100 milliHenrys

SPICE element description

Schematic representation

# 4.5.2 Example: Uncharged inductor

- Name = filter

- Nodes = connected between nodes 8 and 1, no initial current

- Value = 0.75 Henrys

SPICE element description

4.6. TRANSFORMERS

# 4.6 Transformers

Transformers do not exist as independent entities in SPICE. Instead, one must specify the windings of a transformer as separate inductors, then specify a *coupling* factor k magnetically linking those inductors. The relationship between mutual inductance (M), k, and the two inductor values  $(L_1$  and  $L_2)$  are given by the formula  $M = k\sqrt{L_1L_2}$ .

### General format:

```

[\mathbf{K}name] [\mathbf{L}name\_1] [\mathbf{L}name\_2] [value]

```

# 4.6.1 Example: 2:1 ratio step-down transformer

- Name = xfmr1

- Nodes = primary inductor L1 connected between nodes 1 and 2, secondary inductor L2 connected between nodes 3 and 4

- Value = 0.9999

# SPICE element description

# L1 1 2 20 L2 3 4 5 Kxfmrl L1 L2 0.9999

# Schematic representation

41

Note how the ratio of primary to secondary inductance is equal to the square of the turns ratio, because inductance is proportional to the square of the winding turns. Thus, in order to achieve a 2:1 turns ratio, we need a 4:1 inductance ratio.

# 4.7 Transmission lines

Transmission lines are four-terminal devices, much like dependent sources. Rather than specifying a physical length for the transmission line, we may *either* specify delay time (i.e. the time it takes for the signal to propagate along the entire length of the line) or the signal frequency and corresponding electrical length of the line (in units of wavelengths). These two methods of specifying line length are exclusive to each other. If using the frequency option, the electrical line length defaults to 0.25  $(\frac{\lambda}{4})$  unless specified otherwise.

### General format:

[Tname] [node\_ID] [node\_ID] [node\_ID] [rode\_ID] [**Z0**= characteristic impedance] [**TD**= delay time] [**F**= frequency and **NL**= electrical length]

# 4.7.1 Example: 50-Ohm transmission line with 10 nanosecond delay

- Name = cable

- Nodes = one end of cable has nodes 1 and 2, other end of cable has nodes 3 and 4

- Delay = 10e-9 seconds

SPICE element description

Tcable 1 2 3 4 z0=50 td=10e-9

# Schematic representation

$$\begin{array}{c|c} \mathbf{1} & & & & & & & & & & & & \\ \mathbf{2} & & & & & & & & & & \\ \mathbf{2} & & & & & & & & & \\ \end{array}$$

# 4.7.2 Example: half-wavelength (at 35 MHz) 300-Ohm transmission line

- Name = feedline

- Nodes = one end of cable has nodes 3 and 0, other end of cable has nodes 4 and 0

- Frequency = 35 MHz

- Electrical length = 0.5 wavelengths

### SPICE element description

$$Z_0 = 300 \Omega$$

# 4.8 Linear dependent sources

While independent sources output a prescribed voltage or current, dependent sources output a voltage or current as a function of some other voltage or current signal in the circuit. While there is no real-world equivalent component for a dependent source, dependent sources are useful for modeling a variety of phenomena and are often used as portions of a SPICE model for some real-world component.

SPICE offers dependent sources in four different types:

- Voltage-controlled voltage source (E)

- Voltage-controlled current source (G)

- Current-controlled voltage source (H)

- Current-controlled current source (F)

Voltage-controlled sources (types E and G) have four nodes specified in their SPICE card: two nodes for the input terminals of the controlling voltage, and two nodes for the output terminals. Current-controlled sources (types H and F) only specify the two output terminal nodes, the controlling current being specified by the name of some independent voltage source used as a current sensor.

### General formats:

```

[\texttt{E}\textit{name}] \ [+\texttt{output\_node\_ID}] \ [-\texttt{output\_node\_ID}] \ [+\texttt{input\_node\_ID}] \ [-\texttt{input\_node\_ID}] \ [\textit{gain}]

```

```

[Gname] [sink_node_ID] [source_node_ID] [+input_node_ID] [-input_node_ID] [gain]

```

```

[Hname] [+output_node_ID] [-output_node_ID] [Vname] [gain]

```

```

[Fname] [sink_node_ID] [source_node_ID] [Vname] [gain]

```

In each case, the *gain* value is the ratio of output to input, regardless of units (e.g. Volts output per Volt input for a type E source; Amperes output per Volt input for a type G source, etc.).

### 44

# 4.8.1 Example: voltage-controlled voltage source

- Name = 3

- Polarity = input on nodes 3 (+) and 4 (-); output on nodes 1 (+) and 2 (-)

- Gain = 0.5 Volts output per Volt input

# Spice element description

# Schematic representation

E3 1 2 3 4 0.5

3

$$\longrightarrow$$

+  $\longrightarrow$  E<sub>3</sub>

4  $\longrightarrow$  2

$$V_{out} = (0.5)(V_{in})$$

# 4.8.2 Example: voltage-controlled current source

- Name = 1

- ullet Polarity = input on nodes 4 (+) and 8 (-); output current enters node 5 and exits node 6

- Gain = 2.3 Amperes output per Volt input

# Spice element description

# Schematic representation

G1 5 6 4 8 2.3

4 ---

$$G_1$$

8 ---  $G_1$

8 ---  $G_1$

5  $I_{out} = (2.3)(V_{in})$

45

# 4.9 Nonlinear dependent sources

While independent sources output a prescribed voltage or current, dependent sources output a voltage or current as a function of some other voltage or current signal in the circuit. A *nonlinear* source is able to implement a mathematical function relating one or more inputs to its output. While there is no real-world equivalent component for a dependent source, dependent sources are useful for modeling a variety of phenomena and are often used as portions of a SPICE model for some real-world component.

Note: these sources are not available in legacy versions of SPICE, but are supported in NGSPICE.

### General format:

$$[\textbf{B}\textit{name}] \ [+output\_node\_ID] \ [-output\_node\_ID] \ [i=\textit{expression}] \ [v=\textit{expression}]$$

Supported mathematical functions include the arithmetic basic operations of addition (+), subtraction (-), multiplication (\*), division (/), and powers (^) as well as many other functions. Exponential (exp) and logarithmic (both ln and log), trigonometric, hyperbolic, and other functions are supported too.

# 4.9.1 Example: multiplier

- Name = 2

- Polarity = output on nodes 4 (+) and 3 (-)

- Function =  $voltage\ v(1)\ times\ voltage\ v(2)$

### Spice element description

B2 4 3

$$v=(v(1)*v(2))$$

$V_1, V_2 \longrightarrow B_2$  3  $V_{out} = (V_1)(V_2)$

## 4.10 Diodes

Semiconductor diodes, like other semiconductor components in SPICE, must be accompanied by a .model card somewhere in the netlist specifying the model name and parameters.

### General format:

```

[\textbf{D}name] \ [\textbf{a}node\_node\_ID] \ [\textbf{c}athode\_node\_ID] \ [\textbf{m}odel\_name] \ [\textbf{IC} = initial\_voltage] \\ [\textbf{.MODEL}] \ [\textbf{m}odel\_name] \ [\textbf{D}] \ [\textbf{Parameter1} = value] \ [\textbf{Parameter2} = value] \ [\cdots]

```

The following is a list of parameters, any of which may be included in the .model card:

- IS = Reverse saturation current (default =  $1 \times 10^{-14}$  Amperes)

- N = Emission coefficient (default = 1)

- RS = Ohmic resistance (default = 0 Ohms)

- TT = Transit time (default = 0 seconds)

- CJO = Zero-bias junction capacitance (default = 0 Farads)

- VJ = Junction potential (default = 1 Volt)

- M = Grading coefficient (default = 0.5)

- EG = Activation energy (default = 1.11 electron-Volts, representing Silicon)

- BV = Breakdown voltage (default = infinite Volts)

- IBV = Current at breakdown voltage (default =  $1 \times 10^{-3}$  Amperes)

# 4.10.1 Example: Generic diode

- Name = 2

- Polarity = anode on node 5 and cathode on node 8

- $\bullet$  Model = acme, generic diode

# SPICE element description

4.10. DIODES 47

# 4.10.2 Example: 1N4001

- Name = 4

- ullet Polarity = anode on node 1 and cathode on node 0

- Model = 1N4001 rectifying diode

# SPICE element description

# D4 1 0 1N4001

.MODEL 1N4001 d

- + IS=1.2e-8 RS=0.04

- + N=1.83 EG=0.6

- + BV=50 IBV=5e-8

- + CJO=1e-11 VJ=0.65

- + M=0.5 TT=1e-9

# 4.11 Bipolar Junction Transistors (BJTs)

BJTs, like other semiconductor components in SPICE, must be accompanied by a .model card somewhere in the netlist specifying the model name and parameters. This is where the type of BJT (NPN or PNP) is specified.

### General format:

```

[Qname] [collector_node_ID] [base_node_ID] [emitter_node_ID] [model_name] [.MODEL] [model_name] [NPN or PNP] [Parameter1= value] [Parameter2= value] [\cdots]

```

The following is a list of parameters, any of which may be included in the .model card: