#### Recommended schedule

### <u>Day 1</u>

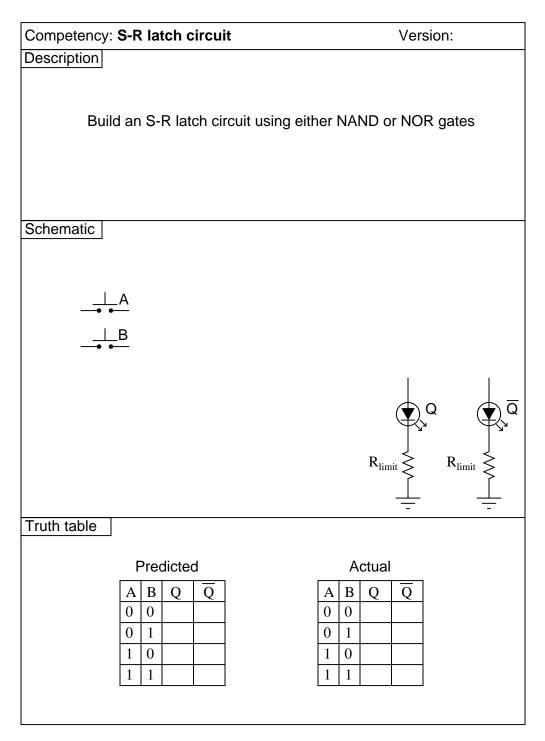

Topics: Latch circuits Questions: 1 through 10 Lab Exercise: S-R latch from individual gates (question 51)

#### Day 2

Topics: 555 timer circuit Questions: 11 through 20 Lab Exercise: 555 timer in astable mode (question 52)

### <u>Day 3</u>

Topics: Gated latch circuits Questions: 21 through 30 Lab Exercise: Troubleshooting practice (decade counter circuit – question 54)

#### Day 4

Topics: Flip-flops Questions: 31 through 40 Lab Exercise: Troubleshooting practice (decade counter circuit – question 54)

#### <u>Day 5</u>

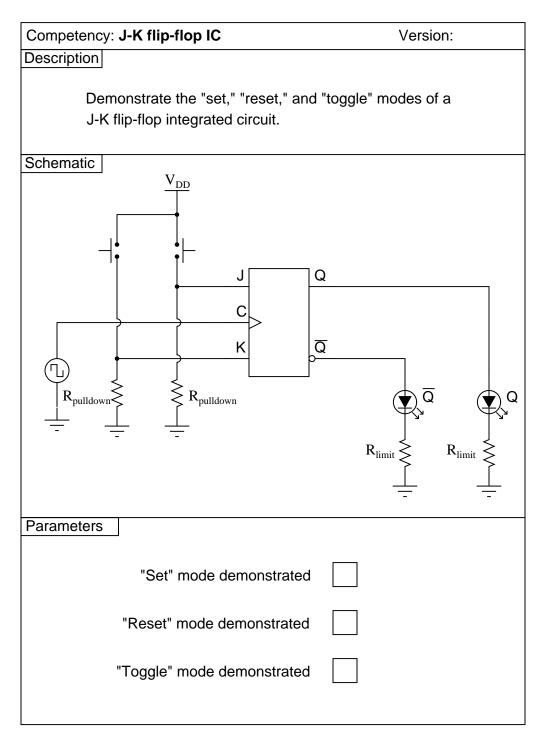

Topics: Flip-flops (continued) Questions: 41 through 50 Lab Exercise: J-K flip-flop IC (question 53)

#### Day 6

Exam 1: includes S-R latch circuit performance assessment Lab Exercise: Troubleshooting practice (decade counter circuit – question 54)

### Troubleshooting practice problems Questions: 57 through 66

DC/AC/Semiconductor/Opamp review problems Questions: 67 through 86

<u>General concept practice and challenge problems</u> Questions: 87 through the end of the worksheet

## Impending deadlines

#### Troubleshooting assessment (counter circuit) due at end of ELTR145, Section 3 Question 55: Troubleshooting log

Question 56: Sample troubleshooting assessment grading criteria

#### Skill standards addressed by this course section

EIA Raising the Standard; Electronics Technician Skills for Today and Tomorrow, June 1994

#### F Technical Skills – Digital Circuits

- F.11 Understand principles and operations of types of flip-flop circuits.

- F.12 Fabricate and demonstrate types of flip-flop circuits.

- F.13 Troubleshoot and repair flip-flop circuits.

- F.17 Understand principles and operations of clock and timing circuits.

- F.18 Fabricate and demonstrate clock and timing circuits.

- F.19 Troubleshoot and repair clock and timing circuits.

#### B Basic and Practical Skills – Communicating on the Job

- B.01 Use effective written and other communication skills. Met by group discussion and completion of labork.

- **B.03** Employ appropriate skills for gathering and retaining information. Met by research and preparation prior to group discussion.

- B.04 Interpret written, graphic, and oral instructions. Met by completion of labourk.

- **B.06** Use language appropriate to the situation. Met by group discussion and in explaining completed laborek.

- **B.07** Participate in meetings in a positive and constructive manner. Met by group discussion.

- **B.08** Use job-related terminology. Met by group discussion and in explaining completed laborek.

- **B.10** Document work projects, procedures, tests, and equipment failures. *Met by project construction and/or troubleshooting assessments.*

### C Basic and Practical Skills – Solving Problems and Critical Thinking

- C.01 Identify the problem. Met by research and preparation prior to group discussion.

- **C.03** Identify available solutions and their impact including evaluating credibility of information, and locating information. *Met by research and preparation prior to group discussion.*

- C.07 Organize personal workloads. Met by daily labwork, preparatory research, and project management.

- C.08 Participate in brainstorming sessions to generate new ideas and solve problems. Met by group discussion.

- D Basic and Practical Skills Reading

- **D.01** Read and apply various sources of technical information (e.g. manufacturer literature, codes, and regulations). *Met by research and preparation prior to group discussion.*

#### **E** Basic and Practical Skills – Proficiency in Mathematics

- **E.01** Determine if a solution is reasonable.

- E.02 Demonstrate ability to use a simple electronic calculator.

- E.06 Translate written and/or verbal statements into mathematical expressions.

- E.07 Compare, compute, and solve problems involving binary, octal, decimal, and hexadecimal numbering systems.

- E.12 Interpret and use tables, charts, maps, and/or graphs.

- E.13 Identify patterns, note trends, and/or draw conclusions from tables, charts, maps, and/or graphs.

- E.15 Simplify and solve algebraic expressions and formulas.

- E.16 Select and use formulas appropriately.

- E.21 Use Boolean algebra to break down logic circuits.

#### Common areas of confusion for students

#### **Difficult concept:** Determining response of a state-dependent logic system.

The very wording of this "difficult concept" may seem difficult to the reader! What I am saying here is that latches and flip-flops are difficult to figure out because their outputs not only depend on the logic levels of the inputs, but also on the *previous* output states. For this reason, these devices fall into the category of "state machines:" they "remember" what logic state they were last in.

I have but one tool for you to use in understanding state machine circuits: the lowly timing diagram. Truth tables fail to fully capture the essence of state machines unless they are expanded to include column(s) showing the last output(s) as well as the inputs. Timing diagrams keep a record of a circuit's last output states as you check to see what will happen for each new input condition. Learn how to draw and interpret timing diagrams, and you will have a powerful tool to apply toward the study of latches and flip-flop circuits!

#### **Difficult concept:** The time-constant equation.

Many students find the time-constant equation difficult because it involves exponents, particularly exponents of Euler's constant *e*. This exponent is often expressed as a negative quantity, making it even more difficult to understand. The single most popular mathematical mistake I see students make with this equation is failing to properly follow algebraic order of operations. Some students try to overcome this weakness by using calculators which allow parenthetical entries, nesting parentheses in such a way that the calculator performs the proper order of operations. However, if you don't understand order of operations yourself, you will not know where to properly place the parentheses. If you have trouble with algebraic order of operations, there is no solution but to invest the necessary time and learn it!

Beyond mathematical errors, though, the most common mistake I see students make with the time constant equation is mis-application. One version of this equation expresses increasing quantities, while another version expresses decreasing quantities. You must already know what the variables are going to do in your time-constant circuit before you know which equation to use! You must also be able to recognize one version of this equation from the other: not by memory, lest you should forget; but by noting what the result of the equation does as time (t) increases. Here again there will be trouble if you are not adept applying algebraic order of operations.

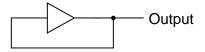

What do you think this logic buffer gate will do, with the output signal "feeding back" to the input?

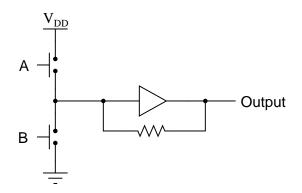

What do you think this buffer will do when each input switch is separately pressed?

Why does the second buffer circuit need a resistor in the feedback loop?  $\underline{file~02896}$

Question 2

When studying latch circuits, you will come across many references to *set* and *reset* logic states. Give a simple definition for each of these terms in the context of latch and flip-flop circuits. <u>file 02897</u>

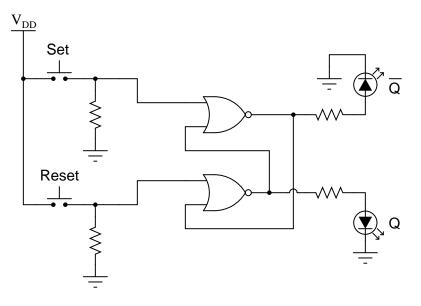

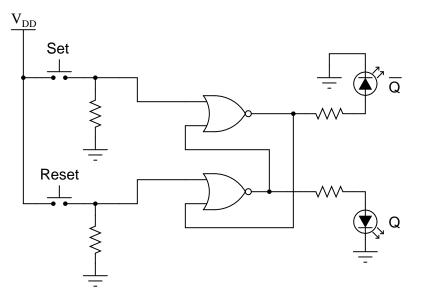

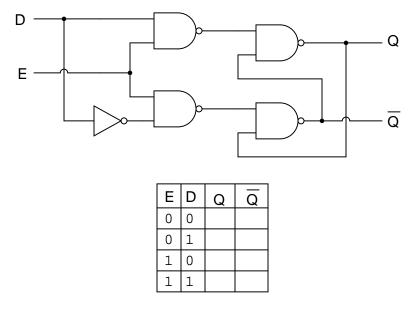

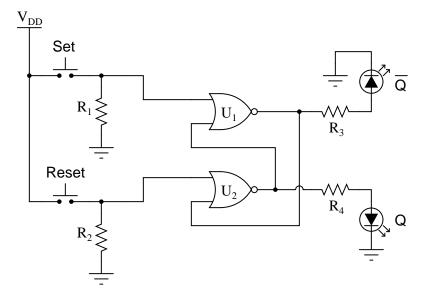

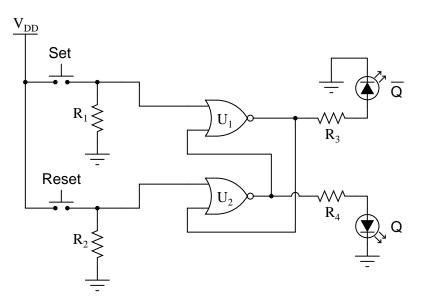

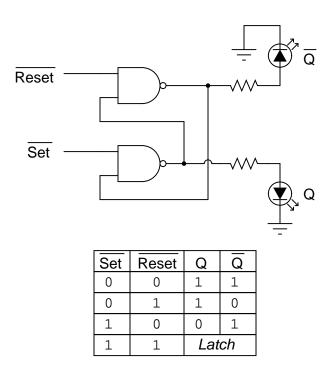

The circuit shown here is called an S-R latch:

Complete the truth table for this latch circuit:

| Set | Reset | Q | Q |

|-----|-------|---|---|

| 0   | 0     |   |   |

| 0   | 1     |   |   |

| 1   | 0     |   |   |

| 1   | 1     |   |   |

<u>file 01349</u>

Question 4

Some digital circuits are considered to have active-low inputs, while others have active-high inputs. Explain what each of these terms means, and how we might identify which type of input(s) a digital circuit has.

$\underline{\mathrm{file}\ 02898}$

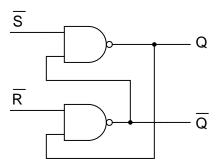

The circuit shown here is called an S-R latch:

Identify which of the two input lines is the *Set*, and which is the *Reset*, and then write a truth table describing the function of this circuit.

# <u>file 01351</u>

#### Question 6

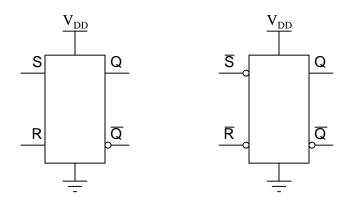

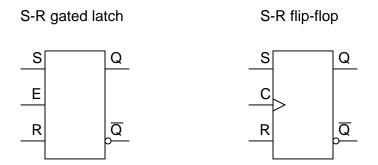

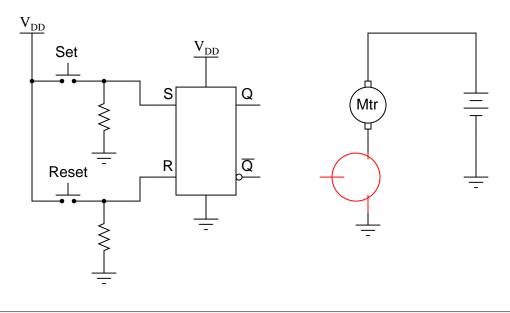

Latch circuits are often drawn as complete units in their own block symbols, rather than as a collection of individual gates:

This simplifies schematic drawings where latches are used, much as the use of gate symbolism (as opposed to drawing individual transistors and resistors) simplifies the diagrams of more elementary digital circuits.

From the block symbols shown in this question, is there any way to determine which of the S-R latches is built with NOR gates, and which one is built with NAND gates?

<u>file 01352</u>

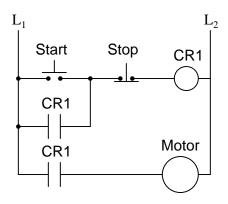

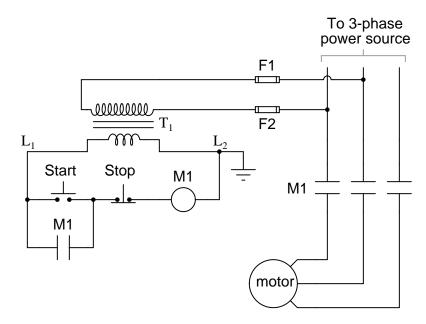

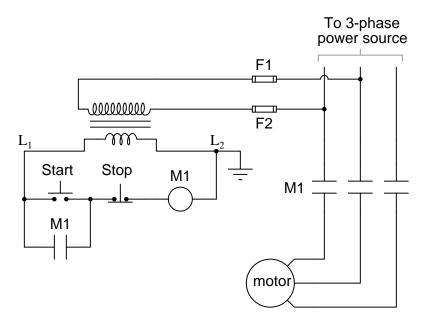

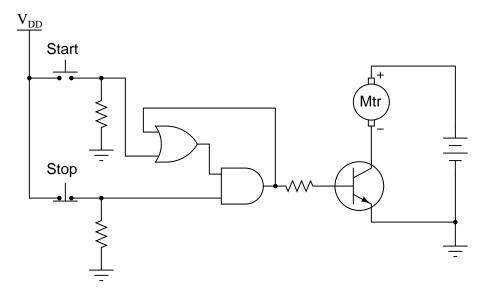

The following relay logic circuit is for starting and stopping an electric motor:

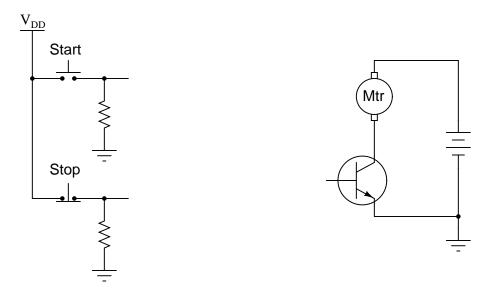

Draw the CMOS logic gate equivalent of this motor start-stop circuit, using these two pushbutton switches as inputs:

Make sure that your schematic is complete, showing how the logic gate will drive the electric motor (through the power transistor shown).

<u>file 01348</u>

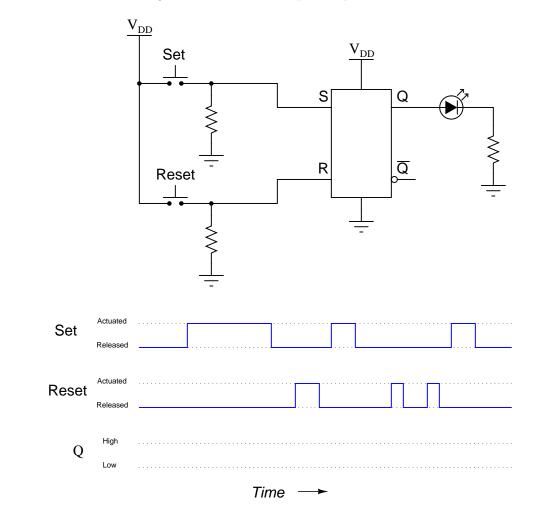

One practical application of S-R latch circuits is *switch debouncing*. Explain what "bounce" refers to in mechanical switches, and also explain how this circuit eliminates it:

Also, show where an oscilloscope could be connected to display any switch "bounce," and explain how the oscilloscope would have to be configured to capture this transient event.

file 01353

### ${\it Question}~9$

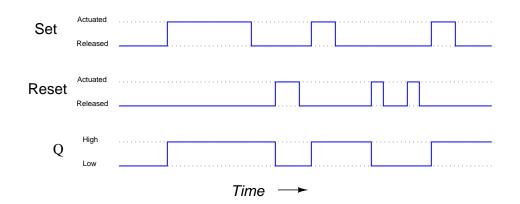

Complete the timing diagram, showing the state of the Q output over time as the Set and Reset switches are actuated. Assume that Q begins in the low state on power-up:

file 02899

A student builds this simple S-R latch for their lab experiment:

When the student powers up this circuit, she notices something strange. Sometimes the latch powers up in the *set* state (Q high and  $\overline{Q}$  low), and other times it powers up in the *reset* state (Q low and  $\overline{Q}$  high). The power-up state of their circuit seems to be unpredictable.

What state *should* their circuit power up in? Did the student make an error building the latch circuit?  $\underline{file \ 01378}$

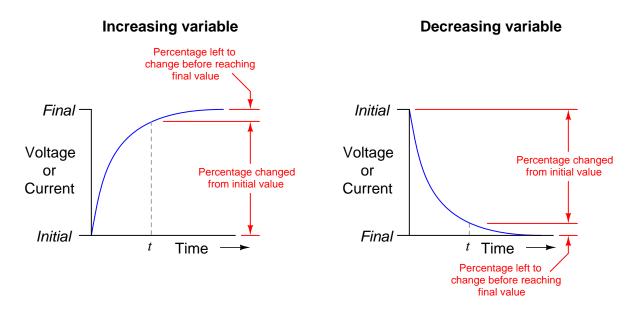

The following expression is frequently used to calculate values of changing variables (voltage and current) in RC and LR timing circuits:

$$e^{-\frac{t}{ au}}$$

or  $\frac{1}{e^{\frac{t}{ au}}}$

If we evaluate this expression for a time of t = 0, we find that it is equal to 1 (100%). If we evaluate this expression for increasingly larger values of time  $(t \to \infty)$ , we find that it approaches 0 (0%).

Based on this simple analysis, would you say that the expression  $e^{-\frac{t}{\tau}}$  describes the percentage that a variable has changed from its initial value in a timing circuit, or the percentage that it has *left* to change before it reaches its final value? To frame this question in graphical terms . . .

Which percentage does the expression  $e^{-\frac{t}{\tau}}$  represent in each case? Explain your answer. file 02946

#### Question 12

Calculate the voltage across a 470  $\mu$ F capacitor after discharging through a 10 k $\Omega$  resistor for 9 seconds, if the capacitor's original voltage (at t = 0) was 24 volts.

Also, express this amount of time (9 seconds) in terms of how many *time constants* have elapsed. file 00452

### ${\it Question}~13$

Calculate the amount of time it takes for a 33  $\mu F$  capacitor to charge from 0 volts to 20 volts, if powered by a 24 volt battery through a 10 k $\Omega$  resistor.

<u>file 01814</u>

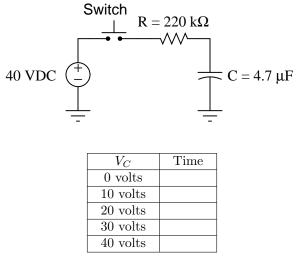

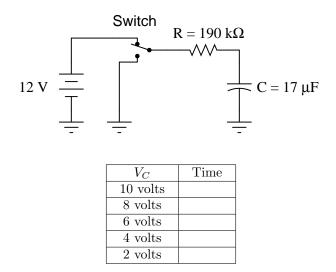

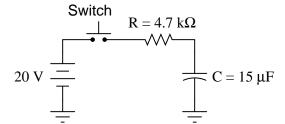

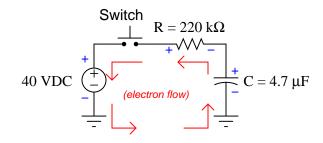

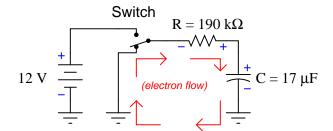

Determine the amount of time needed after switch closure for the capacitor voltage  $(V_C)$  to reach the specified levels:

Trace the direction of electron flow in the circuit, and also mark all voltage polarities.  $\underline{file~02942}$

#### Question 15

Determine the amount of time needed for the capacitor voltage  $(V_C)$  to fall to the specified levels after the switch is thrown to the "discharge" position, assuming it had first been charged to full battery voltage:

Trace the direction of electron flow in the circuit, and also mark all voltage polarities.  $\underline{file~02943}$

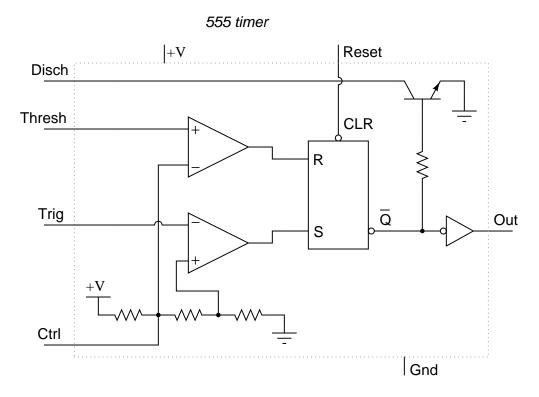

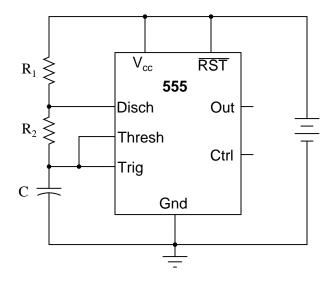

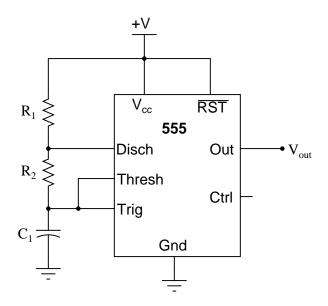

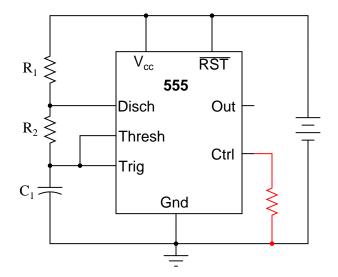

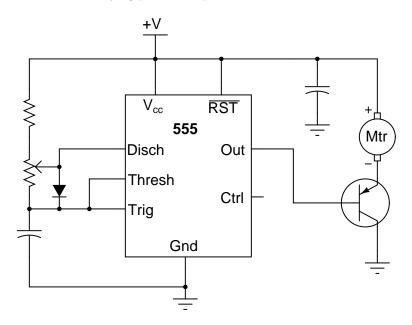

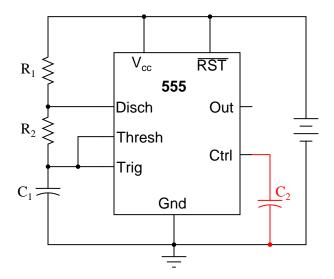

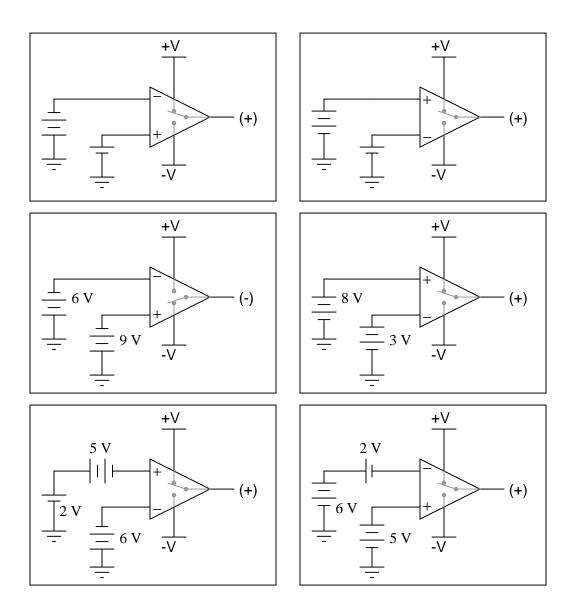

The type "555" integrated circuit is a highly versatile *timer*, used in a wide variety of electronic circuits for time-delay and oscillator functions. The heart of the 555 timer is a pair of comparators and an S-R latch:

The various inputs and outputs of this circuit are labeled in the above schematic as they often appear in datasheets ("Thresh" for *threshold*, "Ctrl" or "Cont" for *control*, etc.).

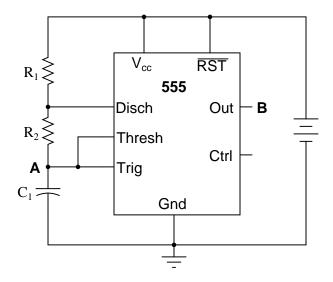

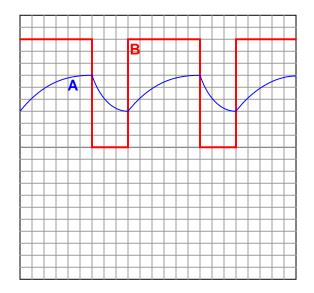

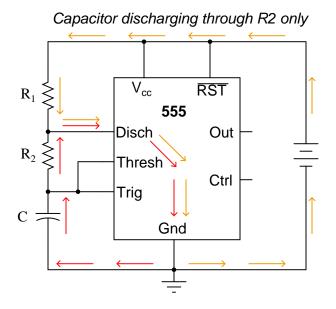

To use the 555 timer as an astable multivibrator, simply connect it to a capacitor, a pair of resistors, and a DC power source as such:

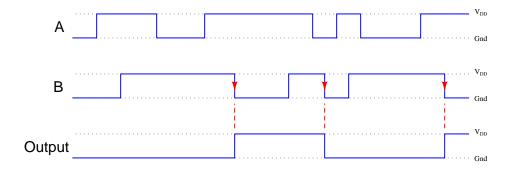

If were were to measure the voltage waveforms at test points  $\mathbf{A}$  and  $\mathbf{B}$  with a dual-trace oscilloscope, we would see the following:

Explain what is happening in this a stable circuit when the output is "high," and also when it is "low."  $\underline{file~01418}$

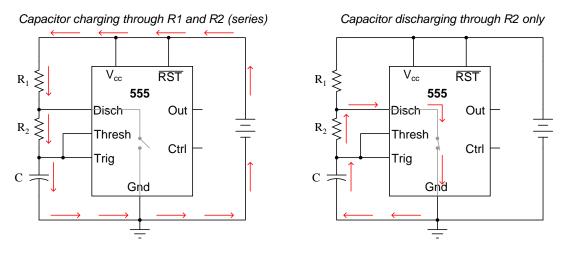

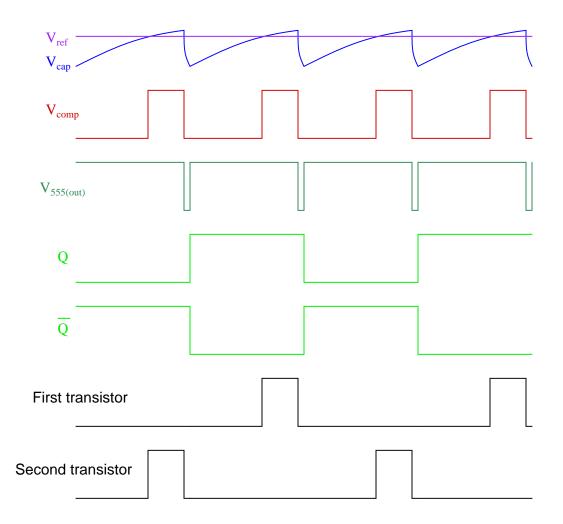

The model "555" integrated circuit is a very popular and useful "chip" used for timing purposes in electronic circuits. The basis for this circuit's timing function is a resistor-capacitor (RC) network:

In this configuration, the "555" chip acts as an *oscillator*: switching back and forth between "high" (full voltage) and "low" (no voltage) output states. The time duration of one of these states is set by the charging action of the capacitor, through both resistors ( $R_1$  and  $R_2$  in series). The other state's time duration is set by the capacitor discharging through one resistor ( $R_2$ ):

Note: all currents shown in the direction of conventional flow

Obviously, the charging time constant must be  $\tau_{charge} = (R_1 + R_2)C$ , while the discharging time constant is  $\tau_{discharge} = R_2C$ . In each of the states, the capacitor is either charging or discharging 50% of the way between its starting and final values (by virtue of how the 555 chip operates), so we know the expression  $e^{\frac{-t}{\tau}} = 0.5$ , or 50 percent.<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> For those who must know why, the 555 timer in this configuration is designed to keep the capacitor voltage cycling between  $\frac{1}{3}$  of the supply voltage and  $\frac{2}{3}$  of the supply voltage. So, when the capacitor is

Develop two equations for predicting the "charge" time and "discharge" time of this 555 timer circuit, so that anyone designing such a circuit for specific time delays will know what resistor and capacitor values to use.

<u>file 01807</u>

#### Question 18

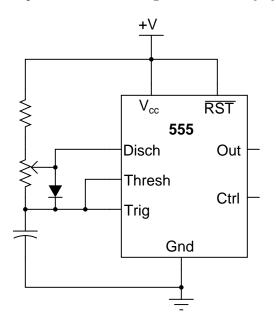

This astable 555 circuit has a potentiometer allowing for variable duty cycle:

With the diode in place, the output waveform's duty cycle may be adjusted to less than 50% if desired. Explain why the diode is necessary for that capability. Also, identify which way the potentiometer wiper must be moved to decrease the duty cycle.

<u>file 01419</u>

charging from  $\frac{1}{3}V_{CC}$  to its (final) value of full supply voltage  $(V_{CC})$ , having this charge cycle interrupted at  $\frac{2}{3}V_{CC}$  by the 555 chip constitutes charging to the half-way point, since  $\frac{2}{3}$  of half-way between  $\frac{1}{3}$  and 1. When discharging, the capacitor starts at  $\frac{2}{3}V_{CC}$  and is interrupted at  $\frac{1}{3}V_{CC}$ , which again constitutes 50% of the way from where it started to where it was (ultimately) headed.

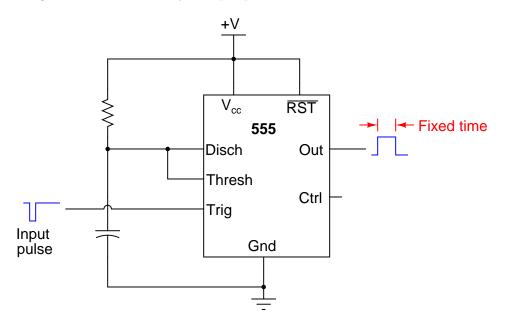

A popular use of the 555 timer is as a *monostable* multivibrator. In this mode, the 555 will output a pulse of fixed length when commanded by an input pulse:

How low does the triggering voltage have to go in order to initiate the output pulse? Also, write an equation specifying the width of this pulse, in seconds, given values of R and C. Hint: the magnitude of the supply voltage is irrelevant, so long as it does not vary during the capacitor's charging cycle. Show your work in obtaining the equation, based on equations of RC time constants. Don't just copy the equation from a book or datasheet!

<u>file 01420</u>

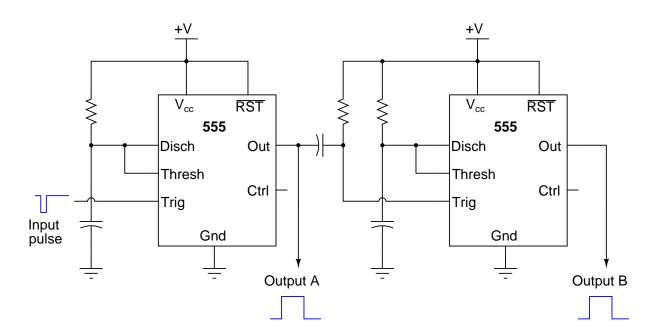

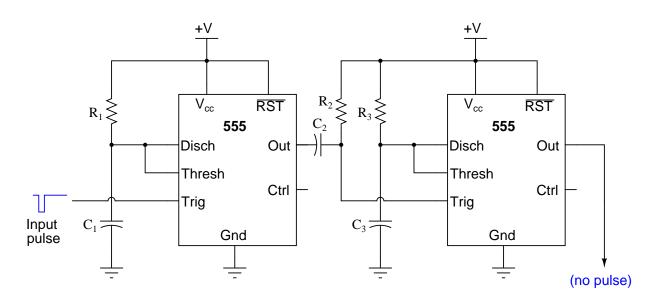

A *sequential* timer circuit may be constructed from multiple 555 timer ICs cascaded together. Examine this circuit and determine how it works:

Can you think of any practical applications for a circuit such as this?  $\underline{\mathrm{file}~02944}$

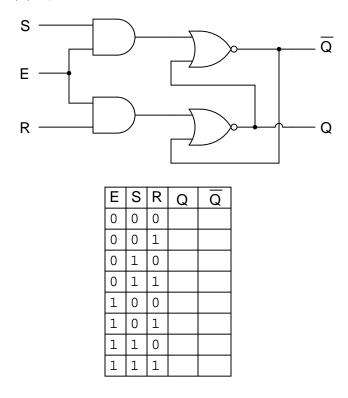

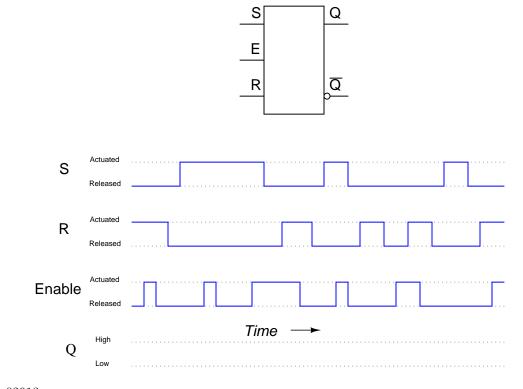

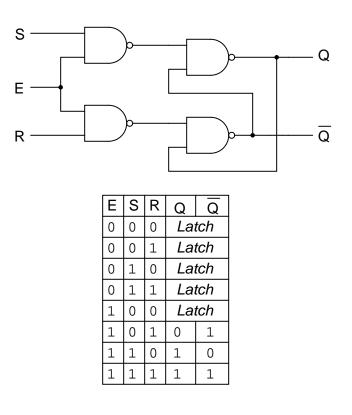

The circuit shown here is a *gated* S-R latch. Write the truth table for this latch circuit, and explain the function of the "Enable" (E) input:

### <u>file 01354</u>

### ${\it Question}~22$

Here is an S-R latch circuit, built from NAND gates:

Add two more NAND gates to this circuit, converting it into a *gated* S-R latch, with an Enable (E) input, and write the truth table for the new circuit. <u>file 01355</u>

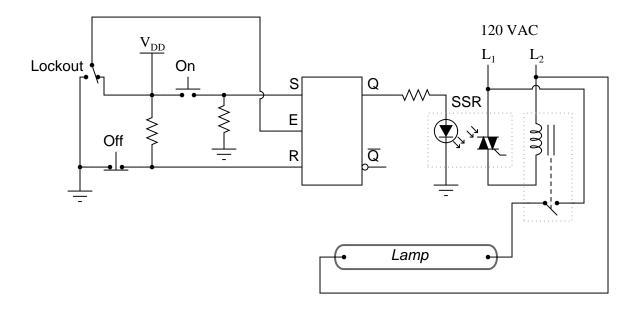

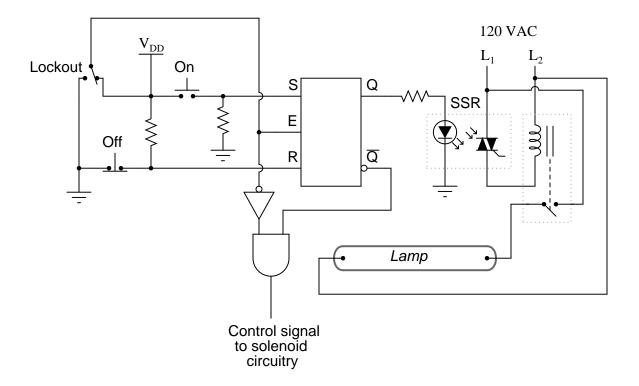

Here, a gated S-R latch is being used to control the electric power to a powerful ultraviolet lamp, used for sterilization of instruments in a laboratory environment:

Based on your knowledge of how gated S-R latches function, what is the purpose of the "Lockout" switch? Also, explain how the CMOS latch is able to exert control over the high-power lamp (i.e. explain the operation of the interposing devices between the latch and the lamp).

Now, suppose the lab personnel want to add a feature to the ultraviolet sterilization chamber: an electric solenoid door lock, so that personnel can open the door to the chamber only if the following conditions are met:

- Lamp is off

- "Lockout" switch is sending a "low" signal to the latch's Enable input

Modify this circuit so that it energizes the door lock solenoid, allowing access to the chamber, only if the above conditions are both true.

<u>file 01356</u>

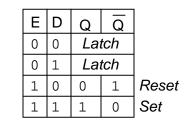

A variation on the gated S-R latch circuit is something called the *D*-latch:

Complete the truth table for this D latch circuit, and identify which rows in the truth table represent the set, reset, and latch states, respectively.

<u>file 01357</u>

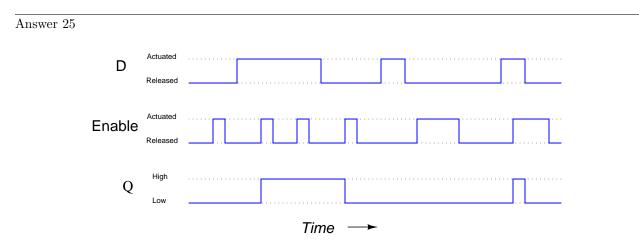

### ${\it Question}~25$

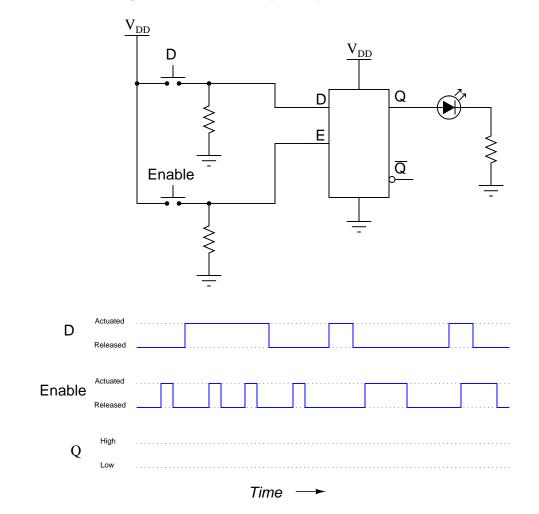

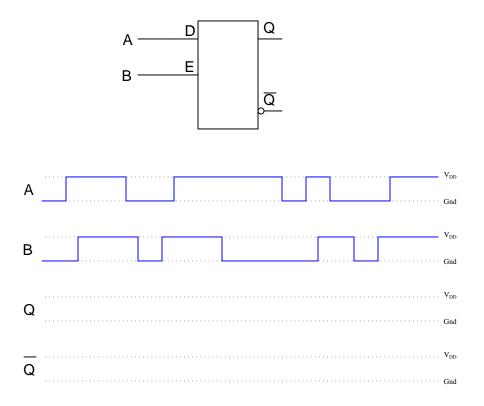

Complete the timing diagram, showing the state of the Q output over time as the input switches are actuated. Assume that Q begins in the low state on power-up:

file 02901

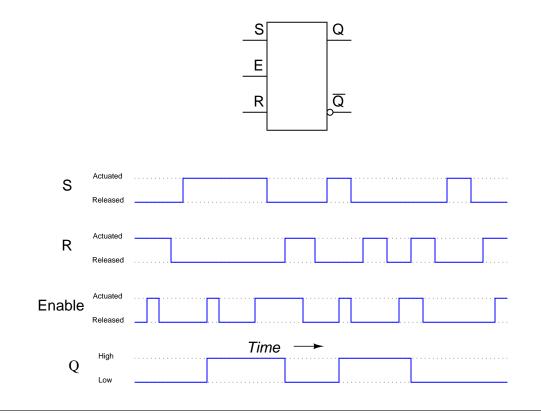

Complete the timing diagram, showing the state of the Q output over time as the input switches are actuated. Assume that Q begins in the low state on power-up:

$\underline{\mathrm{file}~02913}$

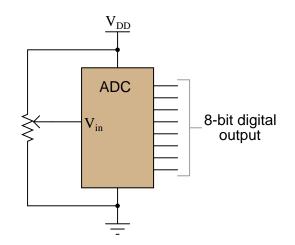

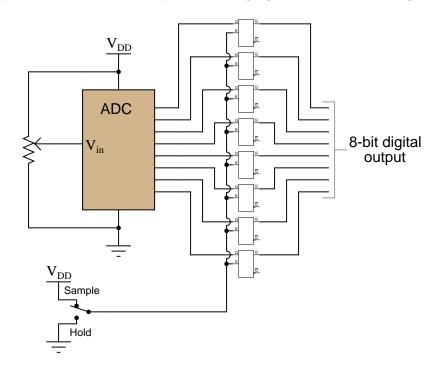

An *analog-to-digital converter* is a circuit that inputs a variable (analog) voltage or current, and outputs multiple bits of binary data corresponding to the magnitude of that measured voltage or current. In the circuit shown here, an ADC inputs a voltage signal from a potentiometer, and outputs an 8-bit binary "word," which may then be read by a computer, transmitted digitally over a communications network, or stored on digital media:

As the input voltage changes, the binary number output by the ADC will change as well. Suppose, though, that we want to have *sample-and-hold* capability added to this data acquisition circuit, to allow us to "freeze" the output of the ADC at will. Explain how using eight D latch circuits will give us this capability:

<u>file 01358</u>

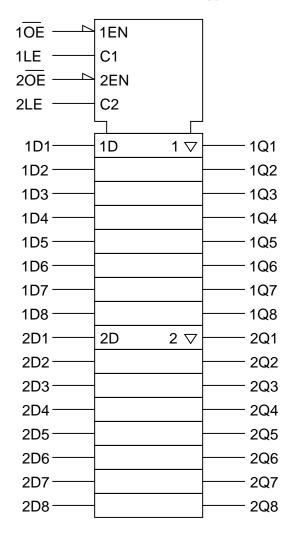

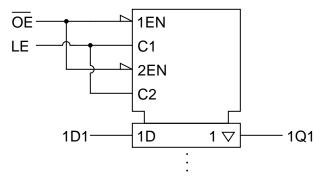

Gated latch circuits often come packaged in multiple quantities, with common gate inputs, so that more than one of the latches within the integrated circuit will be enabled and disabled simultaneously. Examine this logic symbol, representative of the 74AC16373, a 16-bit D-type latch with tri-state outputs:

Note how the sixteen D latches are divided into two groups of eight. Explain the functions of the four inputs at the very top of the symbol (1EN, C1, 2EN, and C2). Which of these input lines correspond to the "Enable" inputs seen on single D-type latch circuits? Also, describe what the "wedge" shapes represent on the 1EN and 2EN input lines.

Suppose you wished to have all sixteen latch circuits enabled as one, rather than as two groups of eight. Show what you would have to do to this circuit in order to achieve this goal.

file 01359

In many types of digital systems, a set of square-wave signals are phase-shifted from each other by  $90^{\circ}$ . Such a phase relationship is called *quadrature*.

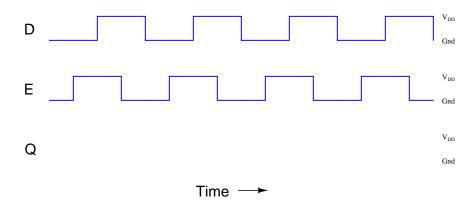

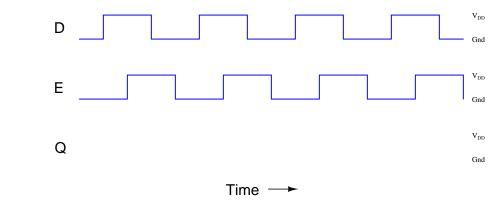

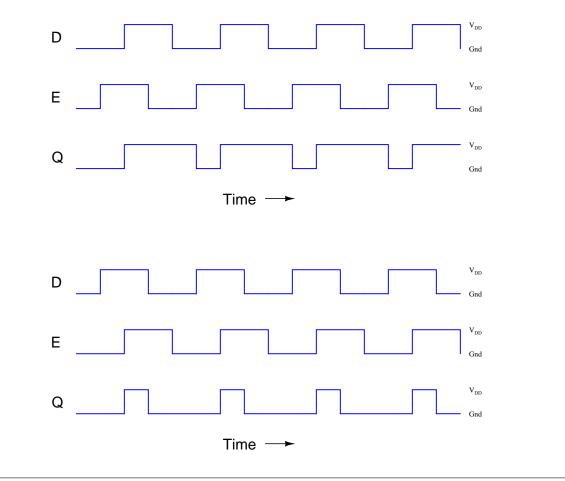

Determine the output of a D-type latch for this pair of quadrature signals, applied to the D and E inputs over time:

Then, determine the output of a D-type latch when the phase relationship is reversed, (D leading E by  $90^{\circ}$ , instead of E leading D by  $90^{\circ}$ ):

<u>file 01360</u>

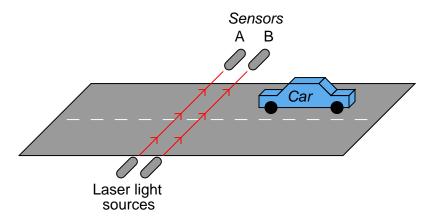

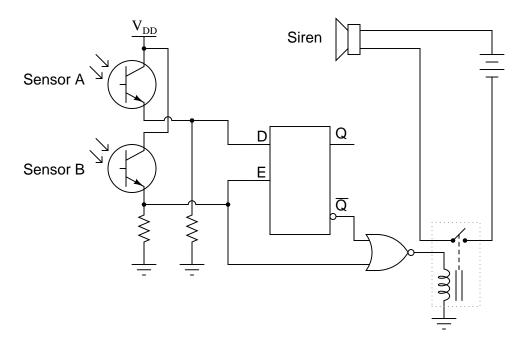

This one-way street is equipped with an alarm to signal drivers going the wrong way. The sensors work by light beams being broken when an automobile passes between them. The distance between the sensors is less than the length of a normal car, which means as a car passes by, first one beam is broken, then both beams become broken, then only the last beam is broken, then neither beam is broken. The sensors are phototransistors sensitive only to the narrow spectrum of light emitted by the laser light sources, so that ambient sunlight will not "fool" them:

Both sensors connect to inputs on a D-type latch, which is then connected to some other circuitry to sound an alarm when a car goes down the road the wrong way:

The first question is this: which way is the *correct* way to drive down this street? From left to right, or from right to left (as shown in the illustration)?

The second question is, how will the system respond if sensor A's laser light source fails? What will happen if sensor B's laser light source fails?

<u>file 01361</u>

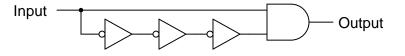

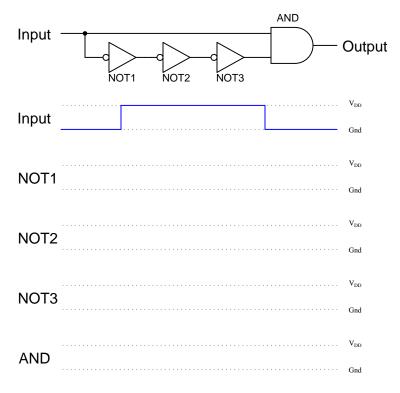

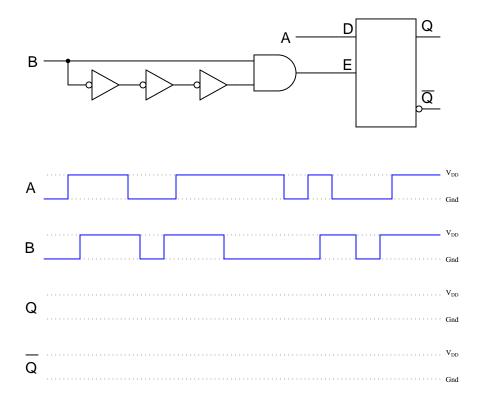

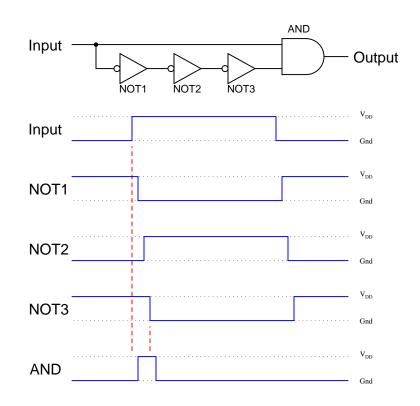

Usually, propagation delay is considered an undesirable characteristic of logic gates, which we simply have to live with. Other times, it is a useful, even necessary, trait. Take for example this circuit:

If the gates constituting this circuit had zero propagation delay, it would perform no useful function at all. To verify this sad fact, analyze its steady-state response to a "low" input signal, then to a "high" input signal. What state is the AND gate's output always in?

Now, consider propagation delay in your analysis by completing a timing diagram for each gate's output, as the input signal transitions from low to high, then from high to low:

What do you notice about the state of the AND gate's output now?  $\underline{\mathrm{file}~01362}$

Question 32

Explain how you would use an oscilloscope to measure the propagation delay of a semiconductor logic gate. Draw a schematic diagram, if necessary. Are the propagation delay times typically equal for a digital gate transitioning from "low" to "high", versus from "high" to "low"? Consult datasheets to substantiate your answer.

Also, comment on whether or not electromechanical relays have an equivalent parameter to propagation delay. If so, how do you suppose the magnitude of a relay's delay compares to that of a semiconductor gate, and why?

file 01371

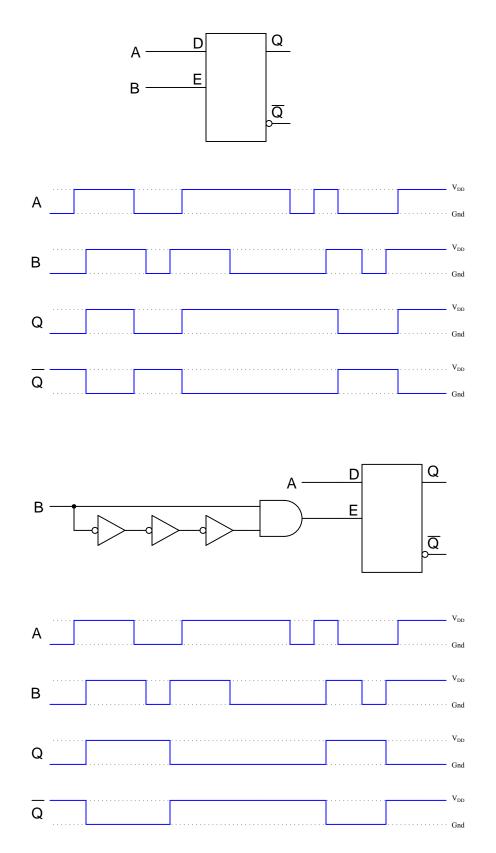

Determine the Q and  $\overline{Q}$  output states of this D-type gated latch, given the following input conditions:

Now, suppose we add a propagation-delay-based one-shot circuit to the Enable line of this D-type gated latch. Re-analyze the output of the circuit, given the same input conditions:

Comment on the differences between these two circuits' responses, especially with reference to the enabling input signal (B).

<u>file 01364</u>

Question 34

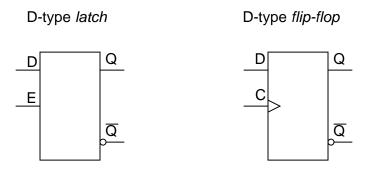

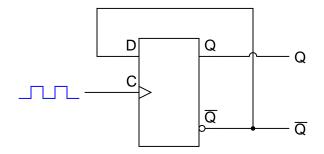

Shown here are two digital components: a D-type *latch* and a D-type *flip-flop*:

Other than the silly name, what distinguishes a "flip-flop" from a latch? How do the two circuits differ in function?

<u>file 01365</u>

Explain how the addition of a propagation-delay-based one-shot circuit to the enable input of an S-R latch changes its behavior:

Specifically, reference your answer to a truth table for this circuit. <u>file 01366</u>

### Question 36

Plain S-R latch circuits are "set" by activating the S input and de-activating the R input. Conversely, they are "reset" by activating the R input and de-activating the S input. Gated latches and flip-flops, however, are a little more complex:

Describe what input conditions have to be present to force each of these multivibrator circuits to *set* and to *reset*.

For the S-R gated latch:

- Set by . . .

- Reset by . . .

For the S-R flip-flop:

- Set by . . .

- $\bullet$  Reset by . . .

<u>file 02935</u>

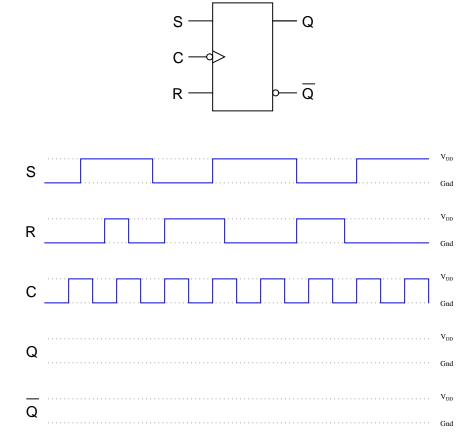

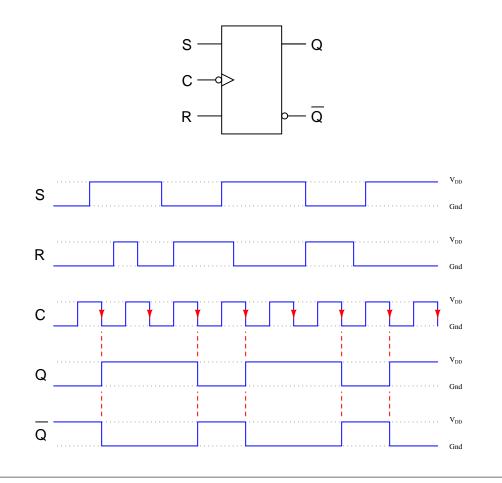

Determine the output states for this S-R flip-flop, given the pulse inputs shown:

<u>file 01367</u>

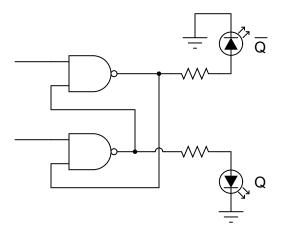

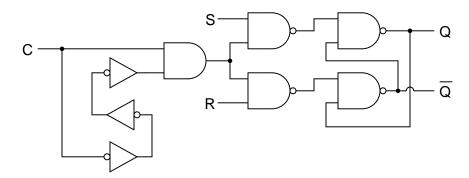

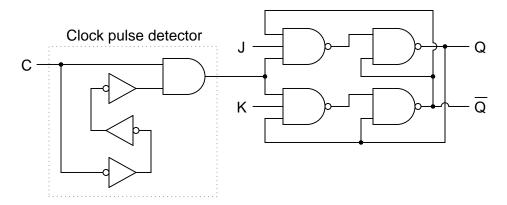

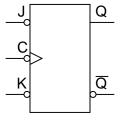

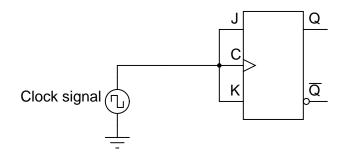

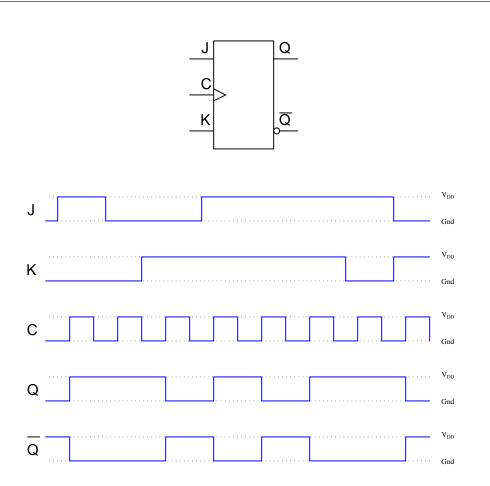

An extremely popular variation on the theme of an S-R flip-flop is the so-called J-K flip-flop circuit shown here:

Note that an S-R flip-flop becomes a J-K flip-flop by adding another layer of feedback from the outputs back to the enabling NAND gates (which are now three-input, instead of two-input). What does this added feedback accomplish? Express your answer in the form of a truth table.

One way to consider the feedback lines going back to the first NAND gates is to regard them as extra enable lines, with the Q and  $\overline{Q}$  outputs selectively enabling just one of those NAND gates at a time. file 01368

### Question 39

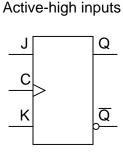

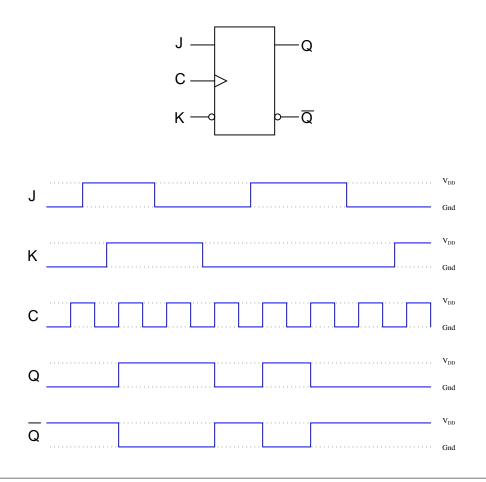

Determine what input conditions are necessary to set, reset, and toggle these two J-K flip-flops:

For the J-K flip-flop with active-high inputs:

- Set by . . .

- Reset by . . .

- Toggle by . . .

For the J-K flip-flop with active-low inputs:

- Set by . . .

- Reset by . . .

- Toggle by . . .

file 02936

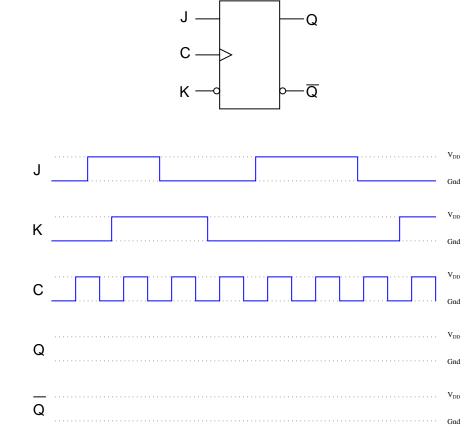

Determine the output states for this J-K flip-flop, given the pulse inputs shown:

<u>file 02934</u>

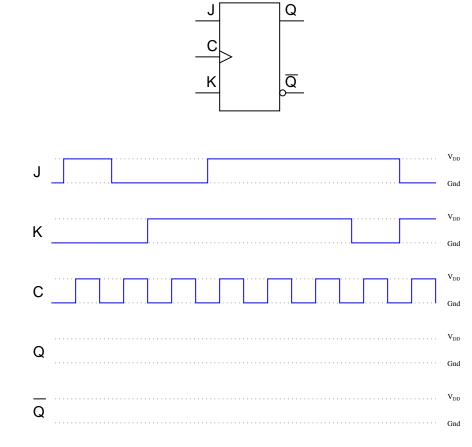

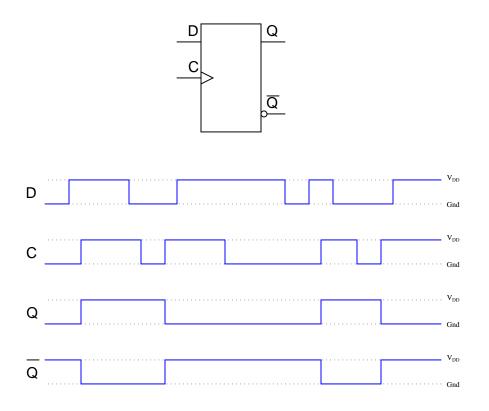

# $\overline{\text{Question } 41}$

Determine the output states for this D flip-flop, given the pulse inputs shown:

<u>file 02940</u>

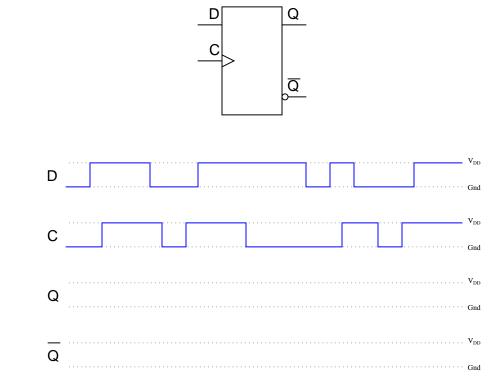

# $\overline{\text{Question } 42}$

Determine the output states for this J-K flip-flop, given the pulse inputs shown:

<u>file 02939</u>

# ${\it Question}~43$

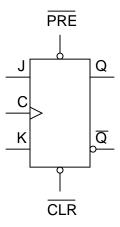

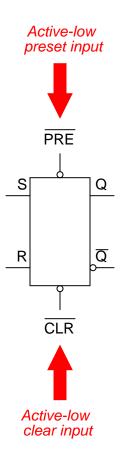

Flip-flops often come equipped with *asynchronous input lines* as well as synchronous input lines. This J-K flip-flop, for example, has both "preset" and "clear" asynchronous inputs:

Describe the functions of these inputs. Why would we ever want to use them in a circuit? Explain what the "synchronous" inputs are, and why they are designated by that term.

Also, note that both of the asynchronous inputs are *active-low*. As a rule, asynchronous inputs are almost always active-low rather than active-high, even if all the other inputs on the flip-flop are active-high. Why do you suppose this is?

<u>file 01370</u>

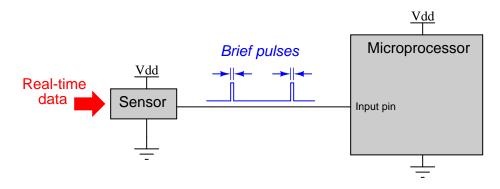

A scientist is using a microprocessor system to monitor the boolean ("high" or "low") status of a particle sensor in her high-speed nuclear experiment. The problem is, the nuclear events detected by the sensor come and go much faster than the microprocessor is able to sample them. Simply put, the pulses output by the sensor are too brief to be "caught" by the microprocessor every time:

She asks several technicians to try and fix the problem. One tries altering the microprocessor's program to achieve a faster sampling rater, to no avail. Another recalibrates the particle sensor to react slower, but this only results in missed data (because the real world data does not slow down accordingly!). No solution tried so far works, because the fundamental problem is that the microprocessor is just too slow to "catch" the extremely short pulse events coming from the particle sensor. What is required is some kind of external circuit to "read" the sensor's state at the leading edge of a sample pulse, and then hold that digital state long enough for the microprocessor to reliably register it.

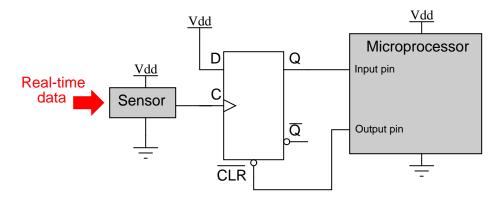

Finally, another electronics technician comes along and proposes this solution, but then goes on vacation, leaving you to implement it:

Explain how this D-type flip-flop works to solve the problem, and what action the microprocessor has to take on the output pin to make the flip-flop function as a detector for multiple pulses.  $\frac{fle \ 01464}{fle}$

# ${\it Question}~45$

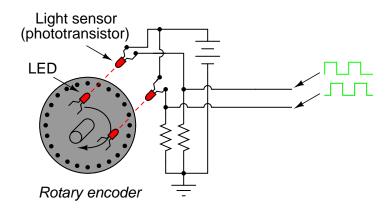

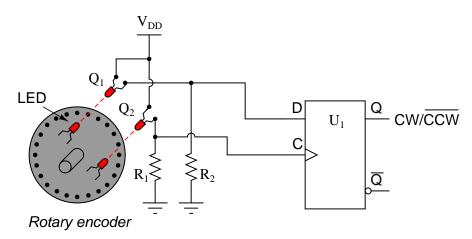

A common type of rotary encoder is one built to produce a *quadrature* output:

The two LED/phototransistor pairs are arranged in such a way that their pulse outputs are always  $90^{\circ}$  out of phase with each other. Quadrature output encoders are useful because they allow us to determine direction of motion as well as incremental position.

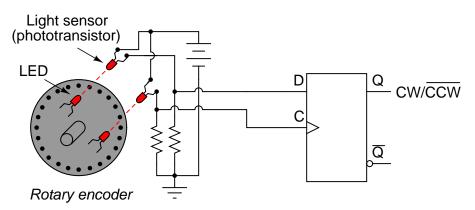

Building a quadrature direction detector circuit is easy, if you use a D-type flip-flop:

Analyze this circuit, and explain how it works.  $\underline{file \ 01384}$

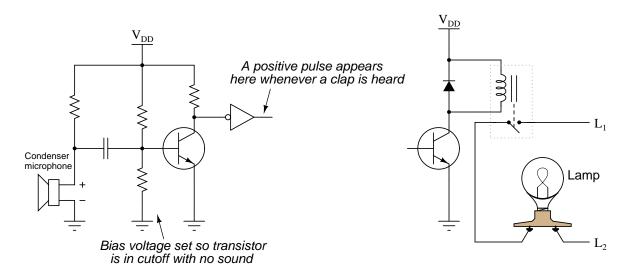

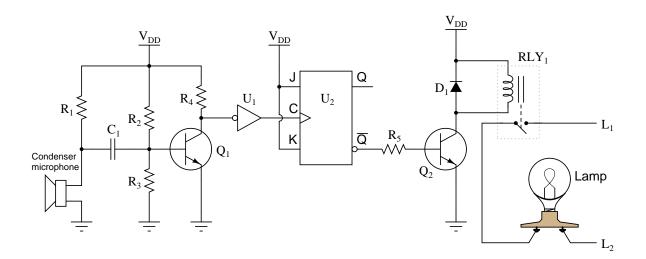

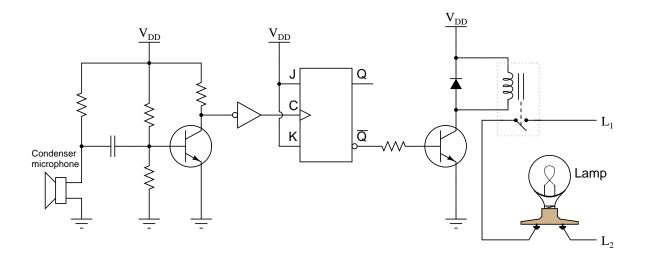

Suppose a student wants to build a sound-controlled lamp control circuit, whereby a single clap or other loud burst of noise turns the lamp on, and another single clap turns it off. The sound-detection and lamp-drive circuitry is shown here:

Add a J-K flip-flop to this schematic diagram to implement the toggling function.  $\underline{file~01369}$

### Question 47

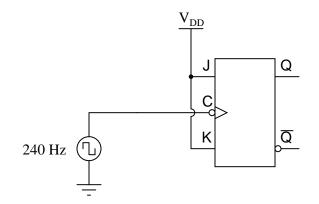

If the clock frequency driving this flip-flop is 240 Hz, what is the frequency of the flip-flop's output signals (either Q or  $\overline{Q}$ )?

<u>file 01372</u>

# ${\it Question}~48$

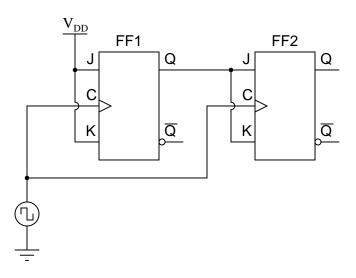

The flip-flop circuit shown here is classified as *synchronous* because both flip-flops receive clock pulses at the exact same time:

Define the following parameters:

- Set-up time

- Hold time

- Propagation delay time

- Minimum clock pulse duration

Then, explain how each of these parameters is relevant in the circuit shown.  $\underline{file~01385}$

# Question 49

Locate a manufacturer's datasheet for a flip-flop IC, and research the following parameters:

- Flip-flop type (S-R, D, J-K)

- Part number

- ANSI/IEEE standard symbol

- How many asynchronous inputs

- Minimum setup and hold times (shown in timing diagrams)

file 02937

A student has an idea to make a J-K flip-flop toggle: why not just connect the J, K, and Clock inputs together and drive them all with the same square-wave pulse? If the inputs are active-high and the clock is positive edge-triggered, the J and K inputs should both go "high" at the same moment the clock signal transitions from low to high, thus establishing the necessary conditions for a toggle (J=1, K=1, clock transition):

Unfortunately, the J-K flip-flop refuses to toggle when this circuit is built. No matter how many clock pulses it receives, the Q and  $\overline{Q}$  outputs remain in their original states – the flip-flop remains "latched." Explain the practical reason why the student's flip-flop circuit idea will not work.

file 02938

<u>file 01621</u>

| Competency: Astable 555 timer    | Version:                  |  |  |  |

|----------------------------------|---------------------------|--|--|--|

| Schematic +V                     |                           |  |  |  |

|                                  |                           |  |  |  |

|                                  | ]                         |  |  |  |

| $R_1 \gtrsim 555$                |                           |  |  |  |

| Disch Out                        | V <sub>out</sub>          |  |  |  |

| R₂≩ ☐Thresh                      |                           |  |  |  |

| Ctrl                             |                           |  |  |  |

| $C_1 \overline{\uparrow}$        | $\square$ $\square$ $C_2$ |  |  |  |

|                                  |                           |  |  |  |

| <u> </u>                         | <u>+</u>                  |  |  |  |

| Given conditions                 |                           |  |  |  |

| $+V =$ $R_1 =$ $R_2 =$           |                           |  |  |  |

| $-V = C_1 = C_2 =$               |                           |  |  |  |

|                                  |                           |  |  |  |

| Parameters                       |                           |  |  |  |

| Predicted Measured               |                           |  |  |  |

| t <sub>high</sub>                |                           |  |  |  |

| t <sub>low</sub>                 |                           |  |  |  |

|                                  |                           |  |  |  |

| f <sub>out</sub>                 |                           |  |  |  |

| Fault analysis                   |                           |  |  |  |

| Suppose component fails shorted  |                           |  |  |  |

| What will happen in the circuit? |                           |  |  |  |

|                                  |                           |  |  |  |

|                                  |                           |  |  |  |

<u>file 02861</u>

<u>file 02900</u>

| Competency: De             | cade counter circuit                                                                                               | Version:                                                                                         |

|----------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Schematic                  |                                                                                                                    |                                                                                                  |

| Reset                      | RST B<br>CTR C                                                                                                     | a<br>b<br>c<br>d<br>e<br>f<br>g<br>g<br>b<br>e<br>d<br>e<br>d<br>d<br>d<br>d<br>d<br>d<br>d<br>d |

| Given conditions           |                                                                                                                    |                                                                                                  |

| Given conditions           |                                                                                                                    |                                                                                                  |

| U <sub>1</sub> =           | U <sub>2</sub> =                                                                                                   |                                                                                                  |

| Parameters                 |                                                                                                                    |                                                                                                  |

| counting front to 0 again. | crements with each physical e<br>om 0 to 9 and then resetting b<br>Count sequence exhibits no<br>no missed events. | back                                                                                             |

<u>file 03851</u>

| Troubleshooting log                                                        |                                                      |  |  |

|----------------------------------------------------------------------------|------------------------------------------------------|--|--|

| Actions / Measurements / Observations<br>(i.e. What I did and/or noticed ) | <b>Conclusions</b> (i.e. <i>What this tells me</i> ) |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

|                                                                            |                                                      |  |  |

Troubleshooting log

<u>file 03933</u>

### **Troubleshooting Grading Criteria**

You will receive the highest score for which *all* criteria are met.

- 100 % (Must meet or exceed all criteria listed)

- A. Absolutely flawless procedure

NAME:

B. No unnecessary actions or measurements taken

90% (Must meet or exceed these criteria in addition to all criteria for 85% and below)

- A. No reversals in procedure (i.e. changing mind without sufficient evidence)

- B. Every single action, measurement, and relevant observation properly documented

$\underline{80\%}$  (Must meet or exceed these criteria in addition to all criteria for 75% and below)

- A. No more than one unnecessary action or measurement

- B. No false conclusions or conceptual errors

- C. No missing conclusions (i.e. at least one documented conclusion for action / measurement / observation)

$\underline{70\%}$  (Must meet or exceed these criteria in addition to all criteria for 65%)

- A. No more than one false conclusion or conceptual error

- B. No more than one conclusion missing (i.e. an action, measurement, or relevant observation without a corresponding conclusion)

65 % (Must meet or exceed these criteria in addition to all criteria for 60%)

- A. No more than two false conclusions or conceptual errors

- B. No more than two unnecessary actions or measurements

- C. No more than one undocumented action, measurement, or relevant observation

- D. Proper use of all test equipment

60 % (Must meet or exceed these criteria)

- A. Fault accurately identified

- B. Safe procedures used at all times

50 % (Only applicable where students performed significant development/design work – i.e. not a proven circuit provided with all component values)

A. Working prototype circuit built and demonstrated

0% (If any of the following conditions are true)

A. Unsafe procedure(s) used at any point

file 03932

Identify at least one component fault that would cause the " $\overline{Q}$ " LED to always remain off, no matter what was done with the input switches.

For each of your proposed faults, explain why it will cause the described problem.  $\underline{file~03892}$

# Question 58

Identify at least one component fault that would cause the "Q" LED to always stay on, no matter what was done with the input switches.

For each of your proposed faults, explain why it will cause the described problem.  $\underline{file~03891}$

Predict how the operation of this astable 555 timer circuit will be affected as a result of the following faults. Specifically, identify what will happen to the capacitor voltage  $(V_{C1})$  and the output voltage  $(V_{out})$  for each fault condition. Consider each fault independently (i.e. one at a time, no multiple faults):

- Resistor  $R_1$  fails open:

- Solder bridge (short) across resistor  $R_1$ :

- Resistor  $R_2$  fails open:

- Solder bridge (short) across resistor  $R_2$ :

- Capacitor  $C_1$  fails shorted:

For each of these conditions, explain why the resulting effects will occur.  $\underline{file~03890}$

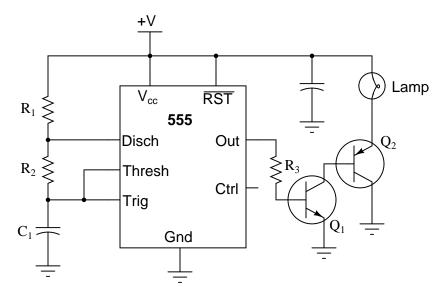

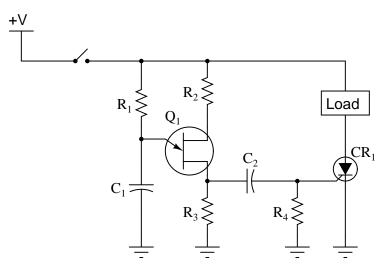

This circuit uses a "555" integrated circuit to produce a low-frequency square-wave voltage signal (seen between the "Out" terminal of the chip and ground), which is used to turn a pair of transistors on and off to flash a large lamp. Predict how this circuit will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults):

- Transistor  $Q_1$  fails open (collector-to-emitter):

- Transistor  $Q_2$  fails open (collector-to-emitter):

- Resistor  $R_3$  fails open:

- Transistor  $Q_1$  fails shorted (collector-to-emitter):

For each of these conditions, explain why the resulting effects will occur.  $\underline{file~03715}$

What would happen to the operation of this astable 555 timer circuit if a resistor were accidently connected between the "Control" terminal and ground? Explain the reason for your answer.

#### file 01435

#### Question 62

A student builds their first astable 555 timer circuit, using a TLC555CP chip. Unfortunately, it seems to have a problem. Sometimes, the output of the timer simply stops oscillating, with no apparent cause. Stranger yet, the problem often occurs at the precise time anyone moves their hand within a few inches of the circuit board (without actually touching anything!).

What could the student have done wrong in assembling this circuit to cause such a problem? What steps would you take to troubleshoot this problem?

$\underline{\text{file } 01433}$

Identify at least one component fault that would cause the final 555 timer output to always remain low:

For each of your proposed faults, explain why it will cause the described problem.  $\underline{file~03893}$

Predict how the operation of this sound-activated lamp circuit will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults):

- Resistor  $R_1$  fails open:

- Resistor  $R_3$  fails open:

- Diode  $D_1$  fails open:

- Transistor  $Q_2$  fails shorted between collector and emitter:

- Solder bridge past resistor  $R_5$ :

For each of these conditions, explain why the resulting effects will occur.  $\underline{file~03894}$

Identify at least one component fault that would cause the flip-flop to indicate "clockwise" all the time, regardless of encoder motion:

For each of your proposed faults, explain why it will cause the described problem. <u>file 03895</u>

#### Question 66

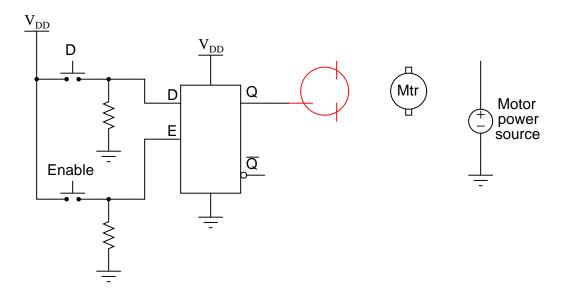

Identify at least one fault that would cause the motor to turn off immediately once the "Start" pushbutton switch was released, instead of "latch" in the run mode as it should:

For each of your proposed faults, explain why it will cause the described problem.  $\underline{file~03896}$

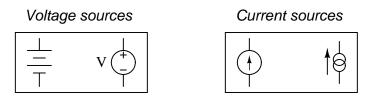

Ideal *voltage sources* and ideal *current sources*, while both being sources of electrical power, behave very differently from one another:

Explain how each type of electrical source would behave if connected to a variable-resistance load. As this variable resistance were increased and decreased, how would each type of source respond? file 03226

Question 68

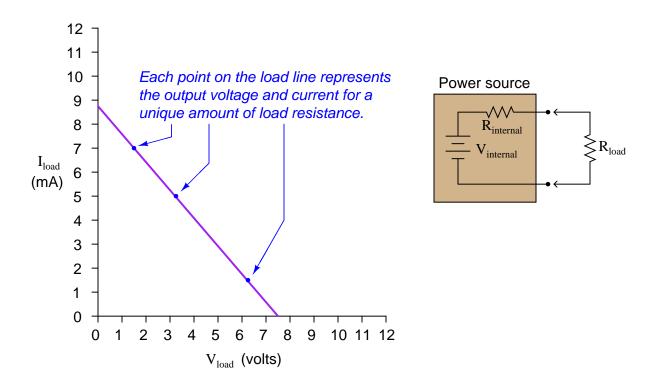

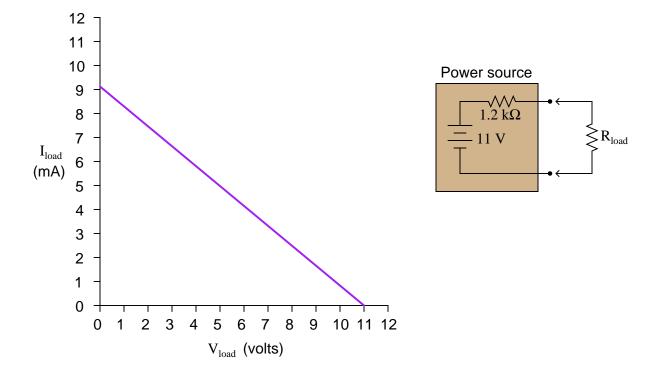

A very common sort of graph used in electronics work is the *load line*, showing all possibilities of load voltage and load current that a particular power source is able to supply to a load:

Note how the load line shows the voltage "sag" of the power source in relation to the amount of current drawn by the load. At high currents, the output voltage will be very low (upper-left end of load line). At low currents, the output voltage will be near its maximum (lower-right end of load line). If all internal components of the power source are *linear* in nature, the load line will always be perfectly straight.

Plot the load line for a power source having an internal voltage  $(V_{internal})$  of 11 volts and an internal resistance  $(R_{internal})$  of 1.2 k $\Omega$ . Superimpose your load line onto the load line graph shown above. Hint: it only takes two points to define a line!

<u>file 03513</u>

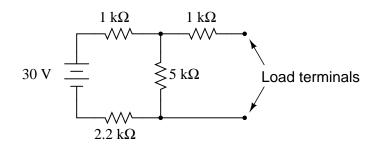

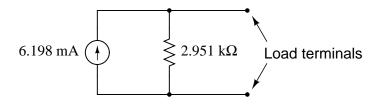

Give a step-by-step procedure for reducing this circuit to a Norton equivalent circuit (one current source in parallel with one resistor):

# <u>file 03230</u>

# Question 70

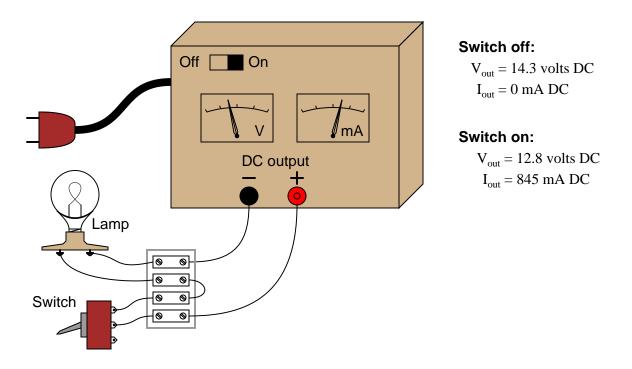

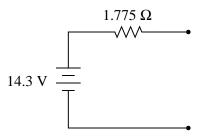

Suppose you had an AC/DC power supply, which performed as follows (open-circuit and loaded test conditions):

Draw a Thévenin equivalent circuit to model the behavior of this power supply.  $\underline{file}~03693$

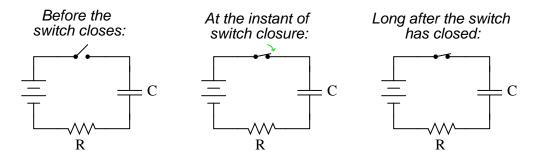

Qualitatively determine the voltages across all components as well as the current through all components in this simple RC circuit at three different times: (1) just before the switch closes, (2) at the instant the switch contacts touch, and (3) after the switch has been closed for a long time. Assume that the capacitor begins in a completely discharged state:

Express your answers qualitatively: "maximum," "minimum," or perhaps "zero" if you know that to be the case.

#### Before the switch closes:

$V_C =$   $V_R =$   $V_{switch} =$ I =

At the instant of switch closure:

$V_C = V_R = V_{switch} = I =$

Long after the switch has closed:

$V_C =$  $V_R =$  $V_{switch} =$ I =

Hint: a graph may be a helpful tool for determining the answers!  $\underline{file \ 01811}$

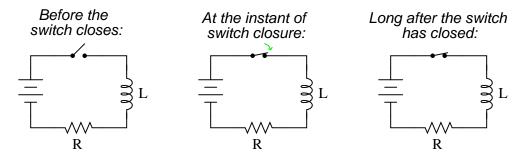

Qualitatively determine the voltages across all components as well as the current through all components in this simple LR circuit at three different times: (1) just before the switch closes, (2) at the instant the switch contacts touch, and (3) after the switch has been closed for a long time.

Express your answers qualitatively: "maximum," "minimum," or perhaps "zero" if you know that to be the case.

Before the switch closes:

$V_L = V_R = V_{switch} = I =$

At the instant of switch closure:

$V_L =$  $V_R =$  $V_{switch} =$ I =

Long after the switch has closed:

$V_L = V_R = V_{switch} = I =$

Hint: a graph may be a helpful tool for determining the answers! file 01812

#### Question 73

What value of resistor would need to be connected in series with a 33  $\mu$ F capacitor in order to provide a *time constant* ( $\tau$ ) of 10 seconds? Express your answer in the form of a five-band precision resistor color code (with a tolerance of +/- 0.1%).

file 00436

An electronic service technician prepares to work on a high-voltage power supply circuit containing one large capacitor. On the side of this capacitor are the following specifications:

#### $3000 \text{ WVDC} \quad 0.75 \mu \text{F}$

Obviously this device poses a certain amount of danger, even with the AC line power secured (lockout/tag-out). Discharging this capacitor by directly shorting its terminals with a screwdriver or some other piece of metal might be dangerous due to the quantity of the stored charge. What needs to be done is to discharge this capacitor at a modest rate.

The technician realizes that she can discharge the capacitor at any rate desired by connecting a resistor in parallel with it (holding the resistor with electrically-insulated pliers, of course, to avoid having to touch either terminal). What size resistor should she use, if she wants to discharge the capacitor to less than 1% charge in 15 seconds? State your answer using the standard 4-band resistor color code (tolerance = +/-10%).

file 01525

### Question 75

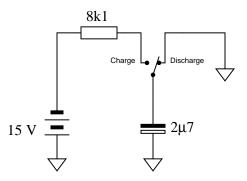

The following circuit allows a capacitor to be rapidly discharged and slowly charged:

Suppose that the switch was left in the "discharge" position for some substantial amount of time. Then, someone moves the switch to the "charge" position to let the capacitor charge. Calculate the amount of capacitor voltage and capacitor current at exactly 45 milliseconds after moving the switch to the "charge" position.

$V_C =$ \_\_\_\_\_\_ @ t = 45 ms

$I_C = \underline{\qquad} @ t = 45 \text{ ms}$ <u>file 03557</u>

## ${\it Question}~76$

Determine the capacitor voltage and capacitor current at the specified times (time t = 0 milliseconds being the exact moment the switch contacts close). Assume the capacitor begins in a fully discharged state:

| Time              | $V_C$ (volts) | $I_C (\mathrm{mA})$ |

|-------------------|---------------|---------------------|

| 0 ms              |               |                     |

| 30 ms             |               |                     |

| 60 ms             |               |                     |

| 90 ms             |               |                     |

| 120 ms            |               |                     |

| $150 \mathrm{ms}$ |               |                     |

file 03556

Question 77

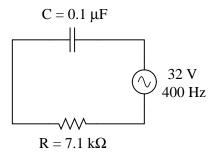

Calculate the power factor of this circuit:

$\underline{\mathrm{file}\ 02179}$

### ${\it Question}~78$

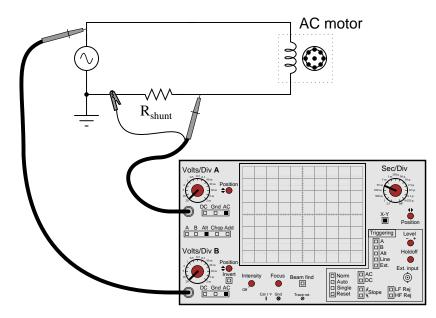

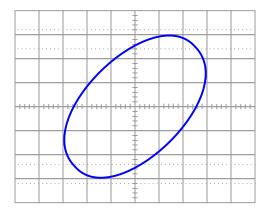

An oscilloscope is connected to a low-current AC motor circuit to measure both voltage and current, and plot them against one another as a Lissajous figure:

The following Lissajous figure is obtained from this measurement:

From this figure, calculate the phase angle  $(\Theta)$  and the power factor for this motor circuit. file 02183

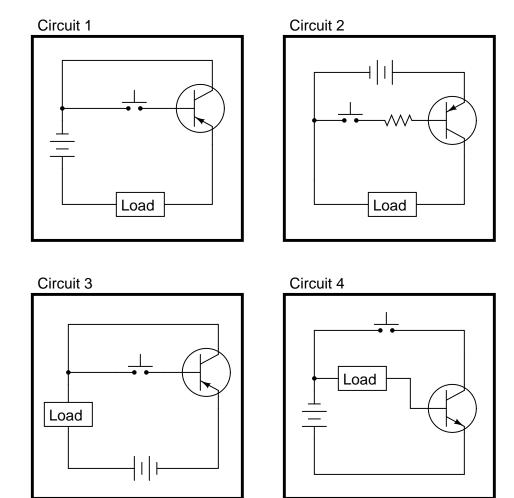

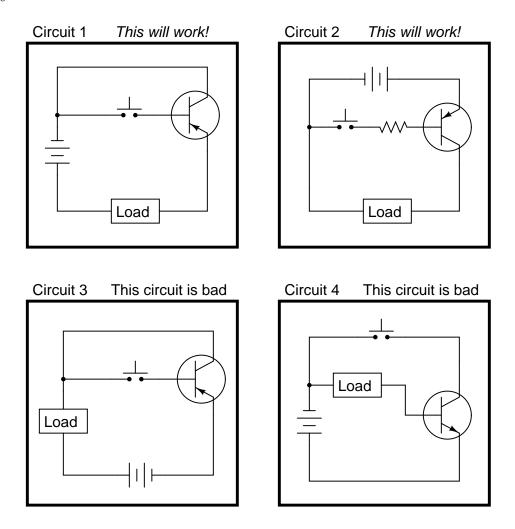

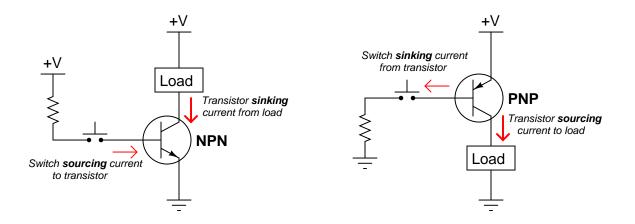

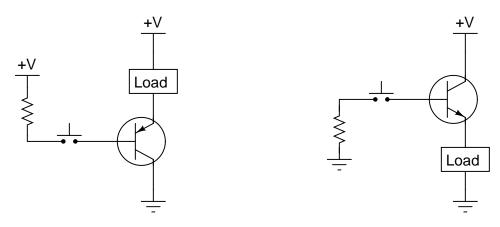

Some of the following transistor switch circuits are properly configured, and some are not. Identify which of these circuits will function properly (i.e. turn on the load when the switch closes) and which of these circuits are mis-wired:

<u>file 02326</u>

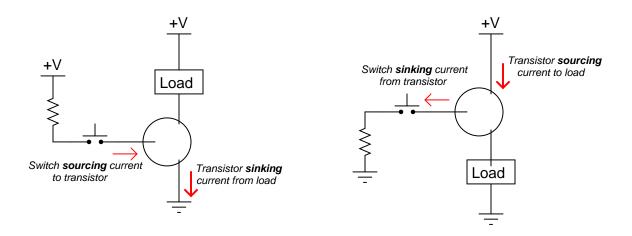

Choose the right type of bipolar junction transistor for each of these switching applications, drawing the correct transistor symbol inside each circle:

Also, explain why resistors are necessary in both these circuits for the transistors to function without being damaged. file 02408

#### Question 81

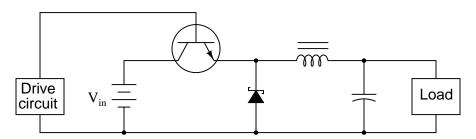

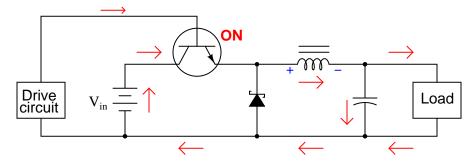

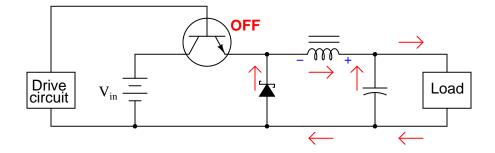

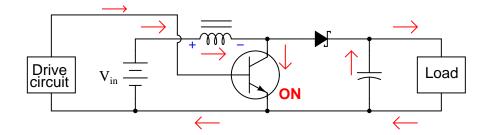

The schematic diagram shown here is for a "buck" converter circuit, a type of DC-DC "switching" power conversion circuit:

In this circuit, the transistor is either fully on or fully off; that is, driven between the extremes of saturation or cutoff. By avoiding the transistor's "active" mode (where it would drop substantial voltage while conducting current), very low transistor power dissipations can be achieved. With little power wasted in the form of heat, "switching" power conversion circuits are typically very efficient.

Trace all current directions during both states of the transistor. Also, mark the inductor's voltage polarity during both states of the transistor.

<u>file 01102</u>

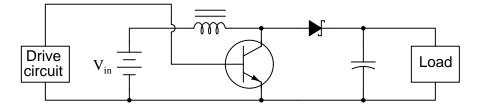

The schematic diagram shown here is for a "boost" converter circuit, a type of DC-DC "switching" power conversion circuit:

In this circuit, the transistor is either fully on or fully off; that is, driven between the extremes of saturation or cutoff. By avoiding the transistor's "active" mode (where it would drop substantial voltage while conducting current), very low transistor power dissipations can be achieved. With little power wasted in the form of heat, "switching" power conversion circuits are typically very efficient.

Trace all current directions during both states of the transistor. Also, mark the inductor's voltage polarity during both states of the transistor.

<u>file 01103</u>

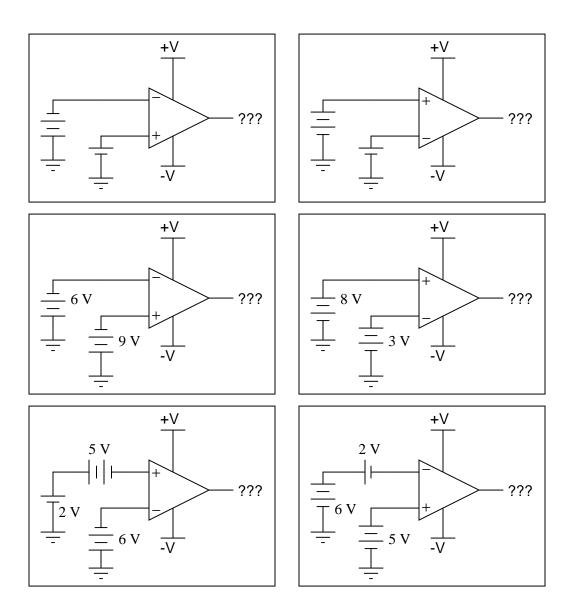

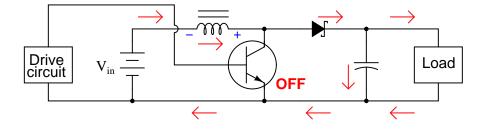

Determine the output voltage polarity of this op-amp (with reference to ground), given the following input conditions:

<u>file 03762</u>

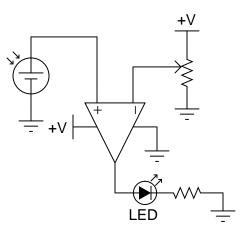

In this circuit, a solar cell converts light into voltage for the opamp to "read" on its noninverting input. The opamp's inverting input connects to the wiper of a potentiometer. Under what conditions does the LED energize?

<u>file 00872</u>

# Question 85

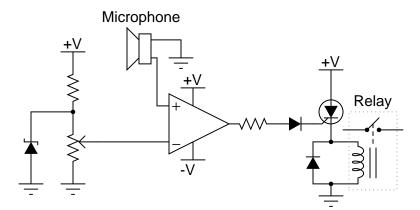

Explain the operation of this sound-activated relay circuit:

<u>file 00879</u>

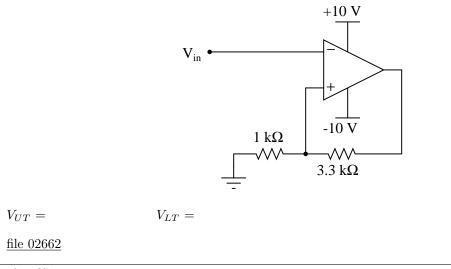

Assume that the comparator in this circuit is only capable of "swinging" its output to within 1 volt of its power supply rail voltages. Calculate the upper and lower threshold voltages, given the resistor values shown:

### Question 87

A very common form of *latch* circuit is the simple "start-stop" relay circuit used for motor controls, whereby a pair of momentary-contact pushbutton switches control the operation of an electric motor. In this particular case, I show a low-voltage control circuit and a 3-phase, higher voltage motor:

Explain the operation of this circuit, from the time the "Start" switch is actuated to the time the "Stop" switch is actuated. The normally-open M1 contact shown in the low-voltage control circuit is commonly called a *seal-in contact*. Explain what this contact does, and why it might be called a "seal-in" contact. <u>file 01347</u>

# ${\it Question}~88$

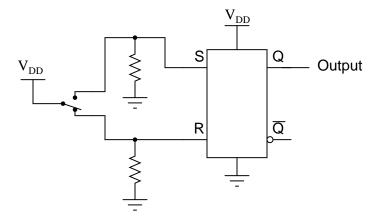

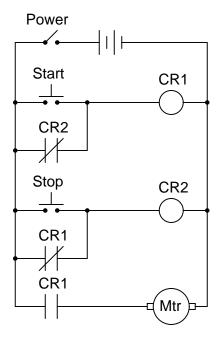

A student decides to build a motor start/stop control circuit based on the logic of a NOR gate S-R latch, rather than the usual simple "seal-in" contact circuit:

The circuit works fine, except that sometimes the motor starts all by itself when the circuit is first powered up! Other times, the motor remains off after power-up. In other words, the power-up state of this circuit is unpredictable.

Explain why this is so, and what might be done to prevent the motor from powering up in the "run" state.

<u>file 01379</u>

The following schematic diagram shows a timer circuit made from a UJT and an SCR:

Together, the combination of  $R_1$ ,  $C_1$ ,  $R_2$ ,  $R_3$ , and  $Q_1$  form a *relaxation oscillator*, which outputs a square wave signal. Explain how a square wave oscillation is able to perform a simple time-delay for the load, where the load energizes a certain time *after* the toggle switch is closed. Also explain the purpose of the RC network formed by  $C_2$  and  $R_4$ .

$\underline{\text{file } 03222}$

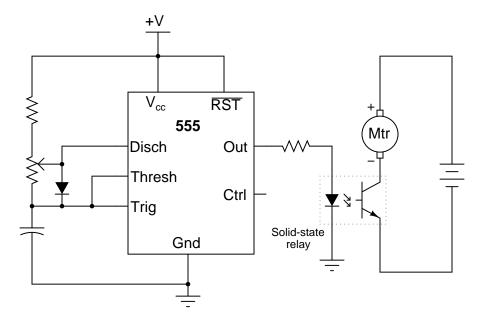

Pulse Width Modulation, or PWM, is a very popular means of controlling power to an electrical load such as a light bulb or a DC motor. With PWM control, the duty cycle of a high-frequency digital (on/off) signal is varied, with the effect of varying power dissipation at the load:

One of the major advantages to using PWM to proportion power to a load is that the final switching transistor operates with minimal heat dissipation. If we were to use a transistor in its linear ("active") mode, it would dissipate far more heat when controlling the speed of this motor! By dissipating less heat, the circuit wastes less power.

Explain why the power transistor in this circuit runs cooler when buffering the PWM signal from the 555 timer, rather than if it were operated in linear mode. Also, identify which direction the potentiometer wiper must be moved to increase the speed of the motor.

Challenge question: suppose we needed to control the power of a DC motor, when the motor's operating voltage was far in excess of the 555 timer's operating voltage. Obviously, we need a separate power supply for the motor, but how would we safely interface the 555's output with the power transistor to control the motor speed? Draw a schematic diagram to accompany your answer.

file 01436

It is common to see a capacitor connected between the "Control" terminal and ground in 555 timer circuits, especially when precise timing is important.

Explain what purpose the capacitor  $C_2$  serves in this circuit. file 01434

### Question 92

Special integrated circuits called *delay elements* or *delay gates* are manufactured to provide nanoseconds' worth of intentional time delays in digital circuits. Identify a part number for such an IC, research its datasheet, and describe an application where one might be needed.

file 02945

# ${\it Question}~93$

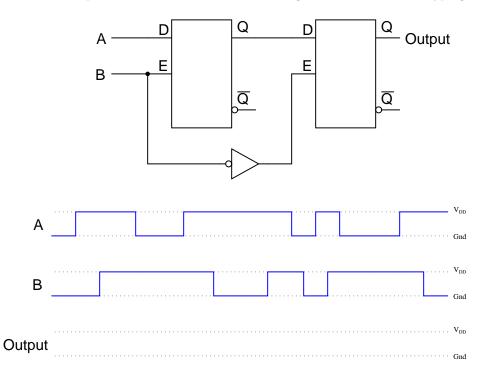

Determine the final output states over time for the following circuit, built from D-type gated latches:

At what specific times in the pulse diagram does the final output assume the input's state? How does this behavior differ from the normal response of a D-type latch?  $\frac{file \ 01363}{file \ 01363}$

# Question 94

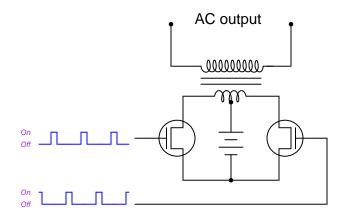

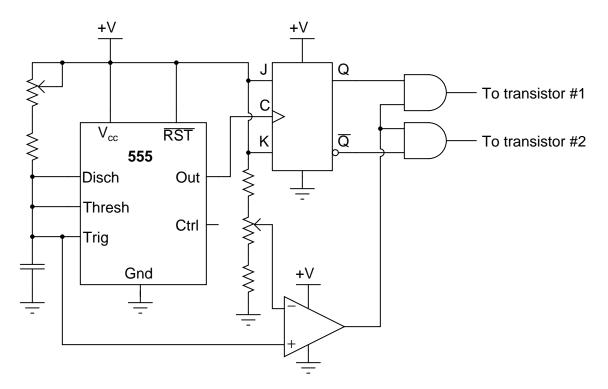

A common topology for DC-AC power converter circuits uses a pair of transistors to switch DC current through the center-tapped winding of a step-up transformer, like this:

Note: protective devices to guard against transient overvoltages have been omitted from this diagram for simplicity!

In order for this form of circuit to function properly, the transistor "firing" signals must be precisely synchronized to ensure the two are never turned on simultaneously. The following schematic diagram shows a circuit to generate the necessary signals:

Explain how this circuit works, and identify the locations of the frequency control and pulse duty-cycle control potentiometers.

file 03452

# Question 95

Although the *toggle* function of the J-K flip-flop is one of its most popular uses, this is not the only type of flip-flop capable of performing a toggle function. Behold the surprisingly versatile D-type flip-flop configured to do the same thing:

Explain how this circuit performs the "toggle" function more commonly associated with J-K flip-flops.  $\underline{fle}~03453$

## Answer 1

The first circuit will "latch" in whatever logic state it powers up in. The second circuit will be "set" or "reset" according to which pushbutton switch is actuated, then latch in that state when neither switch is being pressed. The resistor prevents the gate from "seeing" a short circuit at its output when a pushbutton switch is actuated to change states.

Challenge question: how would you determine an appropriate size for the resistor? Don't just guess – base your answer on specific performance parameters of the gate!

#### Answer 2

A latch is considered set when its output (Q) is high, and reset when its output (Q) is low.

Answer 3

| Set | Reset Q |       | Q |

|-----|---------|-------|---|

| 0   | 0       | Latch |   |

| 0   | 1       | 0     | 1 |

| 1   | 0       | 1     | 0 |

| 1   | 1       | 0     | 0 |

Follow-up question: The final state of this truth table (where the "Set" and "Reset" inputs are both high) is usually referred to as *invalid*. Explain why.

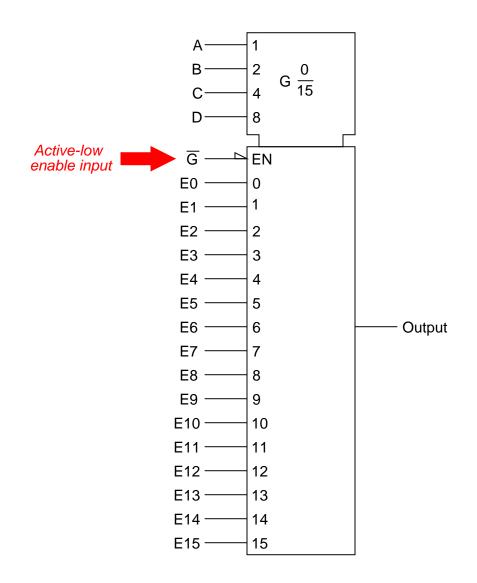

An "active-low" input is one where that particular gate function is activated or invoked on a *low* logic state. Active-low inputs are identified by inversion bubbles (or inversion wedges) drawn at the IC input terminals. For example, the Enable input (EN) for the following integrated circuit is active-low, meaning the chip is enabled when that input line is held at ground potential:

This S-R latch circuit has active-low preset ( $\overline{PRE}$ ) and clear ( $\overline{CLR}$ ) inputs, meaning the latch circuit will be preset and cleared when each of these inputs are grounded, respectively:

Active-high inputs, conversely, engage their respective functions when brought to power supply rail  $(V_{DD} \text{ or } V_{CC})$  potential. As one might expect, an active-high input will *not* have an inversion bubble or wedge next to the input terminal.

Challenge question: to the surprise of many students, there are a great number of digital logic circuit types built with active-low inputs. Explain why. Hint: most of these circuit types and functions were pioneered with TTL logic rather than CMOS logic.

Follow-up question: why are the inputs referred to as  $\overline{\text{Set}}$  and  $\overline{\text{Reset}}$ , rather than just Set and Reset?

## Answer 6

This is a bit of a trick question. If NOR and NAND are the only gate choices available, then the left latch is made from NOR gates and the right latch is made from NAND gates. However, it is possible to make S-R latches out of gates other than NOR or NAND.

Challenge question: can you think of other gate types that could be used to build S-R latch circuits? Hint: there are at least *two* alternatives to NOR and NAND!

Follow-up question: why is the "Stop" switch always normally-closed in motor control circuits, whether it be relay logic or semiconductor logic? It is easy enough to invert a signal if we wish to, either by using a relay or by using a NOT gate, so shouldn't the choice of switch "normal" status be arbitrary?

Challenge question: why not operate the electric motor off the same  $V_{DD}$  power source that the gates are powered by? If we had to do such a thing, what circuit additions would you propose to minimize any potential trouble?

#### Answer 8

The "latching" ability of the S-R latch circuit holds the output state steady during the mechanical switch's bouncing action, allowing a "clean" output transition to take place.

Connecting the input probe of an oscilloscope to either the S or R input of the latch will show bounce, if it occurs. To capture this event, the 'scope would have to be configured for single-sweep mode, and have the triggering controls properly set. A digital storage oscilloscope is essential for this type of work!

Follow-up question: how do you suggest choosing appropriate pull-down resistor sizes for this circuit, or any CMOS circuit for that matter?

Follow-up question: complete a schematic diagram showing how the  $\overline{Q}$  output of the latch could turn on an electric motor through a bipolar junction transistor. Also, determine whether the latch circuit would be *sourcing* or *sinking* current to the transistor when the motor is running:

## Answer 10

The circuit is fine, and working properly. The normal power-up state of a latch circuit is unpredictable, so long as both the inputs are inactive.

## Answer 11

Whether the variable in question is increasing or decreasing over time, the expression  $e^{-\frac{t}{\tau}}$  describes the percentage that a variable has left to change before it reaches its final value.

Follow-up question: what could you add to or modify about the expression to make it describe the percentage that a variable has already changed from its initial value? In other words, alter the expression so that it is equal to 0% at t = 0 and approaches 100% as t grows larger  $(t \to \infty)$ .

$E_C = 3.537$  volts @ t = 9 seconds.

9 s = 1.915 time constants  $(1.915\tau)$

# Answer 13

0.591 seconds

Answer 14

| $V_C$    | Time             |

|----------|------------------|

| 0 volts  | 0  ms            |

| 10 volts | 297.5 ms         |

| 20 volts | 716.7 ms         |

| 30 volts | 1.433 s          |

| 40 volts | $> 5 \mathrm{s}$ |

Answer 15

| $V_C$    | Time                |

|----------|---------------------|

| 10 volts | $588.9 \mathrm{ms}$ |

| 8 volts  | 1.31 s              |

| 6 volts  | 2.24 s              |

| 4 volts  | $3.55 \mathrm{~s}$  |

| 2 volts  | $5.79 \mathrm{~s}$  |

When the output is high, the capacitor is charging through the two resistors, its voltage increasing. When the output is low, the capacitor is discharging through one resistor, current sinking through the 555's "Disch" terminal.

Follow-up question: algebraically manipulate the equation for this astable circuit's operating frequency, so as to solve for  $R_2$ .

$$f = \frac{1}{(\ln 2)(R_1 + 2R_2)C}$$

Challenge question: explain why the duty cycle of this circuit's output is always greater than 50%.

Answer 17

$$t_{charge} = -\ln 0.5(R_1 + R_2)C$$

$$t_{discharge} = -\ln 0.5R_2C$$

#### Answer 18

The diode allows part of the potentiometer's resistance to be bypassed during the capacitor's charging cycle, allowing (potentially) less resistance in the charging circuit than in the discharging circuit.

To decrease the duty cycle, move the wiper up (toward the fixed resistor, away from the capacitor).

Challenge question: write an equation solving for the average current drawn by the 555 timer circuit as it charges and discharges the capacitor while generating a 50% duty cycle pulse. Assume that no current is drawn from the power supply by the circuit while the capacitor is discharging, and use this approximation of the capacitor "Ohm's Law" equation for figuring average current through the charge cycle:

$$i = C \frac{dv}{dt}$$

True "Ohm's Law" for a capacitor

$I_{avg} = C \frac{\Delta V}{\Delta t}$  Capacitive "Ohm's Law" solving for *average* current

Answer 19

The triggering pulse must dip below  $\frac{1}{3}$  of the supply voltage in order to initiate the timing sequence.

$$t_{pulse} = 1.1RC$$

#### Answer 20

Each 555 timer's cycle is triggered by the negative edge of the pulse on the *trigger* terminal. A passive differentiator network between each 555 timer ensures that only a brief negative-going pulse is sent to the trigger terminal of the next timer from the output terminal of the one before it.

Follow-up question: when timer circuits are cascaded like this, do their time delays *add* or *multiply* to make the total delay time? Be sure to explain your reasoning.

When the Enable input is low (0), the circuit ignores the Set and Reset inputs:

| Е | S | R | Q     | Q |

|---|---|---|-------|---|

| 0 | 0 | 0 | Latch |   |

| 0 | 0 | 1 | Latch |   |

| 0 | 1 | 0 | Latch |   |

| 0 | 1 | 1 | Latch |   |

| 1 | 0 | 0 | Latch |   |

| 1 | 0 | 1 | 0     | 1 |

| 1 | 1 | 0 | 1     | 0 |

| 1 | 1 | 1 | 0     | 0 |

Answer 22

Follow-up question: explain why the inputs to the latch circuit are not active-low as they were before the addition of the two extra NAND gates. In other words, why does this latch now have S and R inputs rather than  $\overline{S}$  and  $\overline{R}$  inputs as it did before?

The "Lockout" switch effectively disables the "On" and "Off" controls when it sends a "low" signal to the latch's Enable input.

This circuit uses both a solid-state relay (SSR) and an electromechanical relay for interposing between the latch and the lamp. These devices allow the low-power latch circuit to exert control over the high-power lamp.

Here is one possibility for the door lock control:

Follow-up question: there are better (safer) ways to accomplish this same function. For instance, suppose the TRIAC inside the SSR were to fail shorted, maintaining power to the lamp even when the latch goes into the "reset" mode. Would the door-lock logic shown here prevent someone from opening the door and getting exposed to the strong ultraviolet light? Explain your answer!

Challenge question: why not just use one interposing device: either an SSR, or an electromagnetic relay? Why *both* types of devices in the same circuit?

Follow-up question: complete a schematic diagram showing how this latch circuit could turn a motor on and off through a MOSFET.

Also, comment on whether your MOSFET sources current to the motor or sinks current from the motor.

When the Sample/Hold switch is in the "low" position, the D latches all fall into the "latch" state, holding that last valid input states on their Q outputs.

# Answer 28

Inputs C1 and C2 perform the standard "Enabling" function for the D-type latches within this integrated circuit. The 1EN and 2EN inputs control the tri-state outputs. Their "wedge" symbols mean "complemented," and are equivalent to the "bubbles" seen on traditional gate symbols.

To make all sixteen latches enable and disable as one, bridge the enable inputs as such:

Left-to-right is the correct driving direction for this street.

If sensor A's light source fails, the alarm will never activate. A failed light source for sensor B will have different effects on the system, depending on whether sensor A was sending a "high" or a "low" signal to the latch circuit at the time B's light source failed. I'll let you figure out which way triggers the alarm!

Follow-up question: describe exactly what conditions are necessary to obtain a "high" signal from the output of this circuit, and what determines the duration of this "high" pulse.

#### Answer 32

I'll leave the experimental design details up to you. However, I will tell you that you do not necessarily have to use a digital storage oscilloscope to "capture" a transient waveform to measure propagation delay, if you apply a little creativity. Hint: use a signal generator to send a high-frequency square wave to the gate of your choice, and use a non-storage oscilloscope to monitor the results.

And yes, electromechanical relays also have intrinsic delay times, which tend to be *far* greater than those encountered with semiconductor logic gates.

90

Follow-up question: one of these circuits is referred to as *edge-triggered*. Which one is it?

Challenge question: in reality, the output waveforms for both these scenarios will be shifted slightly due to propagation delays within the constituent gates. Re-draw the true outputs, accounting for these delays.

## Answer 34

A "flip-flop" is a latch that changes output only at the rising or falling edge of the clock pulse.

## Answer 35

The outputs of this device are allowed to change state only when the "clock" signal (C) is transitioning from low to high:

| С | S | R | Q       | IQ |

|---|---|---|---------|----|

| F | 0 | 0 | Latch   |    |

| F | 0 | 1 | 0       | 1  |

| F | 1 | 0 | 1       | 0  |

| F | 1 | 1 | Invalid |    |

Challenge question: what exactly happens in the "invalid" state for this S-R flip-flop?

#### Answer 36

For the S-R gated latch:

- Set by making S high, R low, and E high.

- Reset by making R high, S low, and E high.

For the S-R flip-flop:

- Set by making S high, R low, and C transition from low to high.

- Reset by making R high, S low, and C transition from low to high.

Answer 38

| С | J | Κ | Q      | lq |

|---|---|---|--------|----|

| ₽ | 0 | 0 | Latch  |    |

| ₽ | 0 | 1 | 0      | 1  |

| ₽ | 1 | 0 | 1      | 0  |

| ₽ | 1 | 1 | Toggle |    |

Follow-up question: comment on the difference between this truth table, and the truth table for an S-R flip-flop. Are there any operational advantages you see to J-K flip-flops over S-R flip-flops that makes them so much more popular?

In either case, you cause the flip-flop to go into these three modes by doing the following:

- Set by activating J, deactivating K, and clocking C.

- Reset by activating K, deactivating J, and clocking C.

- Toggle by *activating* J and K simultaneously, and *clocking* C.

Specifically, though, here is what you would need to do to each flip-flop, stated in terms of "high" and "low" logic states:

For the J-K flip-flop with active-high inputs:

- Set by making J high, K low, and C transition from low to high.

- Reset by making K high, J low, and C transition from low to high.

- Toggle by making J high, K high, and C transition from low to high.

For the J-K flip-flop with active-low inputs:

- Set by making K high, J low, and C transition from high to low.

- Reset by making J high, K low, and C transition from high to low.

- Toggle by making J low, K low, and C transition from high to low.

Answer 40

"Asynchronous" inputs force the outputs to either the "set" or "reset" state independent of the clock. "Synchronous" inputs have control over the flip-flop's outputs only when the clock pulse allows.

As for why the asynchronous inputs are active-low, I won't directly give you the answer. But I will give you a hint: consider a *TTL* implementation of this flip-flop.

## Answer 44

The flip-flop becomes "set" every time a pulse comes from the sensor. The microprocessor must clear the flip-flop after reading the captured pulse, so the flip-flop will be ready to capture and hold a new pulse.

Challenge question: what logic family of flip-flop would you recommend be used for this application, given the need for extremely fast response? Don't just say "TTL," either. Research the fastest modern logic family in current manufacture!

## Answer 45

The operation of this circuit is quite easy to understand if you draw a pulse diagram for it and analyze the flip-flop's output over time. When the encoder disk spins clockwise, the Q output goes high; when counterclockwise, the Q goes low.

Follow-up question: comment on the notation used for this circuit's output. What does the label  $"CW/\overline{CCW}"$  tell you, without having to analyze the circuit at all?

$f_{out} = 120 \text{ Hz}$

Follow-up question: how could you use another flip-flop to obtain a square-wave signal of 60 Hz from this circuit?

## Answer 48

The clock frequency must be slow enough that there is adequate *set-up time* before the next clock pulse. The *propagation delay time* of FF1 must also be larger than the *hold time* of FF2. And, of course, the pulse width of the clock signal must be long enough for both flip-flops to reliably "clock."

# Answer 49

I'll let you do the research on this question!

#### Answer 50

With all inputs tied together, there is zero setup time on the J and K inputs before the clock pulse rises.

#### Answer 51

Use circuit simulation software to verify your predicted and actual truth tables.

## Answer 52

Use circuit simulation software to verify your predicted and measured parameter values.

#### Answer 53

Use circuit simulation software to verify your predicted and actual truth tables.

#### Answer 54

Use circuit simulation software to verify your predicted and measured parameter values.

I do not provide a grading rubric here, but elsewhere.

#### Answer 56

Be sure to document all steps taken and conclusions made in your troubleshooting!

### Answer 57

- Resistor  $R_3$  failed open.

- NOR gate  $U_1$  output failed low.

- Resistor  $R_1$  failed open (provided enough ambient electrical noise to activate a floating gate input).

- "Set" switch contacts failed shorted.

#### Answer 58

- NOR gate  $U_2$  output failed high.

- Wire break between "Reset" switch and resistor  $R_2$  (although if this was the only fault it may allow the Q LED to energize at power-up, just not de-energize after the "Set" button had been pressed).

Follow-up question: explain why the nature of the problem rules out the possibility of the only fault being something related to the feedback connections between  $U_1$  and  $U_2$ .

Answer 59

- Resistor R<sub>1</sub> fails open: Capacitor voltage holds at last value, output voltage holds at last value.

- Solder bridge (short) across resistor R<sub>1</sub>: Timer IC will become damaged at the first discharge cycle.

- Resistor R<sub>2</sub> fails open: Capacitor voltage holds at last value, output voltage holds at last value.

- Solder bridge (short) across resistor R<sub>2</sub>: Oscillation frequency nearly doubles, and the duty cycle increases to nearly 100%.

- Capacitor C<sub>1</sub> fails shorted: Capacitor voltage goes to 0 volts DC, output voltage stays "high".

### Answer 60

- Transistor  $Q_1$  fails open (collector-to-emitter): Lamp remains off, no current through any terminal of  $Q_2$ .

- Transistor  $Q_2$  fails open (collector-to-emitter): Lamp remains off, no current through any terminal of  $Q_2$ , normal base current through  $Q_1$ , no current through collector of  $Q_1$ .

- Resistor  $R_3$  fails open: Lamp remains off, no current through any terminal of  $Q_1$  or  $Q_2$ .

- Transistor  $Q_1$  fails shorted (collector-to-emitter): Lamp remains on, full "on" current levels through terminals of  $Q_1$  and  $Q_2$ .

The addition of a resistor between the Control terminal and ground would increase the frequency of the circuit, as well as decrease the peak-to-peak amplitude of the "sawtooth" wave signal across the timing capacitor.

Follow-up question: does the addition of this resistor affect the output signal (pin 3) amplitude as well? Explain why or why not. If it amplitude is affected, does it increase or decrease with the resistor in place?

#### Answer 62

I won't reveal the most probable cause, but I will give you this hint: the TLC555CP integrated circuit ("chip") uses CMOS technology.

## Answer 63

- Resistor  $R_1$  failed open.

- Solder bridge past resistor  $R_2$ .

- No power to either 555 timer IC.

#### Answer 64

- Resistor  $R_1$  fails open: Lamp status does not change.

- Resistor  $R_3$  fails open: Lamp status does not change.

- Diode  $D_1$  fails open: Circuit works fine for a few cycles, then fails with the lamp either remaining on or remaining off (due to failed transistor  $Q_2$ ).

- Transistor  $Q_2$  fails shorted between collector and emitter: Lamp remains on.

- Solder bridge past resistor  $R_5$ : Possible failure of flip-flop  $U_2$  or transistor  $Q_2$  after extended periods of time with the lamp on.

#### Answer 65

- Phototransistor  $Q_1$  failed shorted.

- Resistor  $R_2$  failed open.

- Flipflop  $U_1$  output failed high.

Follow-up question: explain why the presence of ambient light near the phototransistors could also cause this problem to occur.

## Answer 66