## SATURN V

Simplex Models

# Laboratory Maintenance Instructions for LVDA

Volume I

Description and Theory

| NASA-CE-124311) LABORATORY MAINTENANCE                                                                                                                                                          |       | N73-73558       |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|--|

| NASA-CR-124311) LABORATORY HAINIBURGE<br>INSTRUCTIONS: SATURN 5 LAUNCH VEHICLE<br>DATA ADAPTER. SIMPLEX MODELS: NASA<br>PART NO. 50M35011, PBM (International<br>Business Machines Corp.) 140 p | 00/99 | Unclas<br>15135 |  |

Space Guidance Center, Owego, New York

MAY 9 1965

## **VOLUME I OF II**

Laboratory Maintenance Instructions

## SATURN V

## LAUNCH VEHICLE DATA ADAPTER

Simplex Models

NASA Part No. 50M35011 IBM Part Nos. 6112050 and 6112070

International Business Machines Corporation

Contract NAS 8-11561

## · VOLUME | OF - II-

## **GENERAL DESCRIPTION AND THEORY**

**26 FEBRUARY 1965**

Technical Library, Bellcomm, Inc.

## LIST OF EFFECTIVE PAGES

#### INSERT LATEST CHANGED PAGES. DESTROY SUPERSEDED PAGES.

## TOTAL NUMBER OF PAGES IN VOLUME I, OF THIS PUBLICATION IS 140 CONSISTING OF THE FOLLOWING:

| Page No.        | Issue    |

|-----------------|----------|

| Title           | Original |

| A               | Original |

| i               |          |

| ii Blank        |          |

| iii thru v      |          |

| vi Blank        |          |

| vii thru viii   |          |

| 1-1 thru 1-13   | Original |

| 1-14 Blank      | Original |

| 2-1 thru 2-68   |          |

| Glossary-1      | U        |

| thru -16        | Original |

| Symbols-1       | -        |

| thru -30        | Original |

| Index-1 thru -2 | Original |

Α

\*The asterisk indicates pages changed, added, or deleted by the current change.

#### NOTICE

Section V of this manual includes procedures which require the use of the Purging Cart (Tool Number 657900) and the Transport Dolly (Tool Number 656360). As of the publication date of this manual, this equipment has not been delivered; therefore the procedures cannot be performed. Although the procedures have not been verified on the equipment they have been included in the manual for informational purposes.

•

Volume I

| Section | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|

|         | LIST OF RELATED MANUALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>v</b>                        |  |  |

| I       | INTRODUCTION AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-1                             |  |  |

|         | 1-1.Introduction1-2.Scope.1-4.Purpose of Manual1-10.Purpose of Equipment1-14.Structural Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-1<br>1-1<br>1-1<br>1-1<br>1-2 |  |  |

| II      | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-1                             |  |  |

|         | 2-1.       Scope and Purpose         2-3.       Symbols         2-4.       Logic Symbols         2-4.       Logic Symbols         2-6.       Electrical Symbols         2-8.       General Concepts         2-9.       Latches and Tratches         2-19.       Triple Modular Redundancy         2-25.       Power         2-42.       Timing         2-42.       Timing         2-42.       Timing         2-42.       Timing         2-42.       Timing         2-42.       Timing         2-44.       General Description of Functions         2-76.       Delay-Line Registers         2-76.       Delay-Line Registers         2-89.       Computer Output Circuits         2-89.       Computer Output Circuits         2-90.       General         2-910.       Address Decode         2-110.       Data Control Circuit         2-110.       Data Control Circuit         2-113.       Digital-to-Analog (D/A) Converter         2-134.       Digital-to-Analog (D/A) Converter         2-163.       Processors         2-164.       General         2-189. |                                 |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |  |  |

i/ii

٠

Volume I

٩

#### LIST OF ILLUSTRATIONS

| Figure       | Title                                                  | Page           |

|--------------|--------------------------------------------------------|----------------|

| i            | Launch Vehicle Data Adapter                            | viii .         |

| 1-1          | Data Adapter Exploded View                             | 1-2            |

| 1-2          | Page Assembly                                          | 1-4            |

| 1-3          | Typical Panel Assembly                                 | 1-6            |

| 1-4          | Printed Circuit Cables                                 | 1-7            |

| 1-5          | Power-Section-Flange Assemblies                        | 1-8            |

| 1-6          | Mounting Panel                                         | 1-9            |

| 1-7          | Typical Converter-Regulator Assembly                   | 1-10           |

| 1-8          | Typical Distribution Panel (Shown Partially Assembled) | 1-11           |

| 1-9          | Power Section Strut-Mounted Assemblies                 | 1-11           |

| 1-10         | Data Adapter Assemblies                                | 1-12           |

| 1-11         | Data Adapter System Connectors                         | 1-13           |

|              |                                                        | _              |

| 2 - 1        | Basic Latch                                            | 2-2            |

| 2-2          | OR-Extended Latch                                      | 2-3            |

| 2-3          | AND-Extended Latch                                     | 2-4            |

| 2-4          | Exclusive-Zero Tratch                                  | 2-5            |

| 2-5          | Voter Circuits, Block Diagram.                         | 2-5            |

| 2-6          | Power Supply Switching, Simplified Diagram             | 2-7            |

| 2-7          | Memory Driver Relays, Schematic Diagram                | 2-9            |

| 2-8          | Channel Switching Relays                               | 2-10           |

| 2-9<br>2-10  | Channel Switching Inputs                               | $2-11 \\ 2-12$ |

| 2-10<br>2-11 | Discrete Output Driver Relays                          | 2-12<br>2-13   |

| 2-11<br>2-12 | Clock Drivers                                          | 2-13<br>2-14   |

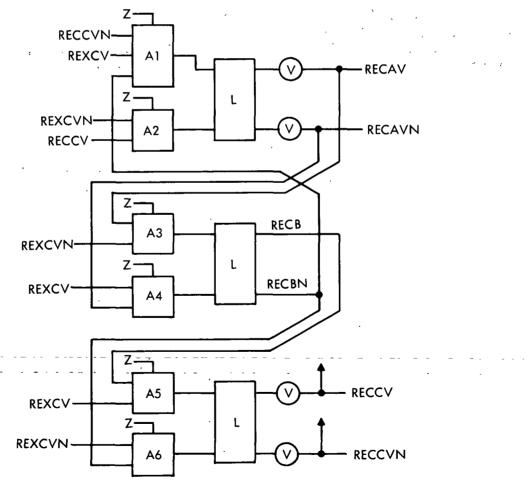

| 2-12<br>2-13 | Control Circuit                                        | 2-14<br>2-15   |

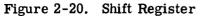

| 2-13<br>2-14 | Shift Register                                         | 2-15<br>2-16   |

| 2-14<br>2-15 | Data Adapter Timing Diagram                            | 2-10<br>2-17   |

| 2-15<br>2-16 | Phase Generator                                        | 2-20           |

| 2-17         | Special Timing Circuits                                | 2-22           |

| 2-18         | Frequency Generator, Block Diagram                     | 2-22           |

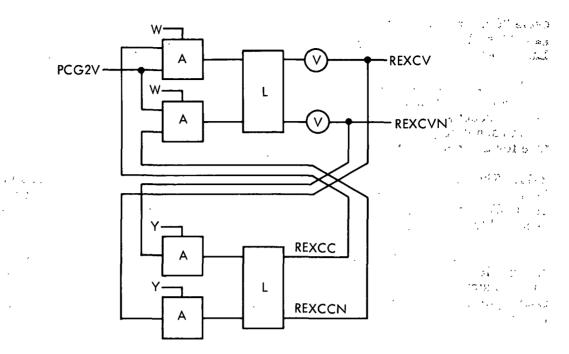

| 2-19         | Control Circuit                                        | 2-23           |

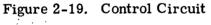

| 2-20         | Shift Register                                         | 2-23           |

| 2-21         | Frequency Generator, Timing Diagram                    | 2-24           |

| 2-22         | Frequency Divider                                      | 2-24           |

| 2-23         | Delay-Line Register Timing                             | 2-25           |

| 2-24         | Delay Line Register                                    | 2-26           |

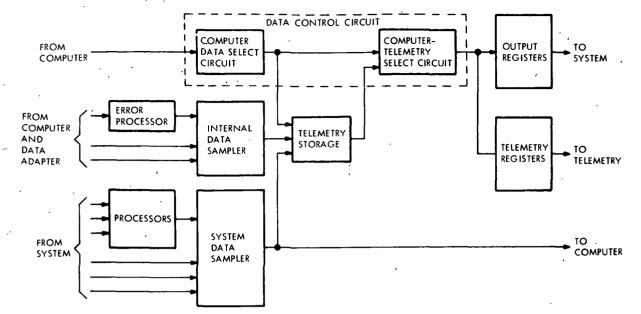

| 2-25         | Data Adapter, Simplified Block Diagram                 | 2-28           |

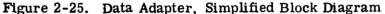

| 2-26         | Data Adapter, Detailed Block Diagram                   | 2-29           |

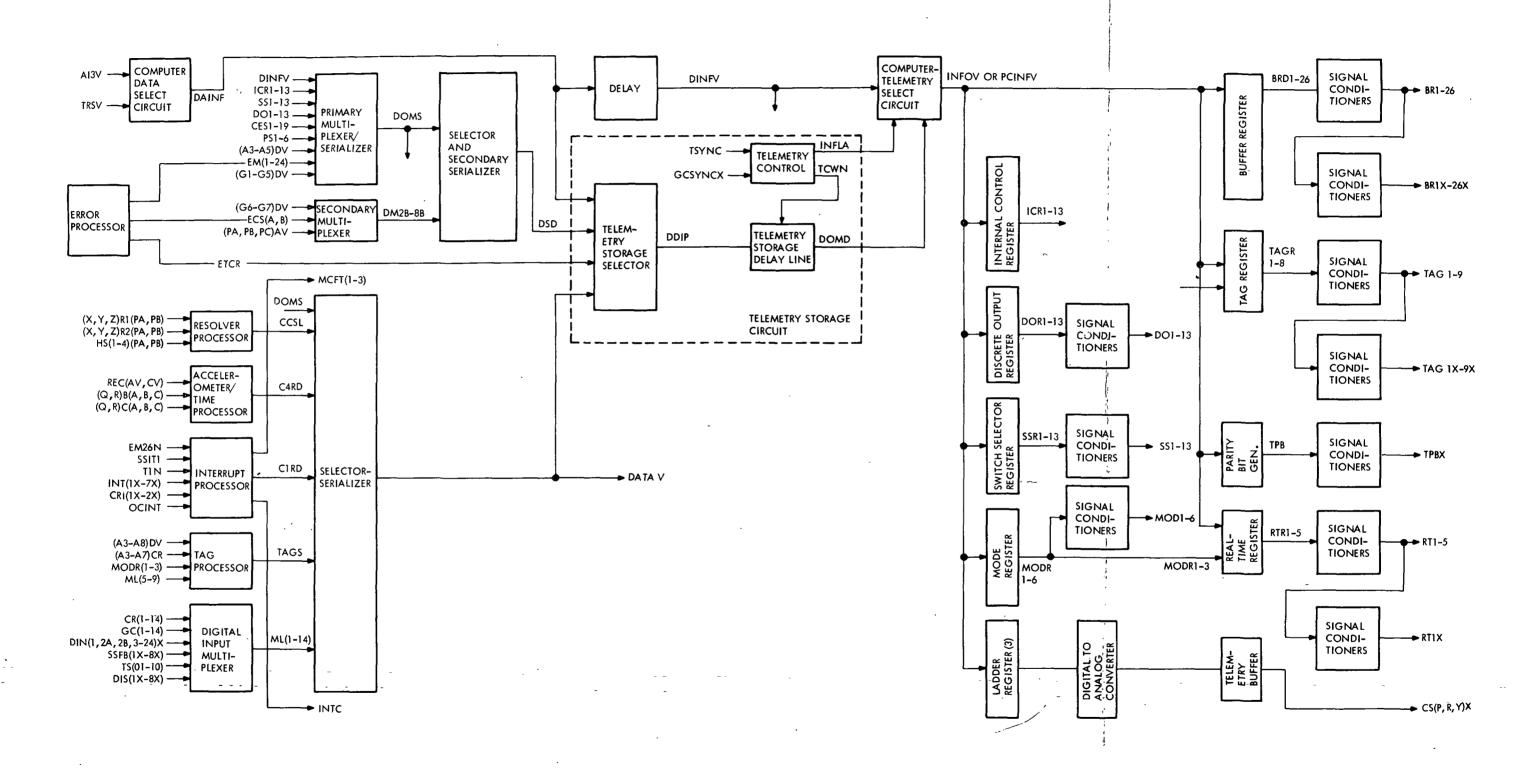

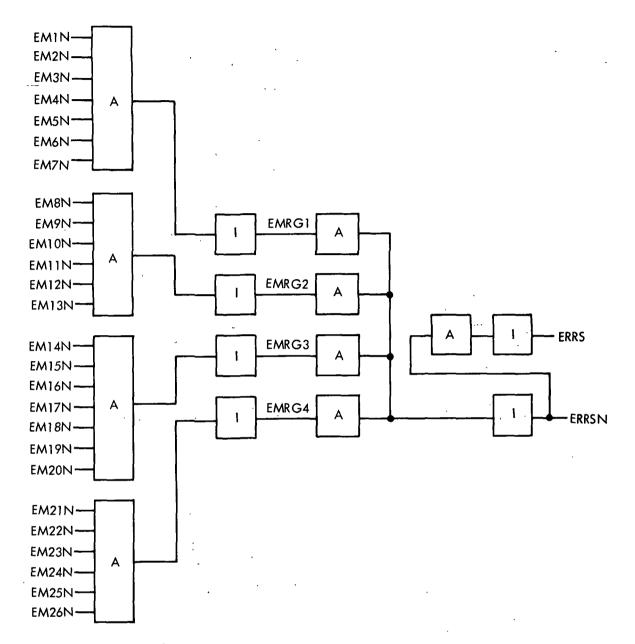

| 2-27         | Error Storage Register                                 | 2-30           |

| 2-28         | Error Or - Circuit                                     | 2-31           |

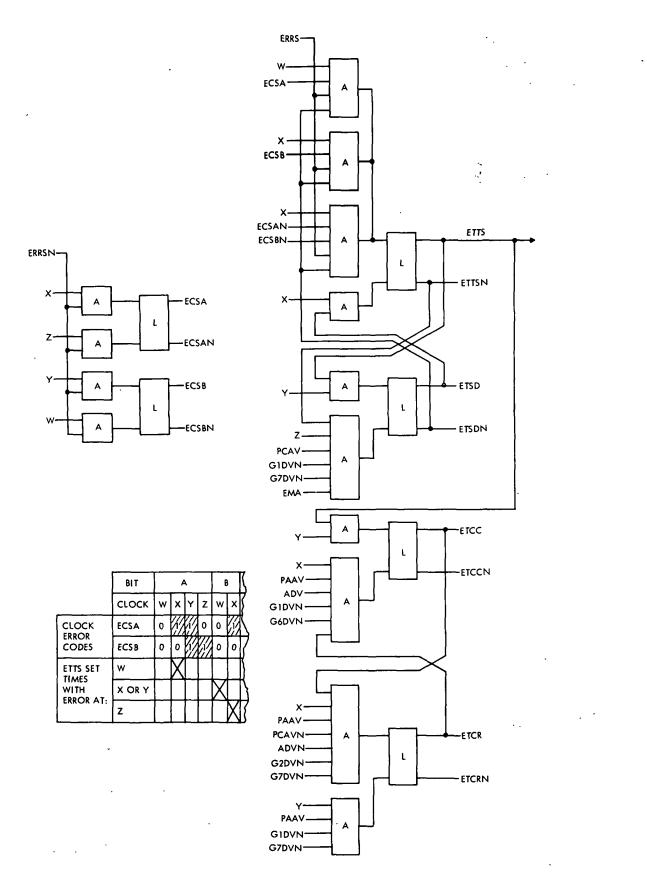

| 2-29         | Error Control Latches                                  | 2-32           |

| 2-30         | Address Group Codes                                    | 2-34           |

| 2-31         | Address Codes                                          | 2-35           |

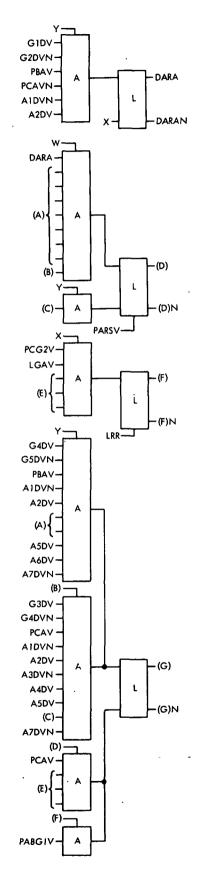

| 2-32         | Address Latches and Control                            | 2-36           |

| 2-33         | Address Group 2 Decoders                               | 2-37           |

| 2-34         | Address Group 4 Decoders                               | 2-38           |

| 2-35         | Address Group 5 Decoders                               | 2-39           |

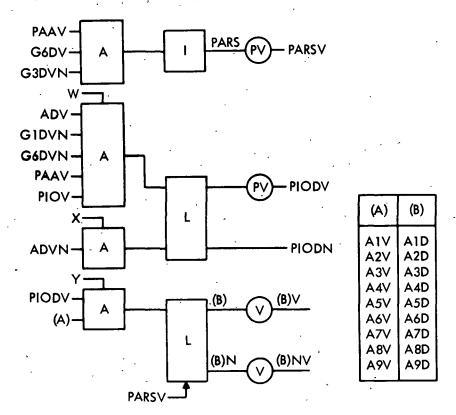

| 2-36         | Data Control Circuit.                                  | 2-40           |

| 2-37         | Internal Control Register, Typical Latch               | 2-41           |

| 2-38         | Discrete Output Register, Typical Latch                | 2-42           |

iii

,

### LIST OF ILLUSTRATIONS (cont)

### Figure

### Title

### Page

| 2-39   | Switch Selector Register, Typical Latch     |            |

|--------|---------------------------------------------|------------|

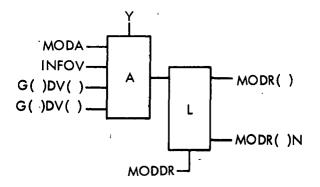

| 2-40   | Mode Register, Typical Latch                |            |

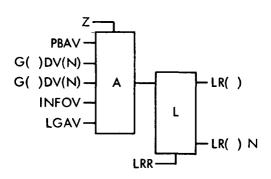

| 2-41   | Ladder Register, Typical Latch              |            |

| 2-42   | Digital-To-Analog Converter                 |            |

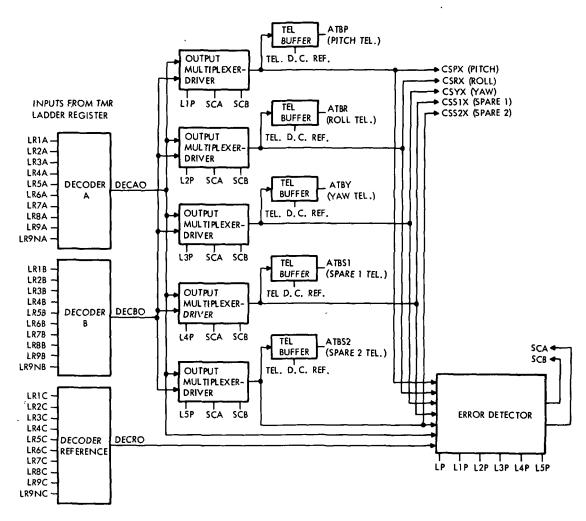

| 2-43   | Ladder Decoder                              |            |

| 2-44   | Current Switching Circuit                   |            |

| 2-45   | Output Multiplexer-Driver                   | 2-47       |

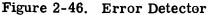

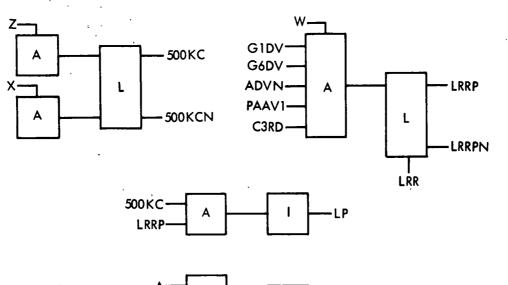

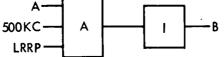

| 2-46   | Error Detector                              | 2-48       |

| 2-47   | D/A Converter Control                       | 2-50       |

| 2-48   | D/A Converter Control                       | 2-50       |

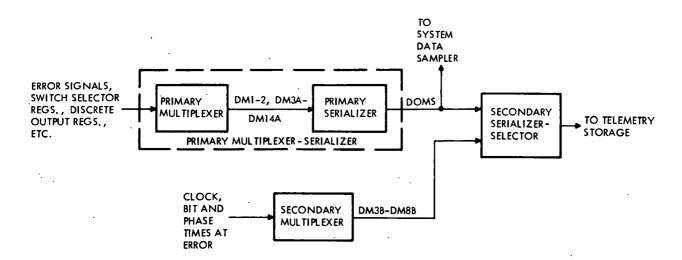

| 2-49   | Typical Primary Multiplexer Latch           | 2-52       |

| 2-50   | Table of Primary Multiplexer Inputs         | 2-53       |

| 2-51   | Primary Serializer                          | 2-54       |

| 2-52   | Primary Serializer Output Format            | 2-54       |

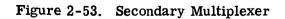

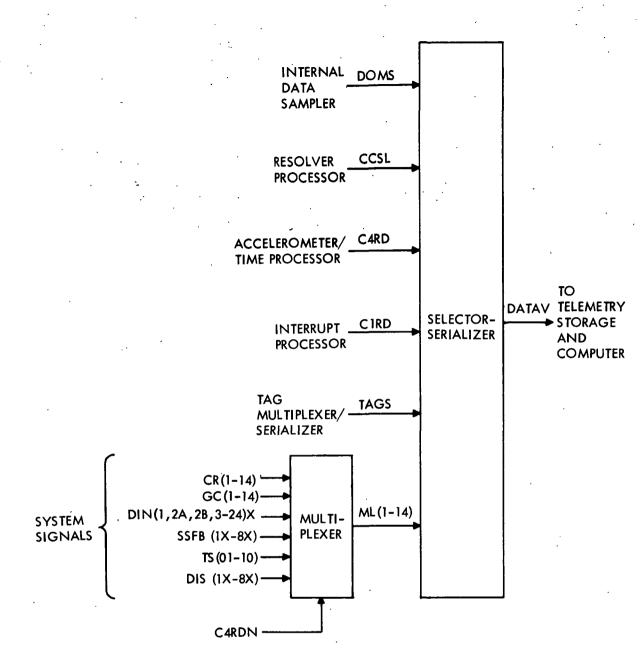

| 2-53   | Secondary Multiplexer                       | 2-54       |

| 2-54   | Secondary Serializer - Selector             |            |

| 2-55   | System Data Sampler                         |            |

| 2-56   | Multiplexer                                 |            |

| 2-57   | Typical Multiplexer Latch                   |            |

| 2-58   | Multiplexer Inputs                          |            |

| 2-59   | Serializer-Selector Inputs                  |            |

| 2-60   | Serializer-Selector Output Format           |            |

| 2-61   | Measuring Phase Shift with A Binary Counter |            |

| 2-62   | Resolver Processor Address Register         |            |

| 2-63   | Counter Start Latch and Control Circuits    |            |

| 2-64   | Counter Stop Latch and Counter Control Gate |            |

|        | •                                           |            |

| A-1    | AND-Gate, Type A                            | Symbols-8  |

| A-2    | AND-Gate, Type AA                           | Symbols-8  |

| A-3    | AND-Gate, Type AB.                          | Symbols-8  |

| A-4    | Analog Telemetry Buffer, ATB                | Symbols-9  |

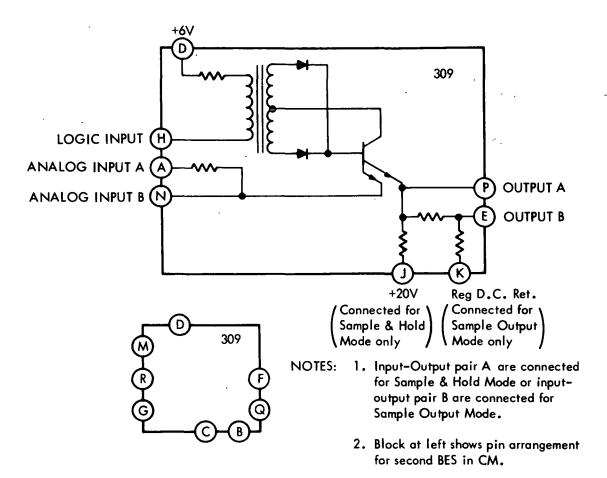

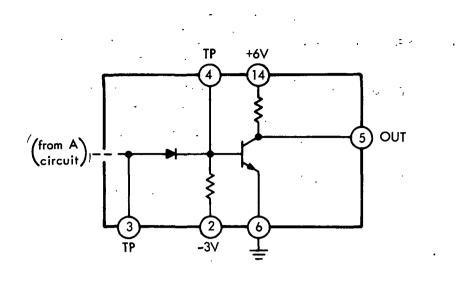

| A-5    | Bipolar Electronic Switch, BES              | Symbols-10 |

| A-6    | Clock Driver, Type 4, CD4                   | Symbols-10 |

| A-7    | Collector Load Network, CLN                 | Symbols-10 |

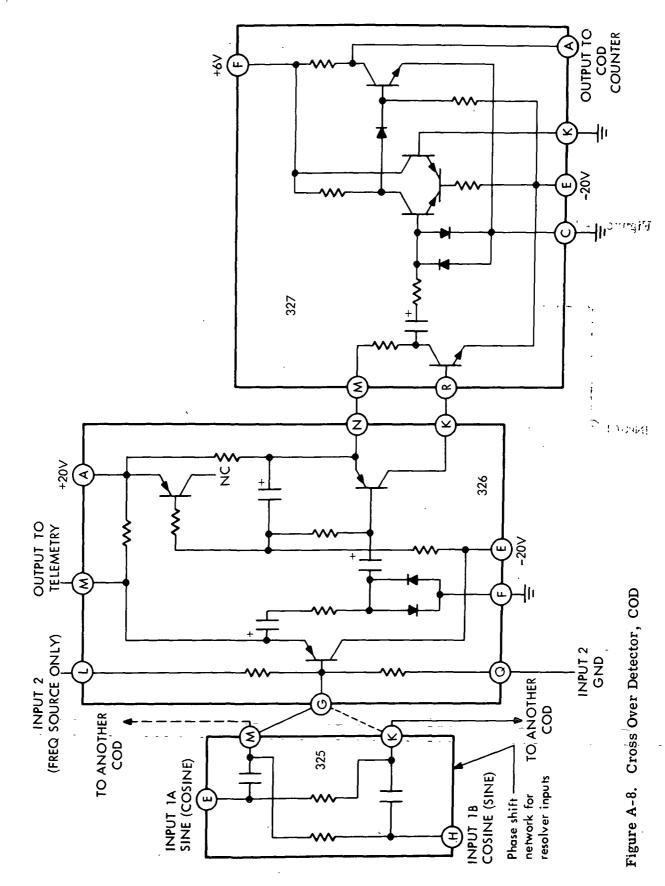

| A-8    | Cross Over Detector, COD                    | Symbols-11 |

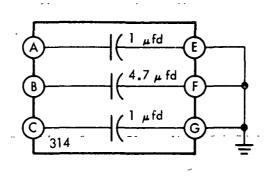

| A-9    | Cordwood Page Decoupling Circuit, CPD       | Symbols-12 |

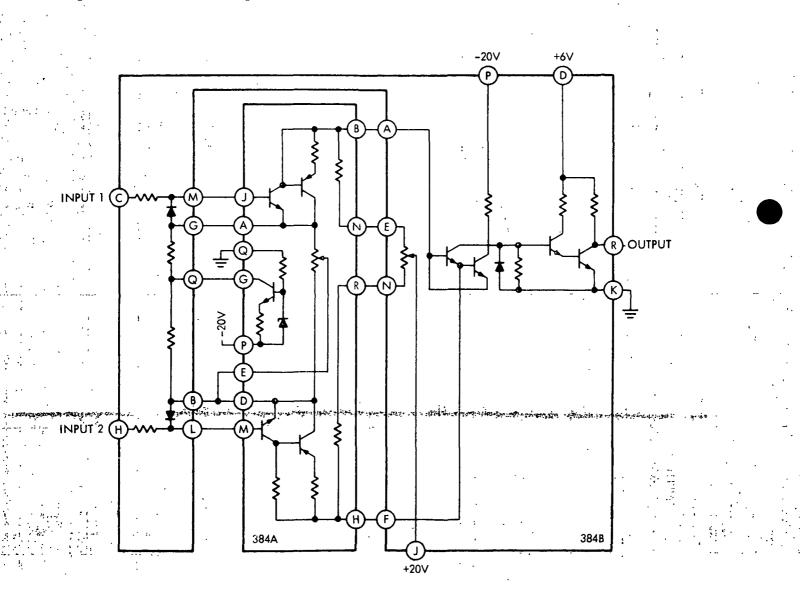

| A-10   | Comparator, CPR                             | Symbols-12 |

| A-11   | Converter Select, CS                        | Symbols-13 |

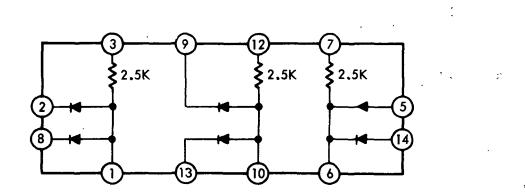

| A-12   | Collector, Transistor, Network, CTW         | Symbols-13 |

| A-13   | Disagreement Detector, DD                   | Symbols-14 |

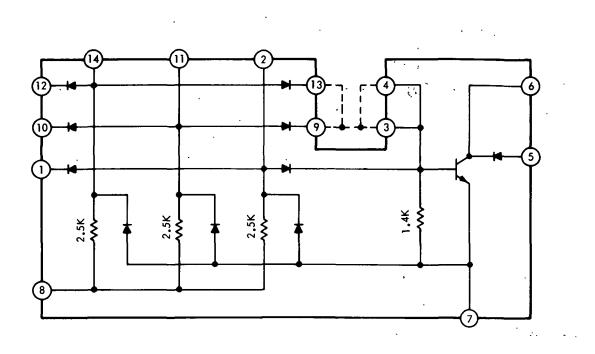

| A-14   | Disagreement Detector Inverter, DDI         | Symbols-14 |

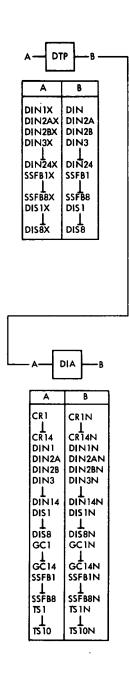

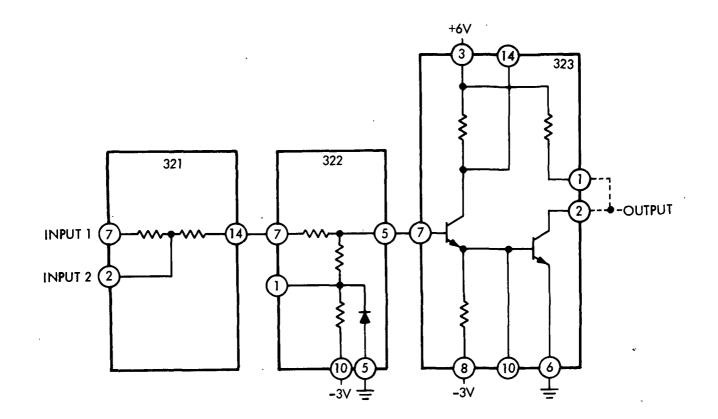

| A-15   | Discrete Input Circuit, Type A, DIA         | Symbols-15 |

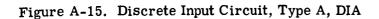

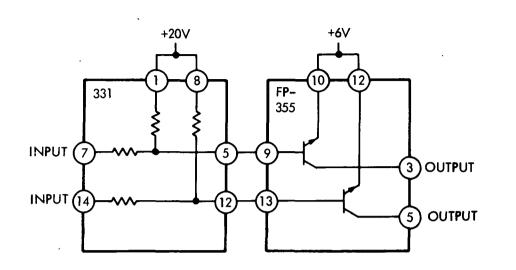

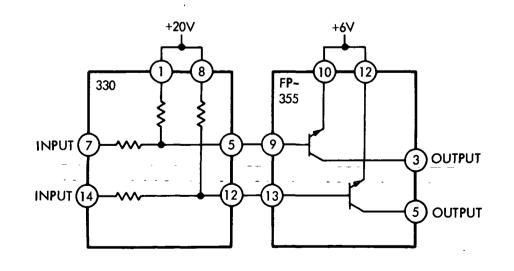

| A-16   | Discrete Input Circuit, Type B, DIB         | Symbols-15 |

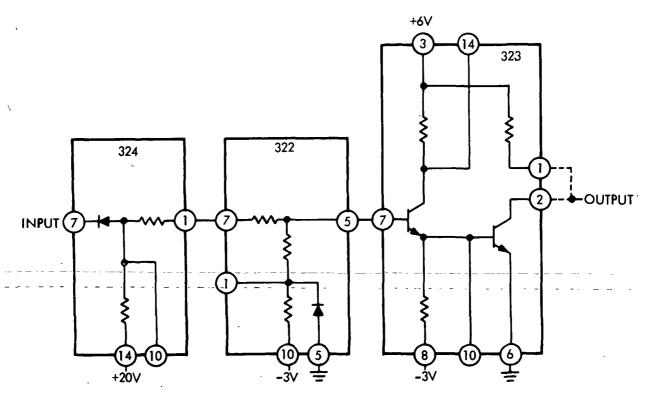

| A-17   | Delay Line Driver, DLD.                     | Symbols-16 |

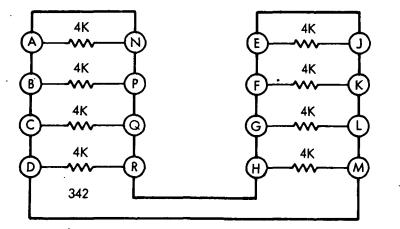

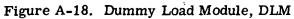

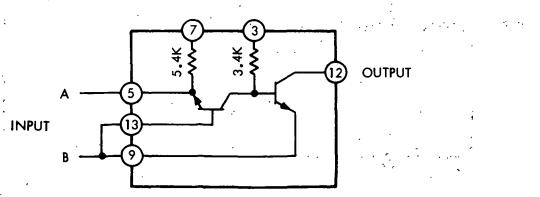

| A-18   | Dummy Load Module, DLM                      | Symbols-16 |

| A-19   | Delay Line Sense Amplifier, DSA             | Symbols-16 |

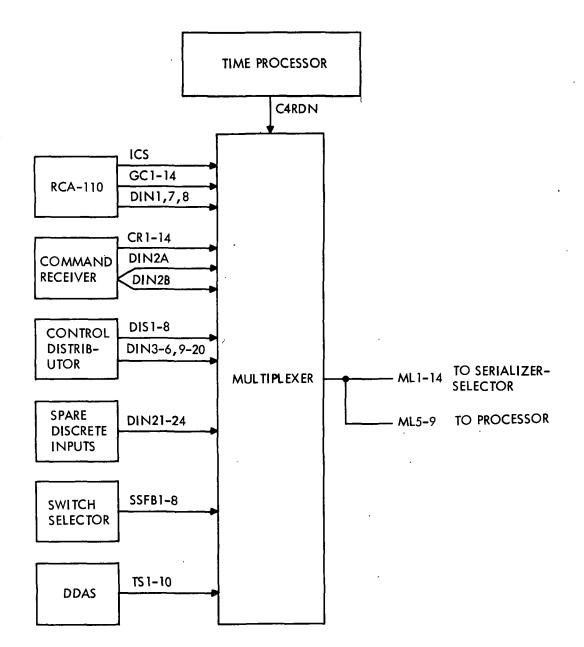

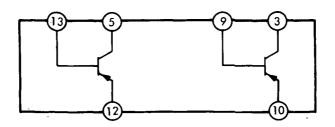

| A - 20 | Discrete Transient Protector, DTP           | Symbols-17 |

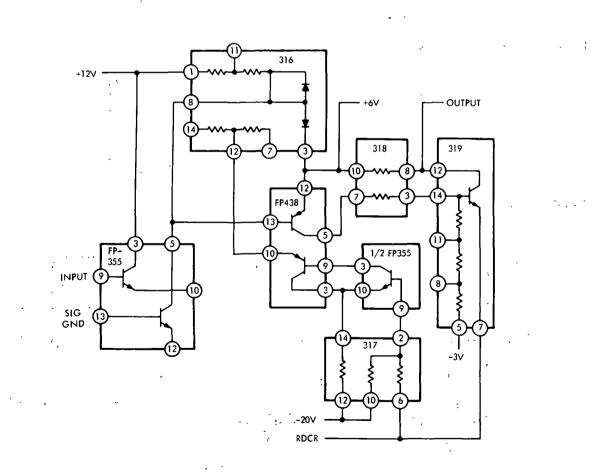

| A-21   | Flat-Pack, Type 355, FP355                  | Symbols-17 |

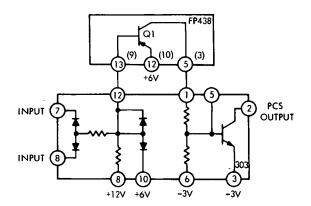

| A-22.  | Flat-Pack, Type 438, FP438                  | Symbols-17 |

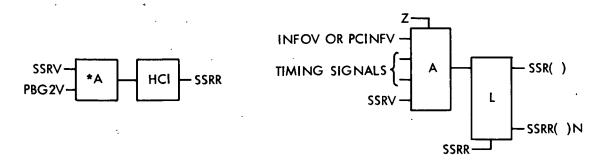

| A-23   | High-Current-Inverter, HCI                  | Symbols-17 |

|        |                                             | J 244      |

.

•

۹

### LIST OF ILLUSTRATIONS (cont)

- -

.

.

| Figure                                                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

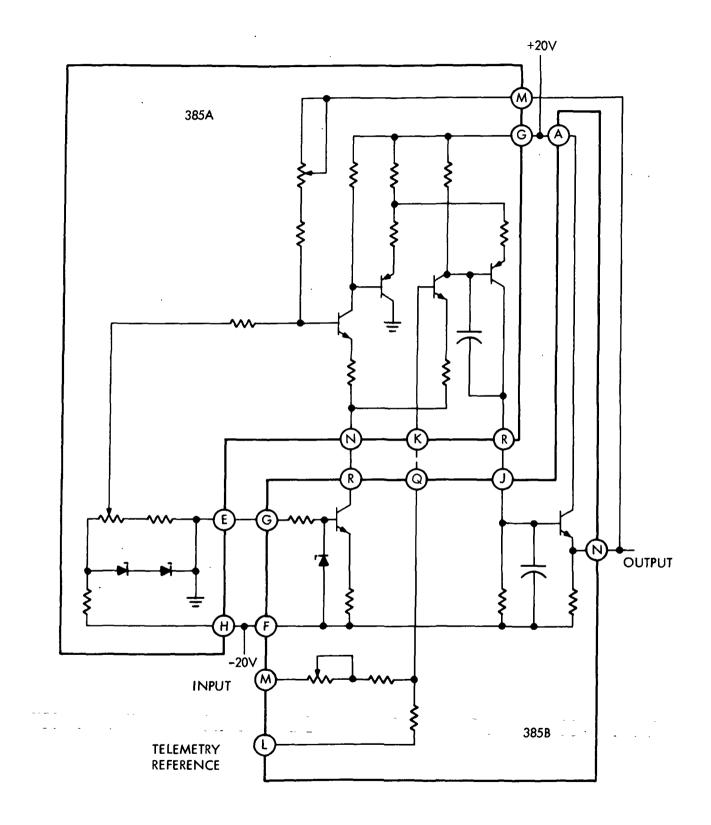

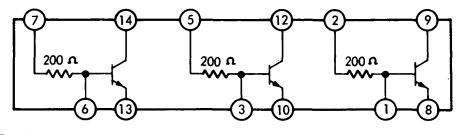

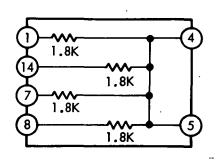

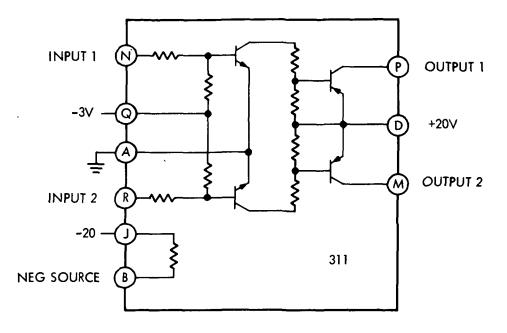

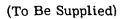

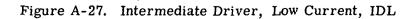

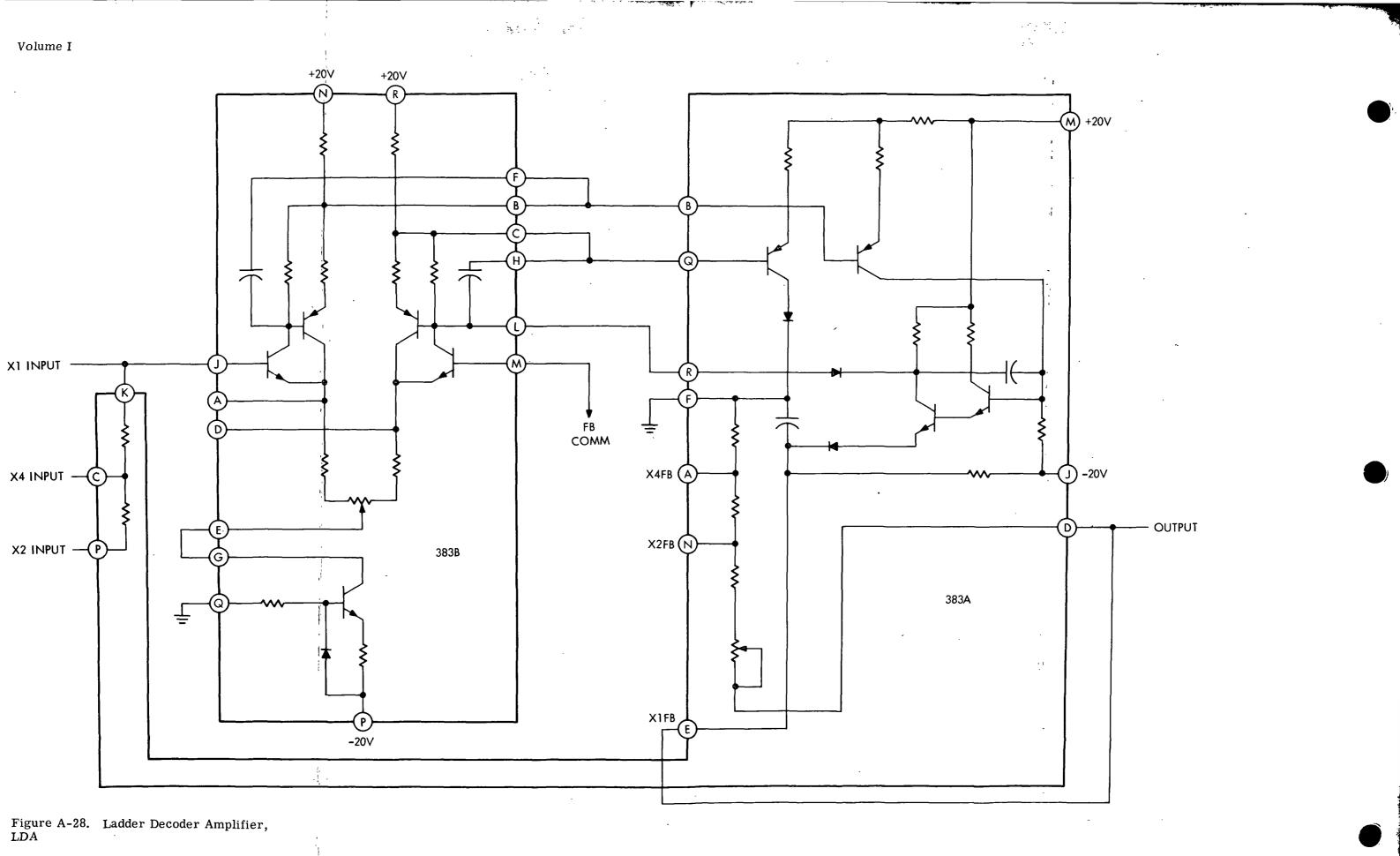

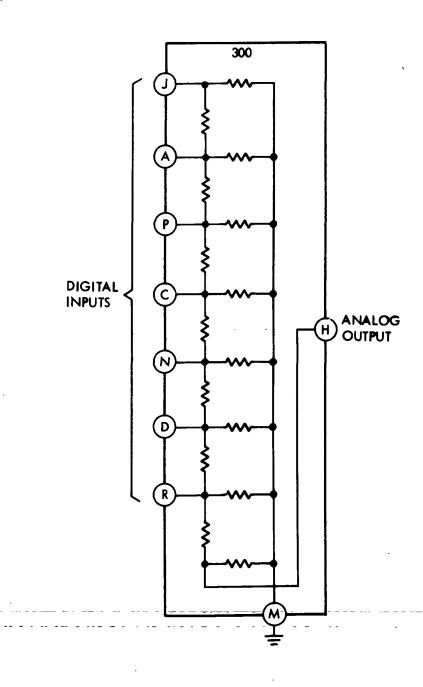

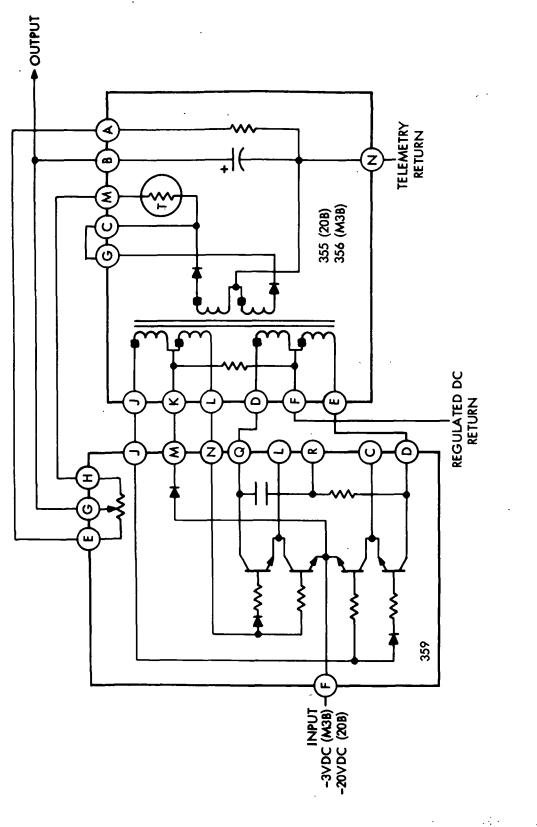

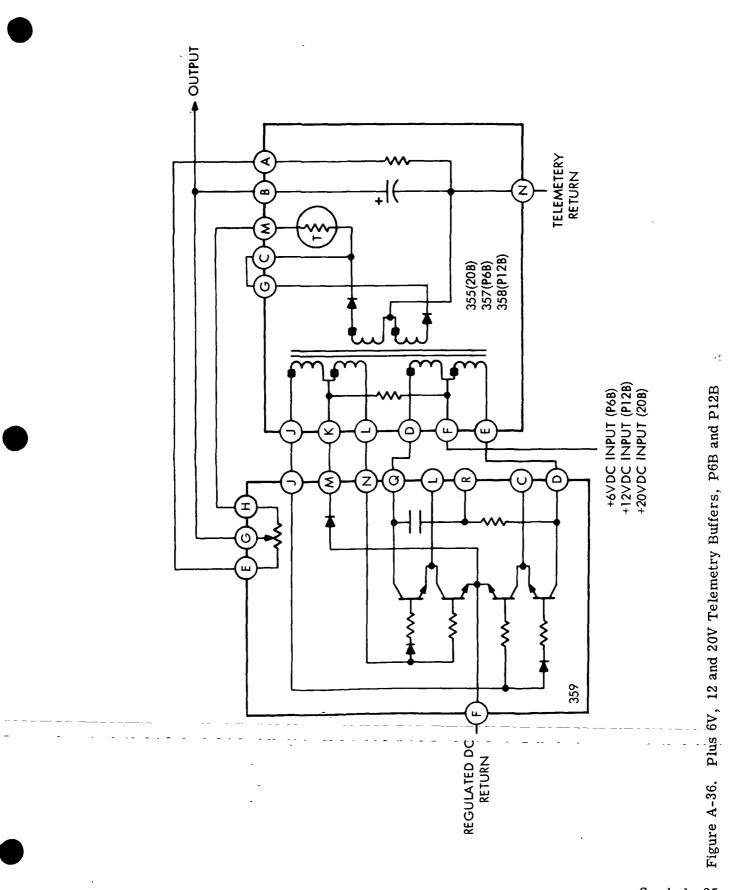

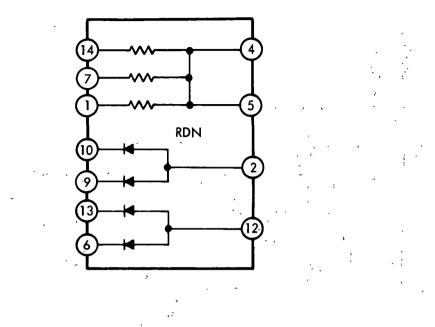

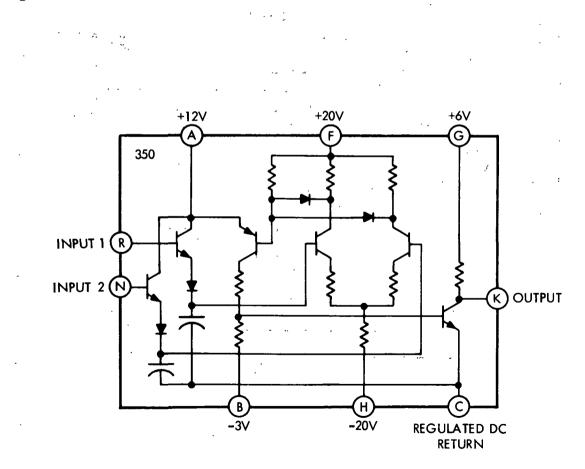

| A -24<br>A -25<br>A -26<br>A -27<br>A -28<br>A -29<br>A -30<br>A -31<br>A -32<br>A -33<br>A -34<br>A -35<br>A -36<br>A -37<br>A -38 | Inverter Circuit, I<br>Interface Buffer, IB<br>Intermediate Driver, High Current, IDH<br>Intermediate Driver, Low Current, IDL<br>Ladder Decoder Amplifier, LDA<br>Ladder Resistor Network, LRN<br>Minus 3V of 20B Telemetry Buffer, M3B or 20B<br>Negative Current Generator, NCG<br>Negative Current Switch, NCS<br>Negative or Positive Voltage Reference, NVR or PVR<br>Positive Current Generator, PCG<br>Positive Current Switch, PCS<br>Plus 6V, 12 and 20V Telemetry Buffers, P6B and P12B<br>Resistor Diode Network, RDN<br>Resolver Telemetry Buffer, RTB | Symbols-18<br>Symbols-19<br>Symbols-19<br>Symbols-20<br>Symbols-20<br>Symbols-21<br>Symbols-22<br>Symbols-23<br>Symbols-23<br>Symbols-24<br>Symbols-24<br>Symbols-24<br>Symbols-25<br>Symbols-26 |

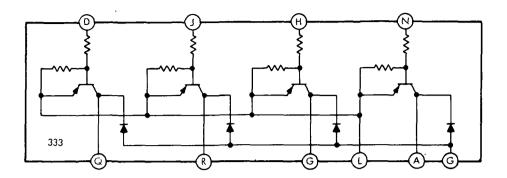

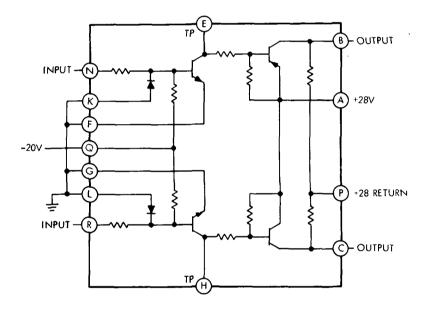

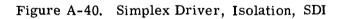

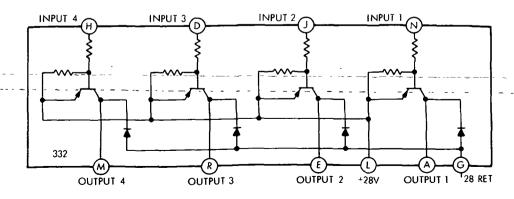

| A -39<br>A -40<br>A -41                                                                                                             | Simplex Driver, High Current, SDH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Symbols-27<br>Symbols-27<br>Symbols-27                                                                                                                                                           |

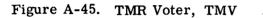

| A - 42<br>A - 43<br>A - 44<br>A - 45<br>A - 46                                                                                      | TMR Driver, High Current, TDHTMR Driver, Low Current, TDLTMR Driver, Medium Current, TDMTMR Voter, TMVVoter Inverter, VI                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbols-28<br>Symbols-29<br>Symbols-29<br>Symbols-30<br>Symbols-30                                                                                                                               |

#### LIST OF RELATED MANUALS

#### Manual Title

Technical Manual, Laboratory Maintenance Instructions, Launch Vehicle Digital Computer (Simplex Models)

Technical Manual, Checkout Procedures, Saturn Launch Vehicle Digital Computer and Data Adapter

Technical Manual, Laboratory Maintenance Instructions, Saturn V Test Equipment

Signal Routing Lists, LVDA Simplex Models

## (To be Supplied.)

Figure i. Launch Vehicle Data Adapter

#### SECTION I

### INTRODUCTION AND DESCRIPTION

#### 1-1. INTRODUCTION.

1-2. SCOPE.

1-3. This section describes the purpose and general features of this manual and the salient features and physical construction of the Launch Vehicle Data Adapter.

#### 1-4. PURPOSE OF MANUAL.

1-5. This manual contains laboratory maintenance instructions for the simplex models of the Launch Vehicle Data Adapter (LVDA), NASA part number 50M35011, IBM part numbers 6112050 and 6112070, manufactured by International Business Machines Corporation, Federal Systems Division, Rockville, Maryland, under contract number NAS 8-11561. (See frontispiece.) In the remainder of this manual, the Launch Vehicle Data Adapter will be referred to as the data adapter.

1-6. This manual is divided into two volumes. Volume I, "General Description and Theory", describes the structure, contents and operation of the data adapter. Volume II, "Maintenance Data", contains all procedures for handling, troubleshooting and repairing the data adapter. Also included in volume II are detailed logic diagrams for analysis and signal tracing. Schematics are supplanted by signal routing lists (see List of Related Manuals) which are not included as part of this manual, but are provided separately. Logic diagrams typical of all data adapter circuits are provided with the descriptive material in volume I. Reference to corresponding detailed logic diagrams in volume II may be made through the index.

1-7. The index and appendices to this manual are provided in volume I. Included with the appendices are a number of comment sheets. Notice of any errors or omissions should be entered on one of these sheets and mailed to the address shown at the beginning of the comment sheets.

1-8. Inserted in the binder pocket of this manual is a plasticized timing diagram. This diagram is a duplicate of a diagram in the manual, and is included for convenient reference. Additional reference data is located on the back of the timing diagram.

1-9. The manual is divided into ten sections whose titles convey the layout of data in a general way. Specific data may be located in the index.

#### 1-10. PURPOSE OF EQUIPMENT.

1-11. The simplex models of the data adapter consist of breadboard model I (6112050) and breadboard model II (6112070). The simplex models are engineering demonstration and evaluation models of a unit which will be part of the Saturn V Launch Vehicle Guidance System. In its ultimate form, the data adapter will adapt guidance system signals for use by the Launch Vehicle Digital Computer (LVDC), and will convert the computer output signals to a form usable by the guidance system. In addition, the data adapter will store computer and system data for subsequent telemetering, and will accumulate real-time and accelerometer data.

a carrier of

1-12. The ultimate version of the data adapter will contain triplicated circuits for reliability. Except for a few demonstration circuits, the simplex models are equipped with only a single set of circuits.

1-13. The breadboard I and breadboard II models of the data adapter are electrically identical. The physical construction of the two models is similar, escept that the breadboard II model is liquid cooled, whereas the breadboard I model is forced-air cooled. The descriptions in this manual are for the breadboard II model data adapter. Differences are noted in the discussion.

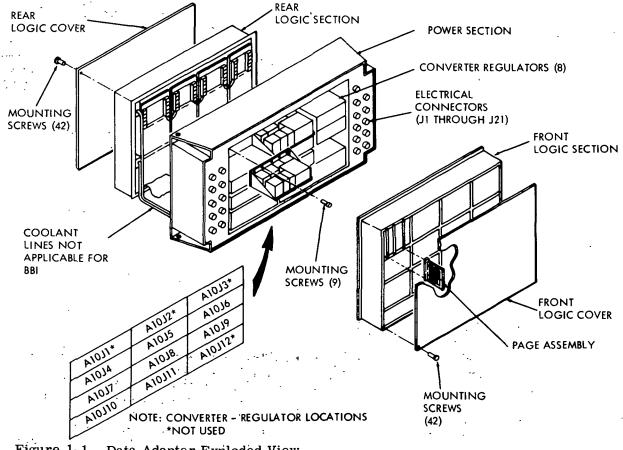

#### 1-14. STRUCTURAL DESCRIPTION. (See figure 1-1.)

1-15. GENERAL. The data adapter consists of three oblong frames which are stacked sandwich-fashion to form the complete unit. The two outer frames contain logic circuits and, accordingly, are called logic sections. The middle frame contains power circuits and is called the power section.

1-16. All the frames of the breadboard II model have been drilled to form small passageways for the flow of liquid coolant. The coolant enters and leaves the data adapter through couplings mounted on each end of the power section. Flexible hose assemblies carry the coolant from the power section to the logic sections.

1-17. Electrical connections between the power section and the logic sections are provided primarily by flat, flexible, printed cable assemblies called tape cables. (Some additional connections are provided through standard wire cables.)

Figure 1-1. Data Adapter Exploded View

1-18. The coolant hose assemblies and the tape cables and wiring are situated at one end of the data adapter so that the logic sections may be opened like clamshells for access to the power section and to the inner sides of the logic sections.

1-19. Electrical connections to and from the data adapter itself are made through 21 system connectors mounted at the ends of the power section.

1-20. The maximum dimensions of both simplex models of the data adapter are 32" by 16-1/4" by 14-3/4". The breadboard model I weighs about 222 pounds and the breadboard model I weighs about 166 pounds.

1-21. LOGIC SECTIONS. Logic circuits in the data adapter are packaged in two basic forms: the unit logic device (ULD) and the circuit module (CM). The unit logic device consists of a 3/10 inch square ceramic wafer on which is deposited a printed wiring pattern and various deposited-film resistors (as required). Fused to the printed wiring at appropriate points are semiconductor "chips". All the components are covered with a potting compound, and the ULD is capped with a plastic wafer on which is imprinted the ULD identification code. Electrical connections to the ULD are made through 14 contacts (7 on each of two sides) along the bottom edge of the ULD. The contacts are referred to as pads.

1-22. The circuit module consists of a metal container in which is encapsulated various circuit components too large for ULDs. The average circuit module measures 1-1/4'' long by 1/2'' wide, and is approximately 1'' high. The top of the module is covered with a sealing compound on which is imprinted the circuit module identification code. Connections to the circuit module are made through 16 pins which protrude from the bottom.

1-23. Both the unit logic devices and the circuit modules are electrically interconnected to one another by multilayer interconnection boards (MIBs). The multilayer interconnection board consists of a number of printed wiring sheets bonded together. Connections between sheets are made by flowing solder through holes drilled through the board at points where desired "lands" coincide. (A land is the pattern of metal which makes up the printed wiring.) Because of differences in the manner of mounting, separate MIBs are used for unit logic devices and circuit modules.

1-24. The unit logic devices are fused to 14-pad patterns on their MIBs. The ULD-type MIBs have 35 locations for ULDs, although not all locations are always used. The circuit modules are fastened to their MIBs by their 16 connector pins which protrude through holes in the MIB and are soldered in place. In addition, a screw extends through the MIB and into a tapped hole in the circuit module.

1-25. Connections to and from the MIB are made through 49 lands (connector lands) at one end of the MIB and 30 lands (thru-pin lands) at the other end. Test points are provided by 18 heavy lands, 9 on each side of the thru-pin lands.

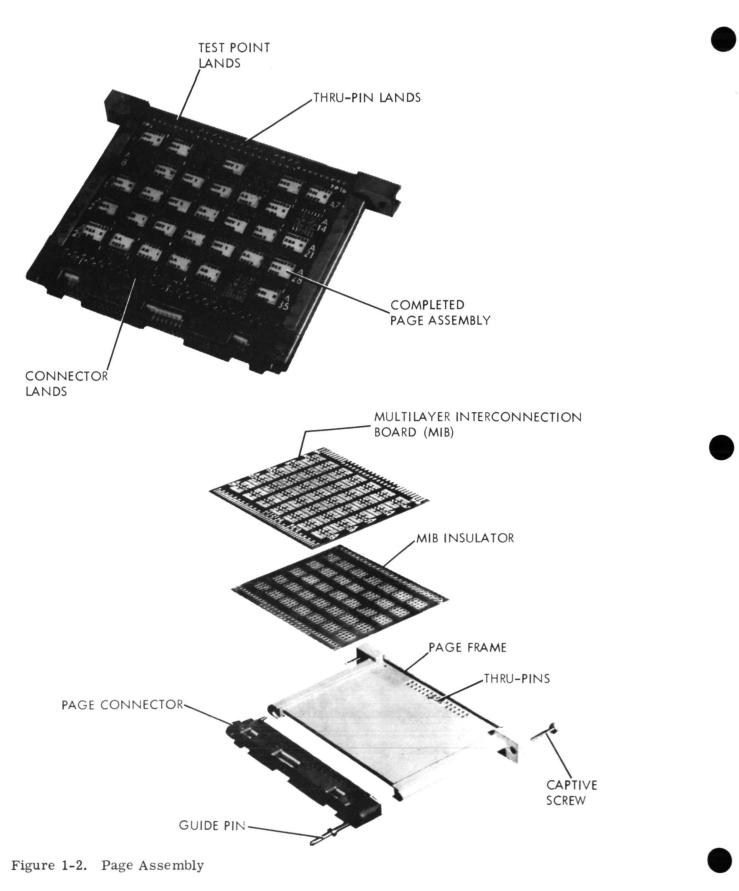

1-26. MIBs are assembled into a frame with a pluggable connector to form a page assembly (figure 1-2). The page assembly consists of a page frame, a 98-pin connector, two guide pins, two captive screws, and either one or two MIBs and MIB insulators. The page assembly may also contain up to 30 thru-pins.

1-27. The connector is fastened to the page frame by the guide pins. The MIB insulator is positioned on the side of the page frame with both the page connector pins and the thru-pins projecting through its clearance holes. The MIB fits over the insulator with the pins projecting through holes in its connector and thru-pin lands. Solder is flowed

over the pins to connect them to the MIB. In cases where a MIB is installed on each side of the page frame, the thru-pins provide a set of connections from one MIB to the other. Inputs and outputs from the MIBs are supplied through the pluggable page connector.

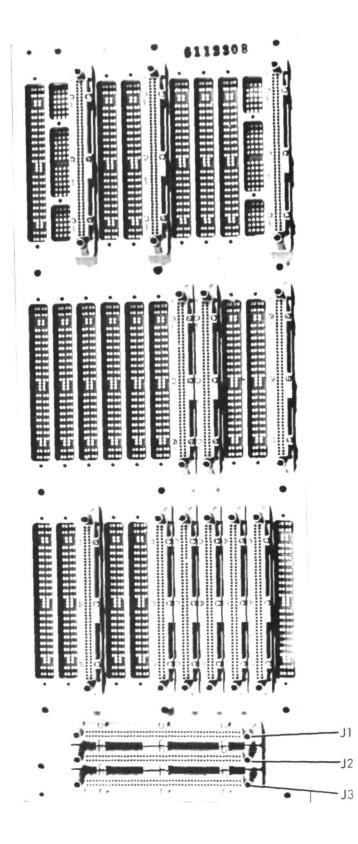

1-28. Connections between pages are provided by large multilayer printed wiring panels called panel assemblies (figure 1-3) on which are mounted receptacles for the page connectors. The panel assemblies are mounted on the logic frames for rigidity and support. The logic frames also contain grooves which position and support the page assemblies. The combination of panel assemblies, logic frame and page assemblies is called a logic section (previously discussed). Each logic section contains four panel assemblies. The center two assemblies can theoretically accommodate 33 pages each, and the two outside panel assemblies have a theoretical capacity of 27 pages each, making a total capacity of 120 pages for each logic section. In actuality, the page capacity is restricted by circuit modules which extend out over adjacent page connector receptacles, rendering them inaccessible for page use, and also by special terminal blocks (two per panel assembly) which are situated in what would otherwise be page receptacle locations.

1-29. The page assemblies are held in the logic frame by two captive screws. The edges, or shoulders, of each page assembly are different sizes so that the page cannot be inverted and inserted the wrong way, since the grooves in the logic frame allow only one orientation. The page sides are designated "A" and "B". The "A" side is the side toward the viewer with the connector down and the large shoulder to the left.

1-30. A flat metal cover is fitted over the outside of each logic section. The cover is dimpled for rigidity and is held in place by socket head screws around its perimeter. Page assemblies are inserted and removed from the cover side, so it is unnecessary to unfasten the logic sections from the power section to gain access to the page assemblies.

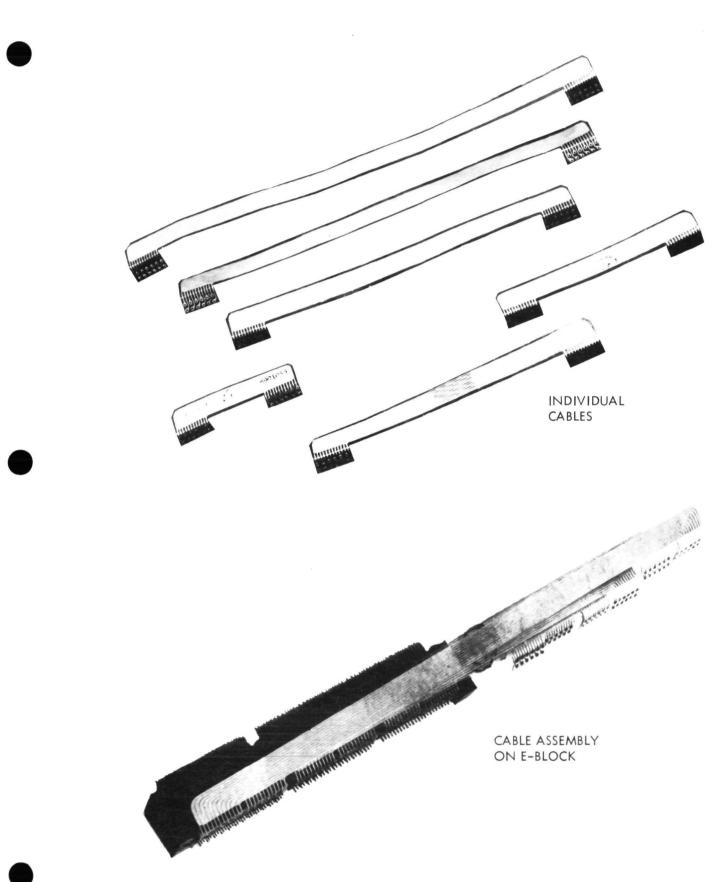

1-31. Connections between panel assemblies are provided by terminal blocks, two in each panel assembly. Each terminal block contains 144 pins. In the breadboard model I, the terminal blocks are wired together from panel assembly to panel assembly. In the breadboard II model, the terminal blocks are interconnected by printed circuit cables (figure 1-4).

1-32. On one end of each of the panel assemblies are three connector receptacles which receive the three plugs of a tape cable from the power section, as previously discussed. The bottom of the logic section is at the same end as the tape cable connectors. From top to bottom, the connectors are designated J1, J2 and J3.

1-33. The logic section which is mounted on the system connector side of the power section is called the front logic section. The remaining logic section is called the back logic section. From left to right, with the top of the logic section facing up, the panel assemblies of the front logic section are designated A5, A6, A7 and A8, respectively. The corresponding panel assemblies on the back logic section are designated A1, A2, A3 and A4, respectively. Page assembly locations are numbered from left to right and top to bottom, A1, A2, A3, etc. A typical page designation would be A3A22, indicating that the page was located in panel assembly A3, position 22. If required, the page assembly MIB side can be added as a suffix, for example, A5A16B, indicating the "B" side of the page in location 16 of panel assembly A5.

1-34. The panel assembly terminal blocks are designated by the letter "E" and for this reason, they are sometimes called E-blocks. In the middle two panel assemblies of each logic section, the E-blocks are located in what would otherwise be page positions

Figure 1-3. Typical Panel Assembly

Figure 1-4. Printed Circuit Cables

2 and 10. These blocks are therefore designated E2 and E10. In the remaining two panel assemblies in each logic section, the E-blocks are located in positions 2 and 8, and are designated E2 and E8.

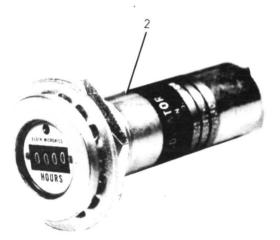

1-35. POWER SECTION. The power section is a boxlike structure with wide flanges at either end. The system connectors, coolant inlet and outlet couplings, and an elapsed time indicator are mounted on the flanges. Reference designations for the system connectors are J1 through J21. The coolant couplings, figure 1-5 (1), are labeled IN and OUT and are designated HP-1 and HP-2 respectively. (No coolant couplings are provided with breadboard model I.) The reference designation for the elapsed time indicator, figure 1-5 (2), is TT-1.

1-36. Across the upper face of the power section is attached a mounting panel (figure 1-6). The mounting panel contains 12 connector receptacles which receive pluggable power supply units called converter-regulators (figure 1-7). (Only eight converter-regulators are provided in the simplex models of the data adapter, although space is provided for 12.) On the back of the mounting panel are 12 power switching relays, two resistors used in computer memory power switching, and two multilayer bus bars. The reference designation for the mounting panel is A10. The connector receptacles for the converter-regulators are numbered left to right and top to bottom, J1, J2, J3, etc. The converter-regulator assemblies have the same designation as the receptacle into which they are plugged. Thus, a typical converter-regulator designation would be A10J11.

(To Be Supplied)

#### LEGEND

1-Adapter (Coolant Coupling) 2-Elapsed Time Indicator

Figure 1-5. Power-Section-Flange Assemblies.

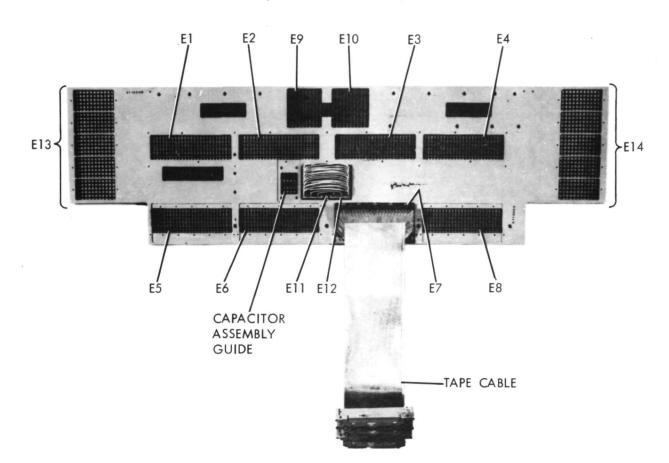

1-37. Across the lower face of the power section is mounted a multilayer interconnection panel called the distribution panel (figure 1-8). The distribution panel contains 14 terminal assemblies called wire guides into which wires are inserted and soldered. The reference designation for the wire guides is "E". Guides E1 through E8 provide connections from the components and connectors on the mounting panel and from the distribution panel to eight tape cable assemblies which, as previously mentioned, interconnect the power section with the logic sections. Guides E9 and E10 provide connections from one side of the distribution panel to the other, as do guides E11 and E12. Guides E13 and E14 provide connections to the system connectors. A capacitor assembly used in conjunction with a digital-to-analog converter circuit is mounted on the distribution panel.

1-38. In most cases, the distribution panel serves as a central point for interconnections between assemblies in the data adapter. In the case of panel assemblies A5 and A6, however, many signals are wired directly from the system connectors to page connector receptacles. This is necessary because the signals so wired would be adversely affected if they were routed through the tape cables.

1-39. Two additional assemblies are mounted on the power section: the resolver frequency source, figure 1-9 (1), and the radio-frequency-interference filter, figure 1-9 (2). Both items are attached to a strut which runs across the frame just below the bottom converter-regulator assemblies. The resolver frequency source, designated FS-1, is wired directly to one of the system connectors. The radio-frequency interference filter output terminals are wired to one of the bus bars on the mounting panel.

(To Be Supplied)

LEGEND

Mounting Plate

Bus Bar No. 1

3- Bus Bar No. 2 4- Relays 5- Terminal Board 6- Resistors

Figure 1-6. Mounting Panel

Inputs to the radio-frequency-interference filter are provided by system connector J11 which is physically part of the radio-frequency-interference filter assembly.

1-40. The reference designator prefix for all data adapter assemblies is 2. Figure 1-10 lists all data adapter assemblies with part numbers and figure reference numbers. Figure 1-11 lists system connectors and part numbers.

1-41. SUBASSEMBLIES. Subassemblies in the data adapter consist of the page assemblies and converter-regulator assemblies, previously described. A list of data adapter subassemblies is included in section IX, since these subassemblies are the only laboratory replaceable items.

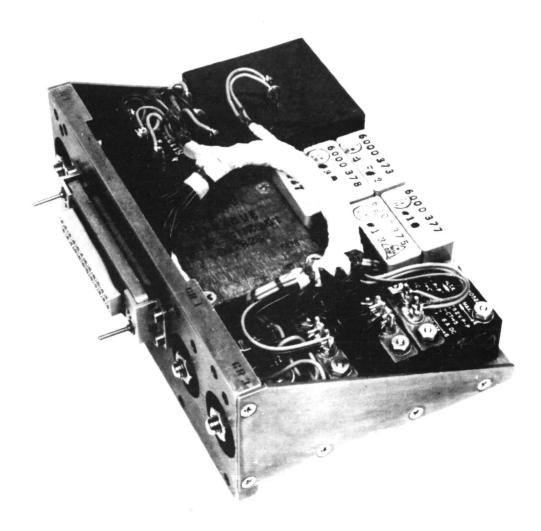

Figure 1-7. Typical Converter-Regulator Assembly

Figure 1-8. Typical Distribution Panel (Shown Partially Assembled)

#### LEGEND

Resolver Frequency Source

Radio-Frequency-Interference Filter

Figure 1-9. Power Section Strut-Mounted Assemblies

| Reference<br>Designator                       | Name                          | Part<br>Number | Figure<br>Reference |

|-----------------------------------------------|-------------------------------|----------------|---------------------|

| 2A1                                           | Panel Assembly                | 6113710        |                     |

| 2A2                                           | Panel Assembly                | 6113730        |                     |

| 2A3                                           | Panel Assembly                | 6113740        |                     |

| 2A4                                           | Panel Assembly                | 6113750        | 1-3                 |

| 2A5                                           | Panel Assembly                | 6113760        | 1-3                 |

| 2A6                                           | Panel Assembly                | 6113770        | · ·                 |

| 2A7                                           | Panel Assembly                | 6113810        |                     |

| 2A8                                           | Panel Assembly                | 6113830        |                     |

| 2A9                                           | Distribution Panel            | 6112726*       | 1-8                 |

|                                               |                               | 6112597**      | 1-0                 |

| 2A10                                          | Mounting Panel consisting of: |                |                     |

|                                               | Mounting Plate                | 6113624        | 1-6(1)              |

|                                               | Bus Bar No. 1                 | 6112528        | 1-6(2)              |

|                                               | Bus Bar No. 2                 | 6112798        | 1-6(3)              |

|                                               | Relays (12)                   | 6080609        | 1-6(4)              |

|                                               | Terminal Board                | 6112808        | 1-6(5)              |

|                                               | Resistors (2)                 | 6071163        | 1-6(6)              |

| 2HP-1                                         | Adapter (Coolant Coupling)    | 6080654        | 1-5(1)              |

| 2HP-2 Same as 2HP-1                           |                               |                |                     |

| 2FL-1 Radio-Frequency-<br>Interference Filter |                               | 6080695        | 1-9(2)              |

| 2FS-1                                         | Resolver Frequency Source     | 6112627        | 1-9(1)              |

| 2TT-1                                         | Elapsed Time Indicator        | 6076600        | 1-5(2)              |

\*breadboard model I only

\*\*breadboard model II only

Figure 1-10. Data Adapter Assemblies

| Reference<br>Designator | Part<br>Number | <sup>.</sup> Diameter | Pin<br>Capacity |

|-------------------------|----------------|-----------------------|-----------------|

| 2J1                     | 6080235        | 1-3/8"                | 55              |

| 2J2                     | 6080237        | 1-3/8''               | 55              |

| 2J3                     | 6080243        | 1-3/8''               | 55              |

| 2J4 ·                   | 6080242        | 1-3/8''               | 55              |

| 2J5                     | 6080238        | 1-3/8"                | 55              |

| 2J6 ·                   | 6081187        | 1-1/4"                | 41              |

| 2J7                     | 6080614        | 1-1/4"                | 41              |

| 2J8                     | 6080239        | 1-3/8''               | 55              |

| 2J9                     | 6080240        | 1-3/8''               | 55              |

| 2J10                    | 6080241        | 1-3/8''               | 55              |

| 2J11*                   | 6080612        | 1-3/8"                | 21              |

| 2J 12                   | 6080243        | 1-3/8''               | 55              |

| 2J 13                   | 6080238        | 1-3/8''               | 55              |

| 2J 14                   | 6080240        | 1-3/8''               | 55              |

| 2J 15                   | 6080237        | 1-3/8''               | 55              |

| 2J16                    | 6080235        | 1-3/8''               | 55              |

| 2J 17                   | 6080613        | 1-1/4''               | 41              |

| 2J 18                   | 6081187        | 1-1/4''               | 41              |

| 2J19                    | 6080614        | 1-1/4''               | 41              |

| 2J20                    | 6080241        | 1-3/8''               | 55              |

| 2J21                    | 6080236        | 1-3/8''               | 55              |

\* Part of Assembly 2FL-1

Figure 1-11. Data Adapter System Connectors

#### SECTION II

#### THEORY OF OPERATION

#### 2-1. SCOPE AND PURPOSE.

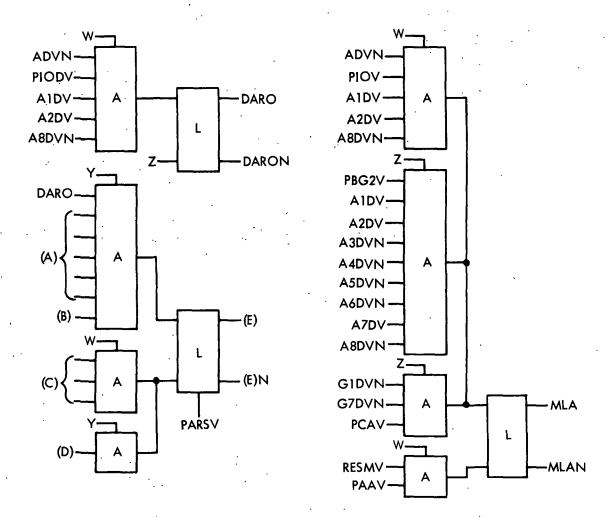

2-2. This section contains descriptions of the electrical and logical functions of the data adapter. The detail of description is sufficient to analyze operations as they may be perceived at test point levels. Included in this section are logic and block diagrams typical of every circuit in the data adapter. If required, detailed diagrams (provided in Section X) may be located by referring to the index. Also, the Section X diagrams are provided in the same order as the order in which they are discussed in this section. Items or circuits which cannot be located in Section X will be located in the signal routing lists.

#### 2-3. SYMBOLS.

2-4. LOGIC SYMBOLS.

2-5. Logic symbols used in the section are described in the Logic Symbols appendix.

2-6. ELECTRICAL SYMBOLS.

2-7. Electrical symbols used in this section conform to military standard MIL-STD-15-1. Special symbols are described in the Part Symbols appendix.

2-8. GENERAL CONCEPTS.

2-9. LATCHES AND TRATCHES.

2-10. Latches and tratches are both defined in the Logic Symbols appendix. However, because of their extensive use in the data adapter, and the various ways in which they are modified and depicted, a more detailed description of their construction and function is included here.

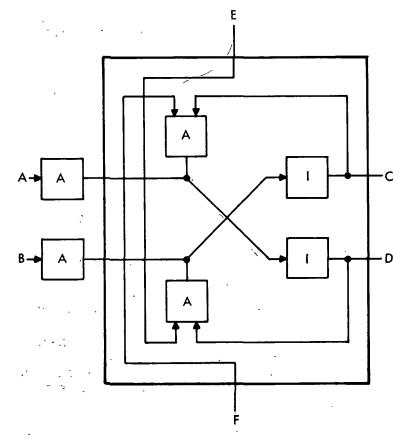

2-11. LATCHES. The basic latch form is shown in figure 2-1. It consists of two cross-coupled AND-INVERTERS. In the quiescent condition, latch inputs A and B are "0's" and inputs E and F are "1's". If C is a "1", D will be a "0" and vice versa.

2-12. Inputs A and B are called one-drive inputs, and inputs E and F are called zerodrive inputs. A "1" on input A will ultimately produce a "1" on output C. A "1" on B will ultimately produce a "1" on output D. The inputs need only be momentary; once the latch feedback path has been completed, the latch will maintain the configuration established by its inputs.

2-13. A "0" at input E will produce a "1" on output C; conversely, a "0" at input F will produce a "1" on output D.

2-14. As previously stated, the latch outputs are always complementary. However, this condition is negated if either set of inputs is double-driven. For instance, if both

1. 2. 2

.j : .

inputs A and B are "1's" at the same time, outputs C and D will both be "0's". If inputs E and F are both "0's" at the same time, outputs C and D will be "1's". Both doubledrive conditions are unstable. As soon as the double-drive is removed, the latch outputs become complementary.

2-15. In general, both outputs of a latch have the same name, except that one output name is suffixed with an "N" (Not). This output is frequently called the "not-side" of a latch. When the not-side of a latch is a "1", the latch is said to be reset. When the not-side is a "0", the latch is set. In cases where the latch outputs are not labeled in this fashion, the set and reset conditions will be specified.

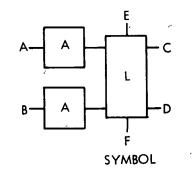

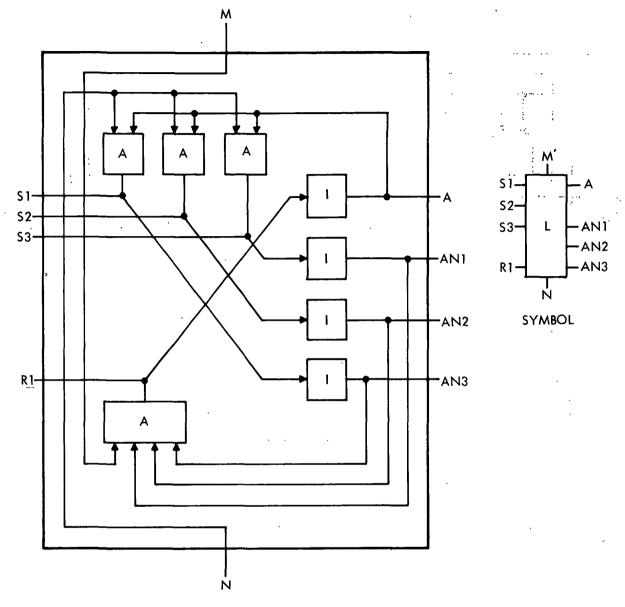

2-16. The basic latch configuration may be modified for certain purposes, such as extending the number of gates that can be used to control the latch. Figures 2-2 and 2-3 show an "OR-extended" and an "AND-extended" latch. In the OR-extended latch, any one of the one-drive set inputs, S1, S2 or S3 is capable of setting the latch. In the AND-extended latch, all three of the set inputs, S1, S2 and S3 must become "1's" simultaneously to set the latch. It should be noted that the three not-sides of the ANDextended latch may be "0's" independently of one another, according to the configuration of "1's" on the three set input lines. The "OR-extended" latch is shown for demonstration purposes only. On the "AND-extended" latch is used in the data adapter.

CONFIGURATION

Figure 2-1. Basic Latch

CONFIGURATION

Figure 2-2. OR-Extended Latch

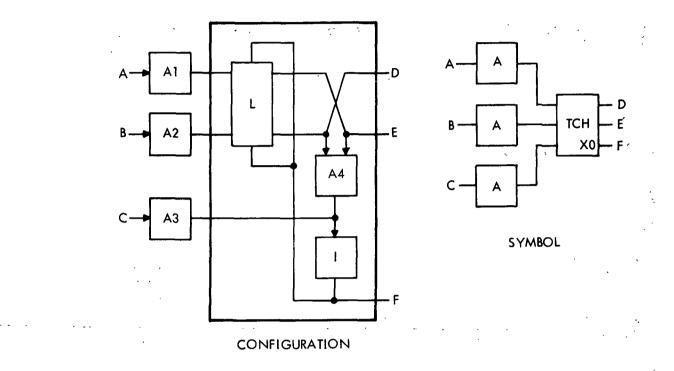

2-17. TRATCHES. Tratches are tristable storage devices which utilize the doubledrive feature of an ordinary latch. Figure 2-4 shows a typical tratch. If input C goes to a "1", output F will become a "0". This "0" is applied to both zero-drive-inputssimultaneously, driving outputs D and E to "1's". Outputs D and E are both fed to gate A4 which opens and maintains the "1" originally supplied through gate A3. The tratch remains in this condition until either input A or input B goes to a "1". When this occurs, the latch is set or reset accordingly, and since its outputs now become complementary, gate A4 opens to remove the double-drive.

2-18. The type of tratch shown in figure 2-4 is called an exclusive-zero tratch, because only one of its outputs can be a "0" at any given time.

Figure 2-3. AND-Extended Latch

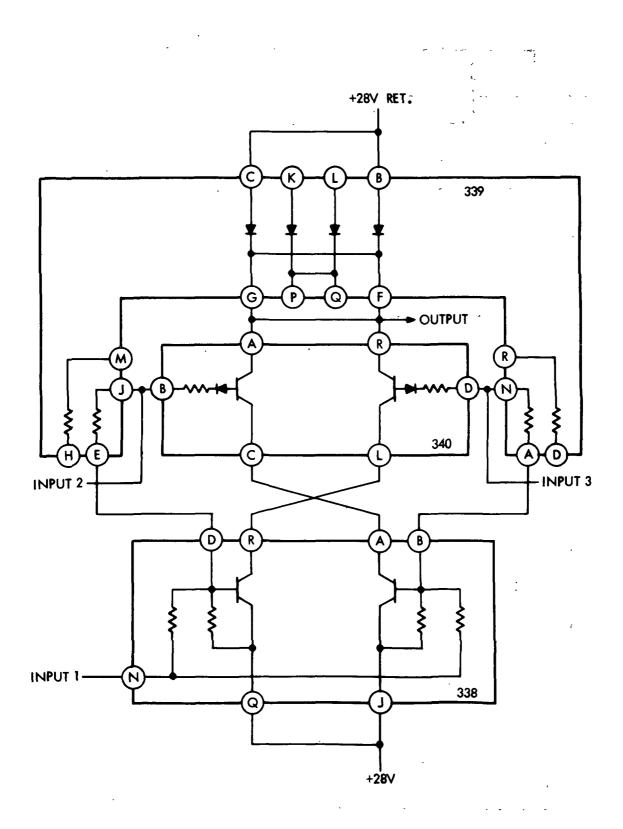

#### 2-19. TRIPLE MODULAR REDUNDANCY.

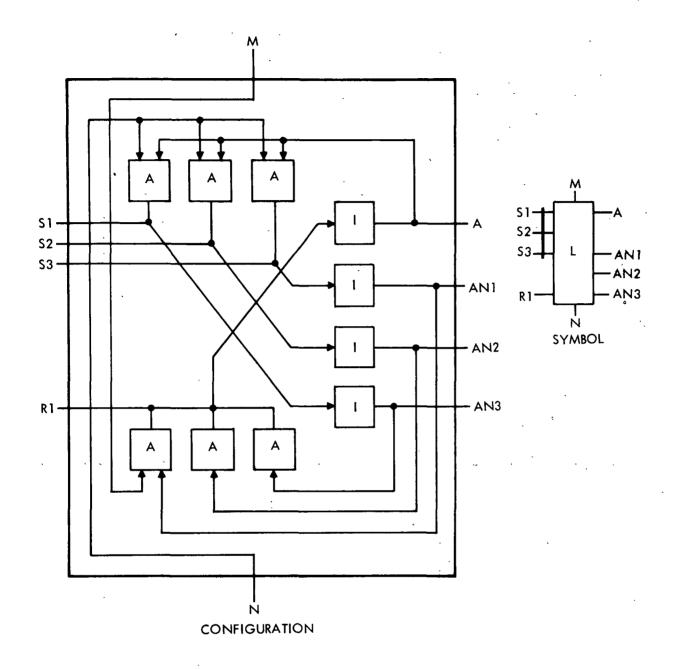

2-20. A failure of almost any circuit in a flight-model data adapter, even a momentary failure, could conceivably cause intolerable malfunctions of the guidance system. To prevent such errors, flight-model data adapter circuits are redundant in the form of three identical sets, or channels, of logic. (Some circuits are duplexed rather than triplexed. This is feasible only if a failed circuit will be overridden by a good circuit as is done with power supplies, or if a reasonableness check can be made of a circuit output and provisions made to switch to the duplex circuit if the reasonableness check fails.)

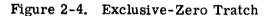

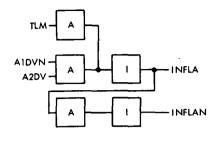

2-21. In the triple modular redundancy, TMR, operation, signals from the three channels are fed to "voter" circuits which duplicate the majority input. Any differing circuit is thereby "outvoted" by two unanimous signals (figure 2-5). Since the voter outputs mask errors by providing correct outputs, the voter inputs are also fed to a circuit called a disagreement detector which senses non-unanimous input conditions. This monitoring feature is necessary for trouble-shooting and evaluation.

Figure 2-5. Voter Circuits, Block Diagram

2-22. In the simplex data adapter models, only a few circuits are triplexed for evaluation purposes. However, a complete set of voter circuits is provided. Therefore, a number of "dummy" circuits have been added to the simplex models to simulate the voter inputs which are not provided by triplicated circuits. In order to get a voter to work properly from one active input, it is necessary to create a "tie vote" on the remaining two inputs, i. e., a "1" and a "0". The active input then breaks the tie, and the output of the voter follows the active input.

2-23. In order to create the "tie vote", one input to the voter is left disconnected. This is equivalent to a "1" input. The "0" input is provided by connecting an AND-Inverter combination to the voter input. The AND input is left disconnected, which is equivalent to driving the AND with a "1". The inverter output is consequently a "0".

2-24. In a number of other cases, the voters are run duplex with one input left disconnected. In these situations, the duplex inputs provide a majority vote whenever they are "0's" and a unanimous input whenever they are "1's" (since the unconnected input looks like a "1"). This system has the advantage of cycling the voters from a unanimous to a non-unanimous condition for demonstration and evaluation purposes.

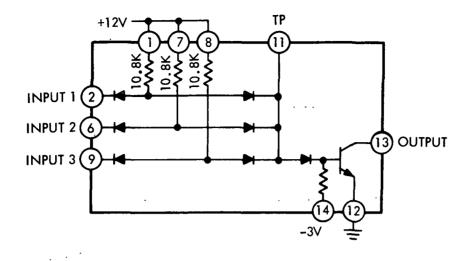

2-25. POWER.

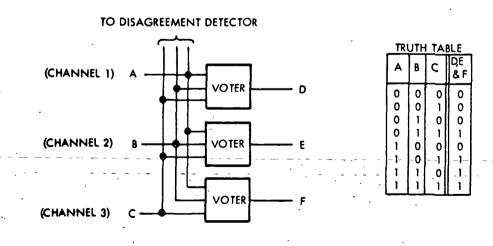

2-26. The data adapter develops the voltages required for both itself and the computer from an externally provided 28 volt dc source. The voltages are +20, +12, +6, +6 COMP, -3 and -20 volts. Figure 2-6 shows a typical power supply. The input 28 volts dc is fed through a radio-frequency interference filter to eight converter-regulator assemblies which provide the six voltages and a spare +20 and +6 for duplexing purposes.

2-27. Included in the converter-regulator assemblies are special circuits which adapt the voltage outputs for telemetry circuits and for telemetry ground reference.

2-28. The outputs of some of the converter-regulators are fed to computer and data adapter circuits through power-switching relays which, in turn, are controlled by external signals. The outputs of the remaining converter-regulators are fed directly to computer or data adapter circuits.

2-29. CONVERTER-REGULATOR. The converter-regulators employ dc chopping with transformer step-up or step-down and rectification to generate unregulated dc voltages which are regulated by a process called pulse-width modulation. In pulsewidth modulation, a triangular shaped signal is fed to a square wave generator which turns on and off as the triangular shaped signal rises and falls past a given reference level. If the reference level is raised (closer to the apex of the triangle), the on and off points will come closer together and the output pulses from the square wave generator will become narrower. If the reference level is lowered (away from the apex of the triangle), the on and off points will become further apart and the square wave generator output pulses will become wider.

2-30. In the converter-regulators, the triangular waveform is supplied by the same chopper and transformer that supplies the unregulated voltage for use by the converterregulator circuits. The reference level is represented by the difference between the regulated output voltage and some standard voltage (established by zener diodes). The pulses from the square wave generator are fed to a transformer-rectifier-filter which produces the output voltage. If the output voltage rises, the reference level of the triangular waveform will be driven upward, shortening the pulse width of the square wave generator output and thereby reducing the output voltage. Conversely, a falling output

Figure 2-6. Power Supply Switching, Simplified Diagram

voltage will lower the reference level of the triangular waveform, increasing the square wave generator pulse width and thereby raising the output voltage back to normal.

2-31. The portion of the pulse-width modulator which senses the difference between the output voltage and some reference, and which provides the reference level for the triangular waveform is called the regulator. The remaining circuits of the pulse-width modulator are called the converter. Each converter-regulator assembly has two regulators which are provided for duplexing purposes.

2-32. ANALOG TELEMETRY BUFFER. Included in the converter-regulator assemblies are analog telemetry buffer circuits which provide a dc signal proportional to the output level of the converter-regulator. The signal from the analog telemetry buffer is isolated from the data adapter ground return. This prevents inaccurate telemetry readings caused by differences in the gound return potential between the data adapter and the telemetry equipment.

2-33. DIGITAL TELEMETRY CIRCUITS. Also included in the converter-regulator assemblies are digital telemetry circuits which sense whether the converter-regulator output is on or off. For positive supplies, the digital telemetry output is a "1" when the supply is on and a "0" when the supply is off. For negative supplies, the digital telemetry output is a "1" when the supply is off.

2-34. POWER CONTROL. Power turn-on and turn-off is controlled simply by turning the external 28 volt dc source on and off. However, in the case of duplexed supplies, arrangements are made to disable each of the supplies to determine if the remaining supply is operable. Simultaneously, one of the two regulators in each converterregulator assembly may be disabled to check the operability of the remaining regulator. The disabling operation is provided by four signals, GCOA, GCOB, GCOC and GCOD. These signals are generated outside the data adapter. A ground on any one of these signals will disable the circuit to which it is fed. A duplexed supply may be represented as in figure 2-6, where the converters are numbered 1 and 2, and the regulators are numbered 1A, 1B, 2A and 2B. The signals required for various operating conditions are shown as follows:

| Operating: |            | Gimele Demined   |  |

|------------|------------|------------------|--|

| Converter  | Regulator  | Signals Required |  |

| 1          | 1A         | GCOD, GCOC       |  |

| 1          | 1B         | GCOD, GCOB       |  |

| 2          | 2A         | GCOA, GCOC       |  |

| 2          | <b>2</b> B | GCOA, GCOB       |  |

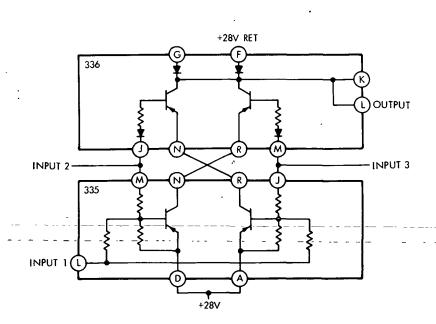

2-35. POWER SWITCHING RELAYS. Relays are used to control power to the computer memory drivers, to the discrete output drivers, and to various logic and voters for channel switching.

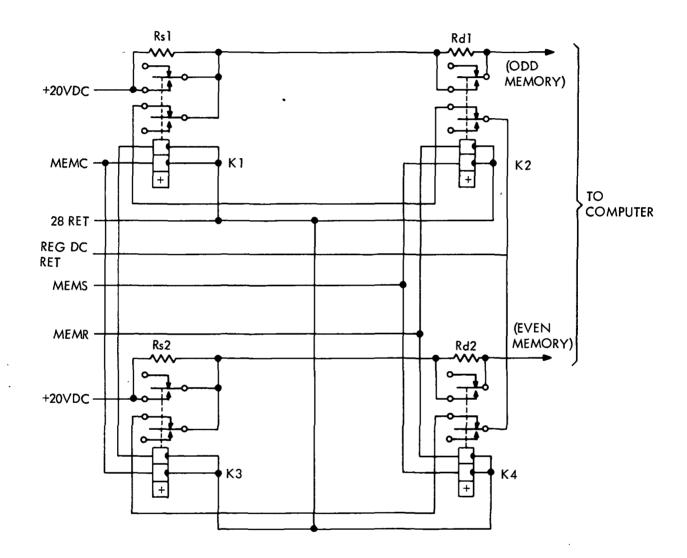

2-36. <u>Computer Memory Driver Switching</u>. Computer memory driver switching is provided by the memory driver relays, figure 2-7. Under control of externally provided signals MEMC, MEMS and MEMR, these relays disable the memory drivers during channel switching or during power-on and power-off sequences to prevent reading in extraneous data or destruction of data by partially energized circuits. The memory driver relays are bipolar. Prior to power-on, they are all reset as shown in figure 2-7. Resistors Rs1 and Rs2 are connected to dc return via circuitous routing through the relay contacts. When +20 volt dc power comes up, it will be loaded by resistors

12/66 Note.

Rs1 and Rs2. This loading maintains a trickle current through the power supply filter. At least 50 milliseconds after power comes on, MEMC will set relays K1 and K3, applying +20 volts dc to the memory drivers through resistors Rd1 and Rd2. The minimum 50 millisecond delay allows the logic and power circuits to stabilize. Resistors Rd1 and Rd2 limit the initial driver current which would otherwise be excessive because of a large decoupling capacitance associated with the memory drivers. At least 15 milliseconds after MEMC is enabled, signal MEMS will set relays K2 and K4, shorting resistors Rd1 and Rd2 and completing the memory power-on sequence.

Figure 2-7. Memory Drive Relays, Schematic Diagram

2-37. In the memory power-off sequence, MEMR will reset all relays, grounding the junction between resistors Rs1 and Rd1 and between Rs2 and Rd2. The ground on resistors Rd1 and Rd2 allows the memory driver decoupling capacitors to discharge without excessive surge current. The ground on resistors Rs1 and Rs2 maintains a  $\pm 20$  volt dc trickle current. Power is not removed until at least 8 milliseconds after the MEMR signal, in order to allow the capacitors to discharge first.

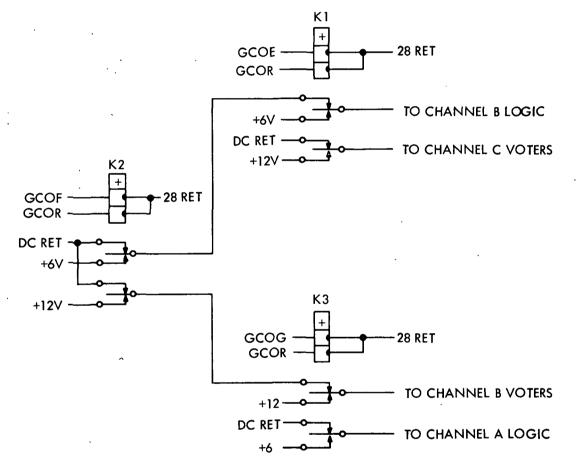

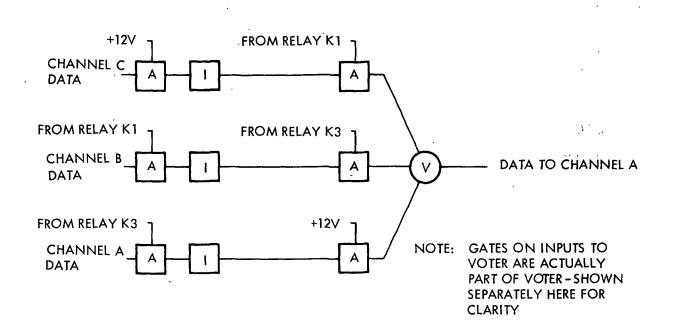

2-38. <u>Channel Switching</u>. Channel switching is provided by the channel switching relays, figure 2-8. Under control of signals GCOE, GCOF, GCOG and GCOR, these relays can disable any two of the three TMR channels in order to check the operation of the remaining one. Basically, disablement consists of forcing a tie vote (a "1" and a "0") at two inputs of each voter. The remaining input then breaks the tie and is free to run the voter. The "0" input to the voter is provided directly from the relays. As shown in figure 2-9, the voter inputs consist of three gates which are usually returned to +12 volts dc. To produce a "0", the gate return is grounded through the relays. In order to produce the "1" input, it is necessary to disable the gate of a gate-inverter combination feeding the voter. When the gate is disabled, its output will be a "0", driving the inverter output to a "1". The logic gates are normally returned to +6 volts dc. To disable these gates, the channel switching relays ground the gate return.

Figure 2-8. Channel Switching Relays

2-39. As shown in figure 2-9, channel C is disabled only by forcing a "0" at the voter. Channel A is disabled only by forcing a "0" at the logic. Channel B may be disabled either way. Briefly, this operation may be summarized as follows:

| . · | To Select<br>Active Channel | Disable Logic<br>On Channel | Disable Voter<br>On Channel |

|-----|-----------------------------|-----------------------------|-----------------------------|

|     | A                           | В                           | С                           |

|     | В                           | A                           | <b>C</b> .                  |

|     | C                           | A                           | B                           |

2-40. As shown in figure 2-8, relay K1 (when set) disables the channel C voters. Relay K3 (when set) disables the channel A logic. Depending on whether relay K1 or relay K3 is set, relay K2 (when set) will disable either the channel B logic or the channel B voters. If none of the relays are set, all channels will operate in TMR. The appropriate relay drive signals for various active channels are shown as follows:

| Channel<br>Selected | Relay Drive<br>Signals |

|---------------------|------------------------|

| A                   | GCOE and GCOF          |

| В                   | GCOE and GCOG          |

| С                   | GCOF and GCOG          |

| A11                 | GCOR                   |

|                     |                        |

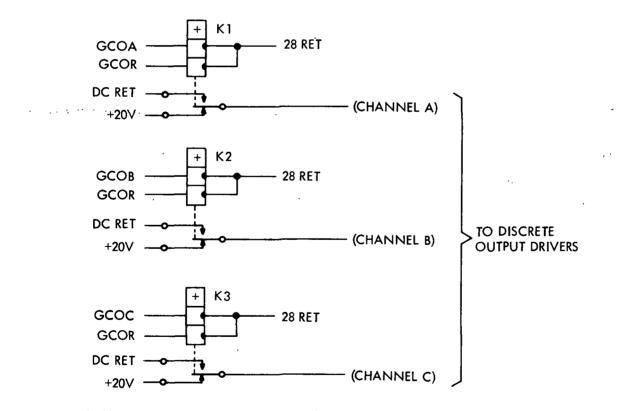

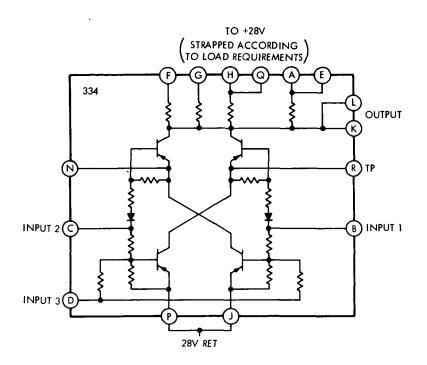

2-41. Discrete Output Driver Switching. Switching of the discrete output drivers in the data adapter is accomplished by the discrete output driver relays, figure 2-10. Under control of externally provided signals, GCOA, GCOB and GCOC (three of the same signals used for converter-regulator control), these relays can disable any one or any two of the driver inputs (in actuality, disabling one or more of the intermediate output drivers which are considered to be part of the discrete output drivers). The discrete output drivers behave like voters. If one input is grounded, the remaining two will provide a majority input and the driver output will consist of data. If two inputs are

grounded, the driver output will be a "0". The appropriate relay drive signals for various driver outputs are as follows:

| Relay Drive<br>Signals | Channel A<br>Input | Channel B<br>Input | Channel C<br>Input | Driver<br>Output |

|------------------------|--------------------|--------------------|--------------------|------------------|

| GCOA                   | ''0''              | Data               | Data               | Data             |

| GCOB                   | Data               | "0":               | Data               | Data             |

| GCOC                   | Data               | Data               | ''0''              | Data             |

| GCOA, GCOB             | ''0''              | ''0''              | Data               | <b>''0''</b>     |

| GCOA, GCOC             | ''0''              | Data               | ''0''              | ''0''            |

| GCOB, GCOC             | Data               | ''0''              | ''0''              | <b>''0''</b>     |

· . ·

Figure 2-10. Discrete Output Driver Relays

2-42. TIMING.

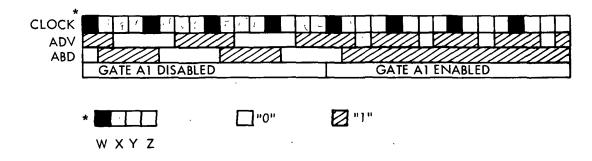

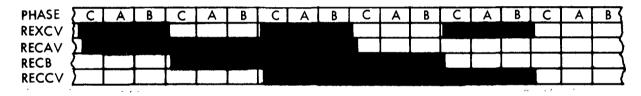

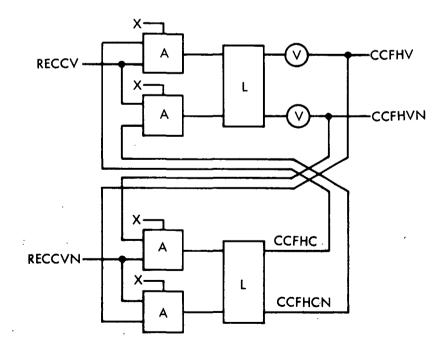

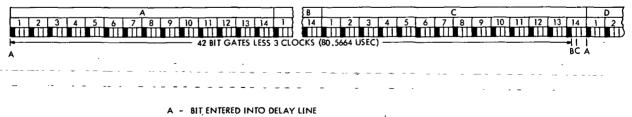

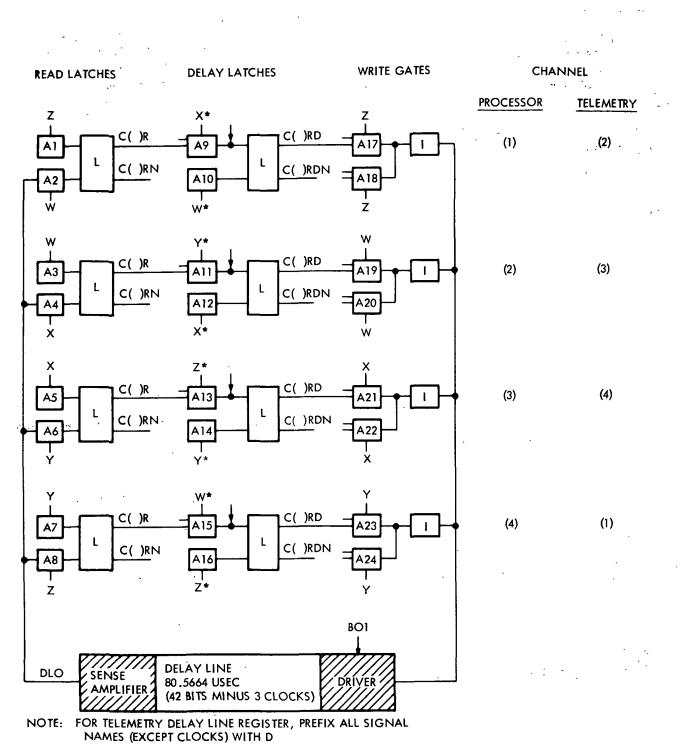

2-43. GENERAL. Data adapter timing is based upon a unit of time known as the operation cycle, which is approximately 82 microseconds long. The operation cycle is divided into three equal intervals called phases; each phase is subdivided into 14 bit gates

;

and each bit gate is further divided into four clocks. The nominal values for duration and period of the various timing intervals are as follows:

|   | Interval        | Name        | Duration (usec) | Period (usec) |

|---|-----------------|-------------|-----------------|---------------|

| 5 | Clocks          | W, X, Y & Z | 0.48828125      | 1.9531250     |

|   | Bit Gates       | 1 thru 14   | 1.9531250       | 27. 343750    |

|   | Phases          | A, B & C    | 27. 343750      | 82.03125      |

|   | Operation Cycle |             | 82.03125        |               |

2-44. Each operation cycle is followed by another as long as the data adapter continues to operate. The preceding values are for the nominal intervals of time indicated and not necessarily for the actual signals used to define these intervals.

2-45. The signals used to define timing intervals are developed from computer clocks which are fed to circuits in the data adapter. Since the timing signals generated in the data adapter are identical to the timing signals generated in the computer, synchronizing signals are provided by the computer.

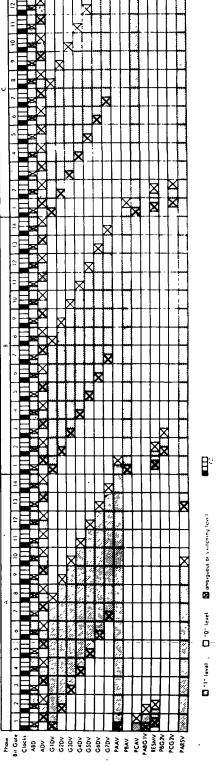

2-46. Clocks provided by the computer are amplified and distributed in the data adapter by clock driver circuits. The signals used to identify bit gates are developed by the Timing Gate Generator, and the signals used to identify phases are developed by the Phase Generator. A number of additional signals, embodying various combinations of phase, bit gate and clock signals are generated by special timing circuits.

2-47. CLOCK DRIVER CIRCUITS. Each clock coming from the computer is fed to eight clock driver circuits (figure 2-11). These circuits provide level restoration and power gain.

(SAME FOR X, Y AND Z CLOCKS.)

Figure 2-11. Clock Drivers

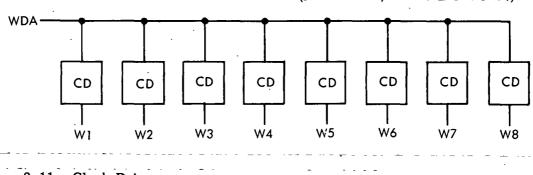

2-48. TIMING GATE GENERATOR. The timing gate generator consists of a control circuit and a seven-bit modified shift register (figure 2-12). The shift register is gated to ultimately force "0's" in positions 2 thru 7 (gating not shown in figure 2-12). The "0's" are complemented to "1's" on subsequent shifts, and when the resulting series of

Figure 2-12. Timing Gate Generator, Block Diagram

"1's" emerge from the shift register, they are complemented back to "0's". Therefore, the shift register continuously cycles a series of seven "0's" followed by seven "1's".

2-49. The rate at which the shift register is cycled is determined by the control circuit, which is a binary counter driven by the Y clock from the computer. Each shift of the register occurs at W clock (or every bit gate, since a bit gate is four successive clocks wide).

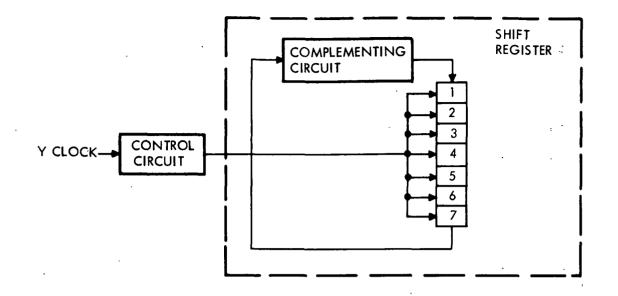

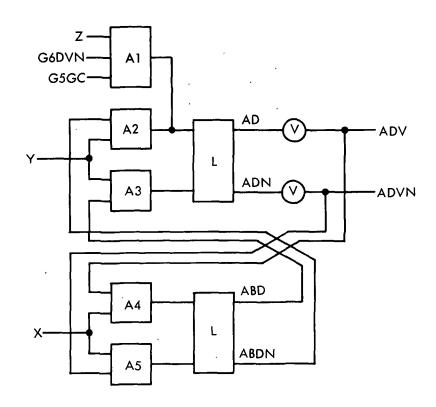

2-50. <u>Control Circuit</u>. The control circuit consists of a pair of latches interconnected to form a binary counter (figure 2-13). The ABD latch stores the configuration of the AD latch during an X clock and steers the AD latch to its complementary state on each following Y clock. When enabled, an additional gate on the set side of the AD latch opens every Z clock to hold the AD latch set, except during Y clock. This gate is used for synchronizing purposes as will be explained later.

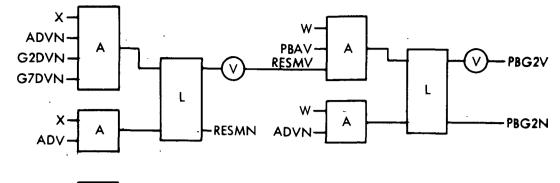

2-51. <u>Shift Register</u>. The shift register consists of seven latches connected in series (figure 2-14). As long as any "1's" exist in latches G2D through G7D, gate A1 cannot open. Ultimately, any "0's" in latches G2D through G7D will be shifted out to open gate A2 and reset latch G1D. Latch G1D will remain reset, effectively cycling "0's" into the shift register until latches G2D through G7D are all reset. Then gate A1 will open, setting latch G1D and effectively cycling "1's" into the register. Latch G1D will remain set as long as "0's" are being cycled out of latch G7D. The complementing circuit previously mentioned is actually latch G1D with its driving gates. A1 and A2.

2-52. In this shift register, "rippling" is prevented by the control circuit, which gates the odd-numbered latches (G1D, G3D, etc.) and the even-numbered latches in alternate modes, i.e., the set sides of the odd-numbered latches are gated at the same time that the reset sides of the even-numbered latches are gated. Consequently, a set condition cannot be propagated through successive latches on any one shift; the same is true for a reset condition.

Figure 2-13. Control Circuit

2-53. <u>Identification of Bit Gates</u>. The outputs of the timing gate generator are diagrammed in figure 2-15. This figures shows transition times, i.e., the time that must be allowed for a signal to complete the transition between "0" and "1" or between "1" and "0". Bit gate 1 may be identified as the coincidence of signals G1DV and G2DVN; how= ever, this identification is valid only during the Y and Z clocks, since G1DV is in transition during the W and X clocks. Bit gate 1 may be identified during the W and X clocks by the coincidence of signals G2DVN, G7DVN and ADVN. Therefore, three signals are needed to identify bit gates during W and X clocks, whereas only two signals are needed during Y and Z clocks.

Figure 2-14. Shift Register

🕅 ambiguous or suitening level

.

#### Sec. 1. . . .

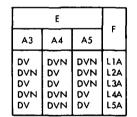

2-54. Bit gates are decoded at the point where they are used. The combination of signals used to identify bit gates are as follows:

| Bit Gate | W or X Clock       | Y or Z Clock |

|----------|--------------------|--------------|

| · 1      | G7DVN, G2DVN, ADVN | G1DV , G2DVN |

| 2        | G1DV , G3DVN, ADV  | G2DV, G3DVN  |

| 3        | G2DV , G4DVN, ADVN | G3DV , G4DVN |

| 4        | G3DV , G5DVN, ADV  | G4DV , G5DVN |

| 5        | G4DV , G6DVN, ADVN | G5DV , G6DVN |

| 6        | G5DV , G7DVN, ADV  | G6DV , G7DVN |

| 7        | G6DV , G1DV , ADVN | G7DV , G1DV  |

| 8        | G7DV , G2DV , ADV  | G1DVN, G2DV  |

| 9        | G1DVN, G3DV , ADVN | G2DVN, G3DV  |

| 10       | G2DVN, G4DV , ADV  | G3DVN, G4DV  |

| 11       | G3DVN, G5DV , ADVN | G4DVN, G5DV  |

| 12       | G4DVN, G6DV , ADV  | G5DVN, G6DV  |

| 13       | G5DVN, G7DV , ADVN | G6DVN, G7DV  |

| 14       | G6DVN, G1DVN, ADV  | G7DVN, G1DVN |

2-55. Synchronization. The timing gate generator is required to operate in synchronization with an identical circuit in the computer. For purposes of synchronization, the computer provides signal G5VN, which is the equivalent of G5DVN in the data adapter shift register. Signal G5VN is fed through an isolating AND gate and an inverter to become G5GC which represents the "1" state of the G5 latch in the computer.

2-56. Whenever G5VN becomes a "1", latch G5DV will be reset; conversely, whenever signal G5V in the computer becomes a "1", G5GC will become a "1" and set latch G5DV. If the signal ADVN is a "1" at this time (an in-sync condition between ADVN and its counterpart in the computer), the next ADV signal will transfer the "1" from the G5D latch into the G6D latch in normal fashion. The shift register will continue to operate, with gate A15 cycling a "1" into latch G5D on every shift for the duration of G5GC. The series of "1's" introduced into latch G5D is, of course, complemented to "0's" in the process of being shifted into latch G1D. At the end of signal G5GC, latched G1D through G4D will be reset and the remaining latches will all be set. Figure 2-15 shows this to be the configuration for bit gate 11. The register makes seven more shifts during the absence of G5GC, reaching the configuration for bit gate 4. On the next shift, latch G5D will be set by the normal shift operation at the same time that signal G5GC is generated; thus, the shift register is synchronized with the corresponding register in the computer. 2-57. Basically, the shift register is synchronized by forcing its configuration to bit gate 11 and releasing it at the end of the computer bit gate 11 (i.e., the end of G5GC). A glance at the timing diagram (figure 2-15) will show that the start of bit gate 12 is coincident with the start of the ADV signal. If the ADV signal is out-of-phase (180°) with its corresponding signal in the computer, the first ADV pulse following bit gate 11 would occur at the beginning of what should be bit gate 13, and the data adapter timing would lag the computer timing by one bit gate.

## NOTE

The ADV signal can only be either in-sync or 180° out-of sync with its corresponding signal in the computer, since both signals are driven from the same source, i.e., the Y clock.

2-58. In one case, to synchronize an out-of-phase ADV signal, the shift register is forced to its bit gate 11 configuration at what should be bit gate 10 time. The first out-of-sync ADV pulse following bit gate 10 time occurs at bit gate 12, which is the next desired configuration of the shift register and an in-sync condition for the ADV signal.

2-59. If latch G6D is in the set condition at the time latch G5D is set by G5GC, the next pulse will be ADVN (remembering that ADV is out-of-sync), and the G7D latch will be set. Latch G7D is therefore set one shift earlier than it would be if ADV were not out-of-sync. Thus, the forced bit gate 11 configuration is shifted into the register one bit gate early.

2-60. In the other case, the ADV signal is synchronized by forcing the ADV latch to its set condition at the time an even-numbered latch is to be set (figure 2-15). If latch G6D is in its reset condition at the time that G5GC is generated, gate A1 (figure 2-13) of the AD latch will open and set the AD latch. This causes latch G6D to be set, since latch G5D has been set by G5GC. Since latch G6D, an even-numbered latch, has been set during ADV time, the ADV signal is now in-sync.

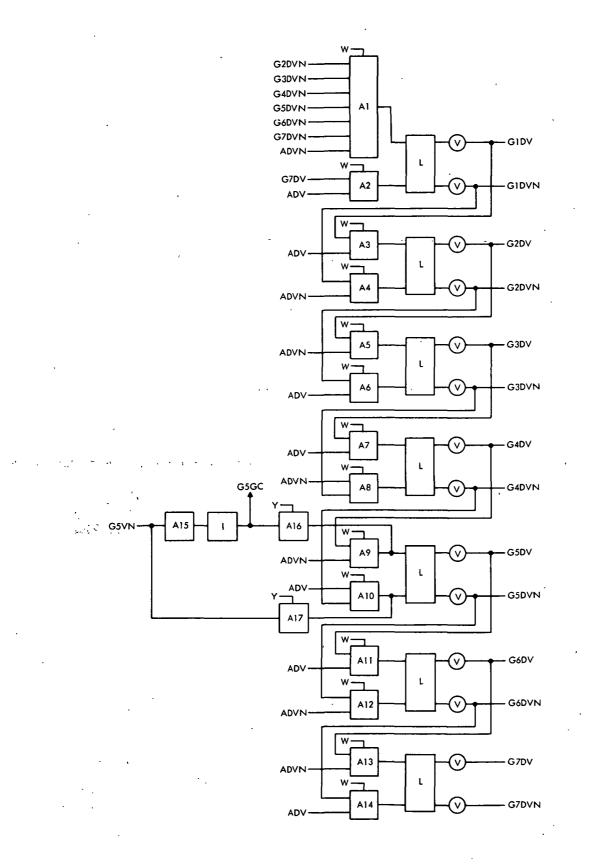

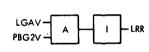

2-61. PHASE GENERATOR. The phase generator consists of a three-step ring counter formed from three latches (figure 2-16). The ring is stepped at bit gate 1 time. The phase generator is synchronized with its counterpart in the computer by signal PBGC. When signal PBGC is a "1", gates A7, A8 and A9 open (at bit gate 2 time) to set the PBA latch and reset latches PCA and PAA.

2-62. The first bit gate 1 after the ring has been synchronized will set the PCA latch (gate A1), and two clocks later, the PBA latch will be reset (gate A6). At the following bit gate 1 time, latch PAA will be set (gate A3), and two clocks later the PCA latch will be reset (gate A2). The following bit gate 1 will set latch PBA (gate A5), and two clocks later, latch PAA will be reset (gate A4), returning the ring to its synchronized condition. Two clocks after latch PAA is reset, the PBGC signal will attempt to synchronize the ring, but the ring will already be in its synchronized condition.

2-63. The outputs of the phase generator are shown in figure 2-15. The outputs of the ring counter correspond to the theoretical phase times except during bit gate 1, where transition time and overlap occur. To properly identify phase time during any bit gate 1, it is necessary to sense the coincidence of timing signals as follows:

|         | Y or Z Cle  | ock   | W or X Clock |            |  |

|---------|-------------|-------|--------------|------------|--|

| Phase A | PAAV, PBAVN | and   | PCAV, PBAVN  | and G2DVN, |  |

| Phase B | PBAV, PCAVN | G1DV, | PAAV, PCAVN  | G7DVN,     |  |

| Phase C | PCAV, PAAVN | G2DVN | PBAV, PAAVN  | ADVN       |  |

2-64. SPECIAL TIMING. Special timing is provided by four latches (figure 2-17) which sense various combinations of the timing signals previously discussed. (Additional timing signals are developed in the data adapter, but their use is so specific that they are discussed with the particular circuit in which they are used.)

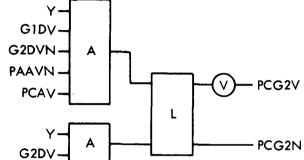

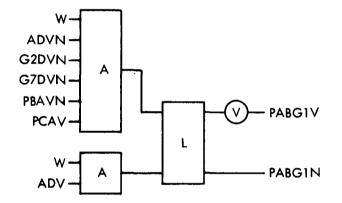

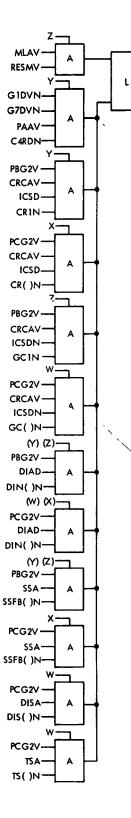

2-65. The RESM latch is set every bit gate 1 time and reset on the following bit gate 2 (figure 2-17). The PBG2 latch ANDs the RESM signal with PBAV to provide a signal during bit gate 2 of phase B. Latch PCG2 is set at the middle of bit gate 1 (phase C) and reset at the middle of the following bit gate. Thus, PCG2 "straddles" bit gates 1 and 2, but is only usable during bit gate 2 because of transition time. Latch PABGIV is set at the beginning of bit gate 1 (phase A) and reset at the beginning of bit gate 2.

2-66. FREQUENCY GENERATOR.

2-67. GENERAL. The frequency generator (actually an extension of the timing circuits) provides pulse intervals in the <u>millisecond range</u> for use as real-time reference.

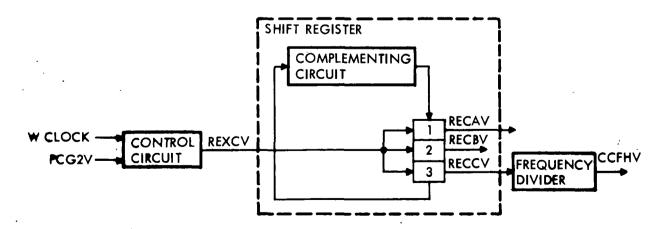

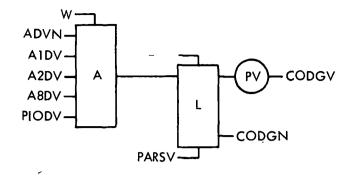

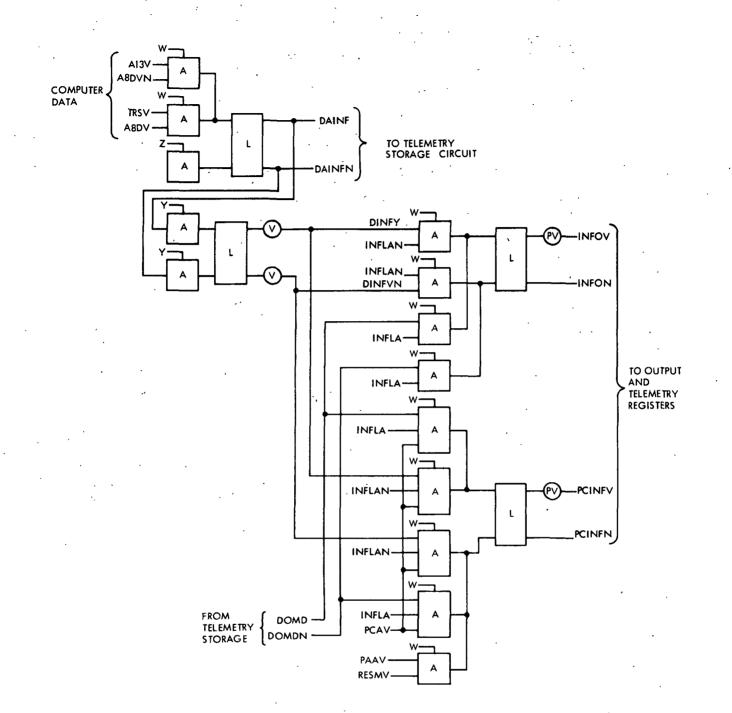

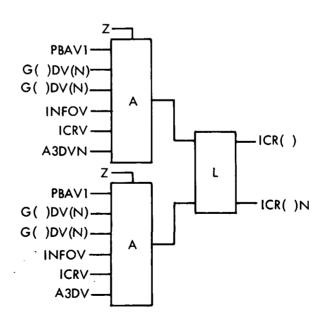

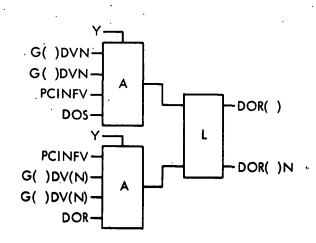

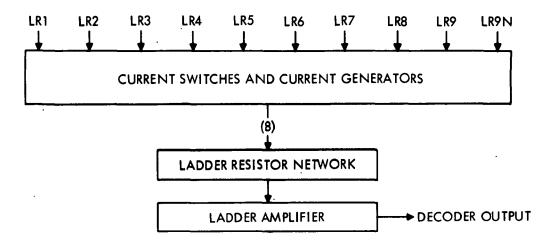

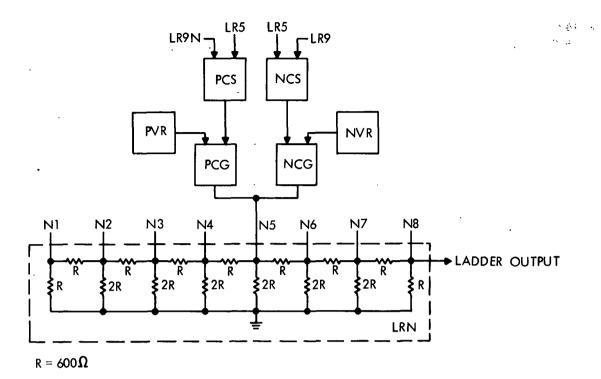

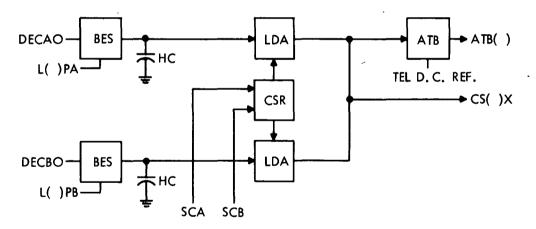

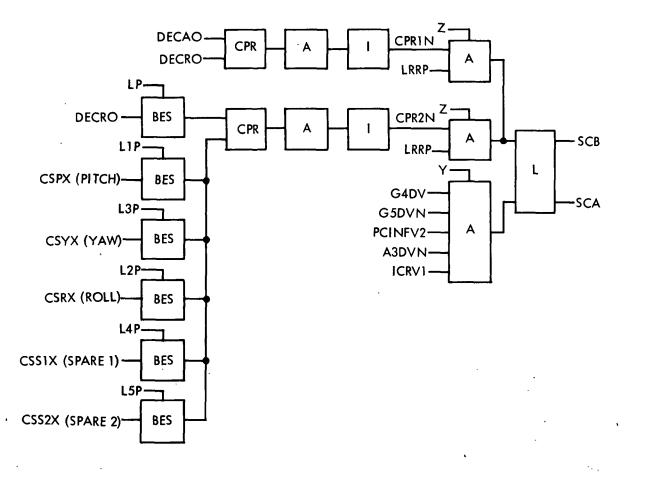

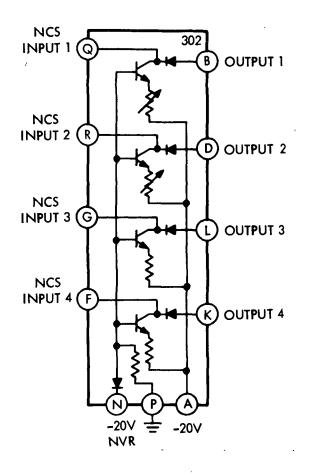

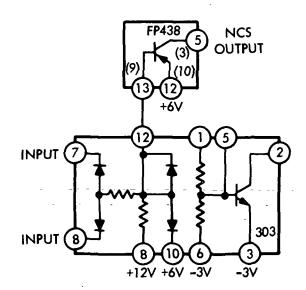

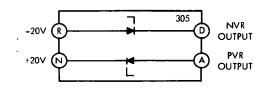

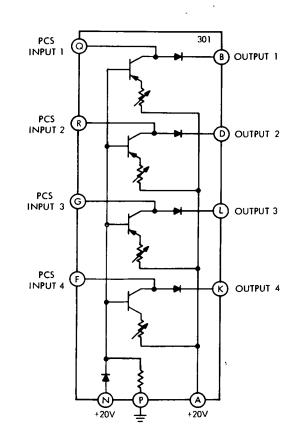

2-68. The frequency generator consists of a control circuit, a three-bit shift register and a frequency divider (figure 2-18). The shift register is so gated that, irrespective of initial conditions when power is first applied, "0's" will be eventually forced into positions 2 and 3. The "0's" are complemented to "1's" on subsequent shifts, and when the resulting series of "1's" emerge from the shift register, they are complemented back to "0's". The shift register, therefore, continuously generates a series of three "1's" followed by three "0's".