The

Launch

Vehicle Digital Computer (LVDC) was a computer that resided in the

Instrument Unit (IU) that perched above the Saturn IVB that was the

second stage in a Saturn IB rocket and the third stage in a Saturn V

rocket. The LVDC was a completely separate computer system

from the AGC, with a different architecture, different

instruction-set, and different runtime software. The purpose

of the LVDC was to precisely control the Saturn from shortly before

liftoff until the point at which the Saturn was discarded by the

CSM.

The

Launch

Vehicle Digital Computer (LVDC) was a computer that resided in the

Instrument Unit (IU) that perched above the Saturn IVB that was the

second stage in a Saturn IB rocket and the third stage in a Saturn V

rocket. The LVDC was a completely separate computer system

from the AGC, with a different architecture, different

instruction-set, and different runtime software. The purpose

of the LVDC was to precisely control the Saturn from shortly before

liftoff until the point at which the Saturn was discarded by the

CSM. |

Factoid

People generally think that the guidance computer (AGC) of

the command module controlled the Saturn rocket, but it

isn't true. During certain burns, it was possible for the

CSM's AGC to control the steering, as a backup to the

LVDC. That backup capability was never used in a

mission. More on

this below. |

|

|

|

Let's talk about how the launch vehicle could interact

with the Command Module's AGC before immersing ourselves

in too much detail about the LVDC specifically. I

may perhaps go into this topic in more detail than suits

your taste, so feel free to ignore this section

entirely! I can just give you the executive

summary: There was very little interaction

between the AGC and the Saturn rocket under normal

circumstances.

I talk about this a lot primarily because it has

sometimes been at the center of spirited arguments for

which I have not necessarily always had all the relevant

facts immediately at my fingertips. (Thanks,

Fabrizio Bernardini.) Well, ... now I will have

those facts lined up when I need them, and so will you.

For the sake of clarity, I've taken the Saturn V block

diagram from the preceding section, chopped out everything

except the Instrument Unit (IU), and added a bit of

coloring to the connections between the IU and the CSM

("SPACECRAFT"):

The launch

vehicle (i.e., the Saturn V or IB rocket) was always directly

steered by the so-called Flight Control Computer (or FCC,

depicted in the picture at the right), an analog computer

whose salient property for our purposes is that it was not

the LVDC. However, the FCC did not operate on its

own, and thus itself needed to be supervised.

Normally, that supervision was performed, by default, by

the LVDC, indirectly through the LVDA, the Launch Vehicle

Data Adapter.

The launch

vehicle (i.e., the Saturn V or IB rocket) was always directly

steered by the so-called Flight Control Computer (or FCC,

depicted in the picture at the right), an analog computer

whose salient property for our purposes is that it was not

the LVDC. However, the FCC did not operate on its

own, and thus itself needed to be supervised.

Normally, that supervision was performed, by default, by

the LVDC, indirectly through the LVDA, the Launch Vehicle

Data Adapter.

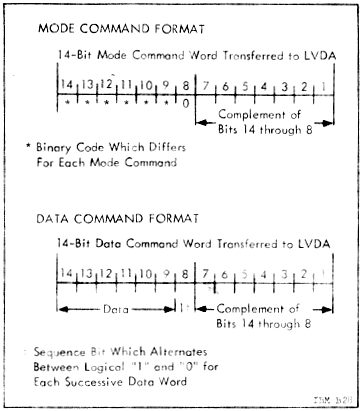

However, it was also possible for the Command Module to

send the flight control computer a signal, the Mode

Command, which instructed it to accept Alternate Steering

Commands from the AGC rather than the default steering

commands from the LVDC/LVDA.

Aside: As far as the detailed mechanisms in the AGC and the Command Module by which this was accomplished are concerned, the Colossus software's program P11 would have presided over the process. Normally P11 would just have been used to monitor the launch vehicle's activity. But if a toggle switch called "LV Guidance" on the CM's control panel (seen to the left) were to be flipped into the position marked "CMC", P11 could detect this via one of the AGC's i/o channels, namely bit 10 of channel 30. In turn, P11 could set bit 9 of i/o channel 12: That's the "Mode Command" signal in the block diagram above, and it's what told the IU that the change of control was taking place. At the same time, P11 would begin sending the "Alternate Steering Commands" to the IU, and those are what performed the actual steering. As it happens, these Alternate Steering Commands were no different than the ones used by the AGC's digital autopilot to steer the CM itself: They were literally the same electrical wires up to the point where they separated to go off to the IU, though controlled within the Colossus software by different polynomial-based flight equations. It's important to recognize that these signals were analog in nature, not digital. Or to put it in other words, the AGC did not control the LVDC. The LVDC was simply completely out of the picture insofar as steering was concerned, once the Mode Command to switch control to the CMC had arrived in the IU. It was also possible during P11 to key in VERB 46 ENTR on the DSKY to disable steering of the launch vehicle by Colossus's digital autopilot and instead allow the CM's Rotational Hand Controller (RHC) to be used by an astronaut to manually send Alternate Steering Commands to the IU.

How much control over the launch vehicle could actually be exercised by the AGC? The Apollo Operations Handbook for the Apollo 16 CM says this: "[Toggling the LV Guidance switch to CMC] allows CMC automatic steering (polynomial guidance) for S-IC stage, and attitude hold commands only, for SII and SIVB stages. Also provides capability of issuing RHC commands via CMC, provided configuration digit in N46 is 3 and V46E is keyed." So the amount of control the AGC could have over the launch vehicle was great, but was not complete.

Could the AGC exercise this control over the launch

vehicle in all Apollo missions? Regarding

Apollo 7, there is presently no information

whatever. But for the remaining missions, No!

The ability for P11 to provide automatic steering wasn't

present in 8 or 9, though it was present in Apollo 10 and

beyond. On the other hand, manual steering via the

Rotational Hand Controller (RHC) was available in Apollo 8

and onward. Unfortunately, there is not enough

surviving documentation presently to have full certainty

about all of the details.

Aside: I draw my conclusions from examination of the Colossus source code. First consider automatic steering. Insofar as Apollo 8 (Colossus 237) and 9 (Colossus 249) are concerned, they did not read bit 10 of i/o channel 30, and therefore could not have known to initiate automatic control. On the other hand, that capability is present in Apollo 10 (a version of Colossus called MANCHE45R2) onward. Admittedly, I have no basis for the assumption that the steering capability was 100% implemented and operational at that juncture. Nor do I have any information as to whether that steering ability was present for every stage of the rocket, or whether it merely applied to the S-IVB stage.

Regarding manual steering via the RHC, every version of Colossus from Apollo 8 onward has the following verbatim comment in P11's source code: "SATURN TAKEOVER FUNCTION ... DURING THE COASTING PHASE OF SIVB ATTACHED, THE ASTRONAUT MAY REQUEST SATURN TAKEOVER THROUGH EXTENDED VERB 46 (BITS 13,14 OF DAPDATR1 SET). THE CMC REGARDS RHC COMMANDS AS BODY-AXES RATE COMMANDS AND IT TRANSMITS THESE TO SATURN AS DC VOLTAGES. THE VALUE OF THE CONSTANT RATE COMMAND IS 0.5 DEG/SEC. AN ABSENCE OF RHC ACTIVITY RESULTS IN A ZERO RATE COMMAND. THE FDAI ERROR NEEDLES WILL INDICATE THE VALUE OF THE RATE COMMAND." This seems pretty conclusive, though it only applies to the "coasting phase", at which point stages S-IC and S-II would have been ejected, so at least on the face of it seems to apply only the S-IVB stage.

Of course, it was also desirable for the CM to be able to

monitor the activity of the Saturn, even under normal

conditions when the LVDC was controlling the rocket.

Since the spacecraft had its own Inertial Measurement Unit

(IMU), it knew its own orientation and acceleration — and

hence the Saturn's orientation and acceleration — at all

times, and the AGC could mathematically integrate these

quantities to know the velocity and position at all

times. Thus it was not necessary for the IU to

communicate that information to the spacecraft in order

for the AGC to monitor the physical motion of the rocket

and to display it for the astronauts on the DSKY.

Which is why there are no signals in the block

diagram showing such state-vector data flowing back from

the IU to the AGC.

Aside: (Refer to the portion of the CSM block diagram at the right.) What about the remaining signals in the Saturn block diagram the we haven't discussed: i.e., the "Abort Decision" and "Status" signals? The block diagram does show an "S-IVB SEPARATE/ABORT" signal directed at the CMC, and it would have been read by the CMC as bit 4 of i/o channel 30. On the other hand, the signal is clearly marked as coming from the control panel switches, and not from the IU, so perhaps there's some additional magic going on with that signal within the control panel. Regarding the IU's Status signals, those would appear to be "LIFTOFF" and "ULLAGE", which are presumably bits 5 and 1 of the CMC's i/o channel 30. The only one of these three signals actually used by Colossus, as far as I can see, is LIFTOFF, though it is used elsewhere in Colossus and not directly by P11.

What would normally happen in P11 with the LV Guidance control-panel switch remaining in the "IU" position as it did in every actual mission, is that VERB 06 NOUN 62 would be used to monitor the following items on the three 5-digit displays of the DSKY: The total inertial velocity in feet per second, the rate of change of altitude in feet per second, and the altitude in nautical miles above the radius of the launch pad.

I actually have an interesting graphic of the monitoring process to show you. This graphic is not from physical system. Rather, Riley Rainey has used the "equation defining document" which specified how the Instrumentation Unit (IU) was supposed to behave, to model the physical behavior of the rocket and the spacecraft's IMU, allowing Virtual AGC to monitor the launch behavior on a simulated DSKY. Here's a short movie he has created of that simulation. It's admittedly a little fuzzy, since I blew it up by about 2×, but perhaps we'll be able to get a better one sometime in the future:

Describing the overall structure of the software loaded into the

LVDC is a bit tricky at the present time. That's because

documentation is scarce, our cache of original LVDC software is

sparse, and the original development process seemed quite

compartmentalized. By the latter, I mean that programmers

concentrated on the specific areas to which they were assigned,

and often seem to have had little cognizance of even the most

basic features of the software when those features happened to be

outside their narrow specialization. Plus the set of LVDC

programmers available to me is limited, so I don't have

representatives of all of those specializations to consult

with. Of course, it's also possible that the many decades

between the time they spent working on the project and the time I

was able to quiz them about it may also have acted to erase some

of the information.

In short, important aspects of my descriptions in these sections

concerning the gross structure of the software are based on

my own inferences and on the recollections of developers not

entirely familiar with the details. So take my comments

about the program structure with a large grain of salt. Of

course, as more LVDC code has dribbled in over the years, more of

it has become susceptible to reverse engineering as well.

With that said, let's contrast the overall structure of the LVDC

code vs the software source code for the Apollo Guidance Computer

(the programs COLOSSUS, LUMINARY, and so on) and for the Abort Guidance System. All of these

non-LVDC programs were monolithic in nature. What I

mean by that is that although the AGC and AGS software was

structured into various semi-independent sections, for which the

development of each was presided over by specialists in those

specific areas, the source code for them was nevertheless

presented to the programmers in a single large chunk — i.e., a

single, unified program listing. Every AGC or AGS developer

saw the entire source code, regardless of whether it pertained to

them or not. The natural result was that it was possible

(and even likely) for an AGC or AGS developer to have some grasp

of the large-scale structure of the software, beyond his or her

own narrow area of specialization. Similarly, every word

stored in the AGC or AGS core memory came from that source

code. In that sense, each AGC or AGS program listing was

entirely self-contained. If you were able to assemble those

program listings, then you obtained a rope image that could be

loaded into the computer and run. Conversely, every word in

core-memory either came directly from the associated program

listing or from some action taken by the code in that program

listing. When you look at an ABC program listing for (say)

LUMINARY, you see the entire contents of the Lunar

Module's AGC's core memory. Moreover, almost all of the AGC

executable code was stored in read-only memory, and thus the AGC

programs contained no self-modifying code; once again, what you

saw in the program listings was what you got! (An exception

could be the relatively-tiny amount of Erasable Memory Programs,

or EMPs. Since these were loaded separately and were in

read-write memory, they were not shown in the main program listing

and could in theory be self-modifying.)

The overall structure of the LVDC software, however, is

fundamentally different. For one thing, the entire memory of

the LVDC was read-write, and thus software could be and was

sometimes self-modifying during operation. Moreover,

simultaneously loaded into the LVDC core memory were several

different logically-distinct "programs", each with different

sets of source code, assembled separately from each other,

and having different areas of specialization. Thus assembly

of any given one of these programs did not produce a full

core-rope image: merely a partial rope image. A full rope

image could be obtained only by merging all of the partial

core-rope images from the different assemblies of the several sets

of source code. The separate programs I'm aware of are

discussed individually in the sections that follow, but in brief,

they were:

A similar situation arises in modern computer systems, where you

typically have an "operating system" program and "application

programs" running in the computer at the same time. The

application programs rely on the operating system for certain

functionality, but have no understanding of how the operating

system provides that functionality. All the application

program needs to know is the exact method for requesting the

desired function from the operating system. Similarly, the

operation system stands ready to provide the desired

functionality, but has no knowledge of the internal workings of

the application program requesting service. The model of a

"BIOS" and software running atop the BIOS is even more á

propos, though that may be a concept no longer meaningful

enough to most computer programmers to be very illustrative.

In the LVDC, the method by which interaction between independent

but simultaneously-loaded programs worked was for there to be an

agreed-upon set of specific memory addresses hard coded into the

programs. For example, one program would know that to obtain

a certain type of service, it had to call a routine at a certain

fixed address in memory. Another program would know that it

had to put code providing certain types of services at certain

fixed addresses, but have no other knowledge of the program(s)

utilizing that functionality.

Because of this much higher degree of compartmentalization,

programmers working on (say) the Flight Program might have no

cognizance at all of the Preflight Program, the developers of

which might have no cognizance of the Flight Program. And

unfortunately, that means that we don't have a lot of

understanding of it either.

With all of that said, later Flight Programs like AS-512 and

AS-513 appear to have much less reliance on the Preflight Program,

to the extent that they may be able to operate with essentially a

skeleton version of the Preflight Program. While this claim

hasn't yet been fully analyzed as of this writing, it appears as

though the only parts of the Preflight Program desired by the

Flight Program may be:

Consequently, for some purposes, a skeleton Preflight Program

could consist essentially of nothing but boot code.

Until recently (as I write this), little about the Preflight

Program has been known. Just from inspection of the

available LVDC Flight Program source code, some inferences were

possible. For example:

The software was apparently known simply as the Flight Program,

and didn't have a catchy name such as "Luminary" or "Colossus".

You may also see references to the Generalized Flight Program (GFP) or generalized Flight Program System, in use from Apollo 12 onward. At that point the flight program was restructured for easier maintenance on a mission-by-mission basic, and that's where the "generalized" comes from.

Was the Flight Program classified in a national-security sense? No. Or at least it was not classified at the time period from which we begin to have any information. Several people associated with the development have stated to me that it was classified. But classified material must be stamped with one of the designations CONFIDENTIAL, SECRET, or TOP SECRET, not to mention having strict controls on availability. In other words, if this software was classified, it's highly unlikely we would have any access to it via parties who simply walked off it it ... current behavior by well-known national figures suggesting otherwise notwithstanding. Moreover, the available software listings are not so stamped, and therefore should not be considered classified. Undoubtedly IBM Federal Systems Division considered it "confidential" at the time, in the sense that like every other organization they reflexively wanted to hide it for their own private corporate reasons, but that doesn't make it classified in the sense of national security.| Mission |

Program |

Source Code |

Other Mission-Specific Documentation |

Notes |

|---|---|---|---|---|

| N/A |

PTC ADAPT Self-Test Program |

Page

Images or Transcribed Source-Code File or Colorized Syntax-Highlighted Assembly Listing |

"Saturn

V Laboratory Maintenance Instruction for LTE" |

This is not flight software as such, but

rather the software used for ground-test equipment known as

the Programmable Test Controller (PTC). The

PTC included a modified LVDC and a complex test panel with

many facilities for stepping through code, setting

breakpoints on code or data, etc. There's an extensive

write-up in the section titled "PTC ADAPT Self-Test

(PAST) Program" below. |

| AS-206RAM (unflown) |

Flight

Program |

We're currently treating LVDC

code as if it is restricted for export from the U.S. by the

International Traffic in Arms Regulations (ITAR). If

you legally qualify as a "U.S. person" and can provide

evidence of that status, contact us directly to arrange to

receive a copy of the code. |

"AS-206 S-IVB Restart

Alternate Mission Launch Vehicle Operational Flight

Trajectory" |

AS-206RAM was an alternate mission profile

which was never flown, and this is the LVDC flight software

for it as provided by an anonymous donor. Or rather,

it's an uncompleted and not-fully-debugged development

version of that software. The mission itself was

principally to get a Saturn S-IVB stage into orbit, and then

to test that the S-IVB's engine could be restarted after it

had been turned off for a while. Which obviously would

have been a good thing to know if you were depending on it! Although LVDC assembly-listing printouts

such as the one that provided this code were not printed

with dates or other identifying information (unless

programmers chose to explicitly include such information

in the source code itself), the mainframe that performed

the compilation sometimes provided additional information

about the printout. I've unfortunately been forced

to omit from the scans that extra bit of information (it's

not much!) due to anonymity concerns; however, I can say

that the assembly-listing printout was made on September

7, 1967. That's consistent with AS-206RAM, as the

documentation (see the link to the left) for that mission

is dated September 15, 1967.

There's a more-extensive write-up in the section titled "AS-206RAM Flight Program" below. |

| AS-512 (Apollo 17) |

Flight

Program |

We're currently treating LVDC code as if it is restricted for export from the U.S. by the International Traffic in Arms Regulations (ITAR). If you legally qualify as a "U.S. person" and can provide evidence of that status, contact us directly to arrange to receive a copy of the code. |  Apollo 17 (AS-512) was, of course, the final

flown lunar-landing mission of Apollo. Apollo 17 (AS-512) was, of course, the final

flown lunar-landing mission of Apollo.As far as we can tell, this is the complete Flight Program used in the actual mission. Lacking the associated Preflight Program, though, it still leaves us a bit short of having the full set of LVDC software for the mission, though perhaps only barely short. Unfortunately, the creators of the original LVDC compiler didn't see fit to include such niceties on their printouts as the date or code version, or at least not in any way we can unambiguously decipher it now, nor did the writers of the code see fit include such information (or even the Apollo mission number) within the code. In other words, the printout itself doesn't actually provide much direct support for the claim that this code was flown on Apollo 17, or indeed anywhere at all. And alas, the surviving owners of the printout appear to have had no knowledge at all of the nature of the material in their possession, with the original owner unfortunately being deceased by the time we became aware of the printout. We believe this code was flown on Apollo 17 partially because of the handwritten markings on the printout, which you can see in the photo to the right ... made at some unknown time by some unknown person. As it happens, there is a somewhat-cryptic notation in the assembler's messages which could be relevant, if we assume that "FT-512-1" stands for "Flight Program AS-512":  Besides which, I'm told that the assembly listing does include various presettings which are consistent with Apollo 17. For example, on p. 31 of the listing we find that something called P.DATE was set to 341. Apollo 17 launched on December 7, 1972, and December 6 was the 341st day of 1972. |

|

| AS-513 (Skylab 1) |

Flight

Program |

We're currently treating LVDC code as if it is restricted for export from the U.S. by the International Traffic in Arms Regulations (ITAR). If you legally qualify as a "U.S. person" and can provide evidence of that status, contact us directly to arrange to receive a copy of the code. | Skylab 1 (AS-513) was the mission that

launched Skylab into orbit. It was an unmanned

mission, succeeded almost immediately by the manned Skylab 2

mission, and then later by the manned Skylab 3 and 4

missions. As you may recall, Skylab itself was based

upon a modified Saturn S-IVB stage, without the usual

propulsion provided by that stage, but with the

S-IVB's Instrumentation Unit (IU) containing the LVDC and

controlling the other stages of the rocket. Thus the

launch was essentially a normal Saturn V launch, but with a

modified third stage. As far as we can tell, this is the complete Flight Program, though whether it was actually flown on the mission or is instead some earlier revision of the code we can't say for sure ... but we think it was. Of course, lacking the matching Preflight Program, it does not by itself provide the full LVDC software for the mission in either case, but even if not, it almost does so. As far as our claim that this code was associated with the Skylab 1 mission is concerned, the evidence consists partially of the handwritten notation seen in the photo below of the physical printout. Next to it, you see also a similar notation on the AS-512 printout, which was received from the same owners at the same time, so we're entitled to have roughly the same level of trust in the handwritten notation for AS-513 as we do for AS-512.  Moreover, the assembler's messages do include the following  and we presume that "FT-513-1" is interpreted as "AS-513 Flight Program". The presettings embedded in the code are reasonably clear too. Consider this excerpt from p. 34 of the assembly listing:  Skylab 1 was launched on May 14, 1973, while day 119 of 1973 was April 29. Those dates are pretty close. But according to NASA, ... a few minor issues led NASA managers on Jan. 15, 1973, to announce a delay of two weeks for the dual launches. The Skylab 1 launch slipped from April 30 to May 14, ... so day 119 (April 29) was indeed

very, very close to the intended

launch date for Skylab 1, so it wouldn't be

surprising for it to be hardcoded.

|

|

| AS-207 (Skylab 3) |

Flight

Program |

Perhaps

some day ... |

"Flight

Simulation Malfunction Overall Test Report" PDF or Full-resolution page images "Saturn IB Launch Vehicle Flight Evaluation Report-SA-207 (SKYLAB 3)" "Skylab Saturn IB Flight Manual" |

Skylab 3 (AS-207) was the 2nd crewed

mission to Skylab. We don't actually have a program

listing for its LVDC at present. But we do have some

interesting related documentation that seems to me to

justify making an entry for it in this table anyway. It's open to question exactly what the "test report" linked at the left is. It arrived at our doorstep with no explanation, so after a bit of research I'm giving you my own personal speculations rather than any official story. Aside from the clues within the printout itself, which are the page headings DATE 04/26/73we also have the handwritten markings on the cover page and the page edges:   No, Malcolm Oats is not

the name of a heroic aerospace engineer in a

"thriller" novel. I think. (But feel free

to use it, if you're writing one!)

The acronym OAT appears in the various Launch Vehicle Flight Evaluation Reports, and specifically the one for Skylab 3 whose link(s) are to the left. OAT stands for Overall Test. For example, the Skylab 3 report specifically gives a timeline that includes "Malfunction Overall Test (OAT)" on June 19,1973. I actually find three types of OAT listed in that (and other) documentation, namely "Space Vehicle OAT No. 1 (Plugs In)", "Launch Vehicle Swing Arm OAT", and "Malfunction OAT". So I think it's reasonable to suppose that a "SIM FLT MAL OAT" would be a "simulated-flight malfunction overall test", or some variation thereof. In other words, our report would be a MAL OAT using simulated flight data, performed prior to the actual MAL OAT using the physical Saturn IB. The MAL OAT itself appears

to be simply a timestamped log of all the

launch-vehicle events that the OAT was capable of

detecting, and those events appear to be the ON/OFF

states of various signal wires. The exact

interpretations are open to question, as I've not yet

found any specific documentation as to how to read MAL

OAT tests. Each event is marked with a

designation like "DDA", "DEE", "LDO", "LDI", "MDO", or

"MDI". "DDA" may stand for "Digital Data

Acquisition"; the Saturn Flight Manual explains, among

other things, that

Telemetry system GP1 is a PCM/DDAS link that transmits realtime checkout data before launch, and measuring program information during flight.Which sound promising, if hardly definitive. Similarly, "DEE" may stand for "Digital Events Evaluator": The digital event evaluators (DEE) are used to monitor the status of input lines and generate a time tagged printout for each detected change in input status.As for "LDO" et al, you might suppose that a trailing "I" refers to input while a trailing "O" refers to output. Of course, what's an "input" vs what's an "output" would depend on your point of view: An "output" from the LVDC is an "input" to the device receiving the signal from the LVDC. So the most we could infer from this is that "I" and "O" signals may be going in opposite directions. For example, given a sequence of notations from the bottom of p. 1 of the report like ... perhaps one could infer that the

"decoder" had been powered on at time 0.472, checked at

time 0.532 to verify that it had been turned on, and so

forth. Or perhaps not.

At any rate, the reason I'm droning on about this report is that if the report really is a log of such events, and if the report could be interpreted properly, then it could perhaps also give us a reasonable timeline of the activities the LVDC was performing; i.e., which of its outputs it was controlling and which of its inputs it was interrogating. That could be useful in assessing simulated runs of other LVDC software versions. With that said, don't assume too much similarity between the Skylab 1 mission (for which we have the software) and the Skylab 3 mission (for which we don't). Skylab 1 used a modified Saturn V launch vehicle, whereas Skylab 3 used a Saturn IB launch vehicle, so the LVDC software must have been configured pretty differently between those two missions. |

Aside: You may wonder why there's an extensive write-up here of the unflown AS-206RAM Flight Program, whereas there is little to-do made of seemingly more-importation flight programs like the one for AS-512 (Apollo 17). (And similarly for the PTC software write-up in the next section.) But it's not some kind of snarky comment on the relative significance of AS-206RAM vs AS-512. It's just that when this write-up was done, AS-206RAM was the only LVDC code known to exist. And naturally, finding it was therefore a very big deal and I made a big fuss over it! A lot of the description below would be relevant to other versions of the Flight Program as well.To a computer programmer, the most important thing about any computer program is its source code, and at present not many versions of the LVDC Flight Program are available to us. (For some non-flight LVDC software, see the PAST program described in the next section.) The Flight Program at issue in this section is an engineering revision of the software, from September 1967, designated "AS-206RAM LVDC FLIGHT PROGRAM". If you were to Google this (don't do it!), you may confuse yourself by noting that Saturn IB launch vehicle AS-206 was used for the Skylab 2 mission (Conrad/Weitz/Kerwin). But the Skylab 2 mission was in 1973, far past the 1967 time frame in which this revision of the program is developed. What gives? The answer, is that AS-206 was originally intended for an unmanned mission that was canceled after the Apollo 1 fire. The software we have is not even for that canceled early AS-206 mission, but rather for a proposed backup to the canceled mission. So whatever software the LVDC had when AS-206 eventually launched as Skylab 2, is not this software. That doesn't alter the fact that this software is ancestral to the versions that followed it ... or at least a very close cousin to the ancestor of the versions following it. There are some references in the software to AS-205, which is what would have been Apollo 2 (the 2nd manned Apollo mission) had the tragic Apollo 1 fire not occurred; naturally, Apollo 2 was canceled thereafter. The designation AS-205 was later used instead for Apollo 7, though considering the time-frames involved, it's likely that the reference in the source code is to Apollo 2 rather than Apollo 7. In other words, the our AS-206RAM flight program had likely been branched off from the LVDC software being developed for the never-flown Apollo 2 mission.

The basic purpose of the Apollo Saturn 206 S-IVB Restart Alternate Mission is to place the S-IVB stage into orbit and test its restart capability, simulating the AS-501 mission profile. In the event S-IVB restart problems occur in the early Saturn V flights, this mission will be flown to help correct or solve the problems. The primary objective of the SA-206 Launch Vehicle is to insert the S-IVB/IU/Payload configuration into a near earth 100 nautical mile circular orbit. The payload consists of a Spacecraft LM Adapter (SLA) and a 25° Nose Cone (NC #2).As usual in these matters, what we have is not the punch cards on which the assembly-language source code was originally provided to the assembler program, but rather the "assembly listing" output by the assembler. Unfortunately, the status of the original assembly process for it found 41 warnings and 7 errors — meaning that there were problems in the source code and that the assembly process failed. Thus our listing represents an uncompleted development version that wouldn't actually work as-is anyway. That doesn't reduce its instructional value any, though, and it doesn't mean that some enterprising individual couldn't fix it up now to make it work! In fact, it's quite easy to get rid of the assembly-time errors, though whether or not that is adequate to get the program into a working state is questionable.

Aside: As far as assembly-time warnings are concerned, almost all warning messages produced by the original LVDC assembler, or for that matter the modern LVDC assembler we'll talk about below, are simply indications that some memory location which naively would be in the direct path of the assembly process had already been allocated for some other purpose. The assembler was able in those cases to transparently jump past the already-allocated locations, so other than the fact that slightly more memory and execution time was used to do so, there's no significant negative impact. In other words, these "warnings" are really typically just informational messages that such a bypassing jump had been added by the assembler. So while 41 warnings sounds like quite a lot, they really mean little, and are not an indication of a problem in most cases. In comparison, the AS-512 flight program, which is the final flight version and was fully debugged (to the extent that the original developers chose to debug it) itself has a couple of hundred of these warnings.

When I say "we" have a copy of this assembly listing, however, there's an unfortunate proviso. In the U.S. there is something called the International Traffic in Arms Regulations (ITAR), which prevents export of certain technologies from the U.S. except under strict controls. Under my non-expert, non-lawyer reading of the ITAR, the LVDC might be such a device whose export is prohibited. However, I cannot personally figure out whether the LVDC's software would also therefore be restricted. If it were restricted, then freely providing the software online would be regarded as "exporting" it, and would therefore also be prohibited! Legal assistance is working through the slow process of getting an official ruling on this matter, so perhaps one day will have a more-definitive answer as to what we can and cannot do with this software from a legal standpoint. But so far, many years have been spent on this effort, so I wouldn't recommend holding your breath. As it happens, the source code from

all available assembly-listing printouts have been

entirely transcribed into machine readable form.

Those are a lot more convenient to deal with than

scanned page images, since you can do things like text

searches on them, or even assemble them using the nifty

LVDC assembler I've written (see below). The

problem, of course, is that the transcribed source code

is just as much subject (or hopefully, it will

eventually turn out, not subject) to ITAR export

restrictions as the scanned images are, so this LVDC

source code is not presently available in our software

repository. The process for convincing me that you are a "United States person" has traditionally been somewhat cumbersome, and has typically involved sending me digital images of appropriate documentation, along with a video telephone call so that I can verify that your appearance matches photo ID. It is, of course, unwise for you to send such personal information to untrusted people — me! — that you've met online. Another alternative would be for you to pay a lawyer to provide me with a letter assuring your status as a United States person, which relieves both of us of the burden of trusting each other ... but which probably involves a monetary expenditure on your part. |

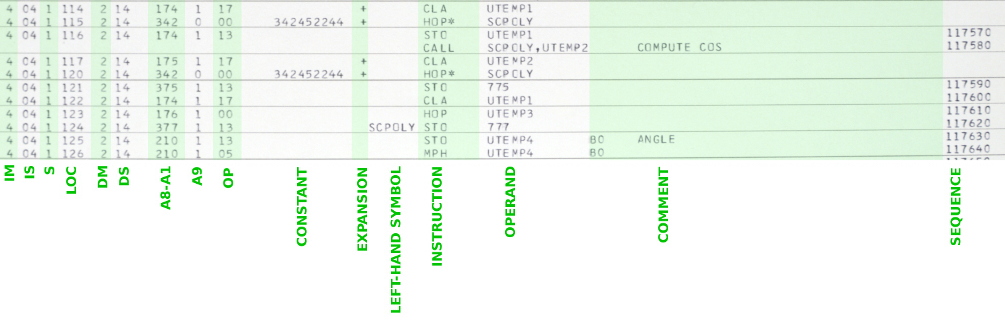

Aside: Alternately, some of the points I make in the following discussion are probably illustrated equally well by the non-flight PAST program discussed in the next section, which is definitely not restricted by ITAR and hence can be viewed in full by everybody. Unfortunately, I didn't have a copy of the PAST program, or even know of its existence, when I wrote up this section.At the time I originally wrote this description, the afore-mentioned abridged AS-206RAM code was something under constant revision, so I chose to illustrate the discussion with the scanned page images. Here are various images of pages of the assembly listing that illustrate things like how constants and variables are defined by the software, how some standard mathematical functions are encoded, and some of the tabular data generated by the assembler:

The middle group of pages above shows a few auxiliary subroutines

for computing the sine, cosine, arctangent, and spare root

functions, plus a 3×3 matrix-multiply routine. Note that

these are some of the very algorithms described in section 13 of the

EDD (LVDC Equation Defining Document), so the source code

can actually be compared to the defining documentation if one so

desired. The two images at the top show an area of the

program where some constants are defined, while the two at the

bottom show a portion of the assembly listing's cross-reference

table.

Regarding preloaded constants for LVDC memory, all missions (I

think!) were associated with a report called the "launch vehicle

operational flight trajectory", and these documents (among other

things) listed the LVDC preload settings. Unfortunately,

most of these reports are presently unavailable, though we do have a few of them. For

example, the AS-202 report says that "LVDC symbol" T1i,

the time-to-go for first IGM stage, is preloaded with 299.25 sec,

while Vex1, the J2 exhaust velocity for first IGM

stage, is loaded with 4165.45 m/sec, and so on.

Finally, I claimed earlier that the AS-206RAM Flight Program is

not, of itself, a complete program. In that assessment, I'm

not referring to the fact that when you try to assemble it you

find that there are a few missing symbols, associated with

variables that haven't been allocated. That problem

is simply due to the fact that the listing we have is an

engineering version of the code that had never been debugged to

the point of being released. It's quite easy, I think, to

fix up the assembly-time errors and warnings in the AS-206RAM so

that it assembles error-free, and is entirely self-contained in

that sense. But it is still not complete in the larger sense

I mean.

Rather, when I say that AS-206RAM is incomplete, I mean that it

references code at specific hard-coded addresses which are not

defined by the AS-206RAM program. Indeed, there are large

areas of core memory left undefined by the program. Even the

location in memory at which the power-up entry point should be

stored is left undefined. But for example, consider the

concrete example of the code necessary for processing commands

uploaded to the LVDC from mission control, as described in the Up-data section of this web-page.

When such a command is uploaded to the LVDC, an interrupt

occurs. The software then looks in an interrupt-vector

table, which appears on p. 207 of the program listing, and looks

like the following:

This

section concerns the "PTC ADAPT Self-Test Program".

Since "PTC ADAPT Self-Test Program" is quite a mouthful, I'll

just refer to it as the PAST program. Not only is that

nice and short, it's also apt since the PAST program

chronologically preceded the AS206-RAM Flight Program

discussed in the preceding section.

This

section concerns the "PTC ADAPT Self-Test Program".

Since "PTC ADAPT Self-Test Program" is quite a mouthful, I'll

just refer to it as the PAST program. Not only is that

nice and short, it's also apt since the PAST program

chronologically preceded the AS206-RAM Flight Program

discussed in the preceding section. ![]() But

beware: The acronym "PAST" is mine, and doesn't come

from the contemporary Apollo documentation.

But

beware: The acronym "PAST" is mine, and doesn't come

from the contemporary Apollo documentation.

Strictly speaking, the PAST program is actually not "LVDC"

software, and it is certainly not flight

software. But it's really quite significant in spite of

that, and shouldn't be ignored if you're interested

technically in the LVDC itself, rather than merely how the

LVDC fits into the context of the launch vehicle. The

PAST program fills in an important gaps in our understanding

of the LVDC and it is technically so close to being "LVDC

software" that it's really a matter of opinion as to whether

you want to label it as LVDC software or not.

(Hint: I do want to call it that.) Let's

begin the explanation with a little acronym-rich terminology:

The PTC is

documented here. (A tiny bit of

ADAPT and ASTEC documentation is here.) This PTC

documentation includes (in Chapter 7) a printout of the

assembly listing of the PAST program and is our only-known

source for it.

But it's not necessary to go into great detail about the PTC,

ADAPT, and ASTEC at the moment. Indeed, for our

immediate purposes, we can ignore the ADAPT and ASTEC entirely

and the only important things to know about the PTC are:

In some sense, you can think of the PTC as a large LVDC that

has been fixed up to allow various kinds of debugging

activities. For example, the PTC provides support via

circuitry enabling things like single-stepping through the

software. (In the PTC documentation, see section 2-80,

"External Control Element"; section 2-216, "External Control

Logic Circuits".) It's the fact that the PTC's CPU is a

"modified" LVDC which means the PAST program is not strictly

LVDC software. Rather, it's modified-LVDC

software. Still, except for small number of differences

I'll list in a minute, the PAST program matches LVDC Flight

Program syntax. Indeed, its assembly listing has clearly

been produced by the LVDC assembler program, although there

are a few differences in the way some of the output is

formatted. In terms of how the PTC's CPU has been

"modified" relative to the LVDC, those changes are described

in detail later but here's a list of some of the differences

visible at the software level, though admittedly it may not be

too meaningful to you until you study more about how the LVDC

works (and particularly its instruction set) later on:

How can I justify my claim that the PAST program is

"significant" and thus deserves your attention? There

are actually quite a few reasons to think so:

As far as the versioning of the software, there is nothing

embedded within the assembly listing itself which dates

it. However, given that it is printed in the PTC

document mentioned above, which is dated 5 MARCH 1965, I think

we can tentatively suppose that the PAST program too is from

early 1965. (Whereas the AS206-RAM program is from late

1967.)

Beyond that, there's also the academic question of the

versioning of the LVDC assembler used. Both the feature

set and the format of the output is more primitive in the PAST

assembly than in the AS206-RAM assembly. For all these

reasons, it's fair to infer that an earlier version of the

assembler was used for the PTC assembly, in which various

more-advanced convenience features did not yet exist.

The PAST program's source code has been transcribed into

textual form, so that it can be assembled.

You can get that source code from our software repository:

Folder in our GitHub repository for PAST program source-code files

I should note that while this code assembles 100% correctly —

i.e., without errors, and producing octal executables 100%

identical to those of the original scanned assembly listing —

there were nevertheless some behaviors (and perhaps bugs) of

the original assembler that I've not yet been able to figure

out how to mimic in the modern assembler. Thus to get an

assembled output identical to the original, some workaround

code consisting of a handful of ORG, DOG,

and TRA pseudo-ops and instructions have been

inserted into the source code. Hopefully it will be

possible to update the modern assembler at some point in the

future, and thus eliminate the workarounds.

You can also look at the scanned assembly listing created by

the Apollo-era assembler. To make it a little more

convenient to work with, I've extracted the listing from the

original scanned PTC document linked earlier, so that it can

be viewed as a set of image files, one per scanned page of the

listing:

Here's a quick index to the zipfile:

These images correspond to the original PTC document's pages

434-717. In general, the entire Chapter 7

("Calibration") of that document is relevant, as it contains

detailed flowcharts for the program, in addition to operating

instructions. Chapter 2 ("Theory of Operation") contains

detailed information about the PTC CPU and its peripheral

devices.

Aside: For a very long time, I had instead stated that at boot-up the LVDC acted as if there were a HOP constant (see below) stored at address 0-00-000, and that the starting instruction pointer, data-memory module, and data-memory sector were determined by this HOP constant. It now appears that the LVDC documentation was somewhat ambiguous — or in vulgar terms, wrong, making me wrong as well — on this point, and that LVDC booted up in the same manner as the PTC, as described in the preceding paragraph.

Aside: The "residual sectors" provide a flexible way of accessing variables. On the other hand, they could be used to hold instructions as well as variables. It's just that by doing so, you can only access instructions if the currently-selected instruction sector happens to point to that selfsame residual sector. In other words, you can't access instructions by using the A9 address bit I mentioned above, and that A9 bit is what makes the residual sectors special in the first place. So if the residual sector is used to store instructions, you're basically not taking advantage of its special features, and are simply treating it like any other memory sector. That's kind of a waste, given that only ~7% of LVDC memory resides in residual sectors, and an even tinier fraction of PTC memory. It's in accessing variables rather than instructions that the residual sector shines. Nevertheless, with that said, both the AS-512 and AS-513 Flight Programs do devote a couple of residual sectors to instructions rather than to data. Whether or not it's worthwhile doing that just depends on your particular needs. If you use the EXM instruction (see below), you'll definitely need to store at least a few instructions in residual sectors.Memory-sector selection and the "residual sector" become clearer when contemplating the HOP Register mentioned earlier. Here is the LVDC's version of the HOP Register:

|

|

Mnemonic |

A 8 |

A 9 |

O P 4 |

O P 3 |

O P 2 |

O P 1 |

Timing (computer cycles) |

Description of the instruction |

|||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| HOP HOP* |

0 |

0 |

0 |

0 |

1 |

The HOP instruction provides an unconditional

jump instruction that also simultaneously changes the

instruction-memory and data-memory contexts. To

perform this operation, a "HOP constant" is needed,

specifying not only the desired instruction-memory sector

and data-memory sector, but the target offset into the

desired instruction-memory sector as well. The operand

is the address of the memory location (in the current or

residual data sector) containing the HOP constant. The following example codes an unconditional jump from HERE to THERE by means of a HOP: HERE HOP HTHEREThe need to explicitly code the HOP constant for every jump is is obviously a big pain in the neck, though convenient if the target location changes throughout execution rather than being known at assembly time. Alternatively, in assembly listings you'll also sometimes see the "instruction" HOP*. But there is no machine instruction such as HOP*. At the machine level there is only HOP, as described in the preceding paragraph. Rather, the presence of the "*" indicates an assembly-language convention that's a workaround for the inconvenience of having to hard-code HOP constants. The convention is that HOP*'s operand can be a left-hand symbol for the target location in the code rather than the left-hand symbol of a HOP constant of that target location. The example code above would change to something like this: HERE HOP* THEREBut the apparent simplicity of HOP* conceals a lot of stuff under the surface. What the assembler does for HOP* is to automatically allocate what I earlier called HTHERE:

See also TRA, TMI, TNZ. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| MPY |

0 |

0 |

0 |

1 |

1 (results available after 4) |

LVDC only ... not PTC. This is a multiplication instruction. It multiplies two 24-bit numbers to produce a 26-bit product. The accumulator provides the address of one operand, and the address embedded in the instruction points to the other operand. Recall that A1-A8 select the offset within a 256-word sector, and A9 is the "residual bit" that selects between the current sector and the "residual sector". In both cases, the most-significant 24-bits of the operands are used, and the least-significant 2 bits of the operand are ignored. A partial product (24 bits from the addressed memory times the 12 less-significant bits from the accumulator) can be fetched from the P-Q Register (0775 octal) on the 2nd instruction (or more accurately, two computer cycles) following MPY, though there is no need to do so if that value isn't desired by the program. The full product is available from the accumulator or from the P-Q Register on the 4th instruction (more accurately, 4 computer cycles) following MPY. However, the result will remain in the P-Q register until the next MPH, MPY, or DIV. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| PRS |

0 |

0 |

0 |

0 |

1 |

TBD |

PTC only ... not

LVDC This is a "print store" operation. Here's what the PTC documentation (see p. V-2-22) has to say about it: Initiates a printer operation. That rather laconic description is trying to tell you that the PRS instruction can send either 4 or 12 characters to the printer peripheral, for printing. In assembly language, the operand of the instruction is always a literal 3-digit octal number or else a symbolic label representing a memory address in the range 0008 to 7738. Recall that addresses in the range 4008 to 7778 refer to addresses 4008 to 7778 in the residual memory sector. See also the discussion of the BCI pseudo-op, farther down on this page, which is a convenient way in assembly language to encode memory-operand data for PRS. Each PRS instruction conveys 26 bits of data to the printer, and that 26-bit word is capable of encoding either 4 or 12 characters. The number of characters encoded depends on whether the printer is in "octal mode" (activated by the CIO 164 instruction) or "BCD mode" (activated by the CIO 170 instruction). The term "BCD mode" is a misnomer, in modern terms, since it would seem to imply that it covers only Binary Coded Decimals, whereas in fact it covers the complete repertoire of printable characters. Besides those, see also CIO 160, which conveys certain control commands to the printer. In octal mode, the 26 data bits comprise 8 octal character encoded as 3 bits each (000="0", 001="1", ..., 111="7"), plus a single "2-bit character", plus three blanks (which are always present, and thus require no bits to encode). So far, I've found no written explanation of what these "2-bit characters" are, but due to the way 26-bit data words are invariably represented in LVDC/PTC assembly listings — namely, as 9 octal digits with the final one being even — I feel confident that the 9th character is encoded as 00="0", 01="2", 10="4", 11="6". In BCD mode, the 26 data bits comprise 4 6-bit character code, left-aligned in the data word. In other words, the first character's most-significant bit appears at the SIGN bit of the 26-bit word. The least-significant 2 bits of the data word are not used as far as I can tell. (That's a pity, because it seems to me that it would be reasonable to use them to indicate how many characters the word contained, rather than just always being 4. Alas, that doesn't seem to be the case.) The 6-bit encoding scheme, called "BA8421", is covered in the discussion of the BCI pseudo-op. The PRS instruction has a side effect: It overwrites the interrupt latch. This potentially triggers interrupts if not inhibited; or, more usefully, the interrupt latch can be read back using the CIO 154 instruction for self-test purposes. Which particular bits are set depends on which characters are being printed. I can't give you too satisfactory a rationale as to the particular bit patterns used. Nor are they documented (unless they can be deduced from the 2nd-level schematics, which I've failed at so far). So all I can do is infer the bit patterns from how the PAST program source code uses them. But take what I say with a big grain of salt, because there's no unique way of making these inferences! With that said, here are the rules for deriving the interrupt-latch patterns that I've built into the PTC emulation software. The bit patterns are all 12-bit codes (stored in SIGN and bits 1-11 of the interrupt latch) as follows:

The parity bit for character data appears to be an odd

parity bit for the most-recently processed

character of the 4 (BCD mode) or 12 (octal mode) encoded

in the 26-bit data word at the time CIO 154 is

issued to read back the interrupt latch. The

characters are processed sequentially after the PRS

instruction is executed. The 4 characters in BCD

mode can be processed within a single CPU instruction

cycle, but the 12 characters in octal mode cannot be, and

require two instruction cycles to fully process. I

think that the timing for this processing is not

synchronized with the CPU clock, and indeed has some

tolerance in terms of frequency, so that it cannot be

known deterministically how many characters have been

processed until enough machine cycles have elapsed to

guarantee that all characters have been

processed. I suspect that's why all octal-mode PRS

test cases in the PAST program consist of strings of

characters having all the same parity; that way,

it doesn't matter which specific character has just been

processed, because the parity of each character is the

same anyway. This leaves many questions unanswered about the precise

original behavior of the PTC panel. Therefore,

ignoring the original behavior and thinking just in terms

of how the PTC emulation implements the parity in

the face of this indeterminacy, I recognize 3 distinct

cases:

PRS something

PRS something

Any intervening CIO or PIO instructions that result in a modification of the interrupt latch will prevent the parity-check bit from appearing in CIO 154.PRS something |

||||||||||||||||||||||||||||||||||||||||||||||||||

| SUB |

0 |

0 |

1 |

0 |

1 |

Subtracts the contents of a word pointed to by the address

embedded within the instruction from the accumulator, and

puts the result back into the accumulator. Recall that

A1-A8 select the offset within a 256-word sector, and A9 is

the "residual bit" that selects between the current sector

and the "residual sector". See also RSU. Regarding borrow from the operation, the CPU provides no direct way of accessing it, and thus no easy way to perform multi-precision subtraction. Refer to the notes for the ADD instruction for more information. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| DIV |

0 |

0 |

1 |

1 |

1 (results available after 8) |

LVDC only ... not PTC. This is the division instruction. The contents of the accumulator are divided by the operand pointed to by the address A1-A9 embedded within the instruction to produce a 24-bit quotient. Recall that A1-A8 select the offset within a 256-word sector, and A9 is the "residual bit" that selects between the current sector and the "residual sector". The quotient is available in the P-Q Register (0775 octal) on the 8th instruction (more accurately, 8 computer cycles) following the DIV. However, the result will remain in the P-Q register until the next MPH, MPY, or DIV. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| TNZ |

0 |

1 |

0 |

0 |

1 |

This is a conditional jump instruction, which branches to

the address embedded in the instruction if the accumulator

is not zero, but simply continues to the next instruction in

sequence if the accumulator is zero. Bits A1-A8 of the

embedded address represent the new offset within the

currently selected 256-word instruction sector, while bit A9

gives the syllable number within that word. The

"residual sector" cannot be accessed. The instruction

sector and data sector are not changed by the jump. As mentioned, the target address for the machine instruction itself had to be within the current sector, because its 8-bit address offset is embedded within the instruction. However, the assembler would transparently work around this problem, allowing essentially any target address to be used. For the sake of discussion, imagine an assembly language instruction, TNZ OINITin which the target location OINIT is not in the current memory sector. The workaround procedure used by the assembler was this:

The distinction between TNZ and TNZ* is reminiscent of the distinction between HOP and HOP* discussed earlier. As with HOP*, it is is unclear whether the * for TNZ* was present in the source code or not. It is therefore my assumption (and the modern LVDC assembler's assumption) that TNZ (without *) was always used in source code, while the * in TNZ* is only present in assembly listings. I am unaware of any evidence to the contrary. See also TMI, TRA, HOP, and the pseudo-op BLOCK. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| MPH |

0 |

1 |

0 |

1 |

5 |

LVDC only ... not PTC. This is a multiplication instruction. It is exactly like MPY except that the program "holds" until the multiplication is complete, so that the product is available from the accumulator or from the P-Q Register at the next instruction following MPY. However, the result will remain in the P-Q register until the next MPH, MPY, or DIV. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| CIO |

0 |

0 |

1 |

0 |

1 |

TBD |

PTC only ... not LVDC. There

is no LVDC equivalent for this instruction, which can be

viewed as a way of extending the LVDC/PTC PIO

instruction (see below) to a wider range of uses. Here's what the original PTC documentation has to say about CIO: "Controls the input, output operations of the CPU. The operand address bits specify the operation to be performed." A list of the CIO i/o ports is given below. As far as I know, only ports 154, 214, and 220 are for input, and they load the accumulator when used. Other ports are for output only, and the accumulator should to be loaded, prior to the CIO itself, with any additional data the specific operation requires, but is not affected by the operation. Note that most output operations do not require any such supplemental data, and therefore ignore whatever value is stored in the accumulator. Many of the operations relate to inhibiting or enabling interrupts (as you can see from the table above!), sending commands to the PTC's printer or plotter, etc. In assembly language, the operand of the instruction is always a literal 3-digit octal number.

|

||||||||||||||||||||||||||||||||||||||||||||||||||

| AND |

0 |

1 |

1 |

0 |

1 |

Logically ANDs the contents of the accumulator with the contents of the address embedded within the instruction and places the result in the accumulator. Recall that A1-A8 select the offset within a 256-word sector, and A9 is the "residual bit" that selects between the current sector and the "residual sector". | |||||||||||||||||||||||||||||||||||||||||||||||||||

| ADD |

0 |

1 |

1 |

1 |

1 |

Adds the contents of the

accumulator with the contents of the address embedded within

the instruction and places the result in the

accumulator. Recall that A1-A8 select the offset

within a 256-word sector, and A9 is the "residual bit" that

selects between the current sector and the "residual

sector". What about the carry bit? As far as I can tell, the CPU has no provision for carry bit that's useful at the software level. If you want to do multi-word precision arithmetic (say, 52-bit addition instead of just 26-bit addition), then you have to find some indirect, software-only way of detecting carry rather than on relying on the CPU to provide you with some easy way of handling it. It's certainly mathematically possible to do so: When adding two addends of the same sign using 2's-complement arithmetic, you can detect carry because the sum has the opposite sign of the addends, whereas adding two addends of opposite signs cannot result in carry anyway. But the coding to exploit this mathematical possibility is obviously going to be cumbersome and inconvenient. (The low-level adder circuit itself can deal with a carry bit, of course. The adder performs additions serially, starting with the least-significant bit and moving upward to the most-significant, and at each bit-stage there's a carry bit from the previous stage to worry about. However, the final carry bit is not accessible to software, and the carry-bit latch is cleared by any CLA instruction, making it very tough to transfer the carry-bit latch's contents from one word-addition to the next. In theory, if you could figure out a way to do multi-precision arithmetic without using CLA, perhaps you could exploit that hidden carry bit. But I'm having trouble seeing any way you might do it. That could just be my failure of imagination, of course.) |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| TRA |

1 |

0 |

0 |

0 |

1 |

TRA is an

unconditional jump instruction, which branches to the

address embedded in the instruction. Bits A1-A8 of the

embedded address represent the new offset within the

currently selected 256-word instruction sector, while bit A9

gives the syllable number within that word. The

"residual sector" cannot be accessed. Note, however, that the assembler could work around the limitation that the target address had to be in the same sector. The assembler would automatically insert a HOP instruction instead of a TRA whenever it found that it was necessary to do so. For example, consider the instruction "TRA ETCBTC". If the target location ETCBTC is within the current instruction sector, the assembler would indeed assemble this exactly as expected, using a TRA instruction with opcode 1000. Actually, the assembler would refuse to directly do a TRA to a target in the same instruction sector under some circumstances, presumably to help guard the programmer from easy-to-make errors. The condition I've noticed in which this occurs is if the target address has been tagged by the assembler as being in a region with a different setting for the data module or sector, since unlike a HOP instruction, a TRA instruction doesn't alter the DM/DS settings. Whereas if a CDS instruction (which changes the DM/DS settings in the processor itself) happens to be at the target location, it doesn't trigger a replacement by HOP. Quite a complicated set of conditions! One wonders if the original programmers actually had much awareness at the time (or cared!) that these substitutions were being made for them. But if the target location (ETCBTC in this example) wasn't within the current instruction sector or failed the DM/DS conditions, then the assembler would instead perform the following complicated maneuver which preserves the expected program logic, at the cost of an extra machine cycle and an extra word of memory:

|

|||||||||||||||||||||||||||||||||||||||||||||||||||

| XOR |

1 1 |

0 1 |

0 0 |

1 1 |

1 |

Logically exclusive-ORs the

contents of the accumulator with the contents of the address

embedded within the instruction and places the result in the

accumulator. Recall that A1-A8 select the offset within

a 256-word sector, and A9 is the "residual bit" that selects

between the current sector and the "residual sector". Note: The opcode bits for XOR are 1001 (118) for LVDC, but 1101 (158) for PTC. However, the PTC documentation incorrectly indicates that the coding is 1001. (Either that, or the assembler assembled the instruction incorrectly; take your pick of explanations.) |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| PIO |

1 |

0 |

1 |

0 |

1 |

Reads or writes an i/o

port. Bits A1-A9 select the source and

destination of the i/o. A table of the i/o ports

vs. addresses is given in the following section. In so far as assembly-language syntax is concerned, the operand of the instruction is always a literal octal numerical constant. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| STO |

1 |

0 |

1 |

1 |

1 |

Stores the contents of the

accumulator in the word indicated by the address embedded

within the instruction. Recall that A1-A8 select the

offset within a 256-word sector, and A9 is the "residual

bit" that selects between the current sector and the

"residual sector". The following addresses are

special, as described in the

documentation of the STO instruction (see p. 2-17):

The LVDC and PTC cases appear to be very different, but

the difference is really just that the PTC has no

multiplication and division instructions, and hence has no

product-quotient or multiplicand-divisor register. Nevertheless, the description of 776 and 777 above is

admittedly a bit tricky to understand, so let's try to get

at it another way. It's mainly about return

addresses for subroutines and interrupt-service

routines. Most modern CPU's have a "CALL"

instruction for calling subroutines, and part of what CALL

would do is to push the return address onto a dedicated

"stack" in memory; a subsequent "RET" instruction would

then pop the return address out of the stack and jump to

that return address. But the LVDC/PTC CPU has no

such features ... no CALL, no RET, no stack. What it

does instead is this: During the process of

executing any given LVDC/PTC instruction, a HOP constant

for the LVDC instruction at the next successive memory

address is formed. Keep in mind that the next

instruction successively in memory is not necessarily the

next instruction sequentially executed. Whatever the

next instruction executed, the previously-generated HOP

constant is temporarily shoved into a register called

"HOP-saver". Thus if the very next instruction executed

after a transfer instruction (HOP, TRA,

TMI, or TNZ) is STO 776 or STO

777, what ends up getting stored in location 776 or

777 is the HOP constant for the memory address that

follows the previously executed transfer instruction

instruction in memory. Or in brief, for a transfer

instruction to a subroutine, what gets saved at 776 or 777

is the return address of the subroutine. In fact,

this is the only easy method for accessing such return

addresses, and the only way at all for accessing return

addresses of interrupt-service routines. ...This becomes trickier if you have nested subroutine calls, because the nested routines can't each use the same storage buffers for their return addresses, and there's no way to temporarily replace the contents of 776/777 while still being able to restore the original contents afterward. (You can certainly read 776/777, for example with CLA 776, but you can't save an arbitrary value into either 776 or 777 afterward.) In other words, if you have a nested subroutine, you have to manage the return address of the parent subroutine manually. Here's an example I've constructed to illustrate the method: You can, of course, perform the same trick with multiple levels of nesting, at the cost of allocating more and more variables to store the manually-managed return addresses. It is perhaps obvious as well that the same address (776 vs 777) should not be used for interrupt-service routines and and for regular subroutines, even for the few instruction cycles needed for manual management, or else tremendous care needs to be taken to insure that no interrupt can occur during a subroutine with conflicting storage requirements for the return addresses. The safest thing would be to use 776 for interrupt-service routines (and their subroutines) and 777 for non-interrupt subroutines, or vice-versa. In examining the PTC ADAPT Self-Test Program and the AS206-RAM Flight Program, the two seem to use the opposite choice, so there may not have been a customary standard for doing so from one program to the next. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| TMI |

1 |

1 |

0 |

0 |

1 |

This is a conditional jump

instruction, which branches to the address embedded in the

instruction if the accumulator is less than zero, but simply

continues to the next instruction in sequence if the

accumulator greater than or equal to zero. Bits A1-A8

of the embedded address represent the new offset within the

currently selected 256-word instruction sector, while bit A9

gives the syllable number within that word. The

"residual sector" cannot be accessed. As mentioned, the target address for the machine instruction itself had to be within the current sector, because its 8-bit address offset is embedded within the instruction. However, the assembler would transparently work around this problem, allowing essentially any target address to be used. The workaround used by the assembler is that same as that described for the TNZ instruction above. Instructions for which the workaround have been applied are shown on the assembly listing as "TMI*" rather than "TMI". As with TNZ*, it is is unclear whether the * for TMI* was present in the source code or not. It is therefore my assumption (and the modern LVDC assembler's assumption) that TMI (without *) was always used in source code, while the * in TMI* is only present in assembly listings. I am unaware of any evidence to the contrary. See also TNZ, TRA, HOP, and the pseudo-op BLOCK. |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| RSU |

1 0 |

1 0 |

0 1 |

1 1 |

1 |

Same as SUB, except that the

order of the operands in the subtraction is reversed. Note: The opcode bits for RSU are 1101 (158) for LVDC, but 0011 (03) for PTC. (0011 in LVDC is for the DIV instruction, which is missing from PTC.) |

|||||||||||||||||||||||||||||||||||||||||||||||||||

| CDS or CDSD or CDSS |

0 |

1 |

1 |

1 |

0 |

1 |

LVDC only ... not

PTC. Change the currently-selected 256-word data sector. For this instruction, A9 forms a part of the instruction itself, so only A1-A8 are significant. The partially overwrite the HOP Register as follows:  See also HOP. In terms of assembly-language syntax, there are the following variations: CDS SYMBOLNAMEThus CDS uses the characteristics of a variable name or a name defined with (for example) the DEQD or DEQS pseudo-ops (see below), whereas the module number and sector number are simply supplied with octal numeric literals in CDSD or CDSS. The difference between CDSD and CDSS is that the former selects duplex memory while the later selects simplex memory. In the usage I've seen, usage of CDSS is confined almost entirely to the context of USE DAT (see below). |

||||||||||||||||||||||||||||||||||||||||||||||||||

| CDS |

1 |

0 |

1 |

1 |

1 |

0 |

TBD |

PTC only ... not LVDC. This

functionally identical to the identically-named LVDC

instruction above, but is slightly different both

syntactically and in the encoding of the assembled

instruction. Changes the currently-selected 256-word data sector by partially overwriting the HOP Register as follows:  See also HOP. In terms of assembly-language syntax: CDS DM,DSDM is limited to 0 or 1, while DS is an octal literal from 0 to 17. |

|||||||||||||||||||||||||||||||||||||||||||||||||

| SHF SHL SHR |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

LVDC only ... not PTC. Performs a shift operation on the accumulator. For this instruction, bits A8 and A9 form a part of the instruction itself, but of the remaining bits only A1, A2, A5, and A6 are actually used, as follows:

By a "left" shift, we mean a shift toward the more-significant direction (multiplying by powers of 2); by a "right" shift, we mean a shift toward the less-significant direction (dividing by powers of 2). In terms of assembly-language syntax, I have never seen SHF itself used. Rather, the synonyms SHL (left shift) and SHR (right shift) are used, and only in the following variations: SHL Nwhere N is a literal decimal numerical constant. However, N is not limited to just 0, 1, or 2, even those are all that SHF directly supports. If an operand N>2 is encountered, the assembler transparently replaces it with an appropriate sequence of shift-by-2 and shift-by-1 instructions. Note: The original documentation of the SHF instruction itself does not actually describe the directionality of the shifts, nor the nature of the data used to fill the bit-positions vacated by the shift. It instead simply refers to the there-undefined terms "MSD shift" and "LSD shift". Elsewhere in the original documentation is a theory-of-operation for the electronic circuitry, and the additional information about directionality and fill-values given above is derived from the theory of operation. |

|||||||||||||||||||||||||||||||||||||||||||||||||

| SHF SHL SHR |

0 |

1 |

1 |

1 |

1 |

0 |

TBD |

PTC only ... not LVDC. Functionally similar to the identically-named LVDC instruction, but differs in detail. It does not provide a "clear accumulator" function as the LVDC instruction does, but allows a shift of up to 6 bit-positions in a single instruction (rather than up to 2 as in the LVDC). As far as the encoding is concerned: A7 determines the direction of the shift: 0 = left shift (filling vacated bit positions with 0), 1 = right shift (duplicating the sign bit into the vacated bit positions). As for A6-A1: